# **DAVICOM Semiconductor, Inc.**

# **DM9010**

10/100 Mbps Single Chip Ethernet Controller with General Processor Interface

**DATA SHEET**

**Preliminary**

Version: DM9010-DS-P03

Apr. 28 2005

# Content

| 1. GENERAL DESCRIPTION                                 |    |

|--------------------------------------------------------|----|

| 2. BLOCK DIAGRAM                                       | 7  |

| 3. FEATURES                                            | 8  |

| 4. PIN CONFIGURATION                                   | 9  |

| 4.1 Pin Configuration I: with MII Interface            | 9  |

| 4.2 PIN CONFIGURATION II: WITH 32-BIT DATA BUS         |    |

| 5. PIN DESCRIPTION                                     | 11 |

| 5.1 MII Interface                                      | 11 |

| 5.2 Processor Interface                                | 12 |

| 5.3 EEPROM INTERFACE                                   |    |

| 5.4 CLOCK INTERFACE                                    |    |

| 5.5 LED INTERFACE                                      |    |

| 5.6 10/100 PHY/FIBER                                   | 14 |

| 5.7 MISCELLANEOUS                                      | 14 |

| 5.8 POWER PINS                                         | 14 |

| 5.9 STRAP PINS TABLE                                   |    |

| 6. VENDOR CONTROL AND STATUS REGISTER SET              |    |

| 6.1 NETWORK CONTROL REGISTER (00H)                     | 17 |

| 6.2 Network Status Register (01H)                      | 17 |

| 6.3 TX Control Register (02H)                          |    |

| 6.4 TX Status Register I ( 03H ) for packet index I    |    |

| 6.5 TX STATUS REGISTER II ( 04H ) FOR PACKET INDEX I I |    |

| 6.6 RX Control Register ( 05H )                        | 19 |

| 6.7 RX Status Register ( 06H )                         | 19 |

| 6.8 RECEIVE OVERFLOW COUNTER REGISTER ( 07H )          |    |

| 6.9 BACK PRESSURE THRESHOLD REGISTER (08H)             | 20 |

| 6.10 Flow Control Threshold Register ( 09H )           |    |

| 6.11 RX/TX FLOW CONTROL REGISTER ( 0AH )               |    |

| 6.12 EEPROM & PHY CONTROL REGISTER ( 0BH )                                       | 21 |

|----------------------------------------------------------------------------------|----|

| 6.13 EEPROM & PHY Address Register ( 0CH )                                       | 21 |

| 6.14 EEPROM & PHY DATA REGISTER (EE_PHY_L : 0DH EE_PHY_H : 0EH)                  | 21 |

| 6.15 WAKE UP CONTROL REGISTER ( 0FH )                                            | 21 |

| 6.16 Physical Address Register ( 10H~15H )                                       | 22 |

| 6.17 MULTICAST ADDRESS REGISTER ( 16H~1DH )                                      | 22 |

| 6.18 GENERAL PURPOSE CONTROL REGISTER (1EH)                                      | 22 |

| 6.19 GENERAL PURPOSE REGISTER (1FH)                                              | 22 |

| 6.20 TX SRAM READ POINTER ADDRESS REGISTER (22H~23H)                             | 23 |

| 6.21 RX SRAM Write Pointer Address Register (24H~25H)                            |    |

| 6.22 Vendor ID Register (28H~29H)                                                | 23 |

| 6.23 PRODUCT ID REGISTER (2AH~2BH)                                               |    |

| 6.24 CHIP REVISION REGISTER (2CH)                                                | 23 |

| 6.25 Transmit Control Register 2 (2DH)                                           | 23 |

| 6.26 OPERATION TEST CONTROL REGISTER ( 2EH )                                     | 24 |

| 6.27 SPECIAL MODE CONTROL REGISTER ( 2FH )                                       |    |

| 6.28 EARLY TRANSMIT CONTROL/STATUS REGISTER ( 30H )                              |    |

| 6.29 Transmit Check Sum Control Register (31H)                                   | 25 |

| 6.30 RECEIVE CHECK SUM CONTROL STATUS REGISTER ( 32H )                           | 25 |

| 6.31 External PHYCeiver Address Register (33H)                                   | 25 |

| 6.32 GENERAL PURPOSE CONTROL REGISTER 2 (34H)                                    | 25 |

| 6.33 GENERAL PURPOSE REGISTER 2 (35H)                                            | 26 |

| 6.34 GENERAL PURPOSE CONTROL REGISTER 3 (36H)                                    | 26 |

| 6.35 GENERAL PURPOSE REGISTER 3 (37H)                                            | 26 |

| 6.36 Monitor Register 1 ( 40H )                                                  | 26 |

| 6.37 MONITOR REGISTER 2 (41H)                                                    | 26 |

| 6.38 MEMORY DATA PRE-FETCH READ COMMAND WITHOUT ADDRESS INCREMENT REGISTER (F0H) | 27 |

| 6.39 MEMORY DATA READ COMMAND WITHOUT ADDRESS INCREMENT REGISTER (F1H)           | 27 |

| 6.40 MEMORY DATA READ COMMAND WITH ADDRESS INCREMENT REGISTER (F2H)              | 27 |

| 6.41 MEMORY DATA READ_ADDRESS REGISTER (F4H~F5H)                                 | 27 |

| 6.42 MEMORY DATA WRITE COMMAND WITHOUT ADDRESS INCREMENT REGISTER (F6H)          | 27 |

| 6.43 MEMORY DATA WRITE COMMAND WITH ADDRESS INCREMENT REGISTER (F8H)             | 27 |

| 6.44 MEMORY DATA WRITE_ADDRESS REGISTER (FAH~FBH)                                | 27 |

| 6.45 TX PACKET LENGTH REGISTER (FCH~FDH)                                         | 27 |

| 6.46 Interrupt Status Register (FEH)                                 | 28             |

|----------------------------------------------------------------------|----------------|

| 6.47 Interrupt Mask Register (FFH)                                   | 28             |

| 7. EEPROM FORMAT                                                     | 29             |

|                                                                      | •              |

| 8. MII REGISTER DESCRIPTION                                          | A .            |

| 8.1 BASIC MODE CONTROL REGISTER (BMCR) - 00                          |                |

| 8.2 BASIC MODE STATUS REGISTER (BMSR) - 01                           | 32             |

| 8.3 PHY ID Identifier Register #1 (PHYID1) - 02                      |                |

| 8.4 PHY ID IDENTIFIER REGISTER #2 (PHYID2) - 03                      | A <sup>p</sup> |

| 8.5 Auto-negotiation Advertisement Register (ANAR) - 04              |                |

| 8.6 AUTO-NEGOTIATION LINK PARTNER ABILITY REGISTER (ANLPAR) – 05     |                |

| 8.7 AUTO-NEGOTIATION EXPANSION REGISTER (ANER)- 06                   |                |

| 8.8 DAVICOM SPECIFIED CONFIGURATION REGISTER (DSCR) - 16             | 37             |

| 8.9 DAVICOM SPECIFIED CONFIGURATION AND STATUS REGISTER (DSCSR) - 17 | 38             |

| 8.10 10BASE-T CONFIGURATION/STATUS (10BTCSR) - 18                    |                |

| 8.11 Power Down Control Register (PWDOR) - 19                        |                |

| 8.12 (Specified config) Register – 20                                | 41             |

| 9. FUNCTIONAL DESCRIPTION                                            | 42             |

| 9.1 Host Interface                                                   |                |

| 9.1 HOST INTERFACE                                                   |                |

|                                                                      |                |

| 9.3 PACKET TRANSMISSION                                              |                |

| 9.4 PACKET RECEPTION                                                 |                |

| 9.5 100Base-TX Operation                                             |                |

| 9.5.1 4B5B Encoder                                                   |                |

| 9.5.2 Scrambler                                                      |                |

| 9.5.3 Parallel to Serial Converter                                   |                |

| 9.5.4 NRZ to NRZI Encoder                                            |                |

| 9.5.5 MLT-3 Converter                                                |                |

| 9.5.6 MLT-3 Driver                                                   |                |

| 9.5.7 4B5B Code Group                                                |                |

| 9.6 100Base-TX Receiver                                              | 45             |

| 9.6.1 Signal Detect                                                  | 45             |

| 9.6.2 Adaptive Equalization                                          | 45             |

| 9.6.3 MLT-3 to NRZI Decoder                                        | 45 |

|--------------------------------------------------------------------|----|

| 9.6.4 Clock Recovery Module                                        | 45 |

| 9.6.5 NRZI to NRZ                                                  | 45 |

| 9.6.6 Serial to Parallel                                           | 45 |

| 9.6.7 Descrambler                                                  | 45 |

| 9.6.8 Code Group Alignment                                         | 46 |

| 9.6.9 4B5B Decoder                                                 | 46 |

| 9.7 10Base-T Operation                                             |    |

| 9.8 Collision Detection                                            |    |

| 9.9 Carrier Sense                                                  | 46 |

| 9.10 Auto-Negotiation                                              | 46 |

| 9.11 Power Reduced Mode                                            | 47 |

| 9.11.1 Power Down Mode                                             | 47 |

| 9.11.2 Reduced Transmit Power Mode                                 |    |

| 10. DC AND AC ELECTRICAL CHARACTERISTICS                           | 48 |

| 10.1 Absolute Maximum Ratings                                      | 48 |

| 10.1.1 Operating Conditions                                        |    |

| 10.2 DC ELECTRICAL CHARACTERISTICS (VDD = 3.3V)                    | 48 |

| 10.3 AC ELECTRICAL CHARACTERISTICS & TIMING WAVEFORMS              | 49 |

| 10.3.1 TP Interface                                                |    |

| 10.3.2 Oscillator/Crystal Timing                                   | 49 |

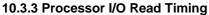

| 10.3.3 Processor I/O Read Timing                                   | 49 |

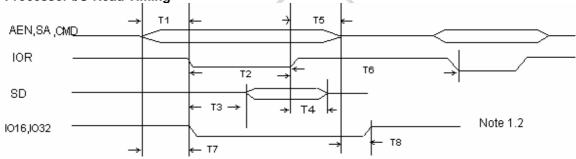

| 10.3.4 Processor I/O Write Timing                                  | 50 |

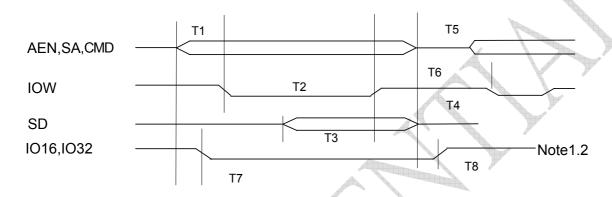

| 10.3.5 External MII Interface Transmit Timing                      | 51 |

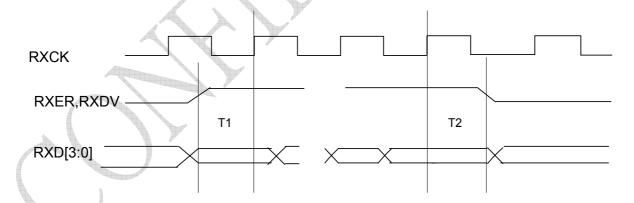

| 10.3.6 External MII Interface Receive Timing                       | 51 |

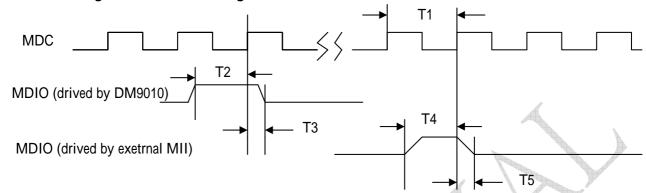

| 10.3.7 MII Management Interface Timing                             | 52 |

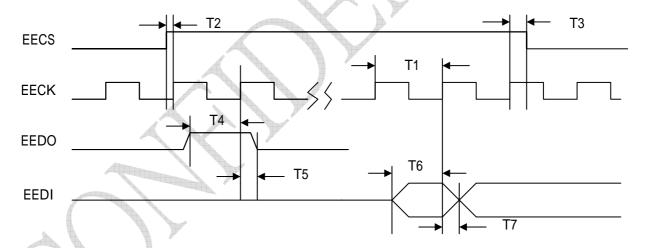

| 10.3.8 EEPROM Interface Timing                                     | 52 |

| 11. APPLICATION NOTES                                              | 53 |

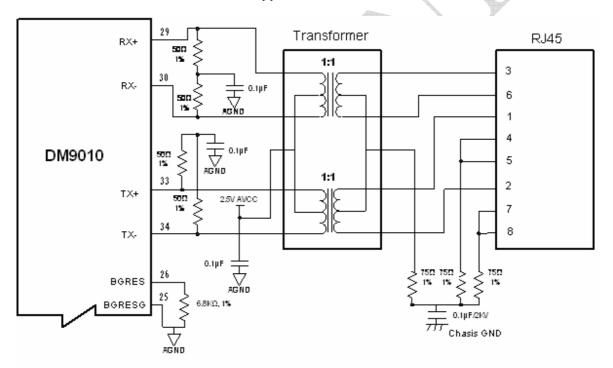

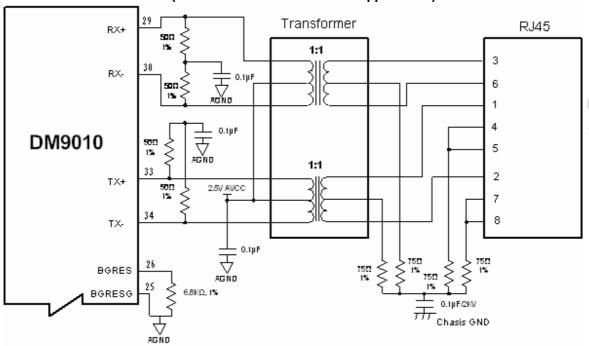

| 11.1 NETWORK INTERFACE SIGNAL ROUTING                              | 53 |

| 11.2 10BASE-T/100BASE-TX AUTO MDIX APPLICATION                     | 53 |

| 11.3 10Base-T/100Base-TX ( Non Auto MDIX Transformer Application ) | 54 |

| 11.4 Power Decoupling Capacitors                                   | 55 |

| 12 ODDEDING INFORMATION         |        |

|---------------------------------|--------|

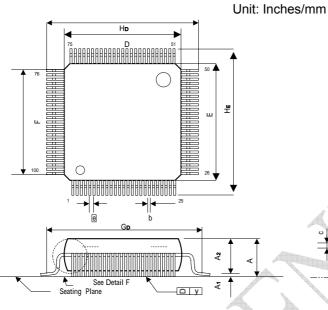

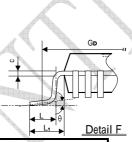

| 12. PACKAGE INFORMATION         | 60     |

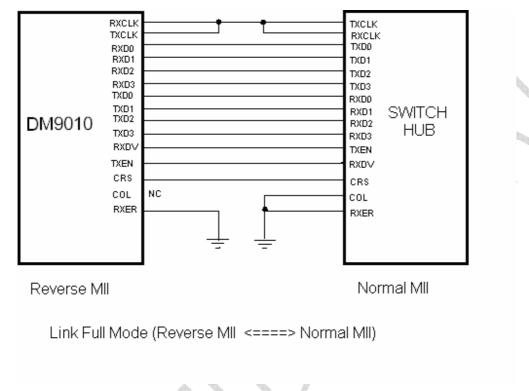

| 11.9 Application of reverse MII | <br>59 |

| 11.8 Crystal Selection Guide    | <br>58 |

| 11.7 Magnetics Selection Guide  | <br>58 |

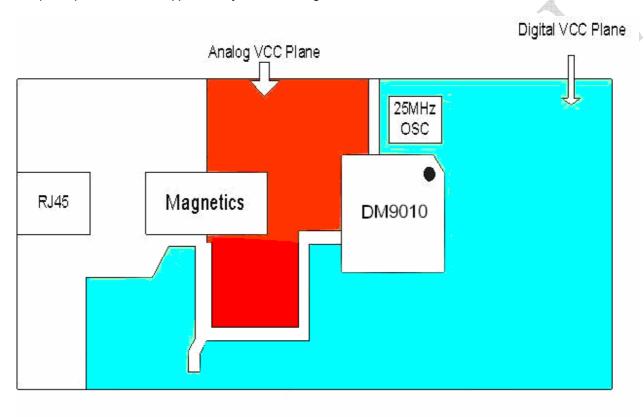

| 11.6 POWER PLANE PARTITIONING   | <br>57 |

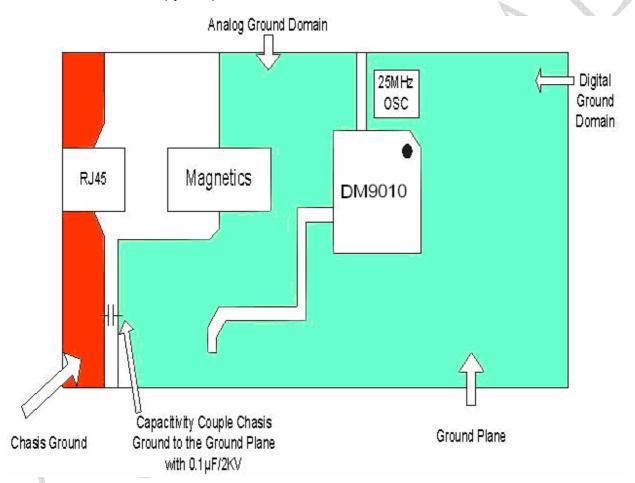

| 11.5 GROUND PLANE LAYOUT        | <br>56 |

|                                 |        |

#### 1. General Description

The DM9010 is a fully integrated and cost-effective single chip Fast Ethernet MAC controller with a general processor interface, a 10/100M PHY and 16K Byte SRAM. It is designed with low power and high performance process that support 3.3V with 5V tolerance.

The DM9010 also provides a MII interface to connect HPNA device or other transceivers that support MII interface. The DM9010 supports 8-bit, 16-bit and 32-bit uP interfaces to internal memory accesses for

different processors. The PHY of the DM9010 can interface to the UTP3, 4, 5 in 10Base-T and UTP5 in 100Base-TX. It is fully compliant with the IEEE 802.3u Spec. Its auto-negotiation function will automatically configure the DM9010 to take the maximum advantage of its abilities. The DM9010 also supports IEEE 802.3x full-duplex flow control. This programming of the DM9010 is very simple, so user can port the software drivers to any system easily.

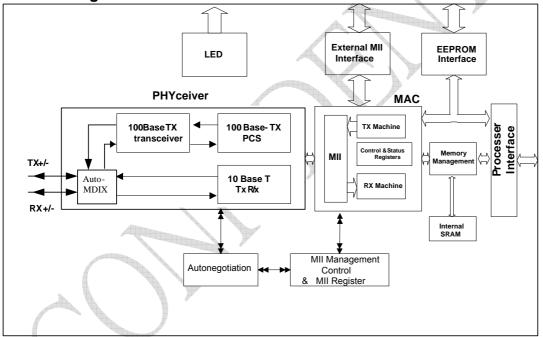

# 2. Block Diagram

#### 3. Features

100-pin LQFP.

Supports processor interface: Byte/word/Dword of I/O command to internal memory data operation Integrated 10/100M transceiver with AUTO-MDIX Supports MII and reverses MII interface Supports back pressure mode for half-duplex mode flow control IEEE802.3x flow control for full-duplex mode Supports wakeup frame, link status change and magic packet events for remote wake up Integrated 16K Byte SRAM Build in 3.3V to 2.5V regulator Supports early Transmit

Supports IP/TCP/UDP checksum generation and checking

Supports automatically load vendor ID and

Supports automatically load vendor ID and product ID from EEPROM

Supports 7 or 23 GPIO pins

Optional EEPROM configuration

Very low power consumption mode:

- Power reduced mode (cable detection)

- Power down mode

- Selectable TX drivers for 1:1 or 1.25:1

transformers for additional power reduction.

- 1: 1 transformers only when Auto MDIX

Enable .

Compatible with 3.3V and 5.0V tolerant I/O

## 4. Pin Configuration

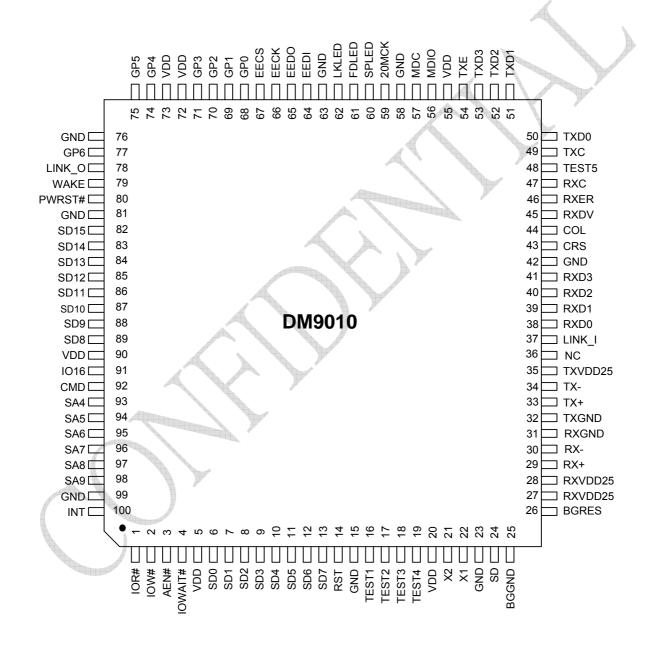

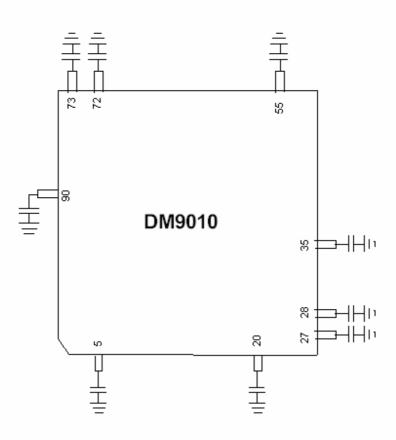

#### 4.1 Pin Configuration I: with MII Interface

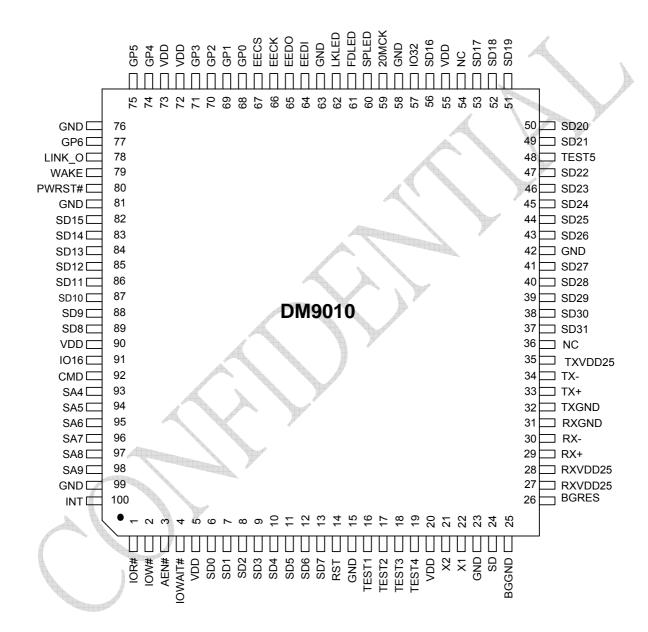

#### 4.2 Pin Configuration II: with 32-Bit Data Bus

# 5. Pin Description

I= Input, O=Output, I/O= Input/Output, O/D= Open Drain, P= Power,

LI= reset Latch Input, #= asserted low, PD=internal pull-low about 60K ohm, PU=internal pull-high

#### 5.1 MII Interface

| Pin No.         | Pin Name  | I/O    | Description                                                                                                                                                                                                                        |

|-----------------|-----------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 37              | LINK_I    | I,PD   | External MII device link status                                                                                                                                                                                                    |

| 41,40,39,<br>38 | RXD [3:0] | I,PD   | External MII Receive Data 4-bit nibble data input (synchronous to RXCLK) when in 10/100 Mbps. MII mode                                                                                                                             |

| 43              | CRS       | I/O,PD | External MII Carrier Sense Active high to indicate the pressure of carrier, due to receive or transmit activities in 10 Base-T or 100 Base-TX mode. This pin is output in reverse MII interface.                                   |

| 44              | COL       | I/O,PD | External MII Collision Detect. This pin is output in reverse MII interface.                                                                                                                                                        |

| 45              | RX_DV     | I,PD   | External MII Receive Data Valid                                                                                                                                                                                                    |

| 46              | RX_ER     | I,PD   | External MII Receive Error                                                                                                                                                                                                         |

| 47              | RX_CLK    | I,PD   | External MII Receive Clock                                                                                                                                                                                                         |

| 49              | TX_CLK    | I/O,PD | External MII Transmit Clock. This pin in output in MII interface.                                                                                                                                                                  |

| 53,52,51,<br>50 | TXD [3:0] | O,PD   | External MII Transmit Data 4-bit nibble data outputs (synchronous to the TX_CLK) when in 10/100Mbps nibble mode TXD [2:0] is also used as the strap pins of IO base address. IO base = (strap pin value of TXD [2:0]) * 10H + 300H |

| 54              | TX_ EN    | O,PD   | External MII Transmit Enable                                                                                                                                                                                                       |

| 56              | MDIO      | I/O,PD | MII Serial Management Data                                                                                                                                                                                                         |

| 57              | MDC       | O,PD   | MII Serial Management Data Clock This pin is also used as the strap pin of the polarity of the INT pin When the MDC pin is pulled high, the INT pin is low active; otherwise the INT pin is high active                            |

#### 5.2 Processor Interface

| 1                                                                  | IOR#                                | I,PD   | Processor Read Command                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|--------------------------------------------------------------------|-------------------------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                                                                    |                                     |        | This pin is low active at default; its polarity can be modified by EEPROM setting. See the EEPROM content description for detail                                                                                                                                                                                                                                                                                                                                 |  |  |

| 2                                                                  | IOW#                                | I,PD   | Processor Write Command This pin is low active at default; its polarity can be modified by EEPROM setting. See the EEPROM content description for detail                                                                                                                                                                                                                                                                                                         |  |  |

| 3                                                                  | AEN                                 | I,PD   | Address Enable A low active signal used to select the DM9010.                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| 4                                                                  | IOWAIT                              | O,PD   | Processor Command Ready When a command is issued before last command is completed, the IOWAIT will be pulled low to indicate the current command is waited The polarity and output type can be updated by EEPROM. The default is Open-Drain output and low active.                                                                                                                                                                                               |  |  |

| 14                                                                 | RST                                 | I,PD   | Hardware Reset Command, active high to reset the DM9010                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| 6,7,8,9,10,<br>11,12,13,<br>89,88,87,<br>86,85,84,<br>83,82        | SD0~15                              | I/O,PD | Processor Data Bus bit 0~15                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

| 93,94,95,                                                          | SA4~9                               | I,PD   | Address Bus 4~9                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| 96,97,98                                                           |                                     | ·,· -  | These pins are used to select the DM9010. When SA9 and SA8 are in high states, and SA7 and AEN are in low states, and SA6~4 are matched with strap pins TXD2~0, the DM9010 is selected.                                                                                                                                                                                                                                                                          |  |  |

| 92                                                                 | CMD                                 | I,PD   | Command Type When high, the access of this command cycle is DATA port When low, the access of this command cycle is INDEX port                                                                                                                                                                                                                                                                                                                                   |  |  |

| 91                                                                 | IO16                                | 0      | Word Command Indication When the access of internal memory is word or Dword width, this pin will be asserted This pin is low active at default; its polarity can be modified by EEPROM setting. See the EEPROM content description for detail                                                                                                                                                                                                                    |  |  |

| 100                                                                | INT                                 | O,PD   | Interrupt Request This pin is high active at default, its polarity can be modified by EEPROM setting or strap pin MDC. See the EEPROM content description for detail                                                                                                                                                                                                                                                                                             |  |  |

| 56,53,52,<br>51,50,49,<br>47,46,45,<br>44,43,41,<br>40,39,38<br>37 | SD16~31 (in<br>double word<br>mode) | I/O,PD | Processor Data Bus bit 16~31 These pins are used as data bus bits 16~31 when the DM9010 is set to double word mode (the straps pin EEDO is pulled high and WAKE is not pull-high)                                                                                                                                                                                                                                                                                |  |  |

| 57                                                                 | IO32 (in double<br>word mode)       | O,PD   | Double Word Command Indication This pins is used as the double word command indication when the DM9010 is set to double data word mode, and this pin will be asserted when the access of internal memory is double word width This pin is low active at default; its polarity can be modified by EEPROM setting. See the EEPROM content description for detail When the IO32 pin is pulled high, the INT pin is low active; otherwise the INT pin is high active |  |  |

#### 5.3 EEPROM Interface

| 64 | EEDI | I    | Data from    | EEPROM                                  |                  |                                                                                                 |

|----|------|------|--------------|-----------------------------------------|------------------|-------------------------------------------------------------------------------------------------|

| 65 | EEDO | O,PD | it can set t | also used<br>he data wi<br>ler table is | idth of the inte | a. It combines with strap pin WOL, and rnal memory access where the logic 1 means the strap pin |

| 66 | EECK | O,PD | Clock to E   | EPROM                                   |                  |                                                                                                 |

| 67 | EECS | O,PD |              | also used                               | l as a strap pin | to define the LED modes.  Indee is mode 1; Otherwise it is mode 0                               |

Note: The pins EECS,EECK and EEDO are all have a pulled down resistor about 60k ohm internally

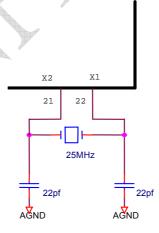

#### 5.4 Clock Interface

| 21 | X2_25M  | 0 | Crystal 25MHz Out                                                                                                                                                                                                            |

|----|---------|---|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 22 | X1_25M  | I | Crystal 25MHz In                                                                                                                                                                                                             |

| 59 | CLK20MO |   | 20Mhz Clock Output It is used as the clock signal for the external MII device's clock is 20MHz This pin has a pulled down resistor about 60k ohm internally. When pin TEST5 state is high, this pin act as the system clock. |

#### 5.5 LED Interface

| 60          | SPLED | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Speed LED                                                                   |  |

|-------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|--|

|             |       | The state of the s | Its low output indicates that the internal PHY is operated in 100M/S, or it |  |

|             |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | is floating for the 10M mode of the internal PHY                            |  |

| 61          | FDLED | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Full-duplex LED                                                             |  |

|             |       | A A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | In LED mode 1, Its low output indicates that the internal PHY is operated   |  |

|             |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | in full-duplex mode, or it is floating for the half-duplex mode of the      |  |

|             |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | internal PHY                                                                |  |

| A Section 1 |       | ĺ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | In LED mode 0, Its low output indicates that the internal PHY is operated   |  |

|             |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | in 10M mode, or it is floating for the 100M mode of the internal PHY        |  |

| 62          | LKLED | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Link / Active LED                                                           |  |

|             |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | In LED mode 1, it is the combined LED of link and carrier sense signal of   |  |

|             |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | the internal PHY                                                            |  |

|             |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | In LED mode 0, it is the LED of the carrier sense signal of the internal    |  |

|             |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | PHY only                                                                    |  |

# 5.6 10/100 PHY/Fiber

| 24    | SD      | I   | Fiber-optic Signal Detect PECL signal, which indicates whether or not the fiber-optic receive pair is receiving valid levels |

|-------|---------|-----|------------------------------------------------------------------------------------------------------------------------------|

| 25    | BGGND   | Р   | Bandgap Ground                                                                                                               |

| 26    | BGRES   | I/O | Bandgap Pin                                                                                                                  |

| 27,28 | RXVDD25 | Р   | Internal regulator 2.5V output for TP RX                                                                                     |

| 29    | RXI+    | I/O | TP RX Input                                                                                                                  |

| 30    | RXI-    | I/O | TP RX Input                                                                                                                  |

| 31    | RXGND   | Р   | RX Ground                                                                                                                    |

| 32    | TXGND   | Р   | TX Ground                                                                                                                    |

| 33    | TXO+    | I/O | TP TX Output                                                                                                                 |

| 34    | TXO-    | I/O | TP TX Output                                                                                                                 |

| 35    | TXVDD25 | Р   | Internal regulator 2.5V output for TP TX                                                                                     |

# 5.7 Miscellaneous

| 16,17,18, | TEST1~TEST4 | I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Operation Mode                                                               |

|-----------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|

| 19        |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Test 1, 2, 3, 4 = (1, 1, 0, 0) in normal application                         |

|           |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                              |

| 48        | TEST5       | I,PD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Internal system clock source                                                 |

|           |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 0: use internal 50MHz clock *(Suggestion)                                    |

|           |             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1: use CLK20MO pin                                                           |

| 68,69,70, | GP0~6       | I/O,PD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | General I/O Ports                                                            |