# **TLE7181EM**

H-Bridge and Dual Half Bridge Driver IC

**Automotive Power**

**Table of Contents**

## **Table of Contents**

| 1                                                                                                                        | Overview 3                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2                                                                                                                        | Block Diagram 4                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| <b>3</b><br>3.1<br>3.2                                                                                                   | Pin Configuration 5 Pin Assignment 5 Pin Definitions and Functions 5                                                                                                                                                                                                                                                                                                                                                                                                  |

| <b>4</b><br>4.1<br>4.2<br>4.3<br>4.4                                                                                     | General Product Characteristics 7 Absolute Maximum Ratings 7 Functional Range 8 Thermal Resistance 9 Default State of Inputs 9                                                                                                                                                                                                                                                                                                                                        |

| <b>5</b><br>5.1<br>5.1.1<br>5.1.2<br>5.1.3<br>5.1.4                                                                      | Description and Electrical Characteristics 10 MOSFET Driver 10 Driving MOSFET Output Stages 10 MOSFET Output Stages 10 Dead Time 11 Bootstrap Principle 11                                                                                                                                                                                                                                                                                                            |

| 5.1.5<br>5.1.6<br>5.1.7<br>5.1.8                                                                                         | 100% D.C. charge pumps 12 Reverse polarity protection of motor bridge 12 Sleep mode 12 Wake up 12                                                                                                                                                                                                                                                                                                                                                                     |

| 5.1.9<br>5.2<br>5.2.1<br>5.2.2<br>5.2.3<br>5.2.4<br>5.2.5<br>5.2.6<br>5.2.7<br>5.2.8<br>5.2.9<br>5.2.10<br>5.2.11<br>5.3 | Electrical Characteristics 13  Protection and Diagnostic Functions 17  State diagram of different operation modes 17  Short Circuit Protection 18  SCDL Pin Open Detection 18  Vs and VDH Over Voltage Warning 18  VS Under Voltage Shutdown 18  VREG Under Voltage Warning 18  Over Temperature Warning 19  Over Current Warning 19  Passive Gxx Clamping 19  ERR Pin 19  Electrical Characteristics 21  Shunt Signal Conditioning 23  Electrical Characteristics 23 |

| <b>6</b><br>6.1<br>6.2                                                                                                   | <b>Application Information</b> 25<br>Layout Guide Lines 26<br>Further Application Information 26                                                                                                                                                                                                                                                                                                                                                                      |

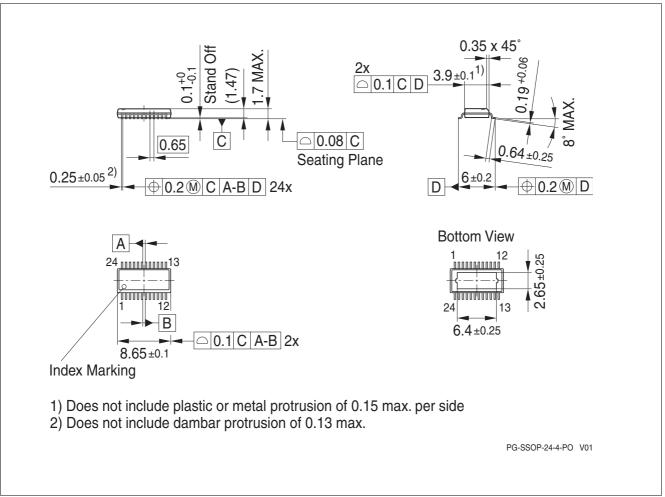

| 7                                                                                                                        | Package Outlines 27                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 8                                                                                                                        | Revision History 28                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

Data Sheet 2 Rev 1.1, 2010-09-30

#### **TLE7181EM**

## H-Bridge and Dual Half Bridge Driver IC

## 1 Overview

#### **Features**

- PWM/DIR-interface drives 4 N-Channel Power MOSFETs

- Unlimited D.C. switch on time of Low and Highside MOSFETs

- 0 ...95% at 20kHz & 100% Duty cycle of High Side MOSFETs

- 0 ... 100 % Duty cycle of Low Side MOSFETs

- · Additional output to drive a reverse polarity protection N-MOSFET

- Current sense OPAMP

- Low guiescent current mode

- Internal shoot through protection

- · Adjustable dead time

- 1 bit diagnosis / ERR

- Over current warning based on current sense OPAMP with fixed warning level

- Analog adjustable Short Circuit Protection levels via SCDL pin with open pin detection

- Over temperature warning

- · Over voltage warning

- · Under voltage warning and shutdown

- Green Product (RoHS compliant)

- · AEC Qualified

#### **Description**

The TLE7181EM is a H-bridge driver IC dedicated to control 4 N-channel MOSFETs typically forming the converter for a high current DC motor drives in the automotive sector. It incorporates several protection features such as over current and short circuit detection as well as under-, over voltage and over temperature diagnosis.

Typical applications are fans, pumps and electric power steering. The TLE7181EM is designed for a 12V power net.

## Table 1 Product Summary

| Specified operating voltage             | $V_{SOP}$  | 7.0 V 34 V   |

|-----------------------------------------|------------|--------------|

| Junction temperature                    | $T_{j}$    | -40 °C 150°C |

| Maximum output source resistance        | $R_{Sou}$  | 13.5 Ω       |

| Maximum output sink resistance          | $R_{Sink}$ | 9 Ω          |

| maximum quiescent current <sup>1)</sup> | $I_{QVS}$  | 8 μΑ         |

<sup>1)</sup> typical value at  $T_i$ =25°CC

| Туре      | Package    | Marking   |

|-----------|------------|-----------|

| TLE7181EM | PG-SSOP-24 | TLE7181EM |

PG-SSOP-24

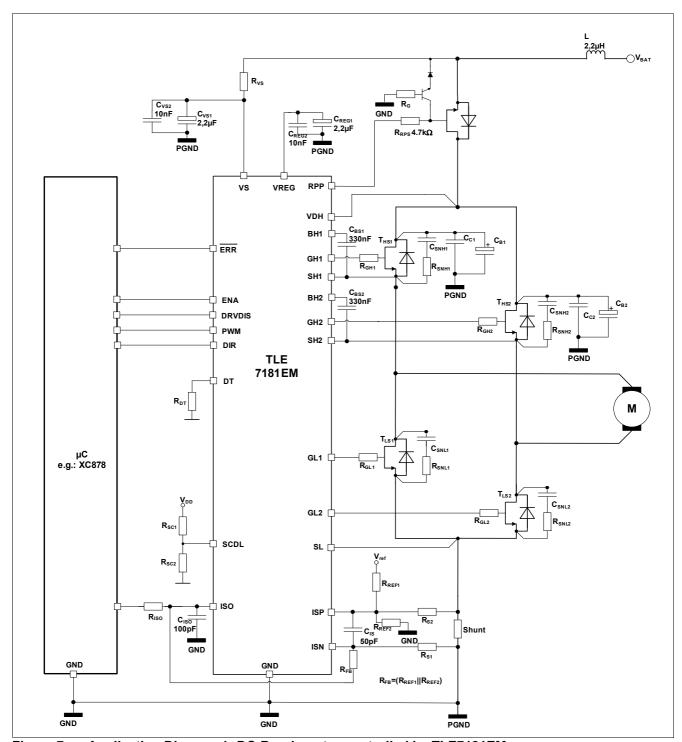

**Block Diagram**

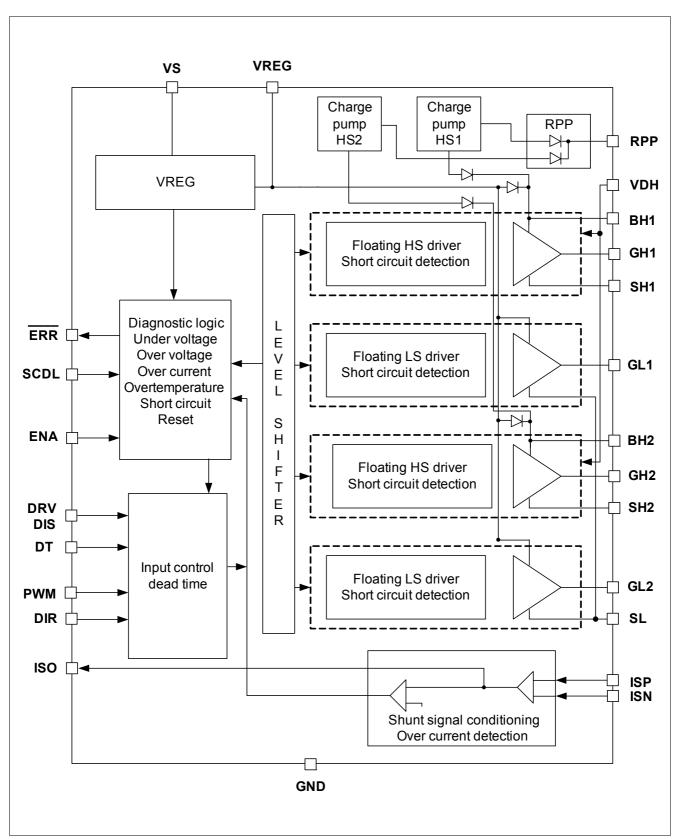

## 2 Block Diagram

Figure 1 Block diagram TLE7181EM

Data Sheet 4 Rev 1.1, 2010-09-30

**Pin Configuration**

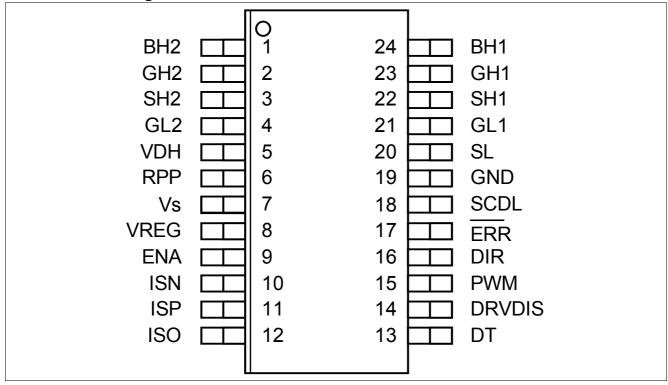

## 3 Pin Configuration

## 3.1 Pin Assignment

Figure 2 Pin Configuration

## 3.2 Pin Definitions and Functions

| # of | Symbol | Function                                                                            |

|------|--------|-------------------------------------------------------------------------------------|

| Pins |        |                                                                                     |

| 1    | BH2    | Pin for + terminal of the bootstrap capacitor of phase 2                            |

| 2    | GH2    | Output pin for gate of high side MOSFET 2                                           |

| 3    | SH2    | Pin for source connection of high side MOSFET 2                                     |

| 4    | GL2    | Output pin for gate of low side MOSFET 2                                            |

| 5    | VDH    | Voltage input common drain high side for short circuit detection                    |

| 6    | RPP    | charge pump output for reverse polarity protection of the motor bridge              |

| 7    | VS     | Pin for supply voltage                                                              |

| 8    | VREG   | Output of supply for driver output stage - connect to a capacitor                   |

| 9    | ENA    | Input pin for reset of ERR registers, active switch off of external MOSFETs and low |

|      |        | quiescent current mode, set HIGH to enable operation                                |

| 10   | ISN    | Input for OPAMP + terminal                                                          |

| 11   | ISP    | Input for OPAMP - terminal                                                          |

| 12   | ISO    | Output of OPAMP                                                                     |

| 13   | DT     | Input for adjustable dead time function, connect to GND via resistor                |

| 14   | DRVDIS | Disable DIR/PWM interface & all output stages switched off                          |

| 15   | PWM    | control input for PWM frequency and duty cycle                                      |

| 16   | DIR    | control input for spinning direction of the motor                                   |

Data Sheet 5 Rev 1.1, 2010-09-30

## **Pin Configuration**

| # of | Symbol | Function                                                  |

|------|--------|-----------------------------------------------------------|

| Pins |        |                                                           |

| 17   | ERR    | Push pull output stage                                    |

| 18   | SCDL   | Input pin for adjustable Short Circuit Detection function |

| 19   | GND    | Ground pin                                                |

| 20   | SL     | Pin for common source of lowside MOSFETs                  |

| 21   | GL1    | Output pin for gate of low side MOSFET 1                  |

| 22   | SH1    | Pin for source connection of high side MOSFET 1           |

| 23   | GH1    | Output pin for gate of high side MOSFET 1                 |

| 24   | BH1    | Pin for + terminal of the bootstrap capacitor of phase 1  |

| Tab  | Tab    | should be connected to GND                                |

**General Product Characteristics**

## 4 General Product Characteristics

## 4.1 Absolute Maximum Ratings

## Absolute Maximum Ratings 1)

40 °C  $\leq T_i \leq$  150 °C; all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Pos.    | Parameter                                       | Symbol     | Lim      | nit Values | Unit | Conditions                                                         |

|---------|-------------------------------------------------|------------|----------|------------|------|--------------------------------------------------------------------|

|         |                                                 |            | Min.     | Max.       |      |                                                                    |

| Voltage | s                                               | <u>'</u>   | <u>'</u> |            | '    |                                                                    |

| 4.1.1   | Supply voltage at VS                            | $V_{VS}$   | -0.3     | 45         | V    | _                                                                  |

| 4.1.2   | Supply voltage at VS                            | $V_{VSRP}$ | -4.0     | 45         | V    | <i>R</i> <sub>VS</sub> ≥10Ω                                        |

| 4.1.3   | Voltage range at VDH                            | $V_{VDH}$  | -0.3     | 55         | V    | _                                                                  |

| 4.1.4   | Voltage range at RPP                            | $V_{RPP}$  | -0.3     | 55         | V    | _                                                                  |

| 4.1.5   | maximum current at RPP                          | $I_{RPP}$  | -25      | 25         | mA   | _                                                                  |

| 4.1.6   | Voltage range at ENA                            | $V_{ENA}$  | -0.3     | 45         | V    | _                                                                  |

| 4.1.7   | Voltage range at SCDL                           | $V_{SCDL}$ | -0.3     | 6          | V    | _                                                                  |

| 4.1.8   | Voltage range at PWM, DIR, DT, DRVDIS           | $V_{DPI}$  | -0.3     | 6          | V    | _                                                                  |

| 4.1.9   | Voltage range at ERR, ISO                       | $V_{DPO}$  | -0.3     | 6          | V    | _                                                                  |

| 4.1.10  | Voltage range at ISP, ISN                       | $V_{OPI}$  | -5.0     | 5.0        | V    | _                                                                  |

| 4.1.11  | Voltage range at VREG                           | $V_{VREG}$ | -0.3     | 15         | V    | _                                                                  |

| 4.1.12  | Voltage range at BHx                            | $V_{BH}$   | -0.3     | 55         | V    | _                                                                  |

| 4.1.13  | Voltage range at GHx                            | $V_{GH}$   | -0.3     | 55         | V    | _                                                                  |

| 4.1.14  | Voltage range at GHx                            | $V_{GHP}$  | -7.0     | 55         | V    | t <sub>P</sub> <1µs; f=50kHz                                       |

| 4.1.15  | Voltage range at SHx                            | $V_{SH}$   | -2.0     | 45         | V    | _                                                                  |

| 4.1.16  | Voltage range at SHx                            | $V_{SHP}$  | -7.0     | 45         | V    | t <sub>P</sub> <1µs; <i>f</i> =50kHz                               |

| 4.1.17  | Voltage range at GLx                            | $V_{GL}$   | -0.3     | 18         | V    | _                                                                  |

| 4.1.18  | Voltage range at GLx                            | $V_{GLP}$  | -7.0     | 18         | V    | <i>t</i> <sub>P</sub> <0.5µs;<br><i>f</i> =50kHz                   |

| 4.1.19  | Voltage range at SL                             | $V_{SL}$   | -1.0     | 5.0        | V    | _                                                                  |

| 4.1.20  | Voltage range at SL                             | $V_{SLP}$  | -7.0     | 5.0        | V    | $t_{\rm P}$ <0.5 $\mu$ s;<br>f=50kHz;<br>$C_{\rm BS}$ $\geq$ 330nF |

| 4.1.21  | Voltage difference Gxx-Sxx                      | $V_{GS}$   | -0.3     | 15         | V    | _                                                                  |

| 4.1.22  | Voltage difference BHx-SHx                      | $V_{BS}$   | -0.3     | 15         | V    | _                                                                  |

| Temper  | atures                                          | •          | •        | •          | •    |                                                                    |

| 4.1.23  | Junction temperature                            | $T_{j}$    | -40      | 150        | °C   | _                                                                  |

| 4.1.24  | Storage temperature                             | $T_{stg}$  | -55      | 150        | °C   | _                                                                  |

| 4.1.25  | Lead soldering temperature (1/16" from body)    | $T_{sol}$  | _        | 260        | °C   | _                                                                  |

| 4.1.26  | Peak reflow soldering temperature <sup>2)</sup> | $T_{ref}$  | _        | 260        | °C   | _                                                                  |

| Power D | Dissipation                                     |            |          | I          |      | ·                                                                  |

| 4.1.27  | Power Dissipation (DC)                          | $P_{tot}$  | _        | 2          | W    | _                                                                  |

| -       | II.                                             | 1          |          |            |      | -I                                                                 |

Data Sheet 7 Rev 1.1, 2010-09-30

#### **General Product Characteristics**

### Absolute Maximum Ratings (cont'd)1)

40 °C  $\leq T_i \leq$  150 °C; all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Pos.   | Parameter                     | Symbol    | Lin      | nit Values | Unit | Conditions |

|--------|-------------------------------|-----------|----------|------------|------|------------|

|        |                               |           | Min.     | Max.       |      |            |

| ESD St | usceptibility                 | <u> </u>  | <u>'</u> |            |      |            |

| 4.1.28 | ESD Resistivity <sup>3)</sup> | $V_{ESD}$ | _        | 2          | kV   |            |

| 4.1.29 | CDM                           | $V_{CDM}$ | _        | 1          | kV   |            |

<sup>1)</sup> Not subject to production test, specified by design.

- 2) Reflow profile IPC/JEDEC J-STD-020C

- 3) ESD susceptibility HBM according to EIA/JESD 22-A 114B

Note: Stresses above the ones listed here may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Note: Integrated protection functions are designed to prevent IC destruction under fault conditions described in the data sheet. Fault conditions are considered as "outside" normal operating range. Protection functions are not designed for continuous repetitive operation.

## 4.2 Functional Range

| Pos.   | Parameter                                           | Symbol        | Limit Values |          | Unit | Conditions                                                       |  |

|--------|-----------------------------------------------------|---------------|--------------|----------|------|------------------------------------------------------------------|--|

|        |                                                     |               | Min.         | Max.     |      |                                                                  |  |

| 4.2.1  | Specified supply voltage range                      | $V_{\rm VS1}$ | 7.0          | 34       | V    | _                                                                |  |

| 4.2.2  | supply voltage range <sup>1)</sup>                  | $V_{ m VS2}$  | 5.5          | 45       | V    | V <sub>VS</sub> <7V reduced functionality                        |  |

| 4.2.3  | Quiescent current at VS                             | $I_{QVS1}$    | -            | 8        | μΑ   | $V_{VS}$ , $V_{VDH}$ =12V;<br>ENA=Low; $T_{j}$ =25°C             |  |

| 4.2.4  | Quiescent current at VS                             | $I_{QVS2}$    | _            | 10       | μА   | $V_{VS}, V_{VDH}$ <15V;<br>ENA=Low; $T_j$ ≤85°C                  |  |

| 4.2.5  | Quiescent current at VDH                            | $I_{QVDH1}$   | _            | 8        | μА   | $V_{VS}$ , $V_{VDH}$ =12V;<br>ENA=Low; $T_{j}$ =25°C             |  |

| 4.2.6  | Quiescent current at VDH                            | $I_{QVDH2}$   | _            | 10       | μА   | $V_{VS}, V_{VDH}$ <15V;<br>ENA=Low; $T_j$ ≤85°C                  |  |

| 4.2.7  | Supply current at Vs (device enabled) <sup>2)</sup> | $I_{Vs(1)}$   | _            | 22       | mA   | no switching                                                     |  |

| 4.2.8  | Supply current at Vs (device enabled)               | $I_{Vs(2)}$   | _            | 45       | mA   | $4xQ_{GS}xf_{PWM} \le 20$ mA<br>; $V_{VS} = 7.034$ V             |  |

| 4.2.9  | D.C. switch on time of output stages                | $D_{DC}$      | _            | $\infty$ | s    | -                                                                |  |

| 4.2.10 | Duty cycle Highside output stage <sup>3)</sup>      | $D_{HS}$      | 0            | 95       | %    | $f_{PWM}$ =20kHz;<br>continuous<br>operation;<br>$C_{BS}$ ≥330nF |  |

| 4.2.11 | Duty cycle Lowside output stage                     | $D_{LS}$      | 0            | 100      | %    | _                                                                |  |

<sup>1)</sup> operation above 34V limited by max. allowed power dissipation and max. ratings

Data Sheet 8 Rev 1.1, 2010-09-30

<sup>2)</sup> Current can be higher, if driver output stages are unsupplied

<sup>3)</sup> max. limit of D.C. will increase, if  $f_{PWM}$  or external gate charge of the MOSFETs is reduced

#### **General Product Characteristics**

The PWM frequency is limited by thermal constraints and the maximum duty cycle (minimum charging time of bootstrap capacitor).

Note: Within the functional range the IC operates as described in the circuit description. The electrical characteristics are specified within the conditions given in the related electrical characteristics table.

### 4.3 Thermal Resistance

Note: This thermal data was generated in accordance with JEDEC JESD51 standards. For more information, go to www.jedec.org.

| Pos.  | Parameter                         | Symbol     | Limit Values |      |      | Unit | Conditions |

|-------|-----------------------------------|------------|--------------|------|------|------|------------|

|       |                                   |            | Min.         | Тур. | Max. |      |            |

| 4.3.1 | Junction to Case <sup>1)</sup>    | $R_{thJC}$ | _            | _    | 5    | K/W  | _          |

| 4.3.2 | Junction to Ambient <sup>1)</sup> | $R_{thJA}$ | _            | 35   | _    | K/W  | 2)         |

<sup>1)</sup> Not subject to production test, specified by design.

## 4.4 Default State of Inputs

## Table 2 Default State of Inputs (if left open)

| Characteristic               | State | Remark                                            |

|------------------------------|-------|---------------------------------------------------|

| Default state of PWM and DIR | Low   | Low side MOSFETs off and Highside MOSFETs on      |

| Default state of DT          | OPEN  | maximum deadtime                                  |

| Default state of ENA         | Low   | Output stages disabled device in sleep mode       |

| Default state of SCDL        | OPEN  | Short circuit detection deactivation & warning    |

| Default state of DRVDIS      | High  | All output stages off & no error will be reported |

Data Sheet 9 Rev 1.1, 2010-09-30

<sup>2)</sup> Exposed Heatslug Package use this sentence: Specified R<sub>thJA</sub> value is according to Jedec JESD51-2,-5,-7 at natural convection on FR4 2s2p board; The Product (Chip+Package) was simulated on a 76.2 x 114.3 x 1.5 mm board with 2 inner copper layers (2 x 70µm Cu, 2 x 35µm Cu). Where applicable a thermal via array under the exposed pad contacted the first inner copper layer.

**Description and Electrical Characteristics**

## 5 Description and Electrical Characteristics

#### 5.1 MOSFET Driver

## 5.1.1 Driving MOSFET Output Stages

The TLE7181EM incorporates 2 high side and low side output stages for 4 external MOSFETs.

The 4 MOSFET output stages will be driven by the PWM/DIR interface. With the PWM/DIR interface only 2 inputs pins are necessary to drive a typical H-bridge topology for a DC-brush motor. The rotation direction of the motor can be chosen with the input pin DIR. The speed of the motor can is controlled by applying a PWM-signal at pin PWM.

The DRVDIS pin allows to switch off all 4 MOSFETs. **Table 3** provides an overview of the different states with this interface.

Table 3 PWM/DIR interface normal operation

| DRVDIS | DIR | PWM | Highside switch1 | Lowside switch1 | Highside switch2 | Lowside switch2 |

|--------|-----|-----|------------------|-----------------|------------------|-----------------|

| 0      | 0   | 0   | ON               | OFF             | ON               | OFF             |

| 0      | 0   | 1   | ON               | OFF             | OFF              | ON              |

| 0      | 1   | 0   | ON               | OFF             | ON               | OFF             |

| 0      | 1   | 1   | OFF              | ON              | ON               | OFF             |

| 1      | Х   | х   | OFF              | OFF             | OFF              | OFF             |

## 5.1.2 MOSFET Output Stages

The six push-pull MOSFET driver stages of the TLE7181EM are realized as separate floating blocks. This means that the output stage is follows the individual MOSFET source voltages and so ensuring stable MOSFET driving even in harsh electrical environment.

All 4 output stages have the same output power and thanks to the used bootstrap principle they can be switched all up to high frequencies.

Each output stage has its own short circuit detection block. For more details about short circuit detection see Chapter 5.2.2.

Data Sheet 10 Rev 1.1, 2010-09-30

#### **Description and Electrical Characteristics**

Figure 3 Block Diagram of Driver Stages including Short Circuit Detection

#### 5.1.3 Dead Time

In bridge applications it has to be assured that the external high side and low side MOSFETs are not "on" at the same time, connecting directly the battery voltage to GND. The dead time generated in the TLE7181EM can be programmed by applying an resistor between the DT pin and GND. Higher external resistor values lead to higher dead time.

A minimum dead time applied, if the DT pin is connected to GND.

The typical dead time can be calculated with the following formula:

$$t_{deadtime}[\mu s] = \frac{0.081}{0.02 + \frac{2.4}{4 + Rdt[k\Omega]}}$$

If an exact dead time of the bridge is needed, the use of the  $\mu C$  PWM generation unit is recommended.

#### 5.1.4 Bootstrap Principle

The TLE7181EM provides a bootstrap based supply for its high side output stages.

The bootstrap capacitors are charged by switching on the external low side MOSFETs, connecting the bootstrap capacitor to GND. Under this condition the bootstrap capacitor will be charged from the VREG capacitor via the integrated bootstrap diode. If the low side MOSFET is switched off and the high side MOSFET is switched on, the bootstrap capacitor will float together with the SHx voltage to the supply voltage of the bridge. Under this condition the supply current of the high side output stage will discharge the bootstrap capacitor. This current is specified. The size of the capacitor together with this current will determine how long the high side MOSFET can be kept on without recharging the bootstrap capacitor.

Data Sheet 11 Rev 1.1, 2010-09-30

**Description and Electrical Characteristics**

## 5.1.5 100% D.C. charge pumps

100% D.C. charge pumps are implemented for each high side output stage. Therefore the high side output stages can be switch on for an unlimited time. These integrated charge pumps can handle leakage currents which will be caused by external MOSFETs and the TLE7181EM itself. They are not strong enough to drive a 99% duty cycle for a longer time. the charge pumps are running when the driver is not in sleep mode and assure that the bootstrap capacitors are charged as long as the user does not apply critical duty cycle for a longer time.

## 5.1.6 Reverse polarity protection of motor bridge

The TLE7181EM provides an additional RPP pin to protect motor bridge for reverse polarity. This RPP pin can drive an additional external N-channel power MOSFET designed in between battery and the motor bridge. The RPP pin is internally supplied by the two integrated 100% D.C. charge pumps. They are especially designed to handle additional current which is needed to drive a the gate charge of the reverse polarity MOSFET. The guarantied output current of the charge pumps is specified.

#### 5.1.7 Sleep mode

If ENA pin is set to low, the ERR flag will be set to low and the output stages will be switched off.

After ENA pin is kept low for  $t_{LOM}$  the sleep mode of the Driver IC will be activated.

In Sleep mode the complete chip is deactivated. This means the internal supply structure of the TLE7181EM will be switched off. This mode is designed for lowest current consumption from the power net of the car. The passive clamping is active. For details see the description of passive clamping, see **Chapter 5.2.9**.

The TLE7181EM will wake up, if ENA is set to high. The ENA pin is 45V compatible, so ENA can be directly be connected to the ignition key signal KL15.

### 5.1.8 Wake up

A special start up procedure is implemented into the TLE7181EM to guarantee charged bootstrap capacitors.

This start up procedure is automatically performed before normal H-bridge motor control with PWM/DIR is possible.

If the ENA pin is set to high, the VREG voltage starts to increase. As soon as the under voltage threshold VREG\_UV is reached, both low side output stages will be switched on for a short period of time for fast charging of the bootstrap capacitors. When the bootstrap capacitor voltage is high enough the auto start up procedure is completed and the low side MOSFETs will be driven according the input pattern.

During wake up procedure the ERR signal is set to low. It will be set to high, if no error occurs at the TLE7181EM and auto start procedure is completed.

To assure that the driver is finally in the normal operation mode, it is recommended to set the DRVDIS pin to high for minimum 1us. After that procedure the output stages can be driven by PWM/DIR interface.

Data Sheet 12 Rev 1.1, 2010-09-30

**Description and Electrical Characteristics**

## **5.1.9** Electrical Characteristics

### **Electrical Characteristics MOSFET Drivers**

$V_{\rm S}$  = 7.0 to 34V,  $T_{\rm j}$  = -40 to +150°C all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Pos.   | Parameter                                           | Symbol      | Limit Values |                      |      | Unit | Conditions                                                                                                                                                                |

|--------|-----------------------------------------------------|-------------|--------------|----------------------|------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        |                                                     |             | Min.         | Тур.                 | Max. |      |                                                                                                                                                                           |

| Contro | inputs                                              |             |              |                      |      |      |                                                                                                                                                                           |

| 5.1.1  | Low level input voltage of PWM; DIR                 | $V_{I\_LL}$ | _            | _                    | 1.0  | V    | _                                                                                                                                                                         |

| 5.1.2  | High level input voltage of PWM; DIR                | $V_{I\_HL}$ | 2.0          | -                    | _    | V    | -                                                                                                                                                                         |

| 5.1.3  | Input hysteresis of PWM; DIR                        | $d_{VI}$    | 100          | 200                  | _    | mV   | _                                                                                                                                                                         |

| 5.1.4  | PWM; DIR pull-down resistors to GND                 | $R_{IL}$    | 20           | _                    | 50   | kΩ   | -                                                                                                                                                                         |

| 5.1.5  | Low level input voltage of ENA                      | $V_{E\_LL}$ | _            | _                    | 0.75 | V    | _                                                                                                                                                                         |

| 5.1.6  | High level input voltage of ENA                     | $V_{E\_HL}$ | 2.1          | _                    | _    | V    | _                                                                                                                                                                         |

| 5.1.7  | Input hysteresis of ENA                             | $d_{VE}$    | 50           | 200                  | _    | mV   | -                                                                                                                                                                         |

| 5.1.8  | ENA pull-down resistor to GND                       | $R_{IL}$    | 70           | 125                  | 200  | kΩ   | _                                                                                                                                                                         |

| 5.1.9  | Low level input voltage of DRVDIS                   | $V_{D\_LL}$ | _            | _                    | 1.0  | V    | _                                                                                                                                                                         |

| 5.1.10 | High level input voltage of DRVDIS                  | $V_{D\_HL}$ | 2.0          | -                    | _    | V    | _                                                                                                                                                                         |

| 5.1.11 | Input hysteresis of DRVDIS                          | $d_{VD}$    | 100          | 200                  | _    | mV   | _                                                                                                                                                                         |

| 5.1.12 | DRVDIS pull-up resistor to internal supply          | $R_{DH}$    | 30           | 50                   | 80   | kΩ   | -                                                                                                                                                                         |

| MOSFE  | T driver output                                     |             |              |                      |      |      | <u> </u>                                                                                                                                                                  |

| 5.1.13 | Output source resistance                            | $R_{Sou}$   | 2            | _                    | 13.5 | Ω    | $I_{Load}$ =-20mA                                                                                                                                                         |

| 5.1.14 | Output sink resistance                              | $R_{Sink}$  | 2            | _                    | 9.0  | Ω    | $I_{Load}$ =20mA                                                                                                                                                          |

| 5.1.15 | High level output voltage Gxx vs. Sxx               | $V_{Gxx1}$  | -            | 11                   | 15   | V    | 13.5 $V \le V_{VS} \le 34V$ ;<br>$I_{Load} = 0 \text{mA}$                                                                                                                 |

| 5.1.16 | High level output voltage Gxx vs. Sxx               | $V_{Gxx2}$  | _            | 11                   | 13.5 | V    | $\begin{array}{l} \text{13.5V} \leq V_{\text{VS}} \leq 34\text{V}; \\ C_{\text{Load}} = 20\text{nF}; \\ \text{D.C.} = 50\%; \\ f_{\text{PWM}} = 20\text{kHz} \end{array}$ |

| 5.1.17 | High level output voltage GHx vs. SHx <sup>1)</sup> | $V_{GHx3}$  | _            | V <sub>VS</sub> -1.5 | _    | V    | $7.0\mathrm{V}{<}V_{\mathrm{VS}}{<}13.5\mathrm{V}$ $C_{\mathrm{Load}}{=}20\mathrm{nF};$ D.C.=50%; $f_{\mathrm{PWM}}{=}20\mathrm{kHz}$                                     |

| 5.1.18 | High level output voltage GLx vs. GND <sup>1)</sup> | $V_{GLx3}$  | _            | V <sub>VS</sub> -0.5 | -    | V    | $7.0 \text{V} < V_{\text{VS}} < 13.5 \text{V} \\ C_{\text{Load}} = 20 \text{nF}; \\ f_{\text{PWM}} = 20 \text{kHz \&} \\ \text{D.C.} = 50\%; \\ \text{or D.C} = 100\%$    |

Data Sheet 13 Rev 1.1, 2010-09-30

## **Description and Electrical Characteristics**

## **Electrical Characteristics MOSFET Drivers**

$V_{\rm S}$  = 7.0 to 34V,  $T_{\rm j}$  = -40 to +150°C all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Pos.   | Parameter                                                     | Symbol              | L    | imit Val                                                                                       | ues  | Unit | Conditions                                                                                              |  |

|--------|---------------------------------------------------------------|---------------------|------|------------------------------------------------------------------------------------------------|------|------|---------------------------------------------------------------------------------------------------------|--|

|        |                                                               |                     | Min. | Тур.                                                                                           | Max. |      |                                                                                                         |  |

| 5.1.19 | High level output voltage GHx vs. SHx <sup>1)2)</sup>         | $+V_{ m diode}$     |      | $V_{\rm VS}$ =7.0V; $C_{\rm Load}$ =20nF; D.C.=95%; $f_{\rm PWM}$ =20kHz; passive freewheeling |      |      |                                                                                                         |  |

| 5.1.20 | High level output voltage GHx vs. SHx <sup>1)</sup>           | $V_{\mathrm{GHx5}}$ | 5.0  | _                                                                                              | _    | V    | $V_{\rm VS}$ =7.0V;<br>$C_{\rm Load}$ =20nF;<br>D.C.=95%;<br>$f_{\rm PWM}$ =20kHz                       |  |

| 5.1.21 | High level output voltage GLx vs. SLx <sup>1)</sup>           | $V_{\rm GLx5}$      | 6.0  | _                                                                                              | _    | V    | $V_{\rm VS} = 7.0 \rm V;$ $C_{\rm Load} = 20 \rm nF;$ $D.C. = 95\%;$ $f_{\rm PWM} = 20 \rm kHz$         |  |

| 5.1.22 | High level output voltage GHx vs. SHx <sup>1)</sup>           | $V_{GHx5}$          | 10   | _                                                                                              | -    | V    | $7.0 \text{V} \leq V_{\text{VS}} \leq 13.5 \text{V};$ $C_{\text{Load}} = 20 \text{nF};$ D.C.=100%       |  |

| 5.1.23 | High level output voltage GLx vs. SLx <sup>1)</sup>           | $V_{\rm GLx5}$      | 6.5  | _                                                                                              | -    | V    | $V_{\rm VS}$ =7.0V; $C_{\rm Load}$ =20nF; D.C.=100%                                                     |  |

| 5.1.24 | Rise time                                                     | $t_{\rm rise}$      | _    | 250                                                                                            | _    | ns   | $C_{Load}$ =11nF;                                                                                       |  |

| 5.1.25 | Fall time                                                     | $t_{fall}$          | _    | 200                                                                                            | _    | ns   | $R_{\text{Load}}$ =1 $\Omega$ ;<br>$V_{\text{VS}}$ =7 $V$ ;<br>20-80%                                   |  |

| 5.1.26 | High level output voltage (in passive clamping) <sup>1)</sup> | $V_{GxxUV}$         | _    | _                                                                                              | 1.2  | V    | Sleep mode or VS_UVLO                                                                                   |  |

| 5.1.27 | Pull-down resistor at BHx to GND                              | $R_{BHUVx}$         | _    | _                                                                                              | 85   | kΩ   | Sleep mode or VS_UVLO                                                                                   |  |

| 5.1.28 | Pull-down resistor at VREG to GND                             | $R_{VRUV}$          | _    | _                                                                                              | 30   | kΩ   | Sleep mode or<br>VS_UVLO                                                                                |  |

| 5.1.29 | Bias current into BHx                                         | $I_{BHx}$           | _    | _                                                                                              | 150  | μΑ   | $V_{\rm CBS}$ >5V; no switching                                                                         |  |

| 5.1.30 | Bias current out of SHx                                       | $I_{SHx}$           | _    | 40                                                                                             | _    | μΑ   | $V_{\rm SHx} = V_{\rm SL};$ ENA=HIGH; affected highside output stage static on; $V_{\rm CBS} > 5 \rm V$ |  |

| 5.1.31 | Bias current out of SL                                        | $I_{SL}$            | _    | _                                                                                              | 1.4  | mA   | $0 \leq V_{\rm SHx} \leq V_{\rm VS} + 1 \rm V;$ ENA=HIGH; no switching; $V_{\rm CBS} > 5 \rm V$         |  |

Data Sheet 14 Rev 1.1, 2010-09-30

### **Description and Electrical Characteristics**

## **Electrical Characteristics MOSFET Drivers**

$V_{\rm S}$  = 7.0 to 34V,  $T_{\rm j}$  = -40 to +150°C all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Pos.    | Parameter                                                                  | Symbol               |                                    | Limit Val                            | ues                                | Unit     | Conditions                                                                               |  |

|---------|----------------------------------------------------------------------------|----------------------|------------------------------------|--------------------------------------|------------------------------------|----------|------------------------------------------------------------------------------------------|--|

|         |                                                                            |                      | Min.                               | Min. Typ. Max.                       |                                    |          |                                                                                          |  |

| Dead ti | me & input propagation delay time                                          | es                   | 1                                  | +                                    |                                    | <u> </u> |                                                                                          |  |

| 5.1.32  | Programmable internal dead time                                            | $t_{DT}$             | 0.08<br>0.25<br>0.82<br>1.0<br>2.0 | 0.13<br>0.42<br>1,21<br>1.88<br>3.62 | 0.20<br>0.57<br>1.65<br>2.7<br>5.6 | μs       | $R_{DT}$ =0kΩ<br>$R_{DT}$ =10kΩ<br>$R_{DT}$ =47kΩ<br>$R_{DT}$ =100kΩ<br>$R_{DT}$ =1000kΩ |  |

| 5.1.33  | Max. internal dead time                                                    | $t_{DT\_MAX}$        | 2.3                                | 4.0                                  | 6.4                                | μs       | DT pin open                                                                              |  |

| 5.1.34  | Dead time deviation between channels                                       | $d_{	ext{tDT1}}$     | -20<br>-15                         | -                                    | 20<br>15                           | %        | $R_{\rm DT} \leq 47 \text{k}\Omega$                                                      |  |

| 5.1.35  | Dead time deviation between channels LSoff -> HS on                        | $d_{tDTH1}$          | -14<br>-12                         | _                                    | 14                                 | %        | $R_{\rm DT} \leq 47 \text{k}\Omega$                                                      |  |

| 5.1.36  | Dead time deviation between channels HSoff -> LS on                        | $d_{tDTL1}$          | -14<br>-12                         | _                                    | 14                                 | %        | $ R_{\rm DT} \le 47 \text{k}\Omega$                                                      |  |

| 5.1.37  | Input propagation time (low on)                                            | $t_{P(ILN)}$         | 0                                  | 100                                  | 200                                | ns       | $C_{\text{Load}}$ =10nF;                                                                 |  |

| 5.1.38  | Input propagation time (low off)                                           | $t_{P(ILF)}$         | 0                                  | 100                                  | 200                                | ns       | $R_{\text{Load}} = 1\Omega$                                                              |  |

| 5.1.39  | Input propagation time (high on)                                           | $t_{P(IHN)}$         | 0                                  | 100                                  | 200                                | ns       |                                                                                          |  |

| 5.1.40  | Input propagation time (high off)                                          | $t_{P(IHF)}$         | 0                                  | 100                                  | 200                                | ns       | 7                                                                                        |  |

| 5.1.41  | Absolute input propagation time difference between above propagation times | $t_{P(diff)}$        | _                                  | 50                                   | 100                                | ns       |                                                                                          |  |

| VREG    | 12 2 2                                                                     |                      |                                    |                                      |                                    |          |                                                                                          |  |

| 5.1.42  | VREG output voltage                                                        | $V_{VREG}$           | 11                                 | 12.5                                 | 14                                 | V        | $V_{ m VS} \ge$ 13.5V; $I_{ m Load}$ =-35mA                                              |  |

| 5.1.43  | VREG over current limitation                                               | $I_{VREGOCL}$        | 100                                | _                                    | 500                                | mA       | _3)                                                                                      |  |

| 5.1.44  | Voltage drop between Vs and VREG                                           | $V_{ m VsVREG}$      | _                                  | _                                    | 0.5                                | V        | $V_{\rm VS}{\ge}7{\rm V};$ $I_{\rm Load}$ =-35mA; Ron operation                          |  |

| 100% D  | D.C. charge pump                                                           |                      |                                    | 1                                    |                                    | 1        | ,                                                                                        |  |

| 5.1.45  | Charge pump frequency <sup>1)</sup>                                        | $f_{\sf CP}$         | -                                  | 21                                   | _                                  | MHz      | _                                                                                        |  |

| Motor b | oridge reverse polarity protection                                         | output               |                                    | <del>-</del>                         | <del>.</del>                       | -        |                                                                                          |  |

| 5.1.46  | High level output voltage RPP vs. VS                                       | $V_{RPP1}$           | _                                  | 11                                   | 15                                 | V        | I <sub>Load</sub> =0μA                                                                   |  |

| 5.1.47  | High level output voltage RPP vs. VS                                       | $V_{RPP2}$           | _                                  | 11                                   | 12.5                               | V        | I <sub>Load</sub> ≥-30μA                                                                 |  |

| 5.1.48  | D.C. output current at RPP                                                 | $I_{RPP1}$           | _                                  | -110                                 | -150                               | μΑ       | $V_{\mathrm{RPP}} \ge 10 \mathrm{V};$ Lowside on                                         |  |

| 5.1.49  | Rise time <sup>1)</sup>                                                    | $t_{RPPrise}$        | _                                  | 1                                    | 2                                  | ms       | $C_{LOAD}$ =10nF                                                                         |  |

| 5.1.50  | Rise time <sup>1)</sup>                                                    | t <sub>RPPrise</sub> | _                                  | 10                                   | 20                                 | μs       | $C_{LOAD}$ =100pF                                                                        |  |

|         |                                                                            |                      |                                    |                                      |                                    |          |                                                                                          |  |

Data Sheet 15 Rev 1.1, 2010-09-30

#### **Description and Electrical Characteristics**

### **Electrical Characteristics MOSFET Drivers**

$V_{\rm S}$  = 7.0 to 34V,  $T_{\rm j}$  = -40 to +150°C all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Pos.   | Parameter                                                            | Symbol                |      | Limit Val | ues  | Unit | Conditions                                                |

|--------|----------------------------------------------------------------------|-----------------------|------|-----------|------|------|-----------------------------------------------------------|

|        |                                                                      |                       | Min. | Тур.      | Max. |      |                                                           |

| ENA ar | nd Low quiescent current mode                                        | 1                     |      |           |      |      |                                                           |

| 5.1.51 | ENA propagation time to output stages switched off                   | t <sub>PENA_H-L</sub> | _    | 2.0       | 3.0  | μs   | -                                                         |

| 5.1.52 | Low time of ENA signal without clearing error register               | $t_{RST0}$            | _    | _         | 1.2  | μs   | _                                                         |

| 5.1.53 | High time of ENA signal after ENA rising edge for error logic active | $t_{RST1}$            | 4    | 5.75      | 7    | μs   | -                                                         |

| 5.1.54 | go to sleep time                                                     | $t_{\sf sleep}$       | 310  | 415       | 540  | μs   | _                                                         |

| 5.1.55 | wake up time                                                         | $t_{ m wake}$         | _    | 50        | 100  | μs   | $C_{\mathrm{REG}}$ =2.2 $\mu$ F; $C_{\mathrm{BS}}$ =330nF |

<sup>1)</sup> Not subject to production test, specified by design.

Data Sheet 16 Rev 1.1, 2010-09-30

<sup>2)</sup>  $V_{\mathrm{diode}}$  is the bulk diode of the external low side MOSFET

<sup>3)</sup> normally no error flag; Error flag might by triggered by under voltage VREG caused by very high load current

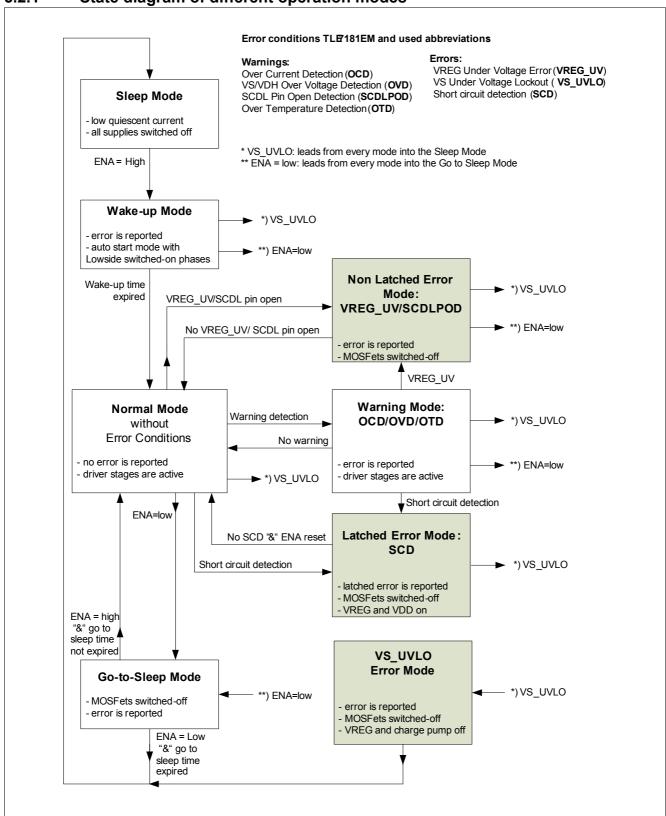

## 5.2 Protection and Diagnostic Functions

### 5.2.1 State diagram of different operation modes

Figure 4 State diagramTLE7181EM

Data Sheet 17 Rev 1.1, 2010-09-30

#### 5.2.2 Short Circuit Protection

The TLE7181EM provides a short circuit protection for the external MOSFETs by monitoring the drain-source voltage of the external MOSFETs.

This monitoring of the short circuit detection for a certain external MOSFET is active as soon as the corresponding driver output stage is set to "on" and the dead time and the blanking time are expired.

The blanking time starts when the dead time has expired and assures that the switch on process of the MOSFET is not taken into account. It is recommended to keep the switching times of the MOSFETs below the blanking time.

The short circuit detection level is adjustable in an analog way by the voltage setting at the SCDL pin. There is a 1:1 translation between the voltage applied to the SCDL pin and the drain-source voltage limit. E.g. to trigger the SCD circuit at 1 V drain-source voltage, the SCDL pin must be set to 1 V. The drain-source voltage limit can be chosen between 0.2 ... 2 V.

If after the expiration of the blanking time the drain source voltage of the observed MOSFET is still higher then the SCDL level, the SCD filter time  $t_{\rm SCP}$  starts to run. A capacitor is charged with a current. If the capacitor voltage reaches a specific level (filter time  $t_{\rm SCP}$ ), the error signal is set and the IC goes into SCDL Error Mode. If the SCD condition is removed before the SC is detected, the capacitor is discharged with the same current. The discharging of the capacitor happens as well when the MOSFET is switched off. It has to be considered that the high side and the low side output of one phase are working with the same capacitor.

### 5.2.3 SCDL Pin Open Detection

An integrated structure at the SCDL pin assures that in case of an open pin the SCDL voltage is pulled to a medium voltage level. The external MOSFETs are actively switched off and an ERR flag is set. This error is self-clearing.

### 5.2.4 Vs and VDH Over Voltage Warning

The TLE7181EM has an integrated over voltage warning to minimize risk of destruction of the IC at high supply voltages caused by violation of the maximum ratings. For the over voltage warning the voltage is observed at the pin VS and VDH. If the voltage level has reached, the fixed over voltage threshold  $V_{\rm OVW}$  for the filter time  $t_{\rm OV}$ , a warning at ERR pin is set and TLE7181EM will go in normal operation with warning.

The over voltage warning is self clearing. If the voltage at pin VS and VDH returns into the specified voltage range, the Error register will be cleared and TLE7181EM returns to normal operation mode.

It is the decision of the user, if and how to react on the over voltage warning.

## 5.2.5 VS Under Voltage Shutdown

The TLE7181EM has an integrated VS Under Voltage Shutdown, to assure that the behavior of the complete IC is predictable in all supply voltage ranges. As soon as the under voltage threshold  $V_{\rm UVVR}$  is reached for a specified filter time the TLE7181EM is in VS\_UVLO error mode. The error signal will be set and output stages, voltage regulator and charge pump will be switched off so the IC will go into sleep mode. An enable is necessary to restart the TLE7181EM.

### 5.2.6 VREG Under Voltage Warning

The TLE7181EM has an integrated under voltage warning detection at VREG. If the supply voltage at VREG reaches the VREG under voltage threshold  $V_{\rm UVVR}$ , a warning at ERR pin is set and the TLE7181EM will go into VREG error mode. In case of VREG error mode all output stages will actively switched off to prevent low gate source voltages at the power MOSFETs causing high RDSon. If supply voltage at the VREG pin recovers; the error flag will be cleared and the TLE7181EM will return in normal operation mode.

Data Sheet 18 Rev 1.1, 2010-09-30

## 5.2.7 Over Temperature Warning

The TLE7181EM provides an integrated digital over temperature warning to minimize risk of destruction of the IC at high temperature. The temperature will be detected by a embedded sensor. During over temperature warning the ERR signal is set and the TLE7181EM is in normal operation mode with warning.

The over temperature warning is self clearing. So if temperature is below  $T_{j(PW)}$ - $dT_{j(OW)}$ , the warning will be cleared and TLE7181EM returns to normal operation mode.

It is the decision of the user to react on the over temperature warning.

## 5.2.8 Over Current Warning

The TLE7181EM offers an integrated over current detection. The output signal of the current sense OpAmp will be monitored. If the output signal reaches the specified voltage threshold  $V_{\rm OCTH}$  for a certain time, over current will be detected. After the comparator the filter time  $t_{\rm OC}$  is implemented to avoid false triggering caused by overswing of the current sense signal. The ERR pin will be set to low and the TLE7181EM will go into normal operation mode with warning.

The error signal disappears as soon as the current decreases below the over current threshold  $V_{\rm OCTH}$ . The error signal disappears as well when the current commutates from the low side MOSFET to the associated high side MOSFET and is no longer flowing over the shunt resistor.

It is the decision of the user to react on the over current signal by modifying input patterns.

## 5.2.9 Passive Gxx Clamping

If VS Under Voltage shutdown is detected or the device is in Sleep Mode, a passive clamping is active as long as the voltage at VS or VDH is higher than 3V. Even below 3V it is assured that the MOSFET driver stage will not switch on the MOSFET actively.

The passive clamping means that the BHx and the VREG pin are pulled to GND with specified pull down resistors. Together with the intrinsic diode of the push stage of the output stages which connect the gate output to BHx respectively VREG, this assures that the gate of the external MOSFETs are not floating undefined.

### 5.2.10 ERR Pin

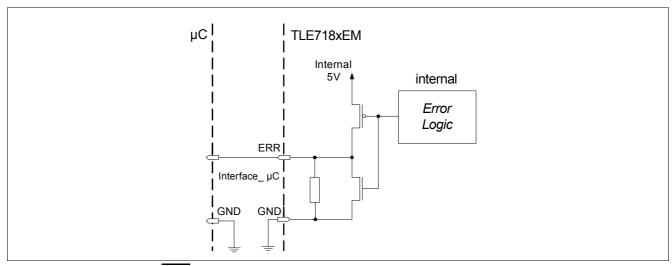

The TLE7181EM has a status pin to provide diagnostic feedback to the  $\mu$ C. The logical output of this pin is a push pull output stage with an integrated pull-down resistor to GND (see **Figure 5**).

#### Reset of error registers and Disable

The TLE7181EM can be reset by the enable pin ENA. If the ENA pin is pulled to low for a specified minimum time, the error registers are cleared. ERR output is still set to low. After the next rising edge at ENA pin ERR pin will be set to high and no error condition is applied.

Data Sheet 19 Rev 1.1, 2010-09-30

Figure 5 Structure of ERR output

Table 4 Overview of error condition

| ERR  | Driver conditions                  | Driver action                             | Restart                                              |  |  |

|------|------------------------------------|-------------------------------------------|------------------------------------------------------|--|--|

| High | no errors                          | Fully functional                          | _                                                    |  |  |

| Low  | Over temperature                   | Warning only                              | Self clearing                                        |  |  |

| Low  | Over voltage VS/VDH                | Warning only                              | Self clearing                                        |  |  |

| Low  | Over current OPAMP                 | Warning only                              | Self clearing                                        |  |  |

| Low  | Under voltage error VREG           | All MOSFETs actively switched off         | Self clearing                                        |  |  |

| Low  | Under voltage shutdown based on VS | MOSFET, charge pump,<br>Vreg switched off | Self clearing restart when enable high <sup>1)</sup> |  |  |

| Low  | SCDL open pin                      | All MOSFETs actively switched off         | Self clearing                                        |  |  |

| Low  | Short circuit detection            | All MOSFETs actively switched off         | Reset at ENA needed                                  |  |  |

| Low  | Go to sleep mode                   | All MOSFETs actively switched off         | immediate restart when ENA goes high                 |  |  |

| Low  | Wake up mode                       | start up –                                |                                                      |  |  |

<sup>1)</sup> When SC detected, reset with ENA necessary

Table 5 Prioritization of Errors

| Priority | Errors and Warnings                                                                                                                   |  |  |  |

|----------|---------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 0        | Under voltage lockout at Vs (VS_UVLO)                                                                                                 |  |  |  |

| 1        | Short circuit detection error (SCD) SCDL pin open warning (SCDLPOD)                                                                   |  |  |  |

| 2        | Under voltage detection VREG (UV_VREG) Over voltage detection warning (OVD) Over temperature warning (OTD) Over current warning (OCD) |  |  |  |

Data Sheet 20 Rev 1.1, 2010-09-30

## 5.2.11 Electrical Characteristics

### **Electrical Characteristics - Protection and diagnostic functions**

$V_{\rm S}$  = 7.0 to 34V,  $T_{\rm j}$  = -40 to +150°C, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Pos.    | Parameter                                                 | Symbol                                  |      | Limit Val | ues  | Unit | Conditions                                 |  |

|---------|-----------------------------------------------------------|-----------------------------------------|------|-----------|------|------|--------------------------------------------|--|

|         |                                                           |                                         | Min. | Тур.      | Max. |      |                                            |  |

| Short c | ircuit protection                                         | 1                                       |      | 1         |      |      |                                            |  |

| 5.2.1   | Short circuit protection detection level input range      | $V_{SCDL}$                              | 0.2  | _         | 2.0  | V    | programmed by SCDL pin                     |  |

| 5.2.2   | Short circuit protection detection accuracy               | $A_{SCP1}$                              | -50  | _         | +50  | %    | 0.2V≤ V <sub>SCDL</sub> ≤0.3               |  |

| 5.2.3   | Short circuit protection detection accuracy               | $A_{SCP2}$                              | -30  | _         | +30  | %    | $0.3$ V $\leq V_{\text{SCDL}} \leq 1.2$    |  |

| 5.2.4   | Short circuit protection detection accuracy               | $A_{SCP3}$                              | -10  | _         | +10  | %    | 1.2V≤ V <sub>SCDL</sub> ≤2.0               |  |

| 5.2.5   | Filter time of short circuit protection                   | $t_{SCP(off)}$                          | 2.5  | 3.5       | 4.5  | μs   | _                                          |  |

| 5.2.6   | Filter time and blanking time of short circuit protection | $t_{SCPBT}$                             | 4    | 6         | 8    | μs   | _                                          |  |

| 5.2.7   | Internal pull-up resistor SCDL to 3V                      | $R_{SCDL}$                              | 180  | 300       | 475  | kΩ   | _                                          |  |

| 5.2.8   | SCDL open pin detection level                             | $V_{SCPOP}$                             | 2.1  | _         | 3.2  | V    | _                                          |  |

| 5.2.9   | Filter time of SCDL open pin detection                    | $t_{SCPOP}$                             | 1.5  | 2.5       | 3.5  | μs   | _                                          |  |

| 5.2.10  | SCDL open pin detection level hysteresis <sup>1)</sup>    | $V_{SCOPH}$                             | _    | 0.3       | -    | V    | _                                          |  |

| Over- a | nd under voltage monitoring                               |                                         |      | •         | •    | •    |                                            |  |

| 5.2.11  | Over voltage warning at Vs and/or VDH                     | $V_{ovw}$                               | 34.5 | 36.5      | 38.5 | V    | $V_{ m VS}$ and/or $V_{ m VDH}$ increasing |  |

| 5.2.12  | Over voltage warning hysteresis for Vs and/or VDH         | $V_{OVWhys}$                            | 2.1  | 3.1       | 4.1  | V    | _                                          |  |

| 5.2.13  | Over voltage warning filter time for Vs and/or VDH        | t <sub>OV</sub>                         | 13   | 19        | 25   | μs   | _                                          |  |

| 5.2.14  | Under voltage shutdown at Vs                              | $V_{UVVR}$                              | 4.5  | 5.0       | 5.5  | V    | $V_{ m VS}$ decreasing                     |  |

| 5.2.15  | Under voltage shutdown filter time for VS <sup>1)</sup>   | $t_{\sf UVLO}$                          | _    | 20        | _    | μs   | -                                          |  |

| 5.2.16  | Under voltage warning at VREG                             | $V_{UVVR}$                              | 5.5  | 6.0       | 6.5  | V    | $V_{ m VS}$ decreasing                     |  |

| 5.2.17  | Under voltage diagnosis filter time for VREG              | $t_{\sf UVVR}$                          | 10   | _         | 30   | μs   | _                                          |  |

| 5.2.18  | Under voltage hysteresis at VREG                          | $V_{\rm UWRhys}$                        | _    | 0.5       | _    | V    | _                                          |  |

| Temper  | rature monitoring                                         | , , , , , , , , , , , , , , , , , , , , |      | 1         |      |      |                                            |  |

| 5.2.19  | Over temperature warning                                  | $T_{j(PW)}$                             | 160  | 170       | 180  | °C   | _                                          |  |

| 5.2.20  | Hysteresis for over temperature warning                   | $dT_{\rm j(OW)}$                        | 10   | _         | 20   | °C   | -                                          |  |

| Over cu | urrent detection                                          | I.                                      | 1    | l         | I    | I    | 1                                          |  |

| 5.2.21  | Over current detection level                              | $V_{OCTH}$                              | 4.5  |           | 4.99 | V    |                                            |  |

Data Sheet 21 Rev 1.1, 2010-09-30

## Electrical Characteristics - Protection and diagnostic functions (cont'd)

$V_{\rm S}$  = 7.0 to 34V,  $T_{\rm j}$  = -40 to +150°C, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Pos.   | Parameter                               | Symbol       |      | Limit Val | ues  | Unit | Conditions       |

|--------|-----------------------------------------|--------------|------|-----------|------|------|------------------|

|        |                                         |              | Min. | Тур.      | Max. |      |                  |

| 5.2.22 | Filter time for over current detection  | $t_{\rm OC}$ | 2.3  | _         | 4.3  | μs   | _                |

| ERR pi | n <sup>2)</sup>                         |              |      |           |      |      |                  |

| 5.2.23 | ERR output voltage                      | $V_{ERR}$    | 4.6  | _         | _    | V    | $V_{VS}$ =7V;    |

| 5.2.24 | Rise time ERR (20 - 80% of internal 5V) | $t_{f(ERR)}$ | _    | _         | 3    | μs   | $C_{LOAD}$ =1nF; |

| 5.2.25 | Internal pull-down resistor ERR to GND  | $R_{f(ERR)}$ | 60   | 100       | 170  | kΩ   | _                |

<sup>1)</sup> Not subject to production test, specified by design.

Data Sheet 22 Rev 1.1, 2010-09-30

<sup>2)</sup>  $\overline{\text{ERR}}$  pin and Reset & Enable functional between  $V_{\text{VS}}$ =6 ... 7V, but characteristics might be out of specified range

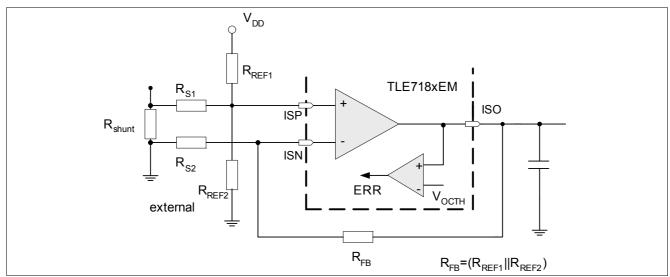

## 5.3 Shunt Signal Conditioning

The TLE7181EM incorporates a fast and precise operational amplifier for conditioning and amplification of the current sense shunt signal. The gain of the OpAmp is adjustable by external resistors within a range higher than 5. The usage of higher gains in the application might be limited by required settling time and band width.

It is recommended to apply a small offset to the OpAmp, to avoid operation in the lower rail at low currents.

The output of the OpAmp ISO is not short-circuit proof.

Figure 6 Shunt Signal Conditioning Block Diagram and Over Current Limitation

Over current warning see Chapter 5.2.8.

#### **5.3.1** Electrical Characteristics

#### **Electrical Characteristics - Current sense signal conditioning**

$V_{\rm S}$  = 7.0 to 36V,  $T_{\rm j}$  = -40 to +150°C, gain = 5 to 75, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Pos.  | Parameter                                                                | Symbol       | Limit Values |      |      | Unit | Conditions                                                          |  |

|-------|--------------------------------------------------------------------------|--------------|--------------|------|------|------|---------------------------------------------------------------------|--|

|       |                                                                          |              | Min.         | Тур. | Max. |      |                                                                     |  |

| 5.3.1 | Series resistors                                                         | $R_{S}$      | 100          | 500  | 1000 | Ω    | _                                                                   |  |

| 5.3.2 | Feedback resistor Limited by the output voltage dynamic range            | $R_{fb}$     | 2000         | 7500 | -    | Ω    | -                                                                   |  |

| 5.3.3 | Resistor ratio (gain ratio)                                              | $R_{fb/RS}$  | 5            | _    | _    | _    | _                                                                   |  |

| 5.3.4 | Steady state differential input voltage range across VIN                 | $V_{IN(ss)}$ | -400         | _    | 400  | mV   | _                                                                   |  |

| 5.3.5 | Input differential voltage (ISP - ISN)                                   | $V_{IDR}$    | -800         | _    | 800  | mV   | _                                                                   |  |

| 5.3.6 | Input voltage (Both Inputs - GND)<br>(ISP - GND) or (ISN -GND)           | $V_{LL}$     | -800         | _    | 2000 | mV   | _                                                                   |  |

| 5.3.7 | Input offset voltage of the I-DC link OpAmp, including temperature drift | $V_{IO}$     | _            | -    | +/-2 | mV   | $R_{\rm S}$ =500 $\Omega$ ; $V_{\rm CM}$ =0V; $V_{\rm ISO}$ =1.65V; |  |

| 5.3.8 | Input bias current (ISN,ISP to GND)                                      | $I_{IB}$     | -300         | _    | _    | μA   | $V_{\rm CM}$ =0V; $V_{\rm ISO}$ =open                               |  |

| 5.3.9 | Low level output voltage of ISO                                          | $V_{OL}$     | -0.1         | _    | 0.2  | V    | $I_{OH}$ =3mA                                                       |  |

Data Sheet 23 Rev 1.1, 2010-09-30

## Electrical Characteristics - Current sense signal conditioning (cont'd)

$V_{\rm S}$  = 7.0 to 36V,  $T_{\rm j}$  = -40 to +150°C, gain = 5 to 75, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Pos.   | Parameter                                                                                                                 | Symbol            | Limit Values |                |      | Unit | Conditions                                                                                                            |

|--------|---------------------------------------------------------------------------------------------------------------------------|-------------------|--------------|----------------|------|------|-----------------------------------------------------------------------------------------------------------------------|

|        |                                                                                                                           |                   | Min.         | Тур.           | Max. |      |                                                                                                                       |

| 5.3.10 | High level output voltage of ISO                                                                                          | $V_{OH}$          | 4.75         | _              | 5.2  | V    | $I_{OH}$ =-3mA                                                                                                        |