NMOS SINGLE-CHIP 4-BIT MICROCOMPUTER

MB88400 SERIES

NMOS SINGLE-CHIP 4-BIT MICROCOMPUTER

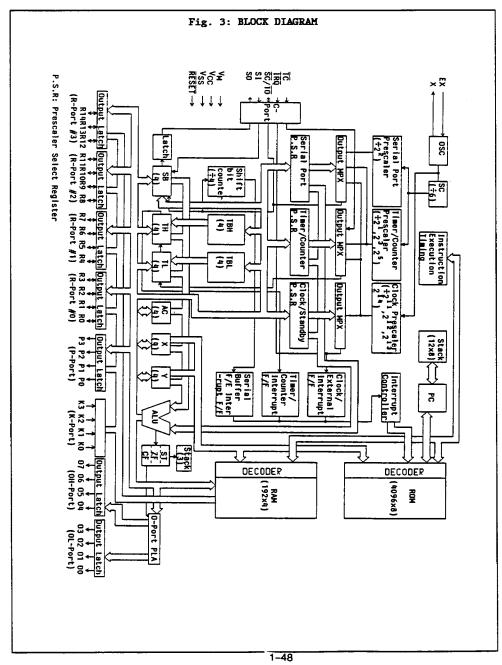

The Fujitsu MB88400H series NMOS single-chip 4-bit microcomputer family is a upgrade version of the conventional MB8840 series.

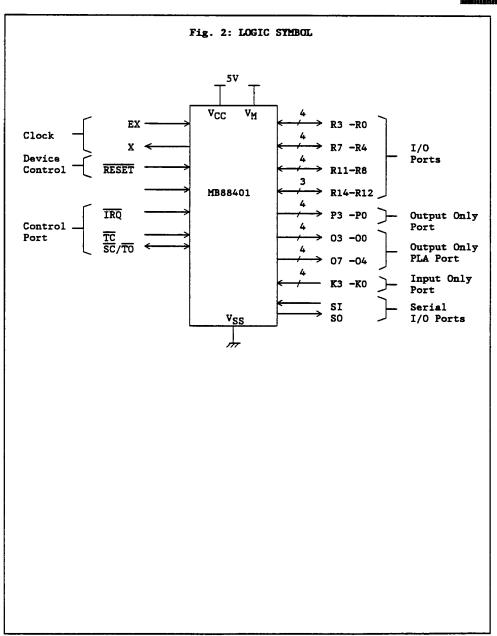

The currently available member of the MB88400 series is the MB88401 only. MB88401H contain a 4K by 8-bit mask ROM (program memory), a 192 by 4-bit static RAM (data memory), a 36 I/O lines (including a serial port), an 8-bit timer/counter, and a clock generator.

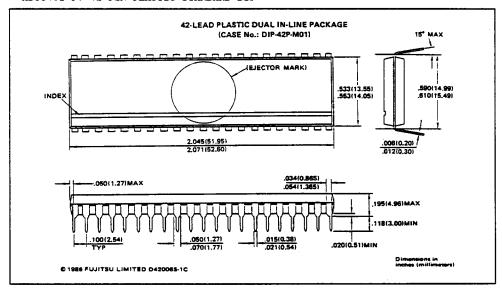

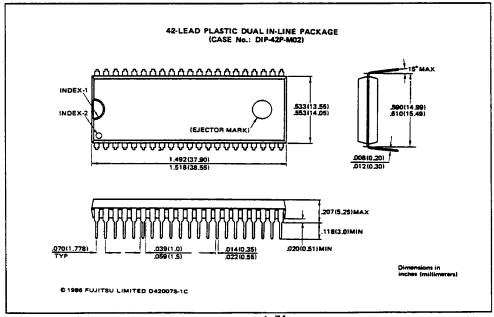

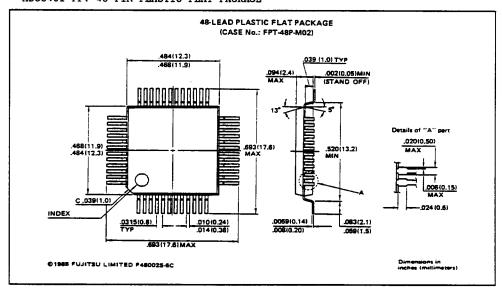

This device fabricated by the NMOS process, packaged in a 42-pin plastic standard, shrink DIP, or 48-pin plastic flat package. They operate with a single +5 V power supply and a 2 MHz clock without a prescaler (or 4.19 MHz clock with prescaler) over the temperature range of -30 °C to +70 °C.

For user's development of the MB88400 series based system, Fujitsu provides the MB88400/500 cross-assembler and host-emulator which run on the CP/M-86 or PC-DOS machines (cross-assembler also run on the Intellec series III MDS), and the MB2115 series evaluation board system, and the MB88408U piggyback EPROM evaluation devices which have external 4K x 8-bit EPROM (MBM2732A). These development tools enables users to minimize their development time and cost.

TM342-A871: January 1987

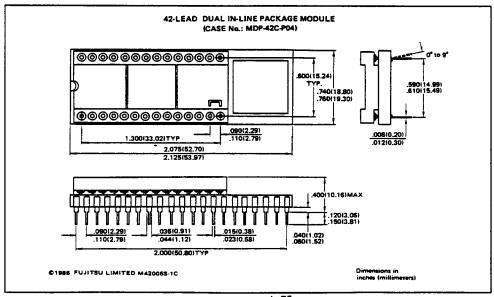

MB88401-P

42-PIN PLASTIC STANDARD DIP (DIP-42P-M01)

MB88401-PSH

42-PIN PLASTIC SHRINK DIP (DIP-42P-M02)

MB88401-PF

48-PIN PLASTIC FLAT PACK (FPT-48P-M02)

MB88408U-C

42-PIN CERAMIC MODULE (MDP-42C-P04)

This device contains circuitry to protect the inputs against damage due to high static voltages or electric fields. However, it is advised that normal precautions be taken to avoid application of any voltage higher than maximum rated voltages to this high impedance circuit.

#### **FEATURES**

- CMOS Single-chip 4-bit Microcomputer

- Program Memory:

- o 4K x 8-bit mask ROM

- Data Memory:

- o 192 x 4-bit static RAM

- 36 I/O Lines:

- o K-Port: 4-bit parallel input only port o P-Port: 4-bit parallel output only port o O-Port: 8-bit parallel output only port

- o R-Port: Three 4-bit and a 3-bit parallel or 15 individual input/output ports o C-Port: Serial I/O, interrupt input, timer/counter input, and timing output

- Three Selectable Output Port Types for O-, P-, and R-Ports with Mask Option:

- o Standard open-drain

- o Standard pull-up

- o High-current open-drain

- Two Selectable K-Port Input Level with Mask Option:

- o Standard threshold level

- o High threshold level

- On-chip Mask-programmable PLA (Programmable Logic Array) for Data Conversion at O-Port

- 8-bit Programmable Timer/Counter with Two Clock Modes:

- o Internal clock (Timer)

- o External clock (Counter)

- Software Selectable Serial I/O with 4-/8-bit Serial Buffer/Three Clock Modes:

- o Internal clock

- o External clock

- o Software clock

- On-chip Clock Generator with 2 Mask Options:

- o External crystal/ceramic resonator or external clock drive

- o External RC-network or external clock drive

- · Mask-option Divide-by-two Clock Prescaler for Expanding Clock Range

- Single Level Four Prior Source Maskable Interrupt:

- o External

- o Clock

- o Timer/counter overflow

- o Serial buffer full/empty

- · 8-nesting Levels for Subroutine Call

- Instruction Set:

- o Number of instructions : 75

- o Instruction length/cycle: 1 byte/1 cycle (82%), 2 bytes/2 cycles (17%), and

- 2 byte/3 cycle (1%)

- o Execution time : 2.86µs min. using 4.19MHz clock with prescaler

- 1-44

### FEATURES (Continued)

- On-chip Power-on Reset Circuit

- Watch-dog Timer Function with Mask Option

- Power Dissipation: o 75mA

- Power Supply:

- o Main power supply (VCC) : 4.5V to 5.5V

- o Memory back up supply (VM): o Active mode : 4.5V to 5.5Vo Standby mode: 3.0V to 5.5V

- · Operation Temperature Range:

- o TA= -30 °C to +70 °C

- Silicon Gate NMOS Technology

- Three Package Types:

- o 42-pin plastic standard DIP: Suffix -P o 42-pin plastic shrink DIP: Suffix -PSH o 48-pin plastic flat package: Suffix -PF

- Powerful Development Support:

- o CP/M-86, PC-DOS, or Intellec series III MDS cross assemblers (SM07415-A012/SMXXXXX-XXXX/SM0525-A010)

- o CP/M-86 or PC-DOS host-emulator software for monitoring evaluation board and symbolic debugging (SM07415-G022/SMXXXX-XXXX)

- o MB2115 evaluation board for software debugging

- o MB88408U NMOS piggyback EPROM evaluation

# PIN DESCRIPTION

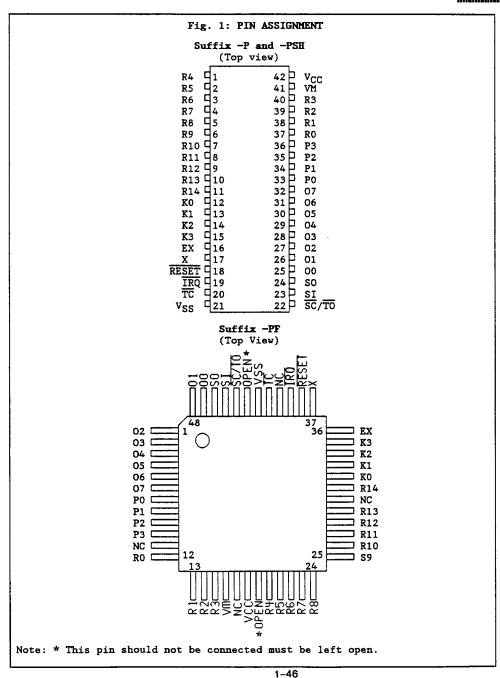

Fig. 1 and Table 1 show the pin assignment and pin description of the MB88400 series.

Table 1: PIN DESCRIPTION

| Symbol          | Pin No.    | Туре | Name & Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----------------|------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| • Power S       | upply      |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| vcc             | 42<br>(18) | -    | +5V DC main power supply pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| V <sub>M</sub>  | 41<br>(16) | -    | Data memory backup power supply.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| v <sub>ss</sub> | 21<br>(42) | -    | Ground pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| • Clock         |            |      | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

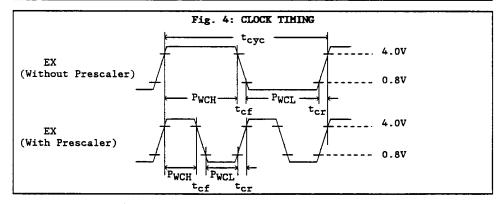

| EX              | 16<br>(36) | I    | Oscillator Input: Input to the inverting amplifier that forms the on-chip oscillator. An external crystal/ceramic resonator or RC-network is connected between the EX and X pins. Either of these two oscillation types can be selected using mask option. When an external oscillator is used, the EX pin receives the external oscillator signal.                                                                                                                                                                                                                                                                           |

|                 |            |      | This pin is a non-hysteresis input when the crystal/ceramic oscillator is selected, and a hysteresis input when the RC-network oscillator is selected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| X               | 17<br>(37) | o    | Oscillator Output: Output of the inverting amplifier that forms the on-chip oscillator, and input to the internal clock generator. An external crystal/ceramic resonator or RC-network is connected between the EX and X pins. Either of these two oscillator types can be selected using mask option. When an external oscillator is used, the X pin should be left open.                                                                                                                                                                                                                                                    |

| • Device        | Control    |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

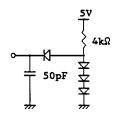

| RESET           | 18<br>(38) | I    | Reset: This pin function as an external reset input or power-on reset output.  External reset input: A reset input to the internal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                 |            |      | reset circuit. A low level on the RESET pin forcedely stops the MCU's operation, and initializes its internal state. After the RESET pin returns high, the MCU restarts execution of program from address #0. The RESET pulse must be low for at least two instruction cycles while the oscillator is stably running after power-on. This pin is a hysteresis input with an internal pullup resistor. An external capacitor from the RESET pin to the VSS pin (and the internal pull-up resistor), whose time constant should be greater than the reset time required (12 clock periods) composes the external reset circuit. |

Table 1: PIN DESCRIPTION (Continued)

| Symbol   | Pin No.   | Туре  | Name & Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------|-----------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | Control ( | لتتيا | nued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| RESET    | 18 (38)   | 1/0   | Power on reset output: A reset output from the on-chip reset control circuit. Normally this output is high during the active operation except the reset mode. The rising of the VCC voltage after power on outputs a low level on the RESET pin, and them automatically returns high 2 <sup>1*</sup> clock periods after the oscillator starts by power on.  This pin is a hysteresis input with an internal pullup resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| • C-Port | 10        | ·     | Total Demonts A markable automal intermed invest                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| IRQ      | 19 (39)   | I     | Interrupt Request: A maskable external interrupt input to the on-chip interrupt control circuit. The falling edge of the IRQ pulse sets the external interrupt request flag (IRF) in the interrupt flag register regardless of enabling or disabling the external interrupt. If the external interrupt is enabled in advance by EN instruction, the interrupt sequence starts at once. Otherwise, the IRF flag is internally held as an interrupt source. Also, the IRQ pin state (logical level), which is reflected in the external interrupt input flag (IF) regardless of enabling or disabling the external interrupt, is testable using TSTI instruction. (When IRQ = L, IF = 1; otherwise IF = 0.)                                                                                                                                                                                                                        |

|          |           |       | resistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| TC       | 20 (40)   | I     | Timer/Counter: An external count clock input to the onchip 8-bit timer/counter. The falling edge of the TC pulse increments the timer/counter by one bit, when the external count clock (counter) mode is enabled by EN instruction programming the timer/counter prescaler select register using OUT instruction (with Y = B). Also, the TC pin state (logical level), which is reflected in the timer/counter input flag (TCIF) in the timer/counter prescaler select register regardless of enabling or disabling the external count clock (counter mode, is testable by reading the prescaler select register using IN instruction (with Y = B). (When TC = L, TCIF = 1; otherwise TCIF = 0.) This pin is inactive as a count clock input when the external count clock mode is not selected or the timer/counter is disabled by DIS instruction or reset.  This pin is a hysteresis input with an internal pullup resistor. |

Table 1: PIN DESCRIPTION (Continued)

| Symbol | Pin No.    | Turns | Name & Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|--------|------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | (Continue  | Type  | Name & Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

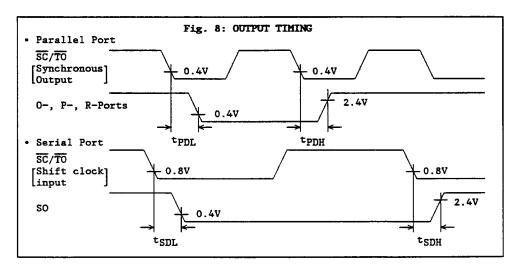

| SC/TO  | 22         | 1/0   | Shift Clock/Timing Output: One of the shift clock input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 30/10  | (44)       | -, -  | $(\overline{SC})$ , shift clock output $(\overline{SC})$ , or synchronous timing output $(\overline{TO})$ is enabled using EN instruction.                                                                                                                                                                                                                                                                                                                                                                                                    |

|        |            | I     | SC: 1) Shift clock input to the on-chip serial port:  When the external shift clock mode is enabled for the serial port, the falling edge of the external SC clock shifts the contents of the internal serial buffer one bit right (from MSB to LSB). This input is inactive when the external clock mode is not selected or the serial port disabled by DIS instruction or reset. This pin is a hysteresis input.                                                                                                                            |

|        |            |       | 2) Shift clock output from the on-chip serial port:<br>When the internal shift clock mode is enabled,<br>the internal shift clock shifts the contents of<br>the serial buffer one bit right. In this mode,<br>the internal timing signal selected is output<br>onto the SC pin for synchronization.                                                                                                                                                                                                                                           |

|        |            | 0     | TO: Synchronous timing output: When the timing output is enabled, the internal timing signal (which is generated by the on-chip state counter outputs, \$1 and \$2) is output onto the TO pin. By DIS instruction or reset, the TO pin is disabled and stops issuing the timing output.                                                                                                                                                                                                                                                       |

|        |            |       | This pin is a hysteresis input with an internal pullup resistor                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| SI     | 23<br>(45) | Ι     | Serial Data Input: Data input to the on-chip serial port. The rising edge of the external (SC) or internal shifts the data bit on the SI pin into the MSB of the serial buffer register when the serial port is enabled by EN instruction. Also, the SI pin state (logical level) is reflected in the serial data input flag (SIF) in the serial port prescaler select register regardless of enabling or disabling the serial port. Therefore, the SI pin can be sensed by reading the prescaler register using IN instruction (with Y = A). |

| SO     | 24<br>(46) | 0     | Serial Data Output: Data output with latch of the on-<br>chip serial port. The falling edge of the external (SC)<br>or internal shift clock shifts the LSB data of the<br>serial buffer register to the serial port output latch,<br>regardless of enabling or disabling to serial port. The<br>content of the output latch directly appears on the SO<br>pin. This pin is a CMOS pullup output, and is set high<br>by reset.                                                                                                                 |

Table 1: PIN DESCRIPTION (Continued)

| Pin No.<br>s<br>15-12<br>(35-32)               | Туре                                                                                                                   | Name & Function  K-Port: A 4-bit parallel non-latched input only port.  K0 is LSB. 4-bit data on K-Port is input into the                                                                                                                                                                                                                                                                                                                                                       |

|------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15-12                                          | I                                                                                                                      | KO is LSB. 4-bit data on K-Port is input into the                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                | I                                                                                                                      | KO is LSB. 4-bit data on K-Port is input into the                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                                                |                                                                                                                        | accumulator by INK instruction.                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                |                                                                                                                        | These pins are internally pullup.                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 36-33<br>(10- 7)                               | 0                                                                                                                      | P-Port: A 4-bit parallel latched output only port. PO is LSB. 4-bit data in the accumulator is output to P-Port by OUTP instruction.                                                                                                                                                                                                                                                                                                                                            |

|                                                |                                                                                                                        | Refer to Table 4 User mask options for available making option.                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 28-25<br>(2,1,48,<br>47)<br>32-39<br>(6-3)     | 0                                                                                                                      | O-Port: An 8-bit parallel latched output only port with<br>the on-chip mask programmable PLA (Programmable Logic<br>Array) for output data conversion. Depending on user's<br>PLA pattern, this port functions as a dual 4-bit<br>parallel output or an 8-bit parallel PLA output.                                                                                                                                                                                              |

|                                                |                                                                                                                        | Dual 4-bit parallel output: By OUTO instruction, 4-bit data in the accumulator is output, without conversion, onto the lower nibble (03-00) or upper nibble (07-04) of 0-Port, depending on whether the carry flag (CF) is "0" or "1".                                                                                                                                                                                                                                          |

|                                                |                                                                                                                        | 8-bit parallel PLA output: By OUTO instruction, 4-bit data in the accumulator and the carry flag (CF) bit are converted into 8-bit data through the PLA array, and the 8-bit data is output to 0-Port. Depending on user's PLA pattern, 32 kinds of 8-bit data conversions are possible. For example, it can be encoded into 8-segment data for LED display.                                                                                                                    |

|                                                |                                                                                                                        | Refer to Table 4 User mask options for available making option.                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 40-37,<br>(15-12)<br>4- 1,<br>(23-20)<br>8- 5, | 1/0                                                                                                                    | R-Port: This port functions as three 4-bit parallel input and one 3-bit parallel input (non-latched)/output (latched) ports, or 15 individual input (non-latched)/output (latched) lines, depending on instructions.                                                                                                                                                                                                                                                            |

| (27-24)<br>11- 9<br>(31,29,<br>28)             |                                                                                                                        | Parallel I/O: Each 4-bit and 3-bit port is named R-Port #0 (R3-R0), R-Port #1 (R7-R4), R-Port #2 (R11-R8), and R-Port #3 (R14-R12), and is indirectly addressed by the Y-register (Port #). 4-bit data in the accumulator is output to an addressed port of R-Ports #0 to #3 by OUT instruction. 4-bit data on the addressed port is input into the accumulator by IN instruction. (Before IN instruction, the port to be addressed must be set up to "1" state (input) mode).) |

|                                                | 28-25<br>2,1,48,<br>47)<br>32-39<br>6-3)<br>40-37,<br>(15-12)<br>4-1,<br>(23-20)<br>8-5,<br>(27-24)<br>11-9<br>(31,29, | 28-25<br>2,1,48,<br>47)<br>32-39<br>6-3)<br>1/0<br>15-12)<br>4-1,<br>(23-20)<br>8-5,<br>(27-24)<br>11-9<br>(31,29,                                                                                                                                                                                                                                                                                                                                                              |

Table 1: PIN DESCRIPTION (Continued)

| Symbol    | Pin No.   | Туре | Name & Function                                                                  |

|-----------|-----------|------|----------------------------------------------------------------------------------|

| • I/O Por | t (Contin | ued) |                                                                                  |

| R3 -R0,   | 40-37,    |      | Individual I/O: Each line from R14 to RO is indirectly                           |

|           | (15-12)   |      | addressed by the Y-register (Bit #). The addressed line                          |

| R7 -R4,   | 4-1,      |      | is individually set/reset by SETR/RSTR instruction, and                          |

|           | (23-20)   |      | especially each line of R-Port #0 (R3-R0) is directly                            |

| R11-R8,   | ,         |      | set/reset by SETD/RSTD instruction. The addressed line                           |

|           | (27-24)   |      | is individually testable by TSTR instruction, and each                           |

| R14-R12   | 1         |      | line of R-Port #2 (R11-R8) is directly testable in                               |

|           | (31,29,   | i    | particular by TSTD instruction. (Before the TSTR and                             |

|           | 28)       |      | TSTD instructions, the line to be addressed must be set up to "1" (input mode).) |

|           |           |      | Refer to Table 4 User mask options for available making option.                  |

Note: Parenthesis number is applied to suffix -PF

# DIFFERENCES BETWEEN MB8840 SERIES AND MB88400 SERIES

# Table 2: DIFFERENCES BETWEEN MB8840 SERIES AND MB88400 SERIES

| Device<br>Item                     | MB8841                                                                                                                       | MB88401                                                                                                          |

|------------------------------------|------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|

| ROM Size                           | · 2K x 8 bits                                                                                                                | · 4K x 8 bits                                                                                                    |

| RAM Size                           | · 128 x 4 bits                                                                                                               | · 192 x 4 bits                                                                                                   |

| Oscillator<br>Type                 | Crystal/Ceramic,<br>RC-network OSC, or<br>external clock drive                                                               | · Crystal/Ceramic OSC or<br>external clock drive<br>· RC-network OSC or<br>external clock drive<br>(Mask option) |

| Min. Instruction<br>Execution Time | · 3.0µs use 4MHz with prescaler                                                                                              | · 2.86µs use 4.19MHz<br>with prescaler                                                                           |

| K-Port Input Level                 | · Standard threshold                                                                                                         | · Standard threshold<br>· High-threshold<br>(Mask option)                                                        |

| Watch-dog<br>Timer<br>Function     | · No                                                                                                                         | · No · Yes (Mask option) 75                                                                                      |

| Instruction Number                 | 70                                                                                                                           | /3                                                                                                               |

| Members                            | <ul> <li>MB8842M/-PSH, MB8846M</li> <li>MB8843M/-PSH, MB8847M</li> <li>MB8844M/-PSH, MB8848M</li> <li>part above.</li> </ul> | · MB88401-P/-PSH/-PF                                                                                             |

#### INPUT/OUTPUT CIRCUITS

All input-only pins are internally pulled up, and all output-only and input/output pins except 0-, P-, and R-Ports have push-pull output buffer (standard pull-up). 0-, P-, and R-Ports can have push-pull (standard pull-up) or open-drain (standard or high-current) buffer using mask option.

Table 3: INPUT/OUTPUT CIRCUITS

| Pin                                    | Circuit                         | Note                                                                                                                                 |

|----------------------------------------|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|

| RESET,<br>IRQ,<br>TC,<br>SI,<br>K-Port | • Input only pin  About 500kΩ   | IIL ≤ -60µA<br>( VCC = 5.5V<br>VIL = 0.4V)                                                                                           |

| SC/TO                                  | • Input/Output pin  About 500kΩ | IIL ≤ -1.8µA<br>(VCC = 5.5V<br>VIL = 0.4V)                                                                                           |

| so                                     | • Output only pin               | VOH ≥ 2.4V<br>( VCC = 4.5V                                                                                                           |

| O-Ports,<br>P-Ports,<br>R-Ports        | • Standard pull-up              | VOH ≥ 2.4V<br>(VCC = 4.5V<br>IOH = -200μA)<br>VOL ≤ 0.4V<br>(VCC = 4.5V<br>IOL = 1.8mA)<br>Internal pullup resistor<br>approx. 10kΩ. |

|                                        | • Standard open-drain           | VOL ≤ 0.4V<br>(VCC = 4.5V<br>IOL = 1.8mA)<br>VOL ≤ 0.6V<br>(VCC = 4.5V<br>IOH = 3.6mA)<br>With 10kΩ pullup resistor                  |

Table 3: INPUT/OUTPUT CIRCUITS (Continued)

| Pin                             | Circuit                   | Note                                                                                                                    |

|---------------------------------|---------------------------|-------------------------------------------------------------------------------------------------------------------------|

| O-Ports,<br>P-Ports,<br>R-Ports | • High-current open-drain | VOL ≤ 0.4V<br>( VCC = 4.5V<br>IOL = 1.8mA )<br>VOL ≤ 2.0V<br>( VCC = 4.5V<br>IOH = 20 mA )<br>With 10kΩ pullup resistor |

# USER MASK OPTIONS

The MB88400 series has the following mask options, which must be specified by the customer on the attached data release form when devices are ordered.

Table 4: USER MASK OPTIONS

| Optional<br>Feature         | Symbol | Option                            | Option<br>No. | Note                                                     |

|-----------------------------|--------|-----------------------------------|---------------|----------------------------------------------------------|

| Clock<br>Prescaler          | CLK    | No                                | 0             | f <sub>C</sub> =0.5 MHz to 2 MHz                         |

|                             |        | Yes                               | 1             | f <sub>C</sub> =1 MHz to 4.19MHz                         |

| Oscillator                  | osc    | Crystal/ceramic OSC               | 0             | * When only external clock                               |

| Туре                        |        | or external clock*                |               | drive is used, we recommend RC-network oscillator.       |

|                             |        | RC-network OSC or external clock* | 1             | We recommend no clock prescaler.                         |

| Output PLA<br>Data          | SPLA   | 4-bit parallel output             | 0             |                                                          |

|                             |        | 8-bit parallel output             | 1             |                                                          |

| Output Port<br>Type         | PORT   | Standard<br>open-drain            | 2/L           | Output port circuit option selected must be the same for |

|                             |        | Standard<br>pull-up               | 3/M           | all 0-, P-, and R-Ports.                                 |

| i                           |        | High-current<br>open-drain        | 1/K           |                                                          |

| K-Port Input<br>Level       | KIN    | Standard threshold                | 0             |                                                          |

|                             |        | High threshold                    | 1             |                                                          |

| Watch-dog<br>Timer Function | WDR    | No                                | 0             |                                                          |

|                             |        | Yes                               | 1             |                                                          |

#### NOTES ON OPERATION

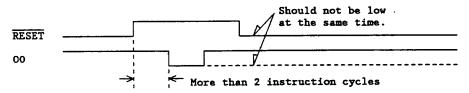

#### · Special Function of 00 Pin

The 00 pin has another function as a test terminal, in addition to its normal function 0-Port. If the 00 pin is forced low while the  $\overline{\text{RESET}}$  pin is low, the MCU is placed in the test mode. Therefore, the 00 pin should not be forced low while the  $\overline{\text{RESET}}$  pin is low (when all output ports are initialized).

Especially when the open-drain is selected for the output port option, the 00 pin should be externally pulled up because such open-drain outputs are subject to noise disturbance if left floating.

At least 2 instruction cycles are required to change 00 pin from high to low after releasing reset ( $\overline{RESET}$ : Low  $\rightarrow$  High)

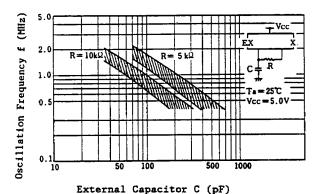

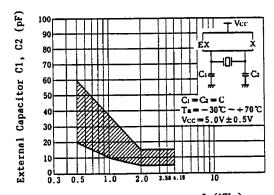

# • External Capacitors for Crystal Oscillation

Fig. 7 gives an aim of an area where the on-chip oscillator has stable oscillator characteristics and short oscillation stabilization time when an average crystal resonator is used.

The external capacitor should be adjusted to individual crystal resonators when precise oscillation frequency is required. It is recommended to use crystal with a frequency higher than required oscillation frequency, together with the on-chip divided-by-two prescaler, because crystal resonators with lower oscillation frequency generally tends to have longer stabilization time and wider characteristics variation.

#### Supply Voltage

Malfunction may occur even within the recommended operating supply voltage if the supply voltage changes rapidly. Therefore, the supply voltage should be regulated as well as possible. The following conditions are recommended for the power supply:

- (1)  $V_{CC}$  ripple (peak-to-peak value) at commercial frequency (50Hz to 60Hz): Less than 10% of typical  $V_{CC}$  value.

- (2)  $V_{CC}$  transient change rate (such as at switching of power supply): Less than 0.1V/ms.

#### INSTRUCTION SET DESCRIPTION

The MB88400 series instruction set includes 75 instructions, 82% of which are single-byte and single-cycle, 17% two-byte two-cycle, and 1% two byte three-cycle. The MB88400 series instruction set is exactly the same as the MB88500 series instruction set, and is divided into ten functional groups:

- Register-to-register transfer

- Register-to-memory transfer

- · Constant transfer

- Arithmetic and logical operations

- Bit manipulation

- Control

- Input/Output

- Branch

- Flag manipulation

- Other

Tables 5 and 6 summarize the MB88400 series instruction set.

Table 5: INSTRUCTION SET SUMMARY

|            | Mnemonic |     |        |     |    | atus | Byte/ | 0                                                         |

|------------|----------|-----|--------|-----|----|------|-------|-----------------------------------------------------------|

|            | +ope:    |     |        | ZF  | CF | ST   | Cycle | Operation                                                 |

| Register-  | TATH     |     | 05     | ٠   | •  | •    | 1/1   | TH+(AC)                                                   |

| to-        | TATL     |     | 06     |     |    | •    | 1/1   | TL+(AC)                                                   |

| Register   | TAS      |     | 07     | •   | •  |      | 1/1   | SB+(AC)                                                   |

| Transfer   | TAY      |     | 04     | •   |    |      | 1/1   | Y+(AC)                                                    |

|            | TSA      |     | 17     | 1   | •  | •    | 1/1   | AC+(SB)                                                   |

|            | TTHA     | ı   | 15     | t   | •  | •    | 1/1   | AC+(TH)                                                   |

|            | TTLA     |     | 16     | ı   | •  |      | 1/1   | AC+(TL)                                                   |

| i          | TYA      |     | 14     | t   |    |      | 1/1   | AC+(Y)                                                    |

|            | XX       |     | 1B     | 1*1 | •  | •    | 1/1   | (AC)≠(X)                                                  |

| Register-  | L        |     | OD     | ī   | •  | •    | 1/1   | $AC \leftarrow \{M(X,Y)\}$                                |

| to-        | LS       |     | 2B     | t   |    |      | 1/1   | $SB \leftarrow \{M(X,Y)\}$                                |

| Memory     | ST       |     | 1D     | •   | •  | •    | 1/1   | $M(X,Y)\leftarrow(AC)$                                    |

| Transfer   | STDC     |     | 1A     | •   | •  | †C   | 1/1   | M(X,Y)+(AC), $Y+(Y)-1$                                    |

|            | STIC     |     | OA     | •   | •  | †C   | 1/1   | M(X,Y)+(AC), $Y+(Y)+1$                                    |

|            | STS      |     | 2A     | 1   |    | •    | 1/1   | $M(X,Y)\leftarrow(SB)$                                    |

|            | X        |     | OB     | 1*1 | •  | •    | 1/1   | $(AC) \neq \{M(X,Y)\}$                                    |

|            | XD       | D   | 50-53* | 1*1 | •  |      | 1/1   | $(AC) \neq \{M(0,D)\}; D=0 \text{ to } 3 (X=0, Y=D)$      |

|            | XYD      | D   | 54-57* | 1*2 | •  |      | 1/1   | $(Y) \neq \{M(0,D)\}; D=4 \text{ to } 7 (X=0, Y=D)$       |

| Constant   | CLA      |     | 90     | 1   | •  | •    | 1/1   | AC+0 (Included in LI instruction)                         |

| Transfer   | LI       | imm | 90-9F* | 1   | .  | .    | 1/1   | AC←imm; imm=0 to 15                                       |

|            | LXI      | imm | 58-5F* | ţ   | .  |      | 1/1   | X3←0, X2 to X0←imm; imm=0 to 7                            |

|            | LXID     |     | 3D90-  | ţ   |    |      | 2/2   | X+imm; imm=0 to 15                                        |

|            |          |     | 3D9F*  |     |    |      |       |                                                           |

|            | LRXA     | imm | 3D20-  |     |    | .    | 2/3   | $X \leftarrow \{ROM(\boxed{imm} \mid X \mid Y)\}d, d=7-4$ |

|            |          |     | 3D3F*  |     |    |      |       | $AC \leftarrow \{ROM([imm \mid X \mid Y])\}d, d=3-0$      |

|            |          |     | j      |     |    |      | 1     | imm=0 to 31                                               |

|            | LYI      | imm | 80-8F* | ŧ   |    | .    | 1/1   | Y ←imm; imm=0 to 15                                       |

| Arithmetic | ADC      |     | 0E     | ţ   | :  | ₽C   | 1/1   | $AC \leftarrow (AC) + \{M(X,Y)\} + (CF)$                  |

| & Logical  | ΑI       | imm | 3D80-  | 1   | t  | †C   | 1/1   | AC+(AC)+imm; imm=0 to 15                                  |

| Operations |          | - 1 | 3D8F   |     |    | 1    | .     | •                                                         |

|            | AND      | 1   | 0F     | t   | .  | ιz   | 1/1   | $AC+(AC)\cap\{M(X,Y)\}$                                   |

| 1          | С        |     | 2E     | 1   | ī  | ĮΖ   | 1/1   | $\{M(X,Y)\}-(AC)$                                         |

| İ          | CI       | imm | BO-BF* | ı   | ı  | ŧΖ   | 1/1   | imm-(AC); imm=0 to 15                                     |

| ŀ          | CYI      | imm | AO-AF* |     |    | ιZ   | 1/1   | imm-(Y); imm=0 to 15                                      |

Table 5: INSTRUCTION SET SUMMARY (Continued)

|            | Mnemonic | Codo   | Fla                                          | ~/S+                                            | a + 11 c     | Byte/ |                                     |

|------------|----------|--------|----------------------------------------------|-------------------------------------------------|--------------|-------|-------------------------------------|

|            | +Operand |        | ZF                                           | CF                                              | ST           | Cvcle |                                     |

| Arithmetic |          | 10     |                                              | 1                                               | 1C           | 1/1   | AC+(AC)+6 if (AC)>9 or (CF)=1       |

| & Logical  | DAS      | 11     |                                              | t                                               | 1c           | 1/1   | AC+(AC)+10 if $(AC)>9$ or $(CF)=1$  |

| Operation  | DCA      | 3D8F   | 1                                            | i                                               | 1C           | 1/1   | AC+(AC)+15 (Included in AI instruc- |

| Operation  | DCM      | 19     | i                                            |                                                 | ‡C           | 1/1   | $M(X,Y)+\{M(X,Y)\}-1$ tion)         |

| i          | DCY      | 18     | •                                            |                                                 | ic           | 1/1   | Y+(Y)-1                             |

| 1          | EOR      | 2F     | 1                                            | ÷                                               | 1Z           | 1/1   | AC+{M(X,Y)}⊕(AC)                    |

|            | ICA      | 3D81   | ī                                            | 1                                               | 1C           | 1/1   | AC+(AC)+1 (Included in AI instruc-  |

|            | ICM      | 09     | i                                            |                                                 | ic           | 1/1   | $M(X,Y)+\{M(X,Y)\}+1$ tion)         |

|            | ICX      | 3DAC   | ·                                            |                                                 | ic           | 2/2   | X← (X)+1                            |

|            | ICY      | 08     | 1                                            | ۱.                                              | ic           | 1/1   | Y+(Y)+1                             |

|            | NEG      | 2D     | ÷                                            | -                                               | ΙZ           | 1/1   | AC+(AC)+1                           |

|            | OR       | 1F     | İ                                            | <b>-</b>                                        | ΙZ           | 1/1   | AC+{M(X,Y)}U(AC)                    |

|            | ROL      | OC.    | 1                                            | 1                                               | †C           | 1/1   | 1.0 (1.(1.)7)((1.0)                 |

|            |          |        |                                              |                                                 |              |       | +CE- A.C.                           |

|            | ROR      | 1C     | t                                            | ;                                               | †C           | 1/1   | A,C, CF                             |

|            | SBC      | 1E     | ī                                            | 1                                               | ΤC           | 1/1   | $AC+\{M(X,Y)\}-(AC)-(CF)$           |

| Bit        | RBIT bp  | 34-37* | •                                            |                                                 | •            | 1/1   | {M(X,Y)}bp+0; bp=0 to 3             |

| Manipula-  | SBIT bp  | 30-33* |                                              | ١.                                              | . !          | 1/1   | $\{M(X,Y)\}bp+1; bp=0 to 3$         |

| tion       | RBA bp   | 3DA4   | •                                            | · ·                                             | ·            | 2/2   | (AC)bp←0 ; bp=0 to 3                |

|            | •        | 3DA7 * |                                              |                                                 | •            | -     |                                     |

|            | SBA bp   | 3DA0   |                                              |                                                 | ١.           | 2/2   | (AC)bp+1 ; bp=0 to 3                |

|            |          | 3DA3 * |                                              |                                                 | 1            |       |                                     |

|            | TBA bp   | 4C-4F* | •                                            | •                                               | ΙZ           | 1/1   | (AC)bp-1 ; bp=0 to 3                |

|            | TBIT bp  | 38-3B* |                                              |                                                 | ΙZ           | 1/1   | {M(X,Y)}bp-1; bp=0 to 3             |

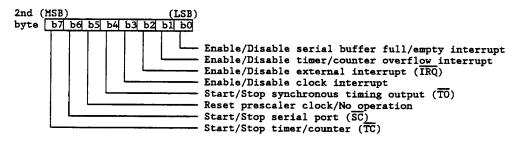

| Control    | EN imm   | 3E00-  | •                                            |                                                 | ·            | 2/2   | Enable the internal resources by    |

|            |          | 3EFF*  |                                              |                                                 |              |       | the operand byte (2nd byte); *3     |

|            | DIS imm  | 3F00-  | ١.                                           | ١.                                              |              | 2/2   | Disable the internal resources by   |

|            | ]        | 3FFF*  |                                              |                                                 | l            |       | the operand byte (2nd byte); *3     |

| Input/     | IN       | 13     | 1                                            | ·-                                              |              | 1/1   | AC+(R)Y ; Y=0 to 3 (Port #)         |

| Output     |          |        |                                              |                                                 | 1            |       | AC+(REG)Y; Y=9 to 15                |

| _          | INK      | 12     | 1                                            | ٠.                                              | <u> </u>     | 1/1   | AC+(K)                              |

|            | OUT      | 03     |                                              | •                                               | · .          | 1/1   | (R)Y+(AC); Y=0 to 3 (Port #)        |

|            |          |        | Ì                                            |                                                 | 1            | İ     | (REG)Y+(R);Y=9 to 15                |

|            | OUTO     | 01     | ٠ ا                                          | ١.                                              | 1 -          | 1/1   | If CF=0 03-00+(AC)                  |

|            |          | l      |                                              |                                                 |              | ļ     | If CF=1 07-04+(AC)                  |

|            | OUTP     | 02     | ٠                                            |                                                 | ·            | 1/1   | P+(AC)                              |

|            | RSTD d   | 44-47* | ١.                                           |                                                 | ١.           | 1/1   | (R)d+0; d=0 to 3 (Bit # of Port #0) |

|            | RSTR     | 22     | ١.                                           |                                                 |              | 1/1   | (R)Y+0; Y=0 to 15 (Bit #)           |

|            | SETD d   | 40-43* | 1 .                                          | •                                               |              | 1/1   | (R)d+1; d=0 to 3 (Bit # of Port #0) |

|            | SETR     | 20     | Ŀ                                            | <u>  :                                   </u>   | <u>  : -</u> | 1/1   | (R)Y+1; Y=0 to 15 (Bit #)           |

|            | TSTD d   | 48-4B* | 1 .                                          |                                                 | ļΖ           | 1/1   | (R)d-1; d=8 to 11 (Bit #)           |

|            | TSTR     | 24     | <u>                                     </u> | <u>  ·                                     </u> | ↓Z           | 1/1   | (R)Y-1; Y=0 to 15 (Bit #)           |

| Branch     | CALL add |        | 1 '                                          |                                                 |              | 2/2   | If ST=1, Subroutine Call for addr;  |

|            |          | 6FFF*  | 1                                            |                                                 |              |       | addr=0 to 4095.                     |

|            | 1        | !      | 1                                            | 1                                               | 1            |       | ST=0, Not Subroutine Call.          |

Table 5: INSTRUCTION SET SUMMARY (Continued)

|           | Mnemonic  | Code           | Fla | g/St | atus | Byte/ |                                                           |

|-----------|-----------|----------------|-----|------|------|-------|-----------------------------------------------------------|

|           | +Operand  | (Hex.)         | ZF  | CF   | ST   | Cycle | Operation                                                 |

| Branch    | JMP addr  | CO-FF*         | •   | •    | •    | 1/1   | If ST=1, Branch to addr; addr=0 to 63<br>ST=0, No Branch. |

|           | JPXY addr | 3D00-<br>3D1F* | •   | •    |      | 2/2   | Branch always to addr on page #n;                         |

|           | JPL addr  | 7000-          |     |      |      | 2/2   | If ST=1, Branch to addr;                                  |

|           |           | 7FFF*          |     |      | l    |       | addr=0 to 4095.                                           |

|           |           |                |     |      |      |       | ST=0, No Branch.                                          |

|           | RTI       | 3C             | •   | •    | •    | 1/1   | Return From Interrupt Routine                             |

|           | RTS       | 2C             | •   |      |      | 1/1   | Return From Subroutine                                    |

| Flag      | RSTC      | 23             | •   | Ţ    | •    | 1/1   | CF+0                                                      |

| Manipula- | SETC      | 21             | •   | 1    |      | 1/1   | CF+1                                                      |

| tion      | TSTC      | 28             | •   | ·    | †CF  | 1/1   | (CF)-1                                                    |

|           | TSTI      | 25             | •   |      | ↓IF  | 1/1   | (IF)-1, (If IRQ=L, IF=1)                                  |

|           | TSTS      | 27             |     | •    | ↓SF  | 1/1   | (SF)-1, SF+0                                              |

|           | TSTV      | 26             | •   | •    | îVF  |       | (VF)-1, VF+0                                              |

|           | TSTZ      | 29             | •   | •    | ↓ZF  | 1/1   | (ZF)-1                                                    |

| Other     | NOP       | 00             | •   | •    |      | 1/1   | No Operation                                              |

#### Notes:

- \*1: ZF is set or reset depending on contents of AC after instruction execution.

\*2: ZF is set or reset depending on contents of Y after instruction execution.

- \*3: Each bit of the operand (the second byte) functions as follows:

### Symbols and Abreviations

```

Symbols

Meaning

Is transferred to

*

Is exchanged with

Arithmetic plus

Arithmetic minus

⊕

∩

Logical exclusive or

Logical OR

Ų

Logical AND

(Overline)

Negation

( )

Contents of parenthesis

Set to "1" always

Set to "0" always

ţ

Affected (set or reset) by operation results

Set to "0" due to carry (not carry flag)

↓C

Set to "0" due to carry flag

↓CF

Set to "0" due to interrupt flag

↓IF

Set to "0" due to serial buffer full/empty flag

↓SF

Set to "0" due to timer/counter overflow flag

↓VF

Set to "0" due to zero (not zero flag)

ψZ

Set to "0" due to zero flag

↓ZF

Not affected

Abbreviation

Meaning

AC

Accumulator

addr

Jump address

Bit pointer (that is part of the instruction code)

bр

С

Carry

CF

Carry flag

Direct line number (that is part of the instruction code)

d

IF

Interrupt flag

Immediate data

imm

IRQ

Interrupt request

K-Port (K3 to K0)

K

LSB

Least significant bit

Data memory (RAM) location indirectly addressed by data pointer

M(X,Y)

(X- and Y-registers)

Data memory (RAM) location directly addressed by "D" bits in the

M(0,D)

instruction code, in page #0 (X=0)

MSB

Most significant bit

0-Port (07-00)

0

PLA

Programmable Logic Array

R-Port (#0: R3-R0, #1: R7-R4, #2: R11-R8, #3: R14-R12)

① R-Port #n specified by Y-register (Y=0 to 3)

(R)Y: Y=n

2 R-Port bit n specified by Y-register (Y=0 to 14)

R-Port bit n specified by "d" bits in the instruction code

(R)d; d=n

SB

Serial buffer register

SF

Serial buffer full/empty flag

ST

Status flag

Timer/counter high byte

TH

Timer/counter low byte

TL

Timer/counter overflow flag

VF

X-register (that indicates page # in data memory RAM)

X

The n-th bit X-register

Χn

Y

Y-register

Z

Zero

1-62

ZF

Zero flag

```

Table 6: INSTRUCTION CODES SUMMARY

| H | 0            | 1               | 2    | 3    | 4    | 5    | 6    | 7        | 8         | 9      | A        | В  | С        | D         | E         | F          |

|---|--------------|-----------------|------|------|------|------|------|----------|-----------|--------|----------|----|----------|-----------|-----------|------------|

| 0 | NOP          | ouro            | OUTP | OUT  | TAY  | TATH | TATL | TAS      | ICY       | ICM    | STIC     | х  | ROL      | L         | ADC       | AND        |

| 1 | DAA          | DAS             | INK  | IN   | TYA  | TTHA | TILA | TSA      | DCY       | DCM    | STDC     | xx | ROR      | ST        | SBC       | OR         |

| 2 | SETR         | SETC            | RSTR | RSTC | TSTR | TSTI | TSTV | TSTS     | TSTC      | TSTZ   | STS      | LS | RTS      | NEG       | C         | EOR        |

| 3 |              | SBIT RBIT bp bp |      |      |      |      |      |          |           | TBIT R |          |    | RTI      | *<br>EXT  | EN<br>imm | DIS<br>imm |

| 4 |              | SETD RSTD       |      |      |      |      |      |          |           |        | STD<br>d |    |          | T<br>_ b  | BA<br>P   |            |

| 5 |              | XD XYD D        |      |      |      |      |      |          |           |        |          |    | XI<br>mm |           |           |            |

| 6 | CALL<br>addr |                 |      |      |      |      |      |          |           |        |          |    |          |           |           |            |

| 7 |              |                 |      |      |      |      |      |          | PL<br>ddr |        |          |    |          |           |           |            |

| 8 |              |                 |      |      |      |      |      |          | YI<br>mm  |        |          |    |          |           |           |            |

| 9 | (CLA)        |                 |      |      |      |      |      | L:<br>i: | T<br>mm   |        |          |    |          |           |           |            |

| A |              |                 |      |      |      |      |      | C:       | YI<br>mm  |        |          |    |          |           |           |            |

| В |              |                 |      |      |      |      |      | C:<br>it | I.        |        |          |    |          | · · · · · | ,         |            |

| С |              |                 |      |      |      |      |      |          |           |        |          |    |          |           |           | :          |

| D |              |                 |      |      |      |      |      |          | 1P        |        |          |    |          |           |           |            |

| E |              |                 |      |      |      |      |      | a.c      | idr       |        |          |    |          |           |           |            |

| F |              |                 |      |      |      |      |      |          |           | ·      |          |    | <u> </u> |           |           |            |

| NOTE: |   |         | : 1- | -byte, | /1-cycle | instruction |                   | : | 2-bytes/2-cycles | instruction |

|-------|---|---------|------|--------|----------|-------------|-------------------|---|------------------|-------------|

|       | * | <br>See | the  | next   | page     |             | 1-63 <sup>L</sup> |   |                  |             |

Table 6: INSTRUCTION CODES SUMMARY (Continued)

Extended instruction

|     |   |          |             |   |   |   |           |     |            |     | ,   |   |     |   |               |       |

|-----|---|----------|-------------|---|---|---|-----------|-----|------------|-----|-----|---|-----|---|---------------|-------|

| 3DH | 0 | 1        | 2           | 3 | 4 | 5 | 6         | 7   | 8          | 9   | A   | В | С   | D | E             | F     |

| О   |   |          |             |   |   |   |           | JF  | YXY        |     |     |   |     |   |               |       |

| 1   |   |          |             |   |   |   |           | ad  | ldr        |     |     |   |     |   |               |       |

| 2   | - |          |             |   |   |   |           |     | XA         |     |     |   |     |   |               |       |

| 3   |   |          |             |   |   |   |           | in  | m          |     |     |   |     |   | · · · · · · · |       |

| 4   |   |          |             | • |   |   |           | רסמ | USE        |     |     |   |     |   |               |       |

| 5   |   |          |             |   |   |   |           |     |            |     |     |   |     |   |               |       |

| 6   |   |          |             |   |   |   |           | NOT | USE        |     |     |   |     |   |               |       |

| 7   |   |          |             |   |   |   |           |     |            |     |     |   |     |   |               |       |

| 8   |   | (ICA)    | !<br>!<br>! |   |   |   |           |     | AI<br>Lmm  |     |     |   |     |   |               | (DCA) |

| 9   |   |          |             |   |   |   |           |     | CID<br>imm |     |     |   |     |   |               |       |

| A   |   | SI<br>br | BA          |   |   | 1 | RBA<br>bp |     |            | NOT | USE |   | ICX | 1 | OT U          | SE    |

| В   |   |          |             |   |   |   |           | NO. | USE        |     |     |   |     |   |               |       |

| С   |   |          |             |   |   |   |           | NO  | r USE      |     |     |   |     |   |               |       |

| D   |   |          |             |   |   |   |           |     |            |     |     |   |     |   |               |       |

| E   |   |          |             |   |   |   |           | NO' | r use      |     |     |   |     |   |               |       |

| F   |   |          |             |   |   |   |           |     |            |     | -   |   |     |   |               |       |

| Note: |  | : | 3 | byte/3 | cycle | instruction 1- | 64 |

|-------|--|---|---|--------|-------|----------------|----|

|-------|--|---|---|--------|-------|----------------|----|

# PRODUCT LINE-UP AND DEVELOPMENT TOOLS

The MB88400 series consists of the MB88401. The MB88408U are available as piggyback EPROM evaluation devices. Refer to Table 7.

Table 7: MB88500 SERIES PRODUCT LINE-UP & DEVELOPMENT TOOLS

|                     | MB88401-P/-PSH/-PF           | MB88408U-C-001E/-002E/-003E  |

|---------------------|------------------------------|------------------------------|

|                     |                              |                              |

| ROM Size            | 4K x 8 bits                  | 4K x 8 bits                  |

|                     | (On-chip mask ROM)           | (External ERPOM)             |

| RAM Size            | 192 x 4 bits                 | 192 x 4 bits                 |

| (Directly addressed | (0-7)                        | (0-7)                        |

| locations)          |                              |                              |

| I/O Port:           | Total 36 lines               | Total 36 lines               |

| -Input-only Port    | 4                            | 4                            |

| -Output-only Port   | 12                           | 12                           |

| -I/O Port           | 15                           | 15                           |

| -Control Port       | 5 (Including serial I/O)     | 5 (Including serial I/O)     |

| Output Port Type    | · Standard pull-up           | · High-current open-drain    |

|                     | · Standard open-drain        |                              |

|                     | · High-current open-drain    |                              |

|                     | (Mask option)                |                              |

|                     | `                            |                              |

| K-Port Input Level  | · Standard threshold         | · Standard threshold         |

| _                   | · High threshold             |                              |

|                     |                              |                              |

| Output PLA Pattern  | 33 patterns                  |                              |

| -                   | · Dual 4-bit parallel ouptut | · Dual 4-bit parallel ouptut |

| 1                   | · 8-bit PLA output           | (-001E)                      |

|                     | (32 patterns)                | · 8-bit PLA output           |

|                     | (00 passess)                 | (-002E/-003E)                |

| Stack Depth         | 8 levels                     | 8 levels                     |

| (Nesting Level)     |                              |                              |

| Timer/Counter:      | Yes (Auto loading)           | Yes (Auto loading)           |

| -Buffer Size        | 8 bits                       | 8 bits                       |

| -Clock Source       | Internal/External            | Internal/External            |

| Serial I/O:         | Yes                          | Yes                          |

| -Buffer Size        | 4 bits                       | 4 bits                       |

| -Clock Source       | Internal/External            | Internal/External            |

| -Output Latch       | Yes                          | Yes                          |

| Clock Generator:    | Yes                          | Yes                          |

| -Oscillator Type    | · Crystal/External           | · Crystal/RC-network/        |

| obciliator Type     | · RC-network/External        | External                     |

|                     | (Mask option)                | Dyrellai                     |

| -Clock Frequency    | 0.5MHz-2MHz                  | 0.5MHz-2MHz                  |

| (With prescaler)    | (1MHz-4.19MHz)               | (1MHz-4.19MHz)               |

| Clock Prescaler     | Yes/No                       | Yes/No                       |

| (Divid-by-two)      | ,                            |                              |

| (DIVIG-BY-EWO)      | (Mask option)                | (Selected by external pin)   |

| Interrupt Function  | Yes                          | Yes                          |

| -Nesting Level      | Single level                 | Single level                 |