# ADC1207S080

Single 12 bits ADC, up to 80 MHz with direct/ultra high IF sampling

Rev. 02 — 7 August 2008

**Product data sheet**

## 1. General description

The ADC1207S080 is a 12-bit Analog-to-Digital Converter (ADC) optimized for direct Input Frequency (IF) sampling and supporting the most demanding use conditions in ultra high IF radio transceivers for cellular infrastructure and other applications such as wireless infrastructure, optical networking and fixed telecommunication. Due to its broadband input capabilities, the ADC1207S080 is ideal for single and multiple carriers data conversion.

Operating at a maximum sampling rate of 80 MHz, analog input signals are converted into 12-bit binary coded digital words. All static digital inputs are CMOS compatible. All output signals are Low-Voltage Complementary Metal-Oxide Semiconductor (LVCMOS) compatible. The ADC1207S080 offers the most flexible acquisition control system because of its programmable Complete Conversion Signal (CCS) that allows to adjust the delay of the acquisition clock.

The ADC1207S080 offers the lowest input capacitance (< 1 pF) and therefore the highest flexibility in front-end aliasing filter strategy because of its internal front-end buffer.

#### 2. Features

- 12-bit resolution

- Differential input with 375 MHz bandwidth

- 90 dB SFDR; 71 dB S/N (f<sub>i</sub> = 225 MHz; f<sub>clk</sub> = 80 MHz; B = 5 MHz)

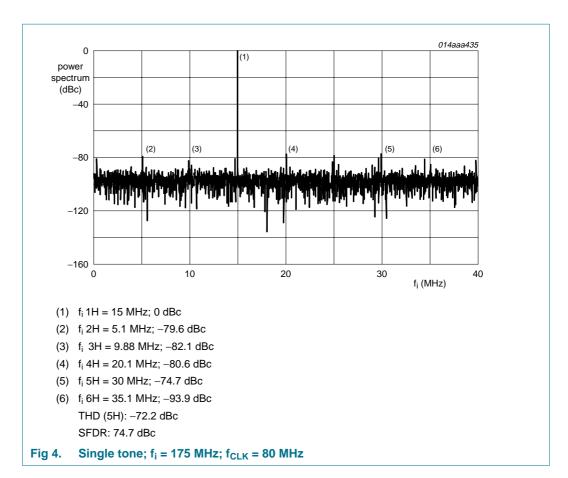

- 74 dB SFDR; 66.5 dB S/N (f<sub>i</sub> = 175 MHz; f<sub>clk</sub> = 80 MHz; B = Nyquist)

- High speed sampling rate up to 80 MHz

- Internal front-end buffer (input capacitance < 1 pF)</p>

- Programmable acquisition output clock (complete conversion signal)

- Full-scale controllable from 1.5 V to 2 V (p-p); continuous scale

- Single 5 V power supply

- 3.3 V LVCMOS compatible digital outputs

- Binary or two's-complement LVCMOS outputs

- CMOS compatible static digital inputs

- Only 2 clock cycles latency

- Industrial temperature range from –40 °C to +85 °C

- HTQFP48 package

## 3. Applications

High speed analog to digital conversion for:

- Radio transceivers

- Wireless infrastructure

- Cable modem

- Digital storage scope

- Fixed telecommunication,

- Optical networking

- Wireless Local Area Network (WLAN) infrastructure.

- General purpose applications

## 4. Ordering information

Table 1. Ordering information

| Type number Package |         |                                                                                                           |          | Sampling           |

|---------------------|---------|-----------------------------------------------------------------------------------------------------------|----------|--------------------|

|                     | Name    | Description                                                                                               | Version  | frequency<br>(MHz) |

| ADC1207S080HW       | HTQFP48 | plastic thermal enhanced thin quad flat package; 48 leads; body $7 \times 7 \times 1$ mm; exposed die pad | SOT545-2 | 80                 |

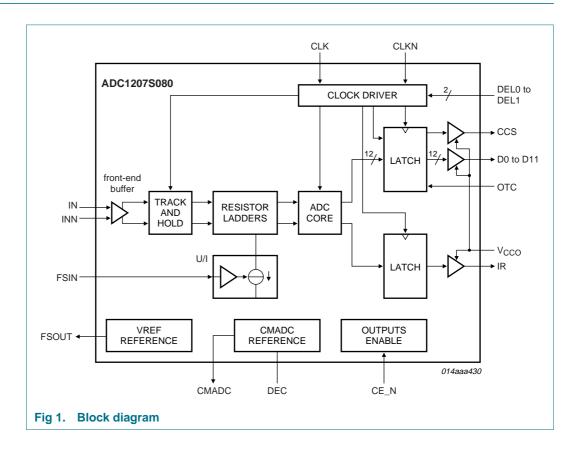

## 5. Block diagram

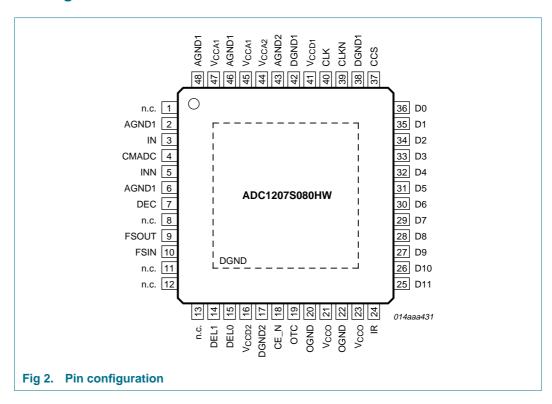

## 6. Pinning information

#### 6.1 Pinning

#### 6.2 Pin description

Table 2. Pin description

| Symbol            | Pin | Type[1] | Description                              |

|-------------------|-----|---------|------------------------------------------|

| n.c.              | 1   | -       | not connected                            |

| AGND1             | 2   | G       | analog ground 1                          |

| IN                | 3   | I       | analog input voltage                     |

| CMADC             | 4   | 0       | regulator common mode ADC output         |

| INN               | 5   | I       | complementary analog input voltage       |

| AGND1             | 6   | G       | analog ground 1                          |

| DEC               | 7   | I/O     | decoupling node                          |

| n.c.              | 8   | -       | not connected                            |

| FSOUT             | 9   | 0       | full-scale reference voltage output      |

| FSIN              | 10  | I       | full-scale reference voltage input       |

| n.c.              | 11  | -       | not connected                            |

| n.c.              | 12  | -       | not connected                            |

| n.c.              | 13  | -       | not connected                            |

| DEL1              | 14  | I       | complete conversion signal delay input 1 |

| DEL0              | 15  | I       | complete conversion signal delay input 0 |

| V <sub>CCD2</sub> | 16  | Р       | digital supply voltage 2 (5.0 V)         |

Table 2.

Pin description ...continued

| Table 2.          | Pin descriptioncontinued |         |                                                         |  |  |

|-------------------|--------------------------|---------|---------------------------------------------------------|--|--|

| Symbol            | Pin                      | Type[1] | Description                                             |  |  |

| DGND2             | 17                       | G       | digital ground 2                                        |  |  |

| CE_N              | 18                       | I       | chip enable input (CMOS level; active LOW)              |  |  |

| OTC               | 19                       | I       | control input for two's complement output (active HIGH) |  |  |

| OGND              | 20                       | G       | data output ground                                      |  |  |

| $V_{CCO}$         | 21                       | Р       | data output supply voltage (3.3 V)                      |  |  |

| OGND              | 22                       | G       | data output ground                                      |  |  |

| $V_{CCO}$         | 23                       | Р       | data output supply voltage (3.3 V)                      |  |  |

| IR                | 24                       | 0       | in-range output                                         |  |  |

| D11               | 25                       | 0       | data output bit 11 (Most Significant Bit (MSB))         |  |  |

| D10               | 26                       | 0       | data output bit 10                                      |  |  |

| D9                | 27                       | 0       | data output bit 9                                       |  |  |

| D8                | 28                       | 0       | data output bit 8                                       |  |  |

| D7                | 29                       | 0       | data output bit 7                                       |  |  |

| D6                | 30                       | 0       | data output bit 6                                       |  |  |

| D5                | 31                       | 0       | data output bit 5                                       |  |  |

| D4                | 32                       | 0       | data output bit 4                                       |  |  |

| D3                | 33                       | 0       | data output bit 3                                       |  |  |

| D2                | 34                       | 0       | data output bit 2                                       |  |  |

| D1                | 35                       | 0       | data output bit 1                                       |  |  |

| D0                | 36                       | 0       | data output bit 0 (Least Significant Bit (LSB))         |  |  |

| CCS               | 37                       | 0       | complete conversion signal output                       |  |  |

| DGND1             | 38                       | G       | digital ground 1                                        |  |  |

| CLKN              | 39                       | I       | complementary clock input                               |  |  |

| CLK               | 40                       | I       | clock input                                             |  |  |

| $V_{CCD1}$        | 41                       | Р       | digital supply voltage 1 (5.0 V)                        |  |  |

| DGND1             | 42                       | G       | digital ground 1                                        |  |  |

| AGND2             | 43                       | G       | analog ground 2                                         |  |  |

| $V_{CCA2}$        | 44                       | Р       | analog supply voltage 2 (5.0 V)                         |  |  |

| V <sub>CCA1</sub> | 45                       | Р       | analog supply voltage 1 (5.0 V)                         |  |  |

| AGND1             | 46                       | G       | analog ground 1                                         |  |  |

| V <sub>CCA1</sub> | 47                       | Р       | analog supply voltage 1 (5.0 V)                         |  |  |

| AGND1             | 48                       | G       | analog ground 1                                         |  |  |

| DGND              | exposed<br>die pad       | G       | digital ground                                          |  |  |

|                   |                          |         |                                                         |  |  |

<sup>[1]</sup> P: power supply; G: ground; I: input; O: output.

## 7. Limiting values

Table 3. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134).

| Symbol           | Parameter                 | Conditions          | Min             | Max                  | Unit |

|------------------|---------------------------|---------------------|-----------------|----------------------|------|

| $V_{CCA}$        | analog supply voltage     |                     | <u>[1]</u> –0.5 | +7.0                 | V    |

| $V_{CCD}$        | digital supply voltage    |                     | <u>[1]</u> –0.5 | +7.0                 | V    |

| $V_{CCO}$        | output supply voltage     |                     | [2] -0.5        | +5.0                 | V    |

| $\Delta V_{CC}$  | supply voltage difference | $V_{CCA} - V_{CCD}$ | -1.0            | +1.0                 | V    |

|                  |                           | $V_{CCD} - V_{CCO}$ | -1.0            | +4.0                 | V    |

|                  |                           | $V_{CCA} - V_{CCO}$ | -1.0            | +4.0                 | V    |

| $V_{i(IN)}$      | input voltage on pin IN   | referenced to AGND  | 0               | V <sub>CCA</sub> + 1 | V    |

| $V_{i(INN)}$     | input voltage on pin INN  | referenced to AGND  | 0               | V <sub>CCA</sub> + 1 | V    |

| $V_{i(CLK)}$     | input voltage on pin CLK  | referenced to DGND  | 0               | V <sub>CCD</sub> + 1 | V    |

| $V_{i(CLKN)}$    | input voltage on pin CLKN | referenced to DGND  | 0               | V <sub>CCD</sub> + 1 | V    |

| lo               | output current            |                     | -               | 10                   | mA   |

| T <sub>stg</sub> | storage temperature       |                     | -55             | +150                 | °C   |

| T <sub>amb</sub> | ambient temperature       |                     | -40             | +85                  | °C   |

| Tj               | junction temperature      |                     | -               | 150                  | °C   |

|                  |                           |                     |                 |                      |      |

<sup>[1]</sup> The supply voltages  $V_{CCA}$  and  $V_{CCD}$  may have any value between -0.5 V and +7.0 V provided that the supply voltage differences  $\Delta V_{CC}$  are respected.

#### 8. Thermal characteristics

Table 4. Thermal characteristics

| Symbol               | Parameter                                   | Conditions | Тур             | Unit |

|----------------------|---------------------------------------------|------------|-----------------|------|

| $R_{th(j-a)}$        | thermal resistance from junction to ambient |            | <u>[1]</u> 36.2 | K/W  |

| R <sub>th(j-c)</sub> | thermal resistance from junction to case    |            | <u>11</u> 14.3  | K/W  |

<sup>[1]</sup> In compliance with JEDEC test board, in free air.

<sup>[2]</sup> The supply voltage  $V_{CCO}$  may have any value between -0.5 V and +5.0 V provided that the supply voltage differences  $\Delta V_{CC}$  are respected.

#### 9. Characteristics

#### Table 5. Characteristics

$V_{CCA} = 4.75 \ V \ to \ 5.25 \ V; \ V_{CCD} = 4.75 \ V \ to \ 5.25 \ V; \ V_{CCO} = 2.7 \ V \ to \ 3.6 \ V; \ AGND \ and \ DGND \ shorted \ together; \ T_{amb} = -40 \ ^{\circ}C$   $to \ +85 \ ^{\circ}C; \ V_{i(IN)} - V_{i(INN)} = -0.5 \ dBFS; \ V_{ref(fs)} = V_{CCA} - 1.87 \ V; \ V_{I(cm)} = V_{CCA} - 1.95 \ V; \ typical \ values \ measured \ at$   $V_{CCA} = V_{CCD} = 5 \ V, \ V_{CCO} = 3.3 \ V, \ T_{amb} = 25 \ ^{\circ}C \ and \ C_L = 10 \ pF; \ unless \ otherwise \ specified.$

| Symbol                 | Parameter                        | Conditions                                                                      |      | Min                  | Тур                    | Max                         | Unit      |  |

|------------------------|----------------------------------|---------------------------------------------------------------------------------|------|----------------------|------------------------|-----------------------------|-----------|--|

| Supplies               |                                  |                                                                                 |      |                      |                        |                             |           |  |

| $V_{CCA}$              | analog supply voltage            |                                                                                 |      | 4.75                 | 5.0                    | 5.25                        | V         |  |

| $V_{CCD}$              | digital supply voltage           |                                                                                 |      | 4.75                 | 5.0                    | 5.25                        | V         |  |

| V <sub>CCO</sub>       | output supply voltage            |                                                                                 |      | 2.7                  | 3.3                    | 3.6                         | V         |  |

| I <sub>CCA</sub>       | analog supply current            |                                                                                 |      | -                    | 120                    | 135                         | mA        |  |

| I <sub>CCD</sub>       | digital supply current           |                                                                                 |      | -                    | 50                     | 65                          | mA        |  |

| I <sub>CCO</sub>       | output supply current            | $f_{clk} = 80 \text{ MHz};$<br>$f_i = 93 \text{ MHz}$                           |      | -                    | 10                     | 15                          | mA        |  |

| P <sub>tot</sub>       | total power dissipation          | f <sub>clk</sub> = 80 MHz; DC input                                             |      | -                    | 840                    | 990                         | mW        |  |

| Clock inpu             | uts: pins CLK and CLKN           | 1                                                                               |      |                      |                        |                             |           |  |

| V <sub>IL</sub>        | LOW-level input voltage          | referenced to DGND; V <sub>C0</sub>                                             | CD = | = 5 V                |                        |                             |           |  |

|                        |                                  | Positive<br>Emitter-Coupled<br>Logic (PECL) mode                                |      | 3.19                 | -                      | 3.52                        | V         |  |

|                        |                                  | Transistor-Transistor<br>Logic (TTL) mode                                       |      | DGND                 | -                      | 0.8                         | V         |  |

| $V_{IH}$               | HIGH-level input voltage         | IGH-level input voltage referenced to DGND; V <sub>CCD</sub> = 5 V              |      |                      |                        |                             |           |  |

|                        |                                  | PECL mode                                                                       |      | 3.83                 | -                      | 4.12                        | V         |  |

|                        |                                  | TTL mode                                                                        |      | 2.0                  | -                      | $V_{CCD}$                   | V         |  |

| I <sub>IL</sub>        | LOW-level input current          | $V_{CLK}$ or $V_{CLKN} = 3.52 \text{ V}$                                        | [2]  | -                    | -                      | 28                          | μΑ        |  |

|                        |                                  | V <sub>CLK</sub> or V <sub>CLKN</sub> = 0.80 V                                  |      | 1                    | -                      | -                           | nA        |  |

| I <sub>IH</sub>        | HIGH-level input current         | $V_{CLK}$ or $V_{CLKN} = 3.83 \text{ V}$                                        |      | -                    | -                      | 30                          | μΑ        |  |

|                        |                                  | $V_{CLK}$ or $V_{CLKN} = 2.00 \text{ V}$                                        |      | 2                    | -                      | -                           | nA        |  |

| V <sub>i(clk)dif</sub> | differential clock input voltage | V <sub>CLK</sub> – V <sub>CLKN</sub> ;<br>AC mode; DC voltage<br>level is 2.5 V |      | 1.3                  | 1.5                    | 1.7                         | V         |  |

| R <sub>i</sub>         | input resistance                 | $f_{clk} = 80 \text{ MHz}$                                                      | [2]  | -                    | 6.3                    | -                           | kΩ        |  |

| Ci                     | input capacitance                | $f_{clk} = 80 \text{ MHz}$                                                      | [2]  | -                    | 1.1                    | -                           | fF        |  |

| Analog in              | outs: pins IN and INN            |                                                                                 |      |                      |                        |                             |           |  |

| I <sub>IL</sub>        | LOW-level input current          | $V_{ref(fs)} = V_{CCA} - 1.75 \text{ V}$                                        |      | -                    | 5                      | -                           | μΑ        |  |

| I <sub>IH</sub>        | HIGH-level input current         | $V_{ref(fs)} = V_{CCA} - 1.75 \text{ V}$                                        |      | -                    | 5                      | -                           | μΑ        |  |

| R <sub>i</sub>         | input resistance                 |                                                                                 | [2]  | 6.3                  | -                      | -                           | $M\Omega$ |  |

| Ci                     | input capacitance                |                                                                                 | [2]  | -                    | -                      | 700                         | fF        |  |

| $V_{I(cm)}$            | common-mode input voltage        | $V_{i(IN)} = V_{i(INN)};$<br>output code = 2047                                 |      | V <sub>CCA</sub> – 2 | V <sub>CCA</sub> – 1.8 | V <sub>CCA</sub> – 1.6      | V         |  |

| Digital inp            | uts: pins OTC and CE_N           |                                                                                 |      |                      |                        |                             |           |  |

| $V_{IL}$               | LOW-level input voltage          |                                                                                 |      | DGND                 | -                      | $0.3 \times V_{\text{CCD}}$ | V         |  |

| $V_{IH}$               | HIGH-level input voltage         |                                                                                 |      | $0.7 \times V_{CCD}$ | -                      | $V_{CCD}$                   | V         |  |

NXP Semiconductors ADC1207S080

#### Single 12 bits ADC, up to 80 MHz with direct/ultra high IF sampling

Table 5.

Characteristics ...continued

$V_{CCA}$  = 4.75 V to 5.25 V;  $V_{CCD}$  = 4.75 V to 5.25 V;  $V_{CCO}$  = 2.7 V to 3.6 V; AGND and DGND shorted together;  $T_{amb}$  = -40 °C to +85 °C;  $V_{i(IN)}$  -  $V_{i(INN)}$  = -0.5 dBFS;  $V_{ref(fs)}$  =  $V_{CCA}$  - 1.87 V;  $V_{I(cm)}$  =  $V_{CCA}$  - 1.95 V; typical values measured at  $V_{CCA}$  =  $V_{CCD}$  = 5 V,  $V_{CCO}$  = 3.3 V,  $T_{amb}$  = 25 °C and  $C_L$  = 10 pF; unless otherwise specified.

| Symbol               | Parameter                         | Conditions                                                                                                                                    | Min                    | Тур                     | Max                         | Unit |

|----------------------|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-------------------------|-----------------------------|------|

| I <sub>IL</sub>      | LOW-level input current           | $V_{IL} = 0.8 \ V$                                                                                                                            | -                      | 1                       | -                           | μΑ   |

| I <sub>IH</sub>      | HIGH-level input current          | V <sub>IH</sub> = 2.0 V                                                                                                                       | -                      | 1                       | -                           | μΑ   |

| Digital inp          | outs: pins DEL0 and DEL1          |                                                                                                                                               |                        |                         |                             |      |

| V <sub>IL</sub>      | LOW-level input voltage           |                                                                                                                                               | DGND                   | -                       | $0.3 \times V_{\text{CCD}}$ | V    |

| V <sub>IH</sub>      | HIGH-level input voltage          |                                                                                                                                               | $0.7 \times V_{CCD}$   | -                       | V <sub>CCD</sub>            | V    |

| I <sub>IL</sub>      | LOW-level input current           | V <sub>IL</sub> = 0.8 V                                                                                                                       | -                      | 8                       | -                           | μΑ   |

| I <sub>IH</sub>      | HIGH-level input current          | V <sub>IH</sub> = 2.0 V                                                                                                                       | -                      | 20                      | -                           | μΑ   |

| Voltage co           | ontrolled regulator output        | : pin CMADC                                                                                                                                   |                        |                         |                             |      |

| V <sub>O(cm)</sub>   | common-mode output                | $I_L = 0 \text{ mA}$                                                                                                                          | -                      | V <sub>CCA</sub> – 1.88 | -                           | V    |

|                      | voltage                           | $I_L = 2 \text{ mA}$                                                                                                                          | -                      | V <sub>CCA</sub> – 1.95 | -                           | V    |

| Reference            | voltage input: pin FSIN           | <u>]</u>                                                                                                                                      |                        |                         |                             |      |

| $V_{ref(fs)}$        | full-scale reference voltage      |                                                                                                                                               | -                      | V <sub>CCA</sub> - 1.80 | -                           | V    |

| I <sub>ref(fs)</sub> | full-scale reference current      |                                                                                                                                               | -                      | 0.1                     | -                           | μΑ   |

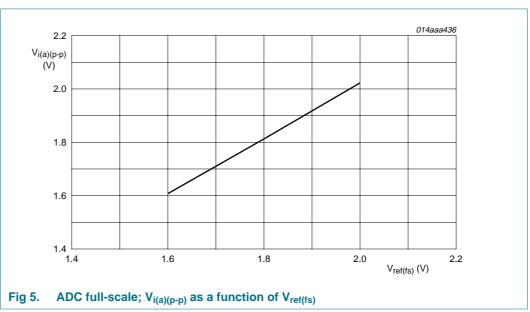

| $V_{i(a)(p-p)}$      | peak-to-peak analog input voltage | $\begin{aligned} &\text{see } \frac{\text{Figure 5}}{V_{i} = V_{i(IN)} - V_{i(INN)}}; \\ &V_{I(cm)} = V_{CCA} - 1.95 \text{ V} \end{aligned}$ | -                      | 1.85                    | -                           | V    |

| Full-scale           | voltage controlled regula         | ator output: pin FSOUT                                                                                                                        |                        |                         |                             |      |

| V <sub>O(ref)</sub>  | reference output voltage          | $I_L = I_{ref(fs)}$                                                                                                                           | -                      | V <sub>CCA</sub> – 1.80 | -                           | V    |

|                      |                                   | $I_L = 2 \text{ mA}$                                                                                                                          | -                      | V <sub>CCA</sub> – 1.82 | -                           | V    |

| Digital out          | tputs: pins D11 to D0, IR         | and CCS                                                                                                                                       |                        |                         |                             |      |

| Output leve          | els                               |                                                                                                                                               |                        |                         |                             |      |

| $V_{OL}$             | LOW-level output voltage          | $I_{OL} = 2 \text{ mA}$                                                                                                                       | DGND                   | -                       | DGND + 0.5                  | V    |

| $V_{OH}$             | HIGH-level output voltage         | $I_{OH} = -0.4 \text{ mA}$                                                                                                                    | V <sub>CCO</sub> – 0.5 | -                       | V <sub>cco</sub>            | V    |

| l <sub>OZ</sub>      | OFF-state output current          | output level between 0.5 V and V <sub>CCO</sub>                                                                                               | -0.1                   | 0                       | +0.1                        | μΑ   |

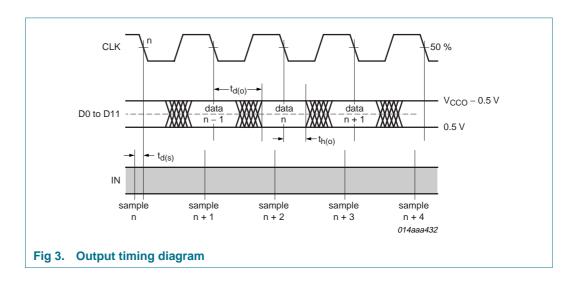

| Timing[4]            |                                   |                                                                                                                                               |                        |                         |                             |      |

| t <sub>d(s)</sub>    | sampling delay time               | C <sub>L</sub> = 10 pF                                                                                                                        | -                      | 0.1                     | 0.24                        | ns   |

| t <sub>h(o)</sub>    | output hold time                  | C <sub>L</sub> = 10 pF                                                                                                                        | 2.6                    | 3.8                     | -                           | ns   |

| $t_{d(o)}$           | output delay time                 | C <sub>L</sub> = 10 pF                                                                                                                        | -                      | 4.7                     | 7.8                         | ns   |

| 3-state out          | put delay                         |                                                                                                                                               |                        |                         |                             |      |

| t <sub>dZH</sub>     | float to active HIGH delay time   |                                                                                                                                               | -                      | 3.6                     | -                           | ns   |

| t <sub>dZL</sub>     | float to active LOW delay time    |                                                                                                                                               | -                      | 3.9                     | -                           | ns   |

| t                    | active HIGH to float              |                                                                                                                                               | -                      | 9.2                     | -                           | ns   |

| t <sub>dHZ</sub>     | delay time                        |                                                                                                                                               |                        |                         |                             |      |

| t <sub>dLZ</sub>     |                                   |                                                                                                                                               | -                      | 7.2                     | -                           | ns   |

Table 5.

Characteristics ...continued

$V_{CCA} = 4.75 \ V \ to \ 5.25 \ V; \ V_{CCD} = 4.75 \ V \ to \ 5.25 \ V; \ V_{CCO} = 2.7 \ V \ to \ 3.6 \ V; \ AGND \ and \ DGND \ shorted \ together; \ T_{amb} = -40 \ ^{\circ}C$   $to \ +85 \ ^{\circ}C; \ V_{i(IN)} - V_{i(INN)} = -0.5 \ dBFS; \ V_{ref(fs)} = V_{CCA} - 1.87 \ V; \ V_{I(cm)} = V_{CCA} - 1.95 \ V; \ typical \ values \ measured \ at$   $V_{CCA} = V_{CCD} = 5 \ V, \ V_{CCO} = 3.3 \ V, \ T_{amb} = 25 \ ^{\circ}C \ and \ C_L = 10 \ pF; \ unless \ otherwise \ specified.$

| Symbol                | Parameter                  | Conditions                                                                                                           | Min            | Тур        | Max | Unit |

|-----------------------|----------------------------|----------------------------------------------------------------------------------------------------------------------|----------------|------------|-----|------|

| Clock timi            | ng inputs: pins CLK and    | CLKN                                                                                                                 |                |            |     |      |

| δ                     | duty cycle                 | $f_{clk} = 80 \text{ MHz};$<br>$f_i = 175 \text{ MHz}$                                                               | 45             | -          | 55  | %    |

| f <sub>clk(min)</sub> | minimum clock<br>frequency |                                                                                                                      | -              | -          | 9.5 | MHz  |

| f <sub>clk(max)</sub> | maximum clock<br>frequency | $\delta$ = 45 % to 55 %                                                                                              | 80             | -          | -   | MHz  |

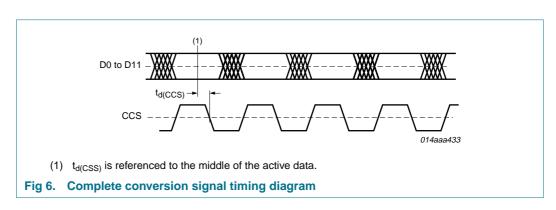

| Timing co             | mplete conversion signal   | : pin CCS; see Figure 6                                                                                              | <u> </u>       |            |     |      |

| t <sub>d(CCS)</sub>   | CCS delay time             | $C_L = 10 \text{ pF};$<br>DEL0 = HIGH;<br>DEL1 = LOW                                                                 | -              | 0.3        | -   | ns   |

|                       |                            | $C_L = 10 \text{ pF};$<br>DEL0 = LOW;<br>DEL1 = HIGH                                                                 | -              | 1.3        | -   | ns   |

|                       |                            | $C_L = 10 \text{ pF};$<br>DEL0 = HIGH;<br>DEL1 = HIGH                                                                | -              | 2.3        | -   | ns   |

| Analog sig            | gnal processing (clock du  | ity cycle 50 %)                                                                                                      |                |            |     |      |

| INL                   | integral non-linearity     | $f_{clk} = 20 \text{ MHz};$<br>$f_i = 21.4 \text{ MHz}$                                                              | -              | ±2.0       | -   | LSB  |

| DNL                   | differential non-linearity | $f_{clk}$ = 20 MHz;<br>$f_i$ = 21.4 MHz; no<br>missing code<br>guaranteed                                            | -              | ±0.6       | -   | LSB  |

| E <sub>offset</sub>   | offset error               | $V_{CCA} = V_{CCD} = 5 \text{ V};$<br>$V_{CCO} = 3.3 \text{ V};$<br>$T_{amb} = 25 \text{ °C};$<br>output code = 2047 | -4             | +8         | +24 | mV   |

| E <sub>G</sub>        | gain error                 | $V_{CCA} = V_{CCD} = 5 \text{ V};$<br>$V_{CCO} = 3.3 \text{ V};$<br>$T_{amb} = 25 \text{ °C}$                        | -              | 2.5        | -   | %FS  |

| В                     | bandwidth                  | f <sub>clk</sub> = 80 MHz; –3 dB;<br>full-scale input                                                                | <u>[5]</u> 320 | 375        | -   | MHz  |

| $\alpha_{2H}$         | second harmonic level      | f <sub>i</sub> = 21.4 MHz                                                                                            | -              | -79        | -   | dBc  |

|                       |                            | $f_i = 93 \text{ MHz}$                                                                                               | -              | -78        | -   | dBc  |

|                       |                            | f <sub>i</sub> = 175 MHz                                                                                             | -              | -74        | -   | dBc  |

| $\alpha_{3H}$         | third harmonic level       | $f_i = 21.4 \text{ MHz}$                                                                                             | -              | -84        | -   | dBc  |

|                       |                            | $f_i = 93 \text{ MHz}$                                                                                               | -              | -80        | -   | dBc  |

|                       |                            | f <sub>i</sub> = 175 MHz                                                                                             | -              | -76        | -   | dBc  |

| THD                   | total harmonic distortion  | $f_i = 21.4 \text{ MHz}$                                                                                             | [6] _          | <b>-75</b> | -   | dBc  |

|                       |                            | f <sub>i</sub> = 93 MHz                                                                                              | -              | -73        | -   | dBc  |

|                       |                            | f <sub>i</sub> = 175 MHz                                                                                             | -              | -68        | -   | dBc  |

| N <sub>th(RMS)</sub>  | RMS thermal noise          | $\begin{aligned} &V_{i(IN)} = V_{i(INN)}; \\ &f_{clk} = 80 \text{ MHz} \end{aligned}$                                | -              | 0.45       | -   | LSB  |

Table 5. Characteristics ... continued

$V_{CCA} = 4.75~V$  to 5.25~V;  $V_{CCD} = 4.75~V$  to 5.25~V;  $V_{CCO} = 2.7~V$  to 3.6~V; AGND and DGND shorted together;  $T_{amb} = -40~^{\circ}C$  to  $+85~^{\circ}C$ ;  $V_{i(IN)} - V_{i(INN)} = -0.5~dBFS$ ;  $V_{ref(fs)} = V_{CCA} - 1.87~V$ ;  $V_{I(cm)} = V_{CCA} - 1.95~V$ ; typical values measured at  $V_{CCA} = V_{CCD} = 5~V$ ,  $V_{CCO} = 3.3~V$ ,  $T_{amb} = 25~^{\circ}C$  and  $T_{CCD} = 10~pF$ ; unless otherwise specified.

| Symbol | Parameter                    | Conditions                                                         | Min          | Тур  | Max | Unit |

|--------|------------------------------|--------------------------------------------------------------------|--------------|------|-----|------|

| S/N    | signal-to-noise ratio        | $f_i = 21.4 \text{ MHz}$                                           | <u>[7]</u> - | 67.4 | -   | dBc  |

|        |                              | $f_i = 93 \text{ MHz}$                                             | 63           | 67.2 | -   | dBc  |

|        |                              | $f_i = 175 \text{ MHz}$                                            | -            | 66.5 | -   | dBc  |

| SFDR   | spurious free dynamic        | $f_i = 21.4 \text{ MHz}$                                           | -            | 76   | -   | dBc  |

|        | range                        | $f_i = 93 \text{ MHz}$                                             | 68           | 78   | -   | dBc  |

|        |                              | f <sub>i</sub> = 175 MHz                                           | -            | 74   | -   | dBc  |

| ACPR   | adjacent channel power ratio | f <sub>i</sub> = 93 MHz; 5 MHz<br>channel spacing;<br>B = 3.84 MHz | -            | 70   | -   | dB   |

| IMD2   | second-order intermodulation | $f_i 1 = 21 \text{ MHz};$<br>$f_i 2 = 22 \text{ MHz}$              | <u>[8]</u> _ | -89  | -   | dBFS |

|        | distortion                   | $f_i 1 = 91.5 \text{ MHz};$<br>$f_i 2 = 94.5 \text{ MHz}$          | -            | -86  | -   | dBFS |

|        |                              | $f_i 1 = 174 \text{ MHz};$<br>$f_i 2 = 176 \text{ MHz}$            | -            | -83  | -   | dBFS |

| IMD3   | third-order intermodulation  | $f_i 1 = 21 \text{ MHz};$<br>$f_i 2 = 22 \text{ MHz}$              | <u>[8]</u> _ | -88  | -   | dBFS |

|        | distortion                   | $f_i 1 = 91.5 \text{ MHz};$<br>$f_i 2 = 93.5 \text{ MHz}$          | -            | -82  | -   | dBFS |

|        |                              | f <sub>i</sub> 1 = 174 MHz;<br>f <sub>i</sub> 2 = 176 MHz          | -            | -83  | -   | dBFS |

- [1] The circuit has two clock inputs: CLK and CLKN. There are 5 modes of operation:

- a) PECL mode 1: (DC levels vary 1:1 with  $V_{CCD}$ ) CLK and CLKN inputs are at differential PECL levels.

- b) PECL mode 2: (DC levels vary 1:1 with V<sub>CCD</sub>) CLK input is at PECL level and sampling is taken on the falling edge of the clock input signal. A DC level of 3.65 V has to be applied on CLKN decoupled to GND via a 100 nF capacitor.

- c) PECL mode 3: (DC levels vary 1:1 with V<sub>CCD</sub>) CLKN input is at PECL level and sampling is taken on the rising edge of the clock input signal. A DC level of 3.65 V has to be applied on CLK decoupled to GND via a 100 nF capacitor.

- d) Differential AC driving mode 4: When driving the CLK input directly and with any AC signal of minimum 1 V (p-p) and with a DC level of 2.5 V, the sampling takes place at the falling edge of the clock signal. When driving the CLKN input with the same signal, sampling takes place at the rising edge of the clock signal. It is recommended to decouple the CLKN or CLK input to DGND via a 100 nF capacitor.

- e) TTL mode 5: CLK input is at TTL level and sampling is taken on the falling edge of the clock input signal. In that case CLKN pin has to be connected to the ground.

- [2] Guaranteed by design.

- [3] The ADC input range can be adjusted with an external reference connected to pin FSIN. This voltage has to be referenced to V<sub>CCA</sub>.

- [4] Output data acquisition: the output data is available after the maximum delay of t<sub>d(o)</sub>.

- [5] The –3 dB analog bandwidth is determined by the 3 dB reduction in the reconstructed output, the input being a full-scale sine wave.

- [6] The total harmonic distortion is obtained with the addition of the first five harmonics.

- [7] The signal-to-noise ratio takes into account all harmonics above five and noise up to Nyquist frequency.

- [8] Intermodulation measured relative to either tone with analog input frequencies f<sub>i</sub> 1 and f<sub>i</sub> 2. The two input signals have the same amplitude and the total amplitude of both signals provides full-scale to the converter (–6 dB below full-scale for each input signal). IMD3 is the ratio of the RMS value of either input tone to the RMS value of the worst case third order intermodulation product; IMD2 is the ratio of the RMS value of either input tone to the RMS value of the worst case second order intermodulation product.

## 10. Additional information relating to Table 5

Table 6. Output coding with differential inputs

$V_{i(IN)} - V_{i(INN)} = 1.9 \text{ V}; V_{ref(fs)} = V_{CCA1} - 1.87 \text{ V}; \text{ typical values to AGND.}$

| Code         | V <sub>i(IN)</sub> (V) | V <sub>i(INN)</sub> (V) | IR           | Binary outputs<br>(D11 to D0) | Two's complement outputs (D11 to D0) |

|--------------|------------------------|-------------------------|--------------|-------------------------------|--------------------------------------|

| Underflow    | < 2.675                | > 3.625                 | 0            | 0000 0000 0000                | 1000 0000 0000                       |

| 0            | 2.675                  | 3.625                   | 1            | 0000 0000 0000                | 1000 0000 0000                       |

| 1            | -                      | -                       | 1            | 0000 0000 0001                | 1000 0000 0001                       |

| $\downarrow$ | $\downarrow$           | $\downarrow$            | $\downarrow$ | $\downarrow$                  | $\downarrow$                         |

| 2047         | 3.15                   | 3.15                    | 1            | 0111 1111 1111                | 1111 1111 1111                       |

| $\downarrow$ | $\downarrow$           | $\downarrow$            | $\downarrow$ | $\downarrow$                  | $\downarrow$                         |

| 4094         | -                      | -                       | 1            | 1111 1111 1110                | 0111 1111 1110                       |

| 4095         | 3.625                  | 2.675                   | 1            | 1111 1111 1111                | 0111 1111 1111                       |

| Overflow     | > 3.625                | < 2.675                 | 0            | 1111 1111 1111                | 0111 1111 1111                       |

Table 7. Mode selection

| Two's complement output (OTC) | Chip enable input (CE_N) | Data output (D0 to D11; IR) |

|-------------------------------|--------------------------|-----------------------------|

| 0                             | 0                        | binary; active              |

| 1                             | 0                        | two's complement; active    |

| X[1]                          | 1                        | high-impedance              |

[1] X = don't care.

The ADC1207S080 allows modifying the ADC full-scale. This could be done with FSIN (full-scale input) according to Figure 5.

The ADC1207S080 generates an adjustable clock output called Complete Conversion Signal (CCS), which can be used to control the acquisition of converted output data by the digital circuit connected to the ADC1207S080 output data bus. Two logic inputs, DEL0 and DEL1 pins, allow adjusting the delay of the edge of the CCS signal to achieve an optimal position in the stable, usable zone of the data.

Table 8. Complete conversion signal selection

| DEL1 | DEL0 | CCS output                   |

|------|------|------------------------------|

| 0    | 0    | high-impedance               |

| 0    | 1    | active, typical delay 0.3 ns |

| 1    | 0    | active, typical delay 1.3 ns |

| 1    | 1    | active, typical delay 2.3 ns |

#### 11. Definitions

#### 11.1 Static parameters

#### 11.1.1 Integral Non-Linearity (INL)

It is defined as the deviation of the transfer function from a best fit straight line (linear regression computation). The INL of the code i is obtained from the equation:

$$INL(i) = \frac{V_i(i) - V_i(ideal)}{S}$$

where: S corresponds to the slope of the ideal straight line (code width); i corresponds to the code value;  $V_i$  is the input voltage.

#### 11.1.2 Differential Non-Linearity (DNL)

It is the deviation in code width from the value of 1 LSB.

$$DNL(i) = \frac{V_i(i+1) - V_i(i)}{S}$$

where:  $V_i$  is the input voltage; i from 0 to  $(2^n - 2)$ .

#### 11.2 Dynamic parameters

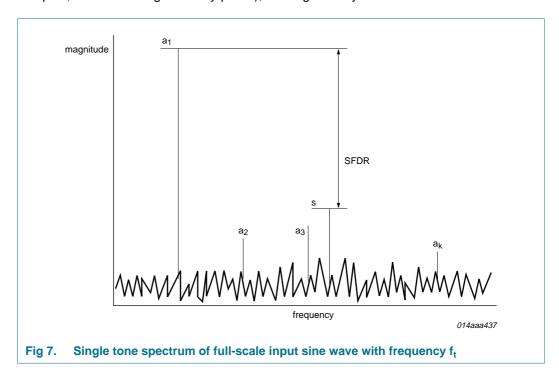

<u>Figure 7</u> shows the spectrum of a single tone full-scale input sine wave with frequency f, conforming to coherent sampling ( $f/f_s = M/N$ , with M number of cycles and N number of samples, M and N being relatively prime), and digitized by the ADC under test.

**Remark:** In the following equations, P<sub>noise</sub> is the power of the terms which include the effects of random noise, non-linearities, sampling time errors, and 'quantization noise'.

#### 11.2.1 Signal-to-Noise And Distortion (SINAD)

The ratio of the output signal power to the noise plus distortion power for a given sample rate and input frequency, excluding the DC component:

$$SINAD[dB] = 10log_{10} \left( \frac{P_{signal}}{P_{noise + distortion}} \right)$$

#### 11.2.2 Effective Number Of Bits (ENOB)

It is derived from SINAD and gives the theoretical resolution an ideal ADC would require to obtain the same SINAD measured on the real ADC. A good approximation gives:

$$ENOB = \frac{SINAD - 1.76}{6.02}$$

#### 11.2.3 Total Harmonic Distortion (THD)

The ratio of the power of the harmonics to the power of the fundamental. For k-1 harmonics the THD is:

$$THD[dB] = 10log_{10} \left( \frac{P_{harmonics}}{P_{signal}} \right)$$

where:

$$P_{harmonics} = \alpha_2^2 + \alpha_3^2 + \dots + \alpha_k^2$$

$$P_{signal} = \alpha_1^2$$

The value of k is usually 6 (i.e. calculation of THD is done on the first 5 harmonics).

#### 11.2.4 Signal-to-Noise ratio (S/N)

The ratio of the output signal power to the noise power, excluding the harmonics and the DC component is:

$$S/N[dB] = 10log_{10} \left(\frac{P_{signal}}{P_{noise}}\right)$$

#### 11.2.5 Spurious Free Dynamic Range (SFDR)

The number SFDR specifies available signal range as the spectral distance between the amplitude of the fundamental and the amplitude of the largest spurious harmonic and non-harmonic, excluding DC component:

$$SFDR[dB] = 20log_{10}\left(\frac{\alpha_1}{max(S)}\right)$$

#### 11.2.6 IMD2 (IMD3)

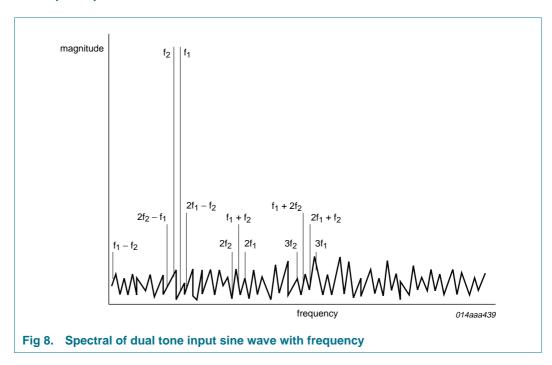

From a dual tone input sinusoid ( $f_{t1}$  and  $f_{t2}$ , these frequencies being chosen according to the coherence criterion), the intermodulation distortion products IMD2 and IMD3 (respectively, 2nd and 3rd order components) are defined, as follows.

The ratio of the RMS value of either tone to the RMS value of the worst second (third) order intermodulation product.

The total InterModulation Distortion (IMD) is given by:

$$IMD[dB] = 10log_{10} \left( \frac{P_{intermod}}{P_{sional}} \right)$$

where:

$$\begin{split} P_{intermod} &= \alpha_{im(f_{tl}-f_{t2})}^2 - \alpha_{im(f_{tl}+f_{t2})}^2 + \alpha_{im(f_{tl}-2f_{t2})}^2 + \alpha_{im(f_{tl}+2f_{t2})}^2 + \dots \\ &\qquad \dots + \alpha_{im(2f_{tl}-f_{t2})}^2 + \alpha_{im(2f_{tl}+f_{t2})}^2 \end{split}$$

with  $\alpha_{lm(f_{tl})}^2$  corresponding to the power in the intermodulation component at frequency  $f_t$ .

$$P_{signal} = \alpha_{f_{tl}}^2 + \alpha_{f_{t2}}^2$$

## 12. Application information

#### 12.1 ADC1207S080 in 3G radio receivers

The ADC1207S080 has been proven in many 3G radio receivers with various operating conditions regarding Input Frequency (IF), signal IF bandwidth and sampling frequency. The ADC1207S080 is provided with a maximum analog input signal frequency of 400 MHz. It allows a significant cost-down of the RF front-end, from two mixers to only one, even in multi-carriers architecture.

Table 9 describes some possible applications with the ADC1207S080 in high IF sampling mode.

| Table 9.             | . Examples of possible i <sub>i</sub> , i <sub>clk</sub> , if bw combinations supported |                |          |            |  |

|----------------------|-----------------------------------------------------------------------------------------|----------------|----------|------------|--|

| f <sub>i</sub> (MHz) | f <sub>clk</sub> (MHz)                                                                  | IF BW (MHz)[1] | SNR (dB) | SFDR (dBc) |  |

| 350                  | 80                                                                                      | 5.00           | 65       | 71         |  |

| 243.95               | 9.60                                                                                    | 0.25           | 71       | 80         |  |

| 96                   | 76.80                                                                                   | 1.60           | 72       | 76         |  |

| 96                   | 76.80                                                                                   | 4.80           | 71       | 77         |  |

| 96                   | 76.80                                                                                   | 20.00          | 68       | 76         |  |

| 80                   | 61.44                                                                                   | 10.00          | 70       | 85         |  |

| 78.4                 | 44.80                                                                                   | 3.50           | 71       | 76         |  |

| 70                   | 40.00                                                                                   | 1.25           | 72       | 79         |  |

Table 0 Examples of possible f | IE RW combinations supported

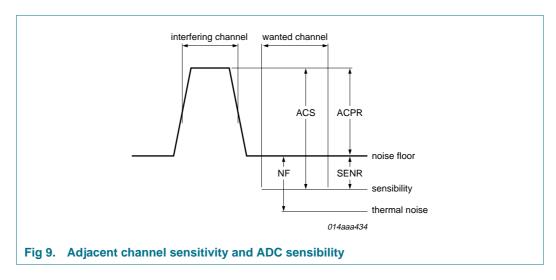

For a dual carrier Wideband-Code-Division-Multiple-Access (W-CDMA) receiver, the most important parameters are sensitivity and Adjacent Channel Selectivity (ACS). The sensitivity is defined as the lowest detectable signal level. In W-CDMA, it can be far below the noise floor. This difference, between the sensitivity and the noise floor, is defined by the Sensitivity-to-Noise Ratio (SENR). Its value is negative due to the gain processing. The Adjacent Channel Power Ratio (ACPR) is the difference between the full-scale -3 dB peak and the noise floor. It represents the ratio of the adjacent-channel power and the average power level of the channel. The ACS is defined by the sum of SENR and ACPR.

<sup>[1]</sup> IF bandwidth corresponds to the observed area on the ADC output spectrum.

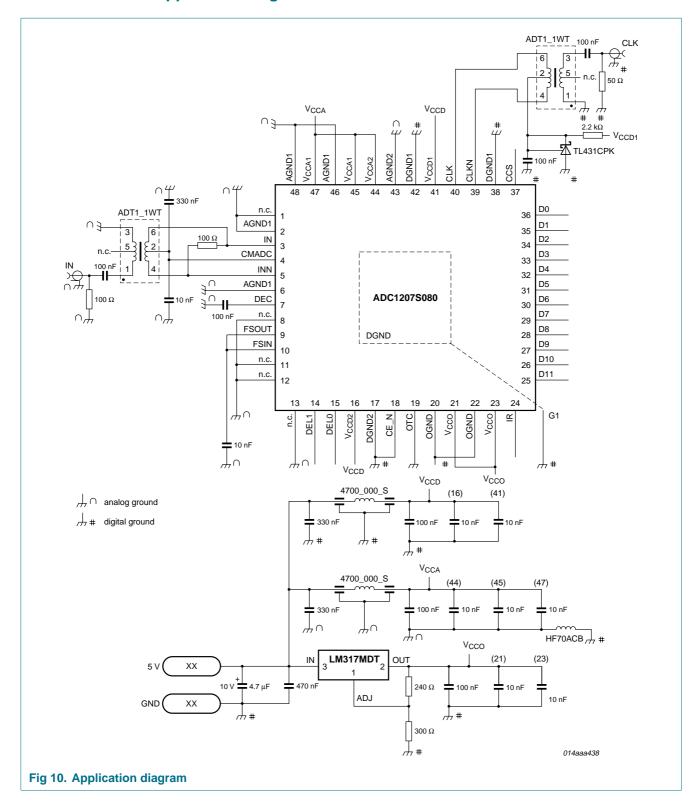

## 12.2 Application diagram

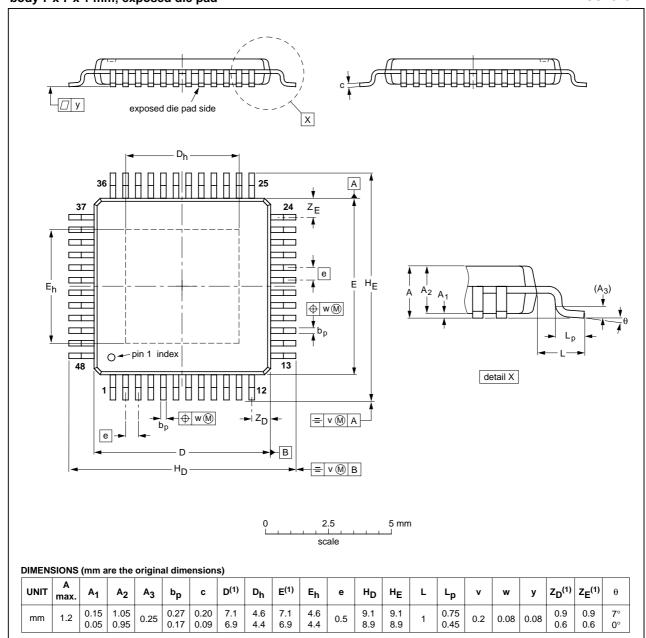

## 13. Package outline

# HTQFP48: plastic thermal enhanced thin quad flat package; 48 leads; body 7 x 7 x 1 mm; exposed die pad

SOT545-2

#### Note

1. Plastic or metal protrusions of 0.25 mm maximum per side are not included.

| OUTLINE  | REFERENCES |        |       | EUROPEAN | ISSUE DATE |                                  |

|----------|------------|--------|-------|----------|------------|----------------------------------|

| VERSION  | IEC        | JEDEC  | JEITA |          | PROJECTION | ISSUE DATE                       |

| SOT545-2 |            | MS-026 |       |          |            | <del>-03-04-07</del><br>04-01-29 |

Fig 11. Package outline SOT545-2 (HTQFP48)

ADC1207S080\_2 © NXP B.V. 2008. All rights reserved.

ADC1207S080

## Single 12 bits ADC, up to 80 MHz with direct/ultra high IF sampling

## 14. Revision history

#### Table 10. Revision history

| Document ID                                                                                                           | Release date                                                               | Data sheet status  | Change notice | Supersedes    |  |

|-----------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|--------------------|---------------|---------------|--|

| ADC1207S080_2                                                                                                         | 20080807                                                                   | Product data sheet | -             | ADC1207S080_1 |  |

| Modifications: • Corrections made to version number in <u>Table 1</u> .                                               |                                                                            |                    |               |               |  |

|                                                                                                                       | <ul> <li>Corrections made to several entries in <u>Table 5</u>.</li> </ul> |                    |               |               |  |

| <ul> <li>Corrections made to alignment in <u>Figure 10</u>.</li> <li>Corrections made to <u>Figure 11</u>.</li> </ul> |                                                                            |                    |               |               |  |

|                                                                                                                       |                                                                            |                    |               |               |  |

| ADC1207S080_1                                                                                                         | 20080611                                                                   | Product data sheet | -             | -             |  |

## 15. Legal information

#### 15.1 Data sheet status

| Document status[1][2]          | Product status[3] | Definition                                                                            |

|--------------------------------|-------------------|---------------------------------------------------------------------------------------|

| Objective [short] data sheet   | Development       | This document contains data from the objective specification for product development. |

| Preliminary [short] data sheet | Qualification     | This document contains data from the preliminary specification.                       |

| Product [short] data sheet     | Production        | This document contains the product specification.                                     |

- [1] Please consult the most recently issued document before initiating or completing a design.

- [2] The term 'short data sheet' is explained in section "Definitions"

- [3] The product status of device(s) described in this document may have changed since this document was published and may differ in case of multiple devices. The latest product status information is available on the Internet at URL http://www.nxp.com.

#### 15.2 Definitions

Draft — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.

Short data sheet — A short data sheet is an extract from a full data sheet with the same product type number(s) and title. A short data sheet is intended for quick reference only and should not be relied upon to contain detailed and full information. For detailed and full information see the relevant full data sheet, which is available on request via the local NXP Semiconductors sales office. In case of any inconsistency or conflict with the short data sheet, the full data sheet shall prevail.

#### 15.3 Disclaimers

**General** — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information.

Right to make changes — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

**Suitability for use** — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in medical, military, aircraft, space or life support equipment, nor in applications where failure or

malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors accepts no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Limiting values — Stress above one or more limiting values (as defined in the Absolute Maximum Ratings System of IEC 60134) may cause permanent damage to the device. Limiting values are stress ratings only and operation of the device at these or any other conditions above those given in the Characteristics sections of this document is not implied. Exposure to limiting values for extended periods may affect device reliability.

Terms and conditions of sale — NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at <a href="http://www.nxp.com/profile/terms">http://www.nxp.com/profile/terms</a>, including those pertaining to warranty, intellectual property rights infringement and limitation of liability, unless explicitly otherwise agreed to in writing by NXP Semiconductors. In case of any inconsistency or conflict between information in this document and such terms and conditions, the latter will prevail.

**No offer to sell or license** — Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights.

#### 15.4 Trademarks

Notice: All referenced brands, product names, service names and trademarks are the property of their respective owners.

#### 16. Contact information

For more information, please visit: http://www.nxp.com

For sales office addresses, please send an email to: <a href="mailto:salesaddresses@nxp.com">salesaddresses@nxp.com</a>

#### 17. Contents

| 1      | General description                        | 1    |

|--------|--------------------------------------------|------|

| 2      | Features                                   | 1    |

| 3      | Applications                               | 2    |

| 4      | Ordering information                       | 2    |

| 5      | Block diagram                              | 2    |

| 6      | Pinning information                        |      |

| 6.1    | Pinning                                    |      |

| 6.2    | Pin description                            |      |

| 7      | Limiting values                            | 5    |

| 8      | Thermal characteristics                    |      |

| 9      | Characteristics                            | 6    |

| 10     | Additional information relating to Table 5 | . 10 |

| 11     | Definitions                                |      |

| 11.1   | Static parameters                          | . 13 |

| 11.1.1 | Integral Non-Linearity (INL)               | . 13 |

| 11.1.2 | Differential Non-Linearity (DNL)           |      |

| 11.2   | Dynamic parameters                         | . 13 |

| 11.2.1 | SIgnal-to-Noise And Distortion (SINAD)     |      |

| 11.2.2 | Effective Number Of Bits (ENOB)            |      |

| 11.2.3 | Total Harmonic Distortion (THD)            |      |

| 11.2.4 | Signal-to-Noise ratio (S/N)                |      |

| 11.2.5 | Spurious Free Dynamic Range (SFDR)         |      |

| 11.2.6 | IMD2 (IMD3)                                |      |

| 12     | Application information                    |      |

| 12.1   | ADC1207S080 in 3G radio receivers          |      |

| 12.2   | Application diagram                        |      |

| 13     | Package outline                            |      |

| 14     | Revision history                           |      |

| 15     | Legal information                          |      |

| 15.1   | Data sheet status                          | . 20 |

| 15.2   | Definitions                                | _    |

| 15.3   | Disclaimers                                |      |

| 15.4   | Trademarks                                 |      |

| 16     | Contact information                        | . 20 |

| 17     | Contents                                   | . 21 |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in section 'Legal information'.

# **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

NXP:

ADC1207S080HW/C2,5