### **Description**

AP9050 is designed to protect the latest generation of PMICs for portable applications such as UMPCs, smartphones and others utilizing battery power.

The integrated LDO allows the PMIC to power up and determine whether the connected power supply (USB or AC-DC wall adapter) is valid and a safe operation can be performed.

The PMIC controls the operation of the integrated n-channel MOSFET to either pass the line voltage or disconnect the line from the PMIC to protect its internal circuits in the event of an over-voltage.

The AP9050 is available in a low-profile U-DFN2020-6 package.

### **Pin Assignments**

#### (Top View)

U-DFN2020-6

### **Features**

- Input Supply Range from 3V to 30V

- Lower Power Dissipation and Higher Efficiency as compared to a Zener Shunt Regulator

- LDO is stable without a bypass capacitor on the output and operates across the temperature range

- Available in a U-DFN2020-6 package with a typical height of 0.575mm

### Applications

- Power Interface for New Generation PMICs

- Charger Front End Protection

- Smartphone

- Cell Phone

- Ultra Mobile PC

- Tablets

Note: 1. EU Directive 2002/95/EC (RoHS). All applicable RoHS exemptions applied. Please visit our website at http://www.diodes.com/products/lead\_free.html.

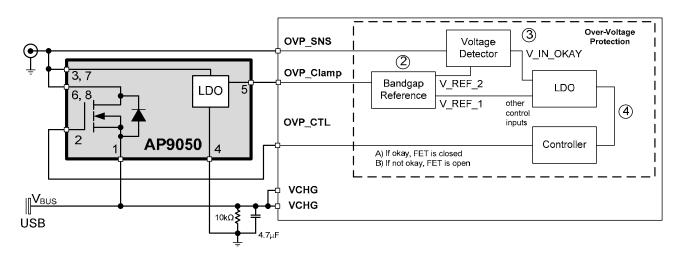

## **Typical Application Circuit**

Figure 1. Typical Application Circuit

## **Pin Descriptions**

| Pin# | Name             | Description                                                  |  |

|------|------------------|--------------------------------------------------------------|--|

| 1    | Source           | Source of the n-channel power FET. Pass-switch's output pin. |  |

| 2    | Gate             | Sate of the FET switch. Pass-switch's control pin.           |  |

| 3, 7 | $V_{IN}$         | nput voltage to the internal LDO.                            |  |

| 4    | Ground           | DO ground connection.                                        |  |

| 5    | V <sub>OUT</sub> | Output of the LDO.                                           |  |

| 6, 8 | Drain            | Drain of the power FET. Pass-switch's input pin.             |  |

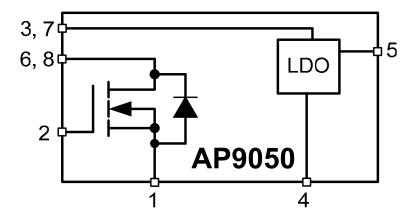

## **Functional Block Diagram**

Figure 2. Functional Block Diagram

## **Absolute Maximum Ratings (Note 2, 3)**

| Symbol           | Parameter                                       | Rating      | Unit  |  |

|------------------|-------------------------------------------------|-------------|-------|--|

| $V_{IN}$         | Supply Voltage                                  | -0.3 to 30  | V     |  |

| $V_{GS}$         | Gate-to-Source Voltage                          | ±12         | V     |  |

| I <sub>Dpk</sub> | Drain Current, Peak (10µs pulse)                | 19          | А     |  |

|                  | Drain Current, Continuous                       |             |       |  |

| 1-               | (Note 4, Steady-State)                          | 3.7         | Α     |  |

| I <sub>D</sub>   | $T_A = 25^{\circ}C$                             | 2.7         | A     |  |

|                  | $T_A = 85^{\circ}C$                             |             |       |  |

| P <sub>max</sub> | Total Power Dissipation @ T <sub>A</sub> = 25°C | 750         | mW    |  |

| гтах             | (Note 3, 4)                                     | 750         | IIIVV |  |

| $T_J$            | Junction Temperature Range                      | -40 to +125 | °C    |  |

| $T_J$            | Non-operating Temperature Range                 | −55 to +150 | °C    |  |

| TL               | Maximum Lead Temperature for Soldering          | 260         | °C    |  |

| 1 [              | Purposes                                        | 200         |       |  |

Semiconductor devices are ESD sensitive and may be damaged by exposure to ESD events. Suitable ESD precautions should be taken when handling and transporting these devices.

- 2. Exceeding these ratings may damage the device.

- 3. Mounted on FR4 Board using 30 mm<sup>2</sup>, 2 oz Cu.

4. Dual die operation (equally-heated).

### **Thermal Resistance**

| Symbol Parameter |                              | Rating | Unit |  |

|------------------|------------------------------|--------|------|--|

| $\theta_{JA}$    | Junction to Ambient (Note 5) | 132    | °C/W |  |

| $\theta_{JC}$    | Junction to Case             | 13     | °C/W |  |

Note: 5. Test condition for DFN2020-6: Mounted on FR4 Board using 30 mm<sup>2</sup>, 2 oz Cu.

## **Recommended Operating Conditions (Note 6)**

| Symbol         | Parameter                           | Min | Max | Unit |

|----------------|-------------------------------------|-----|-----|------|

| $V_{IN}$       | Supply Voltage                      | 3   | 30  | ٧    |

| T <sub>A</sub> | Operating Ambient Temperature Range | -40 | +85 | °C   |

Note: 6. The device function is not guaranteed outside of the recommended operating conditions.

## Electrical Characteristics (V<sub>IN</sub> (OVP\_SENSE) = 5.0V, T<sub>J</sub> = +25°C, unless otherwise noted)

| Symbol              | Parameter                                               | Test Conditions                                                                         | Min  | Тур.     | Max       | Unit |

|---------------------|---------------------------------------------------------|-----------------------------------------------------------------------------------------|------|----------|-----------|------|

| Power FET           | •                                                       |                                                                                         |      |          |           |      |

| I <sub>DSS</sub>    | Zero Gate Voltage Drain Current                         | $V_{DS} = 24V, V_{GS} = 0V$<br>$T_{J} = 85^{\circ}C$                                    |      |          | 1.0<br>10 | μΑ   |

| I <sub>GSS</sub>    | Gate-to-Source Leakage Current                          | $V_{DS} = 0V, V_{GS} = \pm 8V$                                                          |      |          | 80        | nA   |

| $V_{GS(th)}$        | Gate Threshold Voltage                                  | $V_{GS} = V_{DS}, I_D = 250 \mu A$                                                      | 0.62 | 0.9      | 1.2       | V    |

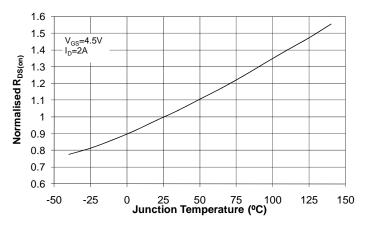

| R <sub>DS(on)</sub> | Drain-to-Source On-Resistance (Note 7)                  | $V_{GS} = 4.5V, I_D = 2.0A$<br>$V_{GS} = 2.5V, I_D = 2.0A$                              |      | 41<br>55 | 53<br>68  | mΩ   |

| 9FS                 | Forward Transconductance                                | V <sub>DS</sub> = 5V, ID = 2.0A                                                         |      | 8        |           | S    |

| C <sub>ISS</sub>    | Input Capacitance                                       | $V_{DS} = 15V, V_{GS} = 0V,$<br>f = 1MHz                                                |      | 500      |           | pF   |

| Coss                | Output Capacitance                                      | $V_{DS} = 15V, V_{GS} = 0V,$<br>f = 1MHz                                                |      | 65       |           | pF   |

| C <sub>RSS</sub>    | Reverse Transfer Capacitance                            | $V_{DS} = 15V, V_{GS} = 0V,$<br>f = 1MHz                                                |      | 50       |           | pF   |

| LDO (unless         | s otherwise noted, $T_J = 25^{\circ}C$ , $V_{IN} = 5.0$ | OV)                                                                                     |      |          |           |      |

| V <sub>OUT</sub>    | Regulated Output Voltage                                | V <sub>IN</sub> = 5.5V, I <sub>OUT</sub> = 1mA                                          | 4.6  | 5.0      | 5.3       | V    |

| V                   | Headroom                                                | $V_{IN} - V_{OUT}$ , $I_{OUT} = 1.2$ mA,<br>$V_{IN} = 4.6$ V                            |      |          | 150       | mV   |

| $V_{head}$          | Headroom                                                | $V_{IN} - V_{OUT}$ , $I_{OUT} = 10$ mA,<br>$V_{IN} = 4.8$ V, $T_{J} = -40$ to $+125$ °C |      |          | 1000      | mV   |

| Response to         | Input Transient                                         |                                                                                         |      |          |           |      |

| t <sub>pulse</sub>  | Time signal is above 5.5V                               | $V_{IN}$ 0 to 30V, < 1μs rise time, 5.0kΩ resistive load (Note 8)                       |      |          | 5.0       | μs   |

| $V_{pk}$            | Peak Voltage                                            | $V_{IN}$ 0 to 30V, < 1μs rise time, 5.0kΩ resistive load (Note 8)                       |      |          | 9.0       | V    |

| Total Devic         | e                                                       |                                                                                         |      |          |           |      |

| I <sub>bias</sub>   | Input Bias Current                                      | V <sub>IN</sub> = 5.5V                                                                  |      | 110      | 850       | μA   |

| $V_{IN\_min}$       | Minimum Operating Voltage                               |                                                                                         |      |          | 3.0       | V    |

Notes:

- 7. Pulse test width 300µs, duty cycle 2%

- 8. Guaranteed by design

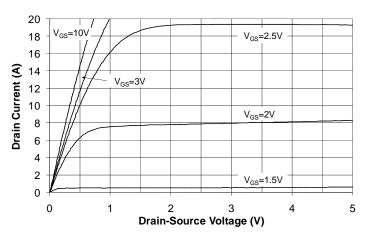

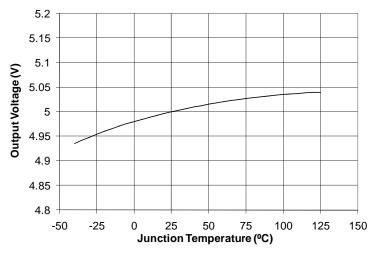

## **Typical Performance Characteristics**

Figure 3. R<sub>DS(ON)</sub> variation over junction temperature

Figure 4. R<sub>DS(ON)</sub> Characteristics

Figure 5. Output voltage variation over junction temperature

### **Applications Information**

### **Theory of Operation**

The AP9050 was designed to work in close relationship with a PMIC (Power Management IC). To protect the PMIC from an overvoltage situation the AP9050 powers up a detection circuit within the connected PMIC. (See Figure 2 as reference)

This detection circuit determines if a valid input source is connected (ex.  $V_{IN}$  < 8V). If a valid input source is detected the power MOSFET will be turned on and the supply current to the PMIC will be turned on. The overvoltage detection is continuous, if an overvoltage occurs at a later state the Power MOSFET will be turned off.

### **PCB Layout**

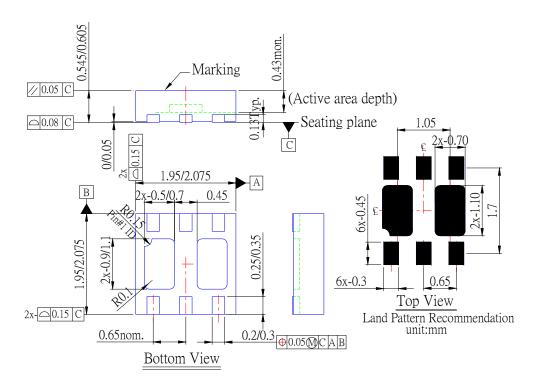

The AP9050 was designed utilizing two process technologies to provide best performance and a cost effective solution.

Figure 6. Package Pin Out

Both die are packaged side by side in the U-DFN2020-6 package and are mounted on two separate exposed pads. These pads are not required for electrical functionality, but to aid with the thermal performance of AP9050.

Attention should be paid in the layout of the PCB (Printed Circuit Board) that PAD7 is connected to  $V_{\text{IN}}$  of the LDO, pin 3, while PAD8 is connected to the Drain of the Power MOSFET, pin 6 of the package. For best thermal performance large copper areas connected to the two exposed pads should be used to transfer heat away from the AP9050.

### **External Capacitors**

AP9050 was specified to reduce board space and external component count, by designing the LDO to be stable without an external bypass capacitor.

A low ESR 1nF to 10nF external capacitor can be used to improve behavior with fast ac transients or other switching currents that might be present.

To improve noise immunity and ac impedance from long input traces a 1nF capacitor can be added to the input  $V_{\text{IN}}$  of the LDO.

## **Ordering Information**

|   | Device      | Package | Packaging   | 7" Tape and Reel |                    |  |

|---|-------------|---------|-------------|------------------|--------------------|--|

|   | Device      | Code    | (Note 10)   | Quantity         | Part Number Suffix |  |

| 3 | AP9050FDB-7 | FDB     | U-DFN2020-6 | 3000/Tape & Reel | -7                 |  |

Pad layout as shown on Diodes Inc. suggested pad layout document AP02001, which can be found on our website at http://www.diodes.com/datasheets/ap02001.pdf.

## **Marking Information**

### U-DFN2020-6

## (Top View)

XX: Identification Code

<u>Y</u> : Year : 0~9

<u>W</u>: Week: A~Z: 1~26 week; a~z: 27~52 week; z represents

52 and 53 week X: A~Z: Internal code

| Device    | Package     | Identification Code |

|-----------|-------------|---------------------|

| AP9050FDB | U-DFN2020-6 | BZ                  |

## Package Outline Dimensions (All Dimensions in mm)

### U-DFN2020-6

#### **IMPORTANT NOTICE**

DIODES INCORPORATED MAKES NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARDS TO THIS DOCUMENT, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION).

Diodes Incorporated and its subsidiaries reserve the right to make modifications, enhancements, improvements, corrections or other changes without further notice to this document and any product described herein. Diodes Incorporated does not assume any liability arising out of the application or use of this document or any product described herein; neither does Diodes Incorporated convey any license under its patent or trademark rights, nor the rights of others. Any Customer or user of this document or products described herein in such applications shall assume all risks of such use and will agree to hold Diodes Incorporated and all the companies whose products are represented on Diodes Incorporated website, harmless against all damages.

Diodes Incorporated does not warrant or accept any liability whatsoever in respect of any products purchased through unauthorized sales channel.

Should Customers purchase or use Diodes Incorporated products for any unintended or unauthorized application, Customers shall indemnify and hold Diodes Incorporated and its representatives harmless against all claims, damages, expenses, and attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized application.

Products described herein may be covered by one or more United States, international or foreign patents pending. Product names and markings noted herein may also be covered by one or more United States, international or foreign trademarks.

#### LIFE SUPPORT

Diodes Incorporated products are specifically not authorized for use as critical components in life support devices or systems without the express written approval of the Chief Executive Officer of Diodes Incorporated. As used herein:

- A. Life support devices or systems are devices or systems which:

- 1. are intended to implant into the body, or

- 2. support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in significant injury to the user.

- B. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or to affect its safety or effectiveness.

Customers represent that they have all necessary expertise in the safety and regulatory ramifications of their life support devices or systems, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of Diodes Incorporated products in such safety-critical, life support devices or systems, notwithstanding any devices- or systems-related information or support that may be provided by Diodes Incorporated. Further, Customers must fully indemnify Diodes Incorporated and its representatives against any damages arising out of the use of Diodes Incorporated products in such safety-critical, life support devices or systems.

Copyright © 2011, Diodes Incorporated

www.diodes.com