**DATA SHEET**

# SKY73134-11: Wideband PLL Frequency Synthesizer

## Applications

- Cellular base station systems: GSM/EDGE, CDMA2000, WCDMA, TD-SCDMA, LTE

- Other wireless communication systems

## Features

- Continuous frequency coverage: 0.35 to 6.2 GHz

- Integer-N frequency synthesizer

- Low phase noise VCO

- Four integrated VCOs with automatic digital frequency calibration

- Automatic VCO selection based on the target RF output

- Programmable VCO division by 1, 2, 3, 4, or 8

- VCO divide-by-three with 50% duty cycle

- Integrated input/output RF buffer

- Device provides both divided and direct VCO outputs

- Programmable RF output power levels

- Low RF output comparison spurs

- Programmable 18-bit N-counter and 11-bit R-counter

- Dual modulus 7 GHz prescaler (selectable 16/17 or 32/33)

- Programmable charge pump current

- Flexible configuration allows connection to external VCO or PLL

- Bidirectional read/write three-wire serial to parallel interface

- Digital lock detect

- Digital output used as a loop filter component switch

- Optional adjustment of the core, divider, and charge pump current by external resistor

- Power supply: 3.3 V

- Small, RFLGA (32-pin, 5 x 5 mm) package (MSL3, 260 °C per JEDEC J-STD-020)

Skyworks Pb-free products are compliant with all applicable legislation. For additional information, refer to *Skyworks Definition of Lead (Pb)-Free*, document number SQ04-0073.

## Description

The SKY73134-11 is a wideband integer-N frequency synthesizer with an approximately 6 GHz locking range.

The device includes four differential Voltage Controlled Oscillators (VCOs), which cover the output frequency range from 2.8 GHz to 6.2 GHz. By applying internal VCO division by 1, 2, 3, 4, or 8, the output frequency range can be increased from 0.35 GHz to 6.2 GHz, monitored at the RF output.

The direct, non-divided internal VCO frequency can also be monitored at the bidirectional VCO pins. The VCO selection can be automatic based on the target RF output. The flexible SKY73134-11 configuration allows the loop to be locked by an external VCO or external Phase Locked Loop (PLL), or the device can use the divider chain only. The SKY73134-11 is controlled by a bidirectional read/write serial to parallel interface.

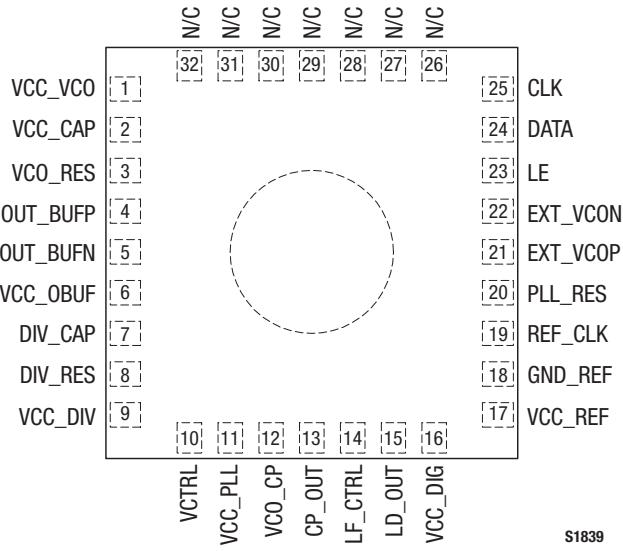

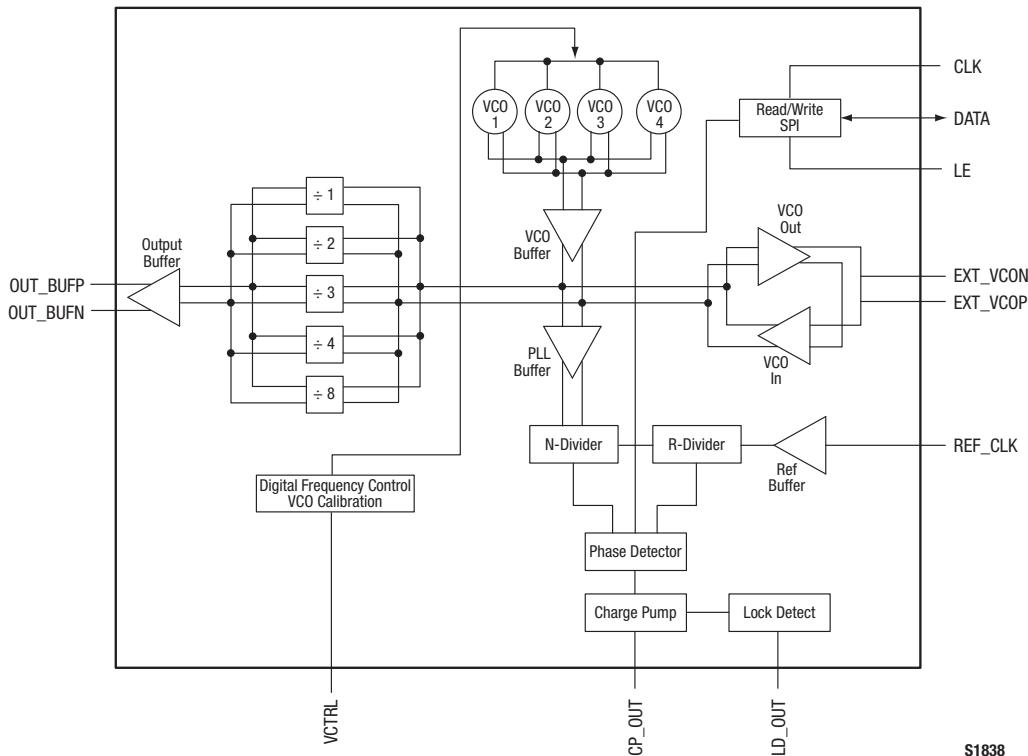

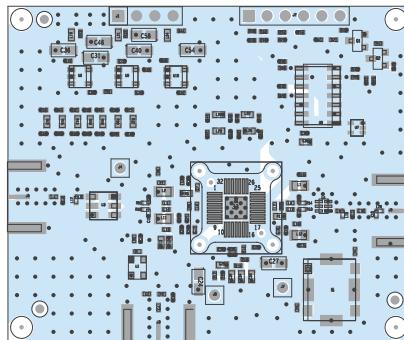

The SKY73134-11 frequency synthesizer is manufactured with a BiCMOS 0.18  $\mu$ m SiGe process and provided in a compact, 32-pin RF Land Grid Array (RFLGA). The pin configuration and package are shown in Figure 1. A functional block diagram is shown in Figure 2. Signal pin assignments and functional pin descriptions are provided in Table 1.

**Figure 1. SKY73134-11 Pinout – 32-Pin RFLGA (Top View)**

S1839

Figure 2. SKY73134-11 Block Diagram

Table 1. SKY73134-11 Signal Descriptions

| Pin # | Name     | Description                                                          | Pin # | Name     | Description                                          |

|-------|----------|----------------------------------------------------------------------|-------|----------|------------------------------------------------------|

| 1     | VCC_VCO  | Supply for VCO                                                       | 17    | VCC_REF  | Supply for reference buffer                          |

| 2     | VCC_CAP  | External capacitor for VCO bias connected to VCC_VCO pin             | 18    | GND_REF  | Reference buffer ground                              |

| 3     | VCO_RES  | External 15 kΩ resistor to set VCO bias                              | 19    | REF_CLK  | Reference clock input                                |

| 4     | OUT_BUFP | Positive LO output                                                   | 20    | PLL_RES  | External 20 kΩ resistor for the PLL/charge pump bias |

| 5     | OUT_BUFN | Negative LO output                                                   | 21    | EXT_VCOP | Positive, external VCO input                         |

| 6     | VCC_OBUF | Supply for output buffer                                             | 22    | EXT_VCON | Negative, external VCO input                         |

| 7     | DIV_CAP  | External capacitor for the divider bias connected to the VCC_DIV pin | 23    | LE       | Latch enable input for the SPI                       |

| 8     | DIV_RES  | External 60 kΩ resistor to set the divider bias                      | 24    | DATA     | Data input for the SPI                               |

| 9     | VCC_DIV  | Supply for dividers                                                  | 25    | CLK      | Clock input for the SPI                              |

| 10    | VCTRL    | VCO tuning voltage                                                   | 26    | N/C      | No connection                                        |

| 11    | VCC_PLL  | PLL supply                                                           | 27    | N/C      | No connection                                        |

| 12    | VCC_CP   | Supply for charge pump                                               | 28    | N/C      | No connection                                        |

| 13    | CP_OUT   | Charge pump output                                                   | 29    | N/C      | No connection                                        |

| 14    | LF_CTRL  | Loop filter component switch control                                 | 30    | N/C      | No connection                                        |

| 15    | LD_OUT   | Lock detect output                                                   | 31    | N/C      | No connection                                        |

| 16    | VCC_DIG  | Supply for digital blocks                                            | 32    | N/C      | No connection                                        |

## Functional Description

The SKY73134-11 is comprised of seven main functional blocks:

1. N-divider

2. R-divider

3. Phase detector

4. Charge pump

5. VCO and digital frequency VCO calibration

6. VCO dividers

7. Lock detect

### N-Divider

The N-divider consists of a selectable 16/17 or 32/33 prescaler, 13-bit main counter, and 5-bit swallow counter. The 18-bit N-divider ratio is calculated as:

$$N = P \times M + S$$

Where:  $P$  = Prescaler value

$M$  = Main counter value

$S$  = Swallow counter value

The N-divider range is from  $P^2$  to  $2^{18}$ . For a 32/33 prescaler, the N-divider range varies from 1024 to 262144.

### R-Divider

The 11-bit programmable R-divider divides the reference input frequency and generates the reference input for the phase detector. The R-divider range varies from 1 to  $2^{11}$  (2048).

### Phase Detector

The phase detector is an edge-controlled digital circuit. The circuit has two inputs: the reference signal (*Ref*) and the N-divider output. There are two digital outputs (*Up* and *Dn*) that drive the charge pump.

When the input phase difference is positive, the *Up* output is pulled up to VDD. When the input phase difference is negative, the *Dn* output is pulled down to ground. This type of phase detector acts only on the positive edges of the input signals.

### Charge Pump

The charge pump is used to convert the logic levels of the *Up* and *Dn* pulses, carrying the phase error between the reference and the divided signal into analog quantities/current pulses.

The output of the SKY73134-11 charge pump is programmable and varies between 0.9 mA and 5.4 mA. Additional adjustment of the charge pump current can be accomplished by changing the value of the external PLL bias resistor.

### VCO and Digital Frequency VCO Calibration

The SKY73134-11 incorporates four VCOs. Each VCO covers a different frequency range between 2.8 and 6.2 GHz.

The VCOs are designed to generate the LO signal with the tuning function controlled by the synthesizer. Each VCO uses a switch capacitor array and an analog varactor for digital tuning. The digital auto-tuning loop provides the proper coarse tuning setting for the VCO switch capacitors. This sets the oscillation frequency as close to target as possible before starting fine analog tuning.

When VCO auto-tuning is enabled, the PLL performs a successive approximation process to digitally tune the VCO close to the final programmed frequency. Once that is complete, analog tuning is enabled to lock the VCO to the programmed frequency.

The auto-tuning loop is designed to compensate process variation so that the VCO fine tuning range can be reduced to cover temperature variation only. This ensures that the PLL is always locked.

### VCO Dividers

The divider chain consists of dividers and LO drivers. Any VCO can be divided by 2, 3, 4, or 8, which improves the LO phase noise by 6 dB, 9.5 dB, 12 dB, and 18 dB, respectively.

Using frequency division, the overall VCO range of the device is widened from 0.35 to 6.2 GHz.

The output RF buffer has a programmable current that provides variation in the output RF level. The direct non-divided VCO output can be monitored at the additional bidirectional internal/external VCO pins. The divider chain and the internal PLL can be locked by an external VCO.

## Lock Detect

The lock detect circuit is activated when the phase difference between the *Up* and *Dn* phase detector signals for a given number of comparison cycles is shorter than a fixed delay. The CMOS output is active high when the loop is locked.

## Bidirectional Digital Interface

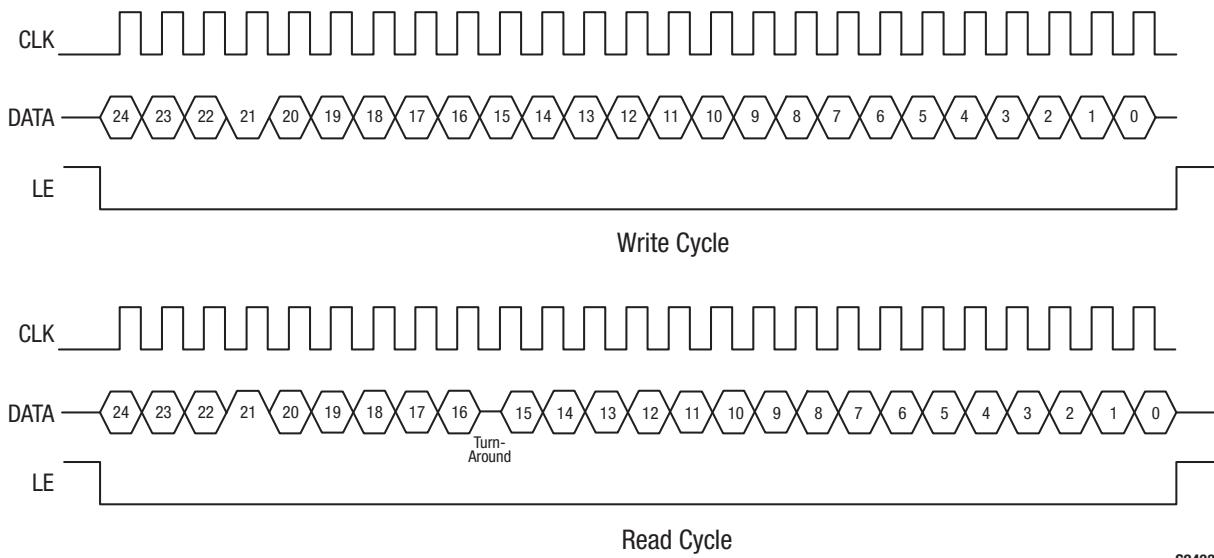

A three-wire Serial Programmable Interface (SPI) with read/write capability provides mode and bias control, and control of the PLL. The serial interface consists of three signals: the bus clock (CLK), latch enable (LE), and the serial, bidirectional data line (DATA).

**Write Mode.** A write data stream consists of 25 bits:

Bits[15:0] provide the 16-bit data block.

Bits[20:16] provide the register address.

Bit[21] is the read/write bit (0 = write, 1 = read).

Bits[24:22] provide the device address (the SKY73134-11 is 011b).

**Read Mode.** The read data stream is almost identical to the write data stream. Following the 5-bit register address, a “turn around”

cycle is inserted so the baseband can disable its drive of the data line and the addressed device on the bus can activate its data output driver.

When the baseband addresses a device connected to the serial bus, the bus enable signal (LE) goes low half a clock cycle before the CLK signal becomes active. Data on the DATA line is clocked into the SKY73134-11 on the rising edge of the clock.

Data from the SKY73134-11 to the baseband is clocked at the falling edge of the clock. The enable line goes high at the end of the data transfer.

A timing diagram for the SPI read/write cycle is shown in Figure 3.

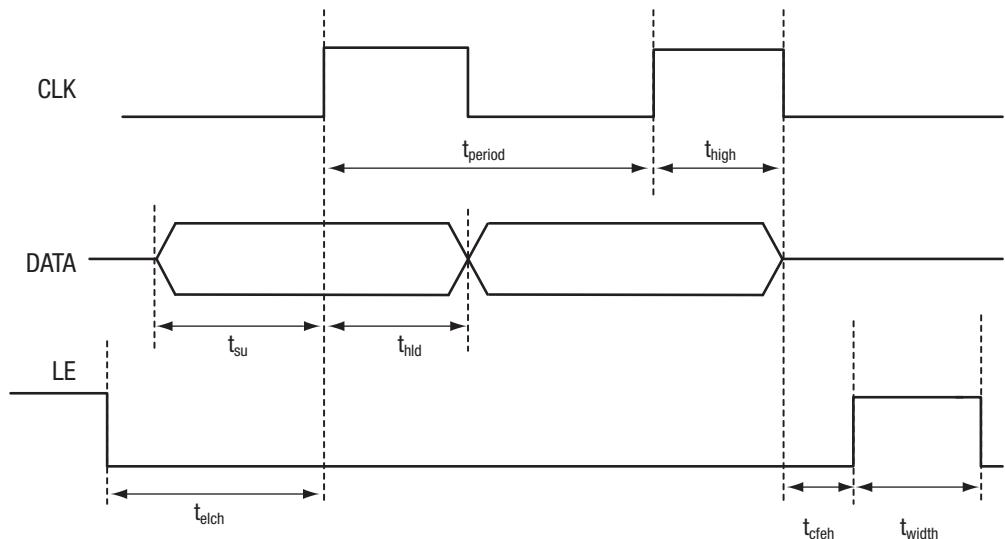

## Serial Bus Timing

The SPI bus speed is programmable. Timing requirements for the CLK, DATA, and LE signals are provided in Table 2. A serial data input timing diagram is shown in Figure 4.

S2433

Figure 3. Read/Write SPI Cycles

**Table 2. SPI Timing Requirements**

| Timing              | Description               | Minimum Time (ns) |

|---------------------|---------------------------|-------------------|

| $t_{\text{period}}$ | Clock period              | 25                |

| $t_{\text{high}}$   | Clock high time           | 10                |

| $t_{\text{su}}$     | Data setup to clock rise  | 5                 |

| $t_{\text{hld}}$    | Data hold from clock rise | 5                 |

| $t_{\text{elch}}$   | Enable low to clock rise  | 10                |

| $t_{\text{width}}$  | Enable high width         | 10                |

| $t_{\text{cfeh}}$   | Clock fall to enable high | 20                |

S2434

**Figure 4. SPI Timing Diagram**

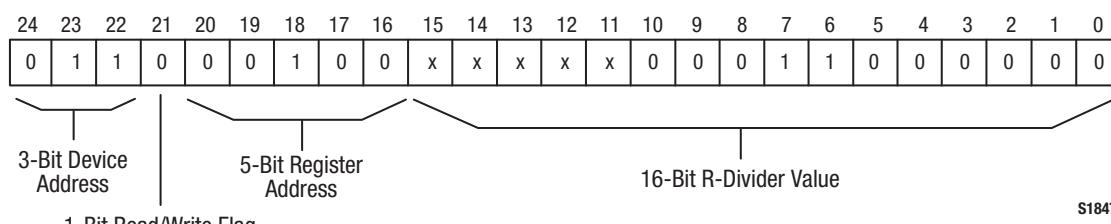

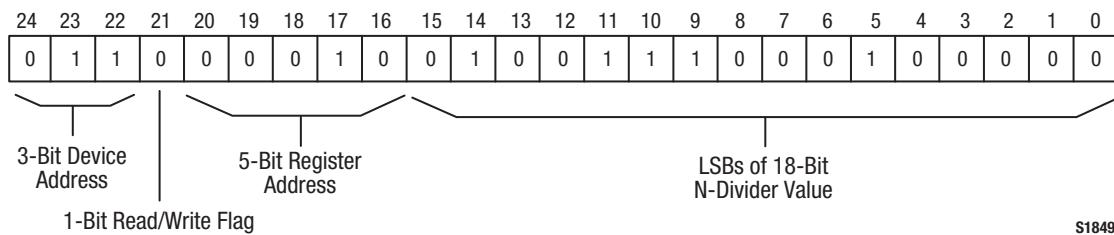

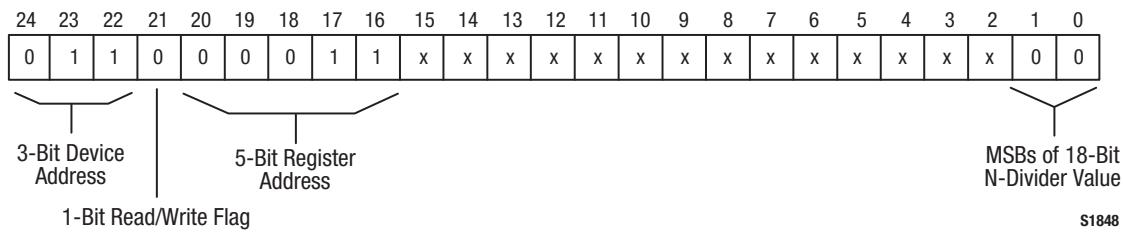

### PLL Control Registers (R-Divider and N-Divider)

There are three digital PLL control registers that are used to store the R-divider and N-divider values: PLL R-Divider, PLL N-Divider 1, and PLL N-Divider 2. By default, all registers are 25 bits wide. Bit[21] is the read/write bit, cleared when writing to the device. Bits[20:16] are the address bits of the registers. The 16 least significant bits (LSBs) represent the data bits.

Three values are needed to calculate the three PLL dividers,  $R_{DIV}$ ,  $N_{DIV1}$  and  $N_{DIV2}$ : the desired frequency ( $F_{RF}$ ), the VCO divider ( $D$ ), and the frequency step size ( $F_{STEP}$ ).

The VCO frequency ( $F_{VCO}$ ) has a range of 2.8 GHz to 6.2 GHz, and is defined by the product of the desired frequency ( $F_{RF}$ ) and the VCO divider,  $D$ :

$$F_{VCO} = F_{RF} \times D \quad (1)$$

The VCO divider (equal to 1, 2, 3, 4, or 8) is chosen so that the product of  $F_{RF} \times D$  is within the specified VCO range.

The frequency step size ( $F_{STEP}$ ) is a user defined value. Given  $F_{STEP}$  and  $D$ , the comparison frequency ( $F_{COMP}$ ) can be calculated by:

$$F_{COMP} = F_{STEP} \times D \quad (2)$$

The PLL R-Divider register stores the value of the 11-bit R-divider that produces the desired comparison frequency ( $F_{COMP}$ ) for the RF PLL according to the following equation:

$$R = \frac{F_{REF}}{F_{COMP}} \quad (3)$$

Where  $F_{REF}$  is the reference frequency provided to the device.

The PLL N-Divider 1 and PLL N-Divider 2 registers store the value of the N-divider according to the following equation:

$$N = \frac{F_{VCO}}{F_{COMP}} \quad (4)$$

Bits[1:0] of the PLL N-Divider 2 register are the most significant bits (MSBs) of the 18-bit representation of the N number.

Bits[15:0] of the PLL N-Divider 1 register are the LSBs of the 18-bit binary representation of the N number.

The calculated R-divider and N-divider values are programmed into the SKY73134-11 using the SPI interface.

Additional programming information is provided in the document, *Skyworks Wideband Integer-N, Phase-Locked Loop Programming Guide*, document number 201322.

#### Example:

A desired RF output frequency of 2000 MHz is required using a reference frequency of 38.4 MHz and a desired frequency step size of 100 kHz. If the VCO divider is equal to 2, the VCO frequency is 4000 MHz from Equation 1 and the comparison frequency is equal to 200 kHz from Equation 2.

From Equations 3 and 4, the R and N values become:

$$R = 192 = 11000000b$$

$$N = 20000 = 100111000100000b$$

These values would be programmed through the SPI interface.

Figure 5 represents the bits of the PLL R-Divider register with the value of  $R = 192$ . Figures 6 and 7 represent the bits of the PLL N-Divider 1 and PLL N-Divider 2 registers, respectively, with the value of  $N = 20000$ .

### Electrical and Mechanical Specifications

The absolute maximum ratings of the SKY73134-11 are provided in Table 3. The recommended operating conditions are specified in Table 4 and electrical specifications are provided in Tables 5 through 7.

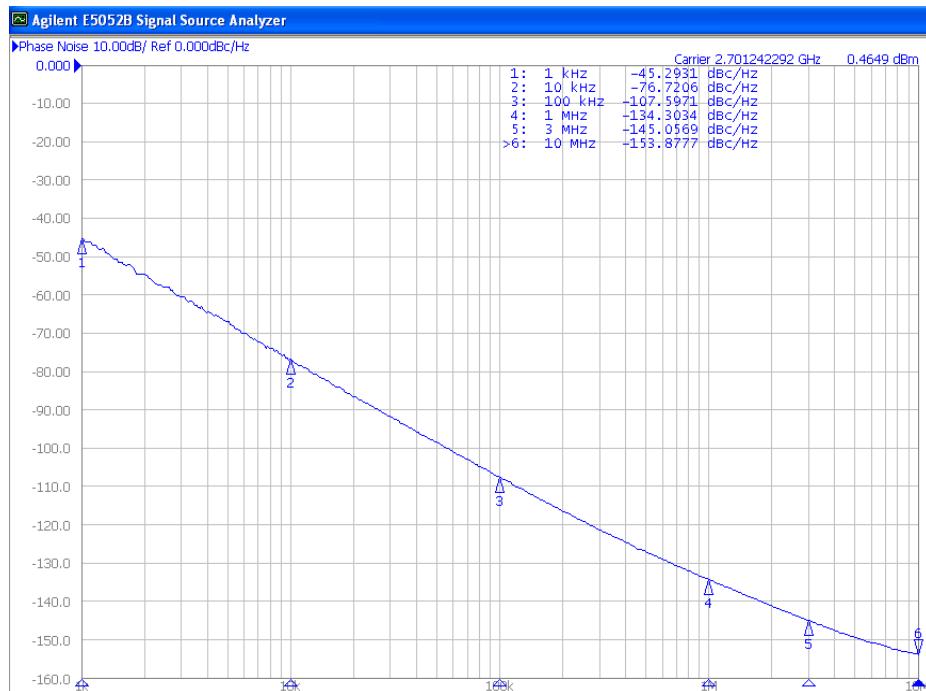

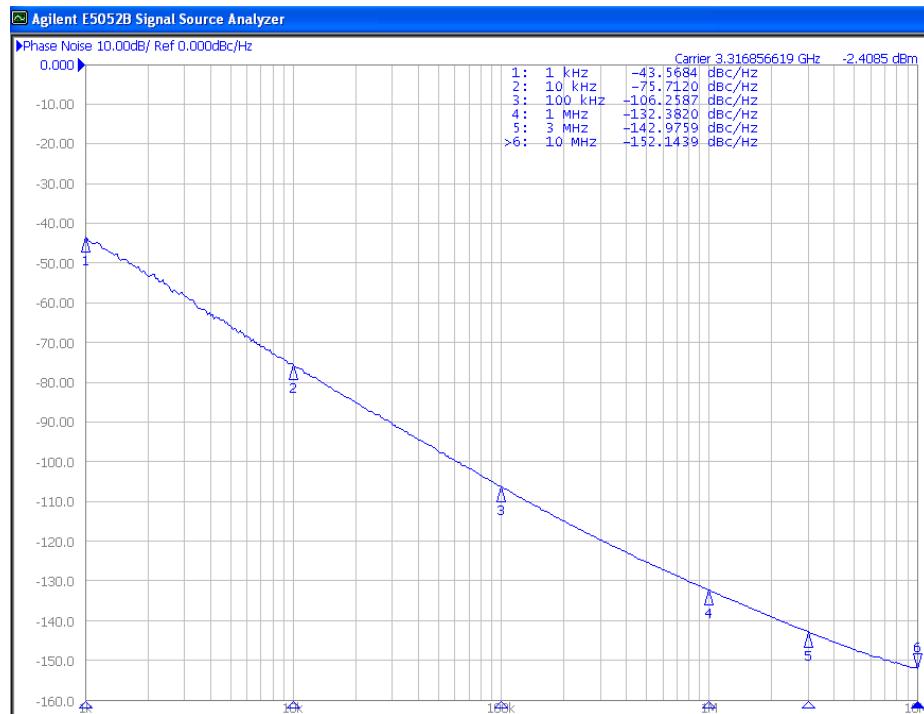

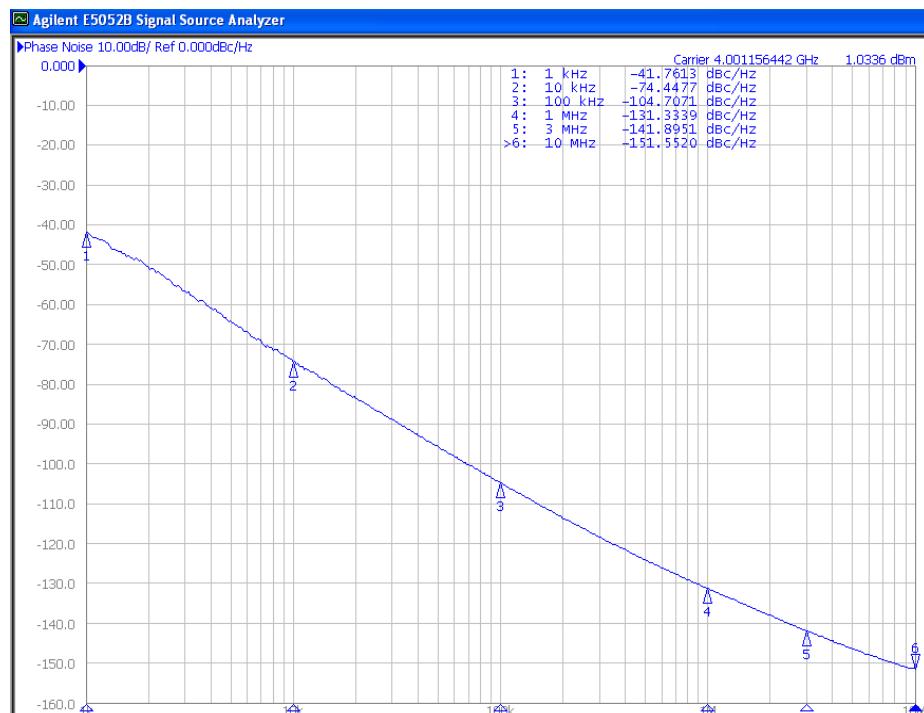

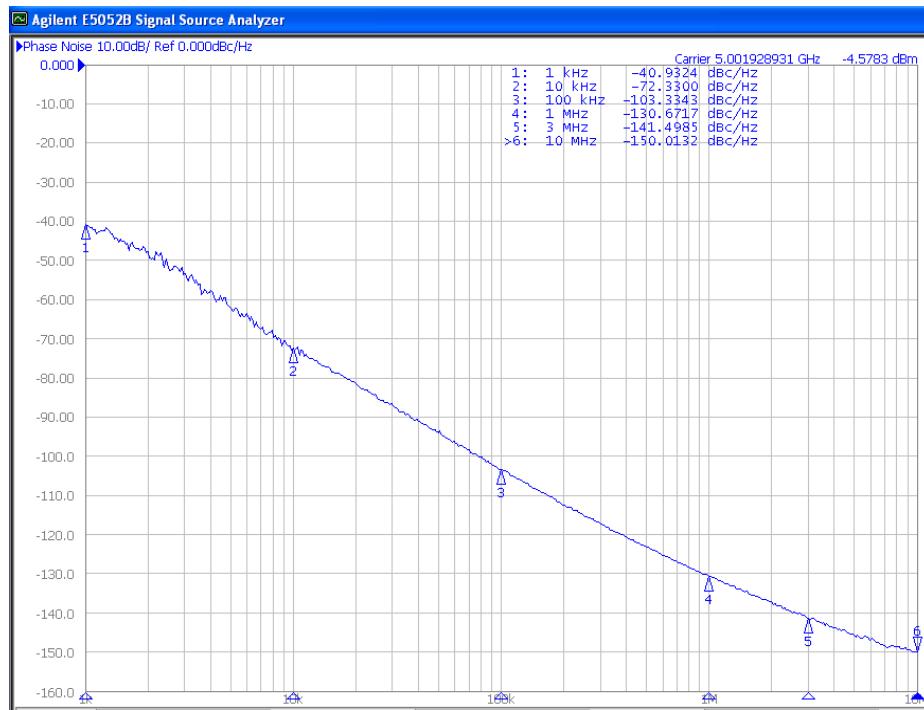

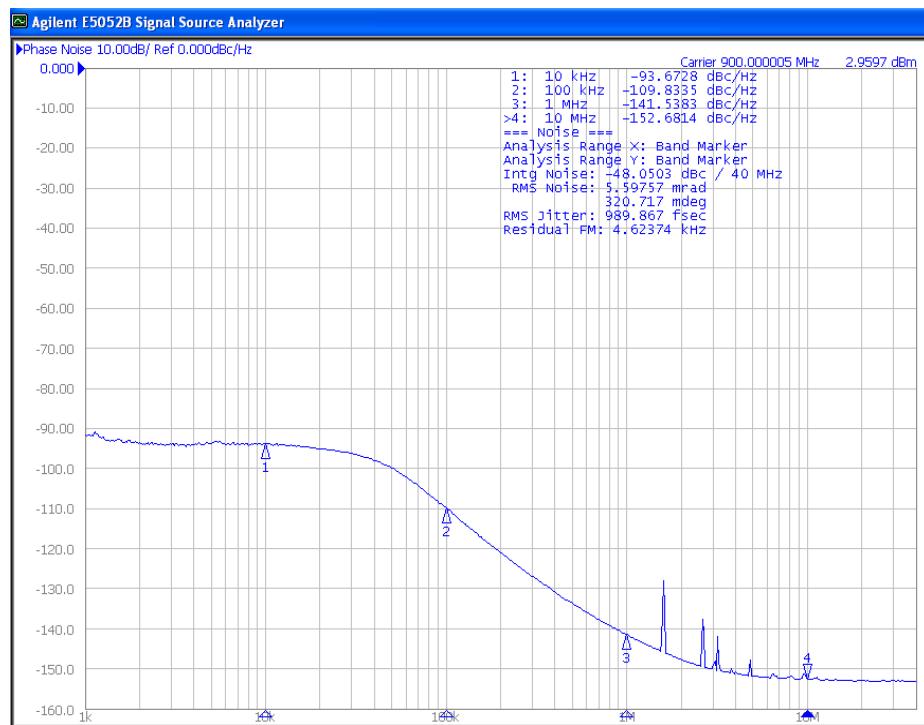

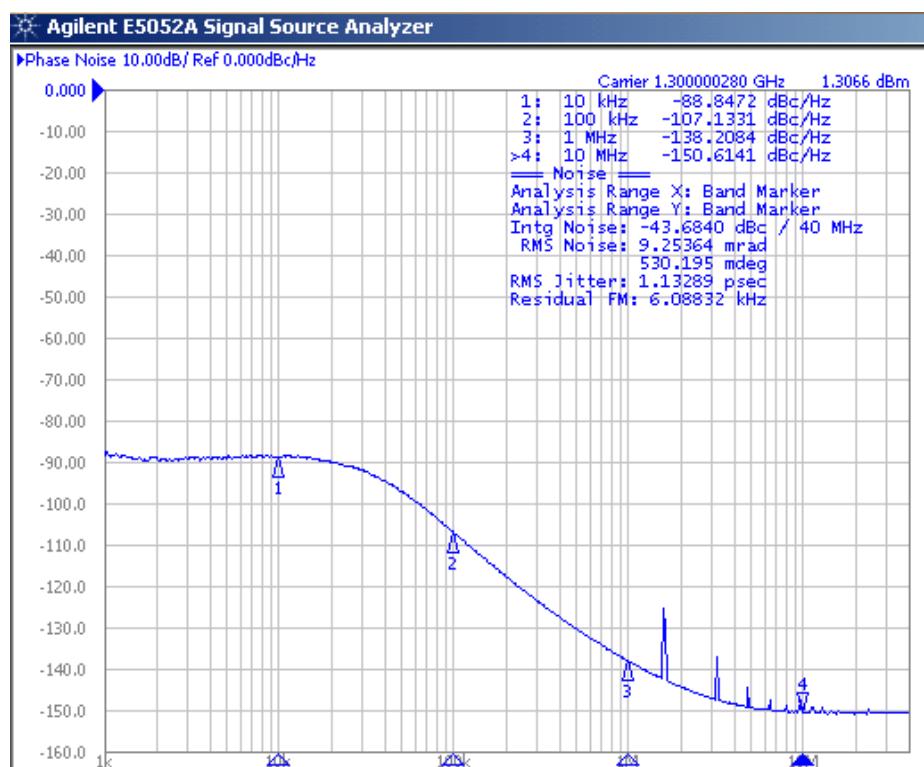

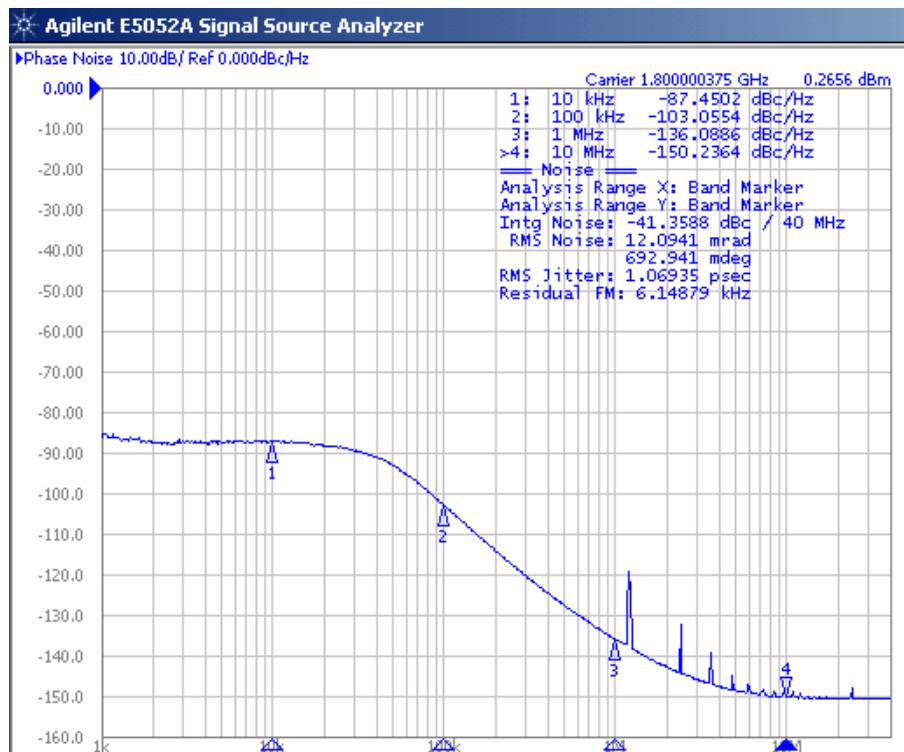

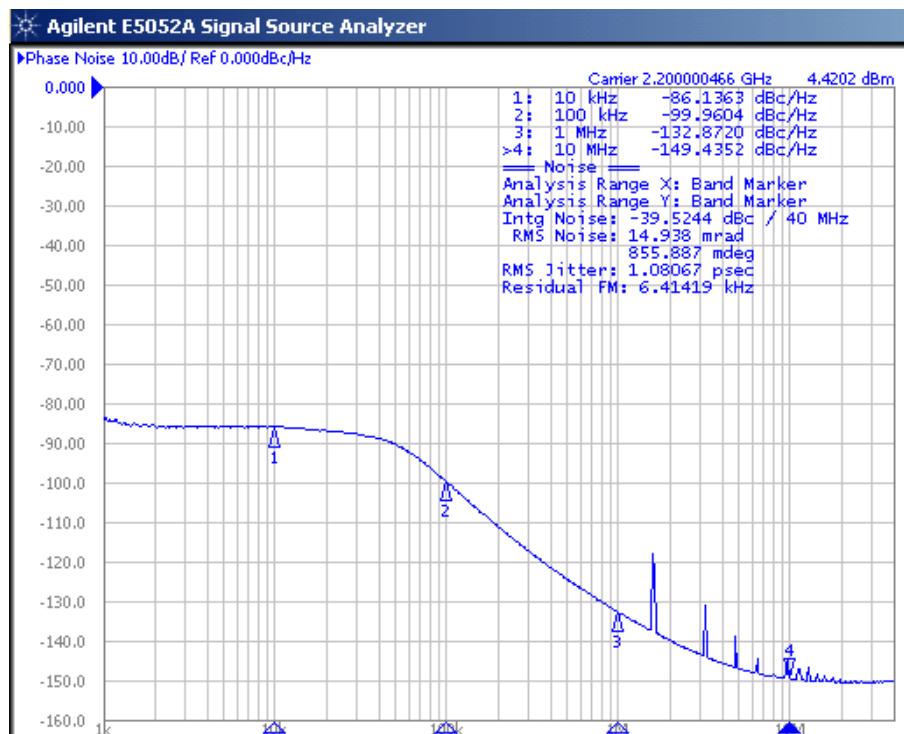

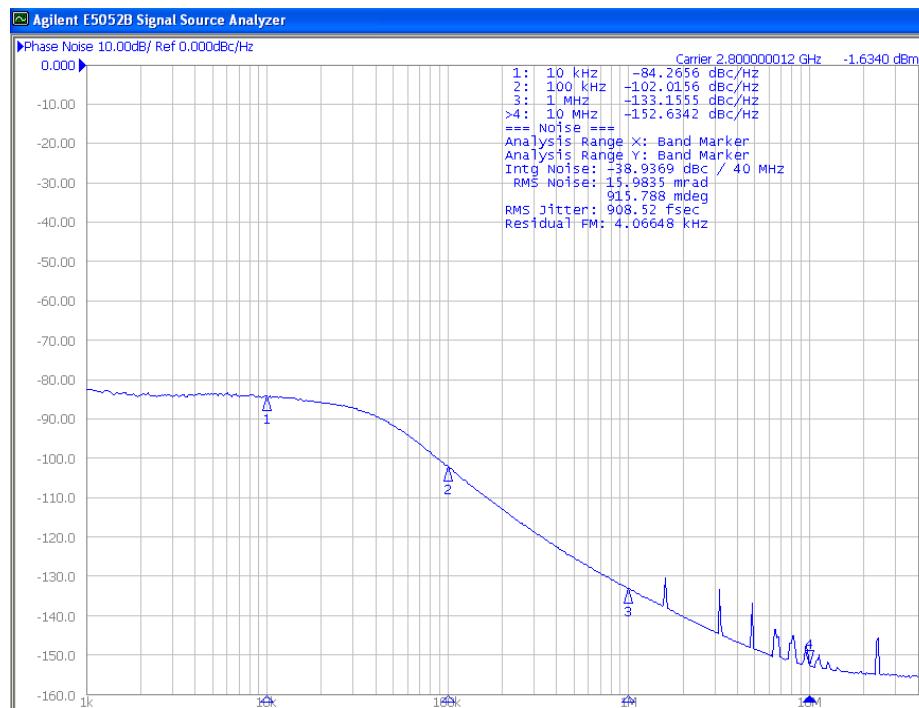

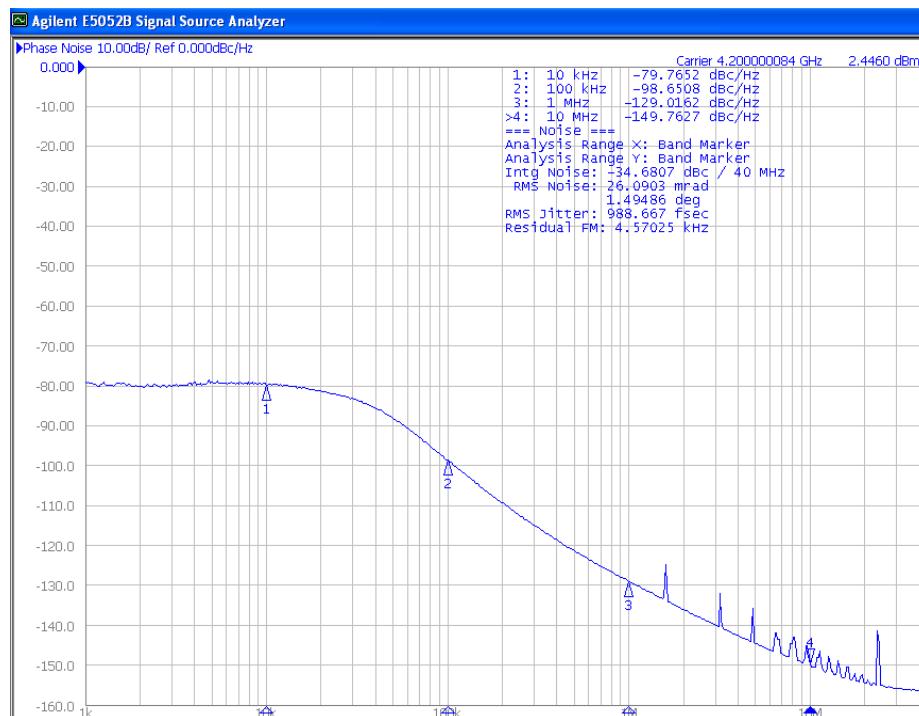

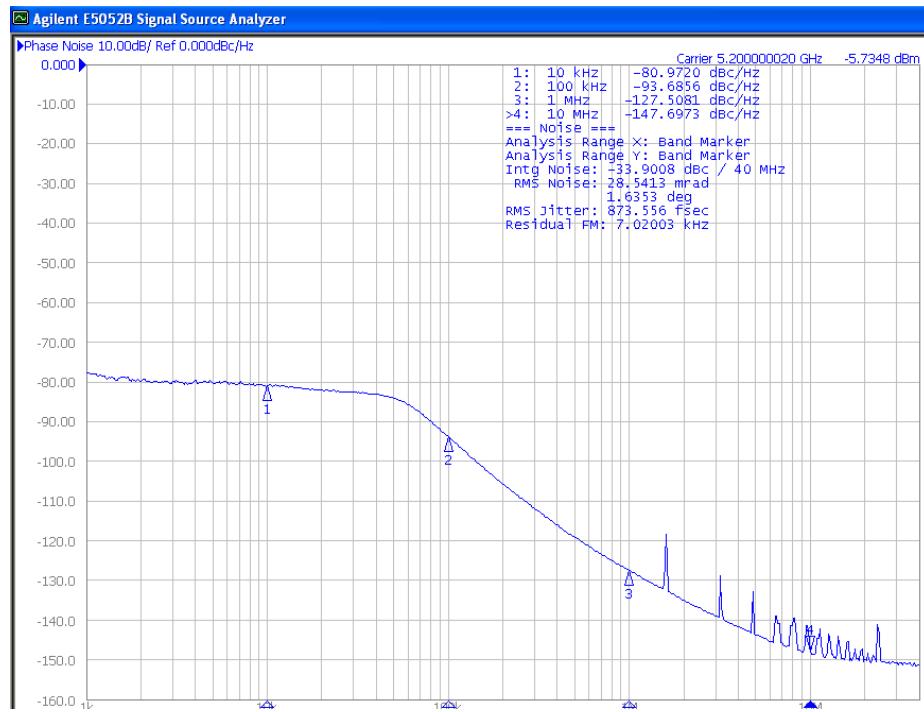

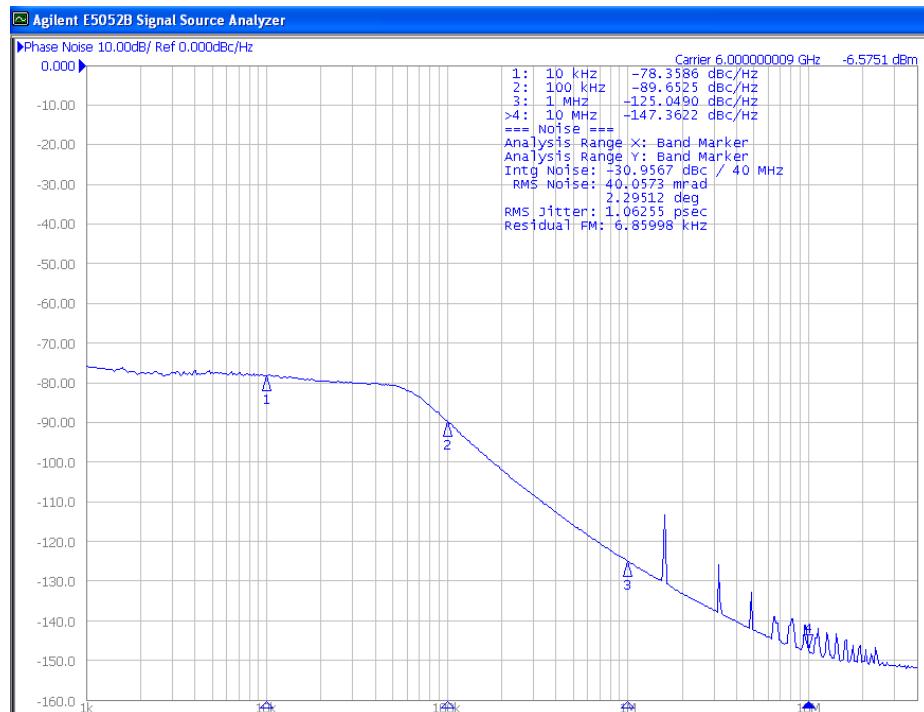

Open-loop VCO phase noise measurements are illustrated in Figures 8 to 11. Closed-loop VCO phase noise measurements are illustrated in Figures 12 to 19. An Agilent E5052 signal source analyzer was used for all phase noise measurements.

S1847

Note: Value of bits [13:11] can vary. Refer to *Skyworks Wideband Integer-N, Phase-Locked Loop Programming Guide*, document number 201199.

**Figure 5. PLL R-Divider Register Showing an R-Divider Value of 192**

S1849

Figure 6. PLL N-Divider 1 Register Showing an N-Divider Value of 20000 (LSBs)

S1848

Note: Value of bits [15:2] can vary. Refer to *Skyworks Wideband Integer-N, Phase-Locked Loop Programming Guide*, document number 201322.

Figure 7. PLL N-Divider 2 Register Showing an N-Divider Value of 20000 (MSBs)

Table 3. SKY73134-11 Absolute Maximum Ratings

| Parameter                                                                               | Symbol           | Minimum | Maximum | Units |

|-----------------------------------------------------------------------------------------|------------------|---------|---------|-------|

| Supply voltage (VCC_VCO, VCC_OBUF, VCC_DIV, VCC_PLL, VCC_CP, VCC_DIG, and VCC_REF pins) | V <sub>CC</sub>  |         | 3.6     | V     |

| Supply current                                                                          | I <sub>CC</sub>  |         | 150     | mA    |

| Operating case temperature                                                              | T <sub>C</sub>   | -40     | +85     | °C    |

| Junction temperature                                                                    | T <sub>J</sub>   |         | +150    | °C    |

| Storage case temperature                                                                | T <sub>STG</sub> | -40     | +125    | °C    |

**Notes:** Exposure to maximum rating conditions for extended periods may reduce device reliability. There is no damage to device with only one parameter set at the limit and all other parameters set at or below their nominal value. Exceeding any of the limits listed here may result in permanent damage to the device.

**CAUTION:** Although this device is designed to be as robust as possible, Electrostatic Discharge (ESD) can damage this device. This device must be protected at all times from ESD. Static charges may easily produce potentials of several kilovolts on the human body or equipment, which can discharge without detection. Industry-standard ESD precautions should be used at all times. The SKY73134-11 is rated as a Class 1B device using Human Body Model (HBM) testing, Class 2 device using Charged Device Model (CDM) testing, and as a Class A device using Man-Machine (MM) testing.

Table 4. SKY73134-11 Recommended Operating Conditions

| Parameter                                                                               | Symbol          | Minimum | Typical | Maximum | Units |

|-----------------------------------------------------------------------------------------|-----------------|---------|---------|---------|-------|

| Supply voltage (VCC_VCO, VCC_OBUF, VCC_DIV, VCC_PLL, VCC_CP, VCC_DIG, and VCC_REF pins) | V <sub>CC</sub> | 3.0     | 3.3     | 3.6     | V     |

| Supply current                                                                          | I <sub>CC</sub> |         | 120     | 130     | mA    |

| Operating case temperature                                                              | T <sub>C</sub>  | -40     |         | +85     | °C    |

**Table 5. SKY73134-11 Electrical Specifications: Reference Input and Charge Pump (Note 1)**

( $T_c = +25^\circ\text{C}$ , Unless Otherwise Noted)

| Parameter                       | Symbol            | Test Condition                          | Min                                                     | Typical | Max                                                     | Units |

|---------------------------------|-------------------|-----------------------------------------|---------------------------------------------------------|---------|---------------------------------------------------------|-------|

| Reference input frequency       | $F_{\text{REF}}$  |                                         | 10                                                      |         | 200                                                     | MHz   |

| Reference input sensitivity     |                   |                                         | 200                                                     | 900     |                                                         | mVp-p |

| Comparison frequency            | $F_{\text{COMP}}$ |                                         | $F_{\text{RF}} \times 10^3 \times D/2^{18}$<br>(Note 2) |         | $F_{\text{RF}} \times 10^3 \times D/2^{10}$<br>(Note 2) | kHz   |

| Frequency step                  | $F_{\text{STEP}}$ |                                         | $F_{\text{RF}} \times 10^3/2^{18}$                      |         | $F_{\text{RF}} \times 10^3/2^{10}$                      | kHz   |

| Charge pump current             | $I_{\text{CP}}$   | Step size = 0.6 mA                      | 0.9                                                     | 2.7     | 5.4                                                     | mA    |

| Output voltage compliance range |                   |                                         | 0.4                                                     |         | $V_{\text{DD}} - 0.4$                                   | V     |

| Comparison spurs                |                   |                                         |                                                         | -70     | -65                                                     | dBc   |

| Locking time                    |                   | 20 kHz bandwidth, 1 ppm frequency error |                                                         |         | 1                                                       | ms    |

Note 1: Performance is guaranteed only under the conditions listed in this Table.

**Table 6. SKY73134-11 Electrical Specifications: VCO and RF Output Characteristics (Note 1)**

( $T_c = +25^\circ\text{C}$ , Unless Otherwise Noted)

| Parameter           | Symbol            | Test Condition | Min | Typical | Max                   | Units |

|---------------------|-------------------|----------------|-----|---------|-----------------------|-------|

| RF output frequency | $F_{\text{RF}}$   |                | 350 |         | 6000                  | MHz   |

| VCO frequency       |                   |                | 2.8 |         | 6.2                   | GHz   |

| VCO sensitivity     | $K_{\text{VCO}}$  |                | 12  | 20      | 38                    | MHz/V |

| VCO pushing         |                   |                |     | 5       | 10                    | MHz/V |

| VCO control voltage | $V_{\text{CTRL}}$ |                | 0.4 |         | $V_{\text{DD}} - 0.4$ | V     |

| RF power            |                   |                | -8  | +2      | +4                    | dBm   |

Note 1: Performance is guaranteed only under the conditions listed in this Table.

**Table 7. SKY73134-11 Electrical Specifications: Phase Noise Performance (1 of 3) (Note 1)**

( $T_c = +25^\circ\text{C}$ , Unless Otherwise Noted)

| Parameter                                              | Symbol | Test Condition                                                                 | Min | Typical                                              | Max | Units  |

|--------------------------------------------------------|--------|--------------------------------------------------------------------------------|-----|------------------------------------------------------|-----|--------|

| <b><i>In-Band Phase Noise, Closed Loop</i></b>         |        |                                                                                |     |                                                      |     |        |

| Normalized in-band phase noise floor with internal VCO |        | $I_{\text{CP}} = 3.6 \text{ mA}$ , PLL bandwidth = 30 kHz                      |     | -213                                                 |     | dBc/Hz |

| In-band phase noise floor divide-by-1                  |        | $I_{\text{CP}} = 3.6 \text{ mA}$ , PLL bandwidth = 30 kHz                      |     | $-213 + 20 \times \log N + 10 \log(F_{\text{COMP}})$ |     | dBc/Hz |

| In-band phase noise floor divide-by-2                  |        | $I_{\text{CP}} = 3.6 \text{ mA}$ , PLL bandwidth = 30 kHz                      |     | $-219 + 20 \times \log N + 10 \log(F_{\text{COMP}})$ |     | dBc/Hz |

| In-band phase noise floor divide-by-3                  |        | $I_{\text{CP}} = 3.6 \text{ mA}$ , PLL bandwidth = 30 kHz                      |     | $-222 + 20 \times \log N + 10 \log(F_{\text{COMP}})$ |     | dBc/Hz |

| In-band phase noise floor divide-by-4                  |        | $I_{\text{CP}} = 3.6 \text{ mA}$ , PLL bandwidth = 30 kHz                      |     | $-225 + 20 \times \log N + 10 \log(F_{\text{COMP}})$ |     | dBc/Hz |

| In-band phase noise floor divide-by-8                  |        | $I_{\text{CP}} = 3.6 \text{ mA}$ , PLL bandwidth = 30 kHz                      |     | $-231 + 20 \times \log N + 10 \log(F_{\text{COMP}})$ |     | dBc/Hz |

| <b><i>PLL Integrated Phase Noise</i></b>               |        |                                                                                |     |                                                      |     |        |

| Integrated phase noise (1 kHz to 10 MHz)               |        | PLL bandwidth = 30 MHz, RF output = 1 GHz, $F_{\text{STEP}} = 400 \text{ kHz}$ |     | -45                                                  |     | dBc    |

**Table 7. SKY73134-11 Electrical Specifications: Phase Noise Performance (2 of 3) (Note 1)**

(T<sub>c</sub> = +25 °C, Unless Otherwise Noted)

| Parameter                                  | Symbol | Test Condition | Min | Typical   | Max | Units  |

|--------------------------------------------|--------|----------------|-----|-----------|-----|--------|

| <b>Open Loop VCO Phase Noise @ 2.7 GHz</b> |        |                |     |           |     |        |

| Phase noise:                               |        |                |     |           |     |        |

| @ 1 kHz                                    |        |                |     | -45       |     | dBc/Hz |

| @ 10 kHz                                   |        |                |     | -77       |     | dBc/Hz |

| @ 100 kHz                                  |        |                |     | -108      |     | dBc/Hz |

| @ 1 MHz                                    |        |                |     | -134      |     | dBc/Hz |

| @ 3 MHz                                    |        |                |     | -145      |     | dBc/Hz |

| @ 10 MHz                                   |        |                |     | -154      |     | dBc/Hz |

| <b>Open Loop VCO Phase Noise @ 3.3 GHz</b> |        |                |     |           |     |        |

| Phase noise:                               |        |                |     |           |     |        |

| @ 1 kHz                                    |        |                |     | -44       |     | dBc/Hz |

| @ 10 kHz                                   |        |                |     | -76       |     | dBc/Hz |

| @ 100 kHz                                  |        |                |     | -106      |     | dBc/Hz |

| @ 1 MHz                                    |        |                |     | -132      |     | dBc/Hz |

| @ 3 MHz                                    |        |                |     | -143      |     | dBc/Hz |

| @ 10 MHz                                   |        |                |     | -152      |     | dBc/Hz |

| <b>Open Loop VCO Phase Noise @ 4.0 GHz</b> |        |                |     |           |     |        |

| Phase noise:                               |        |                |     |           |     |        |

| @ 1 kHz                                    |        |                |     | -42       |     | dBc/Hz |

| @ 10 kHz                                   |        |                |     | -75       |     | dBc/Hz |

| @ 100 kHz                                  |        |                |     | -105      |     | dBc/Hz |

| @ 1 MHz                                    |        |                |     | -131      |     | dBc/Hz |

| @ 3 MHz                                    |        |                |     | -142      |     | dBc/Hz |

| @ 10 MHz                                   |        |                |     | -152      |     | dBc/Hz |

| <b>Open Loop VCO Phase Noise @ 5.0 GHz</b> |        |                |     |           |     |        |

| Phase noise:                               |        |                |     |           |     |        |

| @ 1 kHz                                    |        |                |     | -41       |     | dBc/Hz |

| @ 10 kHz                                   |        |                |     | -73       |     | dBc/Hz |

| @ 100 kHz                                  |        |                |     | -104      |     | dBc/Hz |

| @ 1 MHz                                    |        |                |     | -131      |     | dBc/Hz |

| @ 3 MHz                                    |        |                |     | -142      |     | dBc/Hz |

| @ 10 MHz                                   |        |                |     | -150      |     | dBc/Hz |

| <b>VCO Divided by 2</b>                    |        |                |     |           |     |        |

| Phase noise:                               |        |                |     |           |     |        |

| @ 1 kHz                                    |        |                |     | VCO - 6   |     | dBc/Hz |

| @ 10 kHz                                   |        |                |     | VCO - 6   |     | dBc/Hz |

| @ 100 kHz                                  |        |                |     | VCO - 6   |     | dBc/Hz |

| @ 1 MHz                                    |        |                |     | VCO - 6   |     | dBc/Hz |

| <b>VCO Divided by 3</b>                    |        |                |     |           |     |        |

| Phase noise:                               |        |                |     |           |     |        |

| @ 1 kHz                                    |        |                |     | VCO - 9.5 |     | dBc/Hz |

| @ 10 kHz                                   |        |                |     | VCO - 9.5 |     | dBc/Hz |

| @ 100 kHz                                  |        |                |     | VCO - 9.5 |     | dBc/Hz |

| @ 1 MHz                                    |        |                |     | VCO - 9.5 |     | dBc/Hz |

**Table 7. SKY73134-11 Electrical Specifications: Phase Noise Performance (3 of 3) (Note 1)**

**( $T_c = +25^\circ\text{C}$ , Unless Otherwise Noted)**

| Parameter                      | Symbol | Test Condition | Min | Typical  | Max | Units  |

|--------------------------------|--------|----------------|-----|----------|-----|--------|

| <b><i>VCO Divided by 4</i></b> |        |                |     |          |     |        |

| Phase noise:                   |        |                |     |          |     |        |

| @ 1 kHz                        |        |                |     | VCO – 12 |     | dBc/Hz |

| @ 10 kHz                       |        |                |     | VCO – 12 |     | dBc/Hz |

| @ 100 kHz                      |        |                |     | VCO – 12 |     | dBc/Hz |

| @ 1 MHz                        |        |                |     | VCO – 12 |     | dBc/Hz |

| <b><i>VCO Divided by 8</i></b> |        |                |     |          |     |        |

| Phase noise:                   |        |                |     |          |     |        |

| @ 1 kHz                        |        |                |     | VCO – 18 |     | dBc/Hz |

| @ 10 kHz                       |        |                |     | VCO – 18 |     | dBc/Hz |

| @ 100 kHz                      |        |                |     | VCO – 18 |     | dBc/Hz |

**Note 1:** Performance is guaranteed only under the conditions listed in this Table.

## Open-Loop Phase Noise Measurements

**Figure 8. Open-Loop VCO Phase Noise @ 2.7 GHz**

Figure 9. Open-Loop VCO Phase Noise @ 3.3 GHz

Figure 10. Open-Loop VCO Phase Noise @ 4.0 GHz

Figure 11. Open-Loop VCO Phase Noise @ 5.0 GHz

## Closed-Loop Phase Noise Measurements

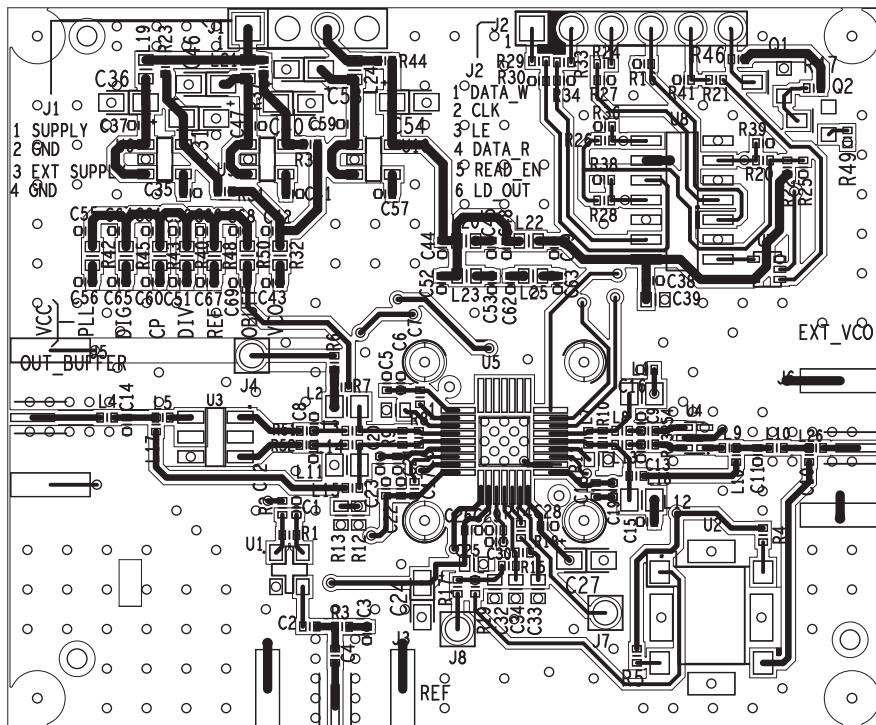

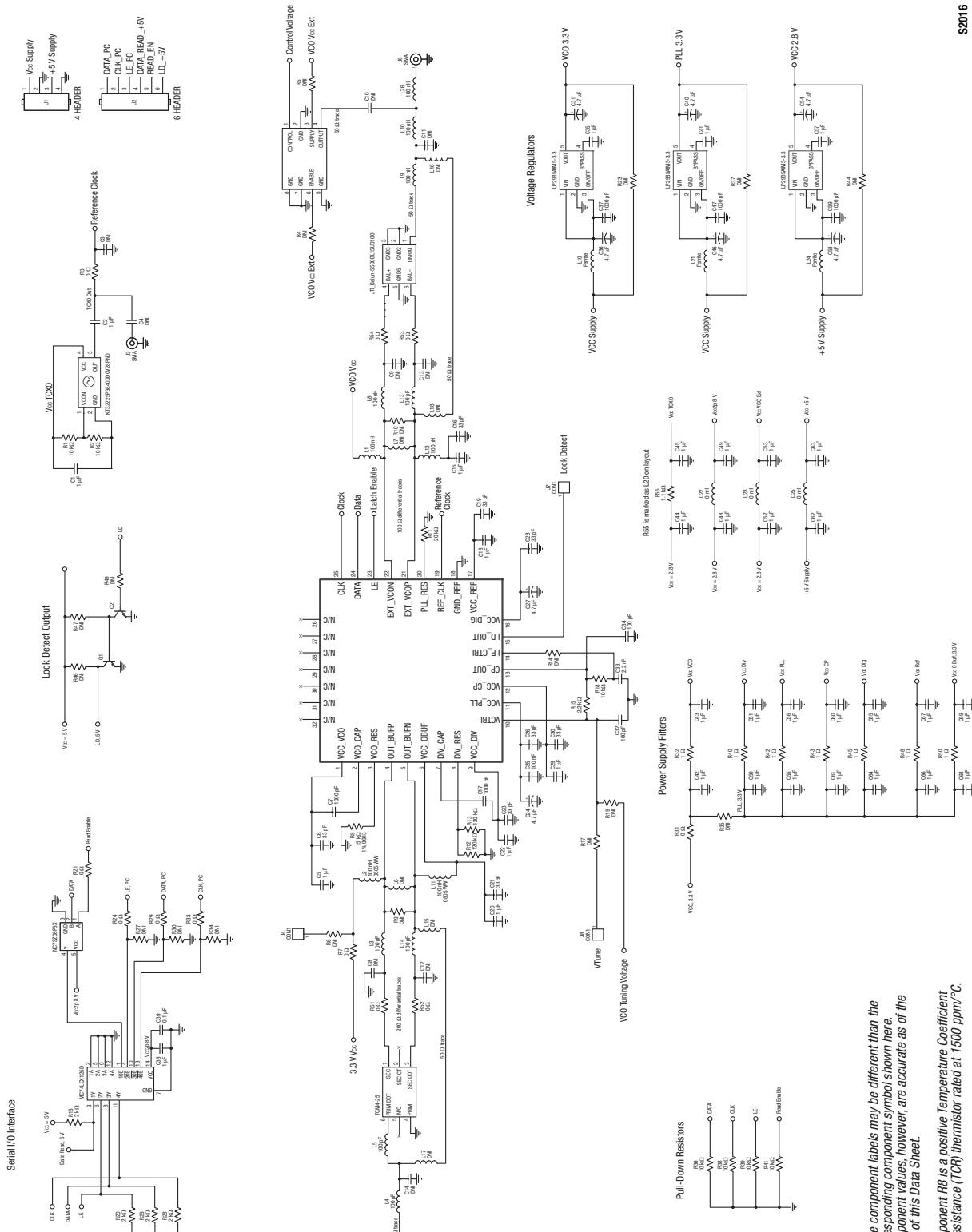

Closed-loop phase noise is measured with a 76.8 MHz external reference clock. The values of the loop filter components for Figures 12 to 15 are shown on the schematic diagram in Figure 22: C33 = 2.2 nF, C32 = C34 = 100 pF, R15 = 2.2 k $\Omega$ , and R18 = 10 k $\Omega$ .

For Figures 16 to 19, the loop filter components are: C33 = 4.4 nF, C32 = C34 = 200 pF, R15 = 1.1 k $\Omega$ , and

R18 = 5 k $\Omega$ . The following parameters characterize the phase noise measurements:

RFOUT = measured output frequency

FSTEP = the frequency step (channel spacing)

VCO\_Div = the VCO frequency divider

FCOMP = the comparison (phase detector) frequency

**Figure 12. Closed-Loop Phase Noise Performance For RFout = 900 MHz

(FSTEP = 400 kHz, VCO\_Div = 4, FCOMP = 1.6 MHz)**

**Figure 13. Closed-Loop Phase Noise Performance For RFout = 1.3 GHz

(FSTEP = 400 kHz, VCO\_Div = 4, FCOMP = 1.6 MHz)**

**Figure 14. Closed-Loop Phase Noise Performance For RFout = 1.8 GHz

(FSTEP = 400 kHz, VCO\_Div = 3, FCOMP = 1.2 MHz)**

**Figure 15. Closed-Loop Phase Noise Performance For RFout = 2.2 GHz

(FSTEP = 800 kHz, VCO\_Div = 2, FCOMP = 1.6 MHz)**

**Figure 16. Closed-Loop Phase Noise Performance For RFout = 2.8 GHz

(FSTEP = 1600 kHz, VCO\_Div = 1, FCOMP = 1.6 MHz)**

**Figure 17. Closed-Loop Phase Noise Performance For RFout = 4.2 GHz

(FSTEP = 1600 kHz, VCO\_Div = 1, FCOMP = 1.6 MHz)**

**Figure 18. Closed-Loop Phase Noise Performance For RFout = 5.2 GHz

(FSTEP = 1600 kHz, VCO\_Div = 1, FCOMP = 1.6 MHz)**

**Figure 19. Closed-Loop Phase Noise Performance For RFout = 6.0 GHz

(FSTEP = 1600 kHz, VCO\_Div = 1, FCOMP = 1.6 MHz)**

## Evaluation Board Description

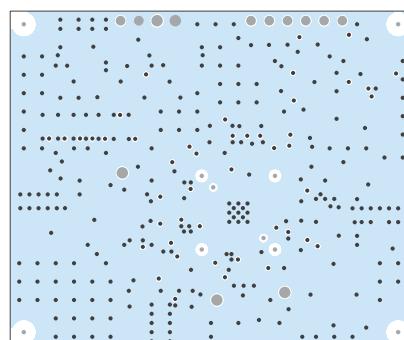

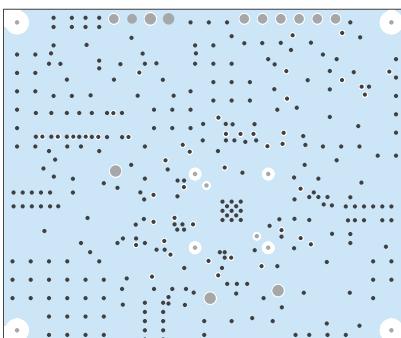

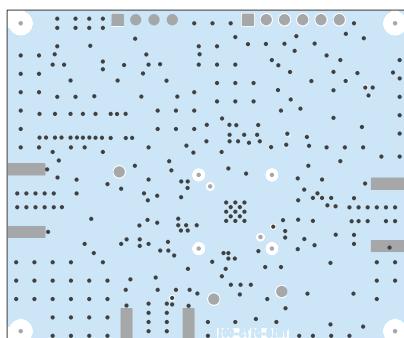

The SKY73134-11 Evaluation Board is used to test the performance of the SKY73134-11 frequency synthesizer. An assembly drawing for the Evaluation Board is shown in Figure 20 and the layer detail is provided in Figure 21. A schematic diagram of the SKY73134-11 Evaluation Board is shown in Figure 22.

## Circuit Design Configurations

The following design considerations are general in nature and must be followed regardless of final use or configuration:

1. Paths to ground should be made as short as possible.

2. The ground pad of the SKY73134-11 has special electrical and thermal grounding requirements. This pad is the main thermal conduit for heat dissipation. Since the circuit board acts as the heat sink, it must shunt as much heat as possible from the device. Therefore, design the connection to the ground pad to dissipate the maximum wattage produced by the circuit board.

3. Skyworks recommends including external bypass capacitors on the VCC voltage inputs of the device.

## Package Dimensions

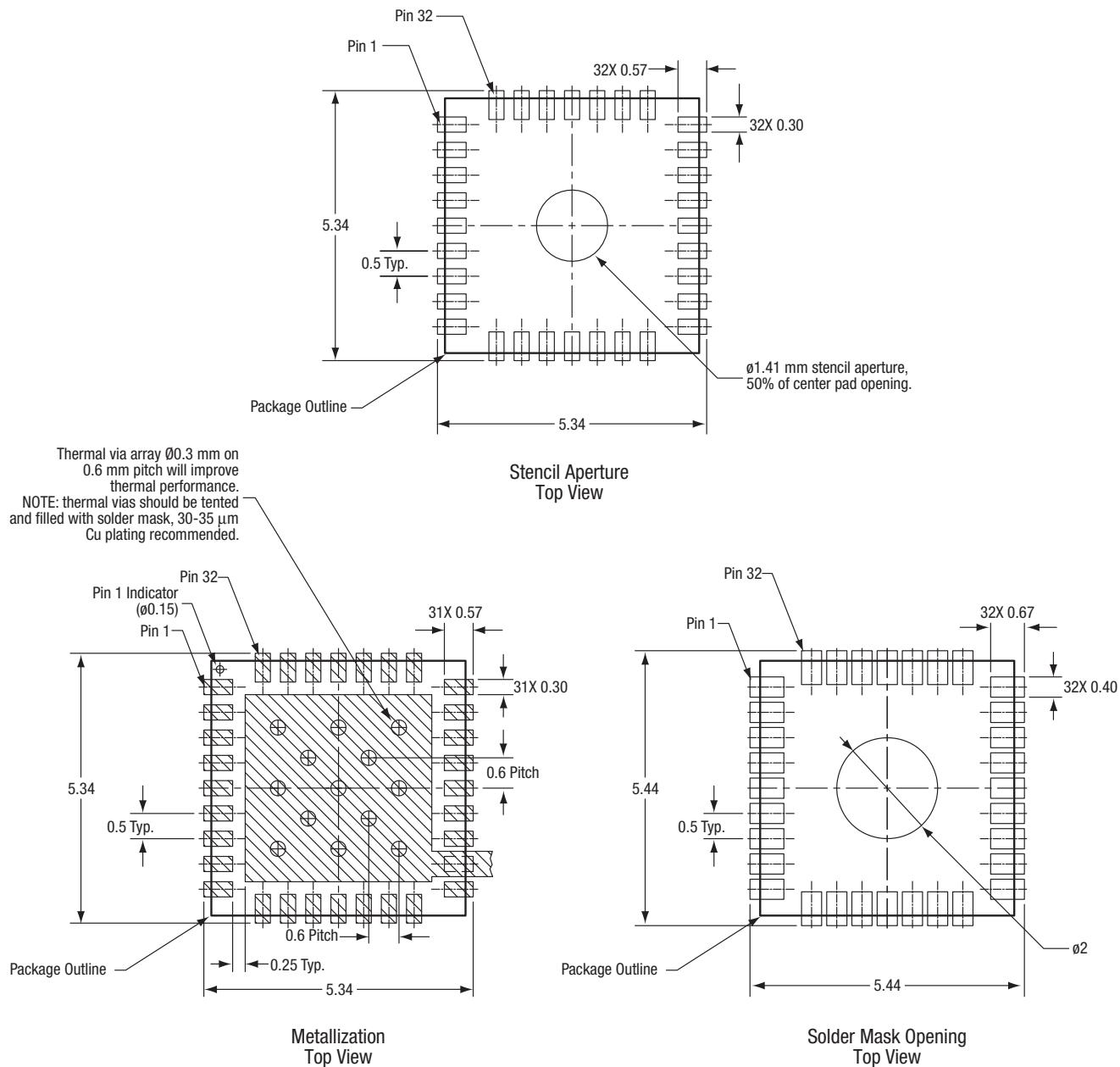

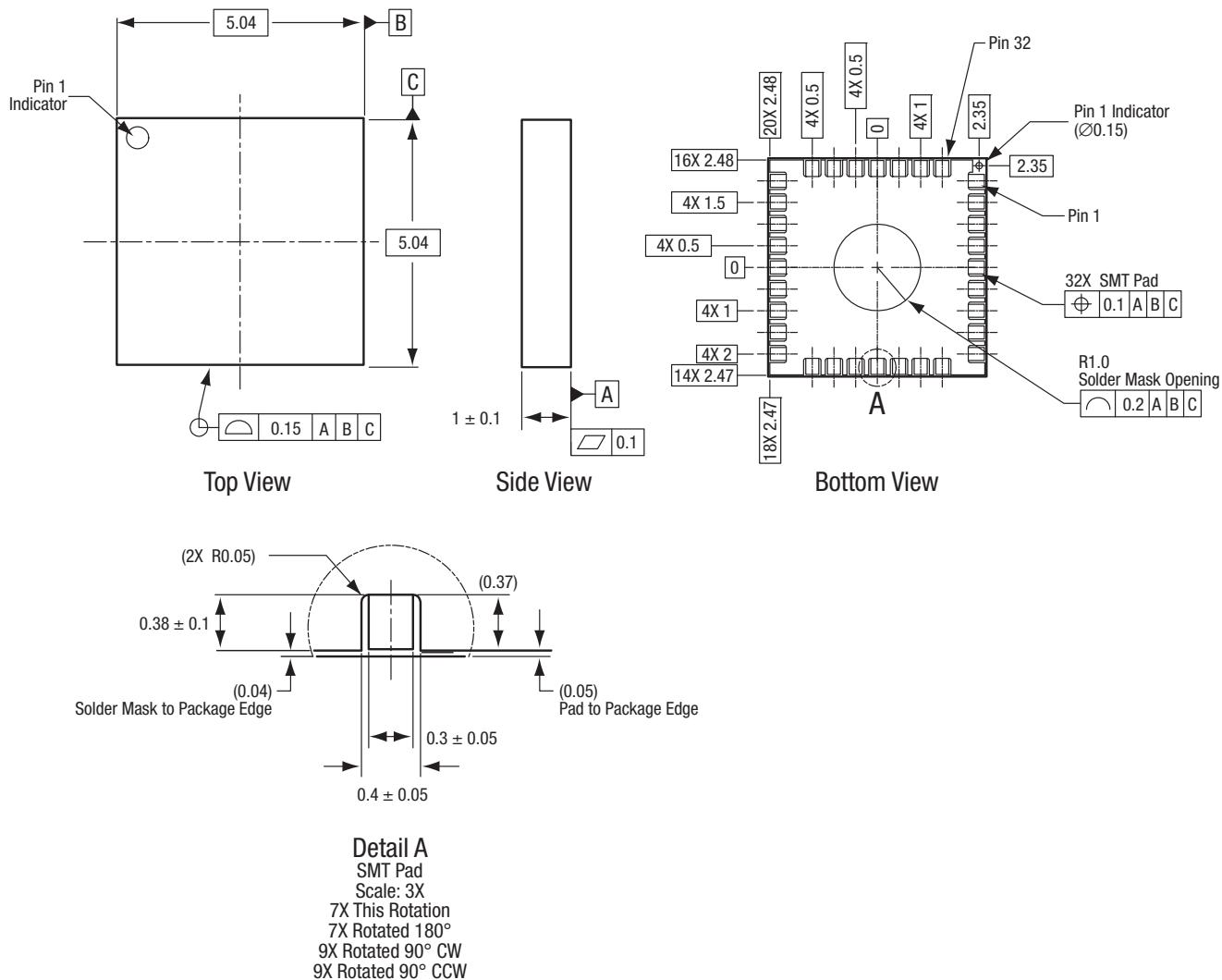

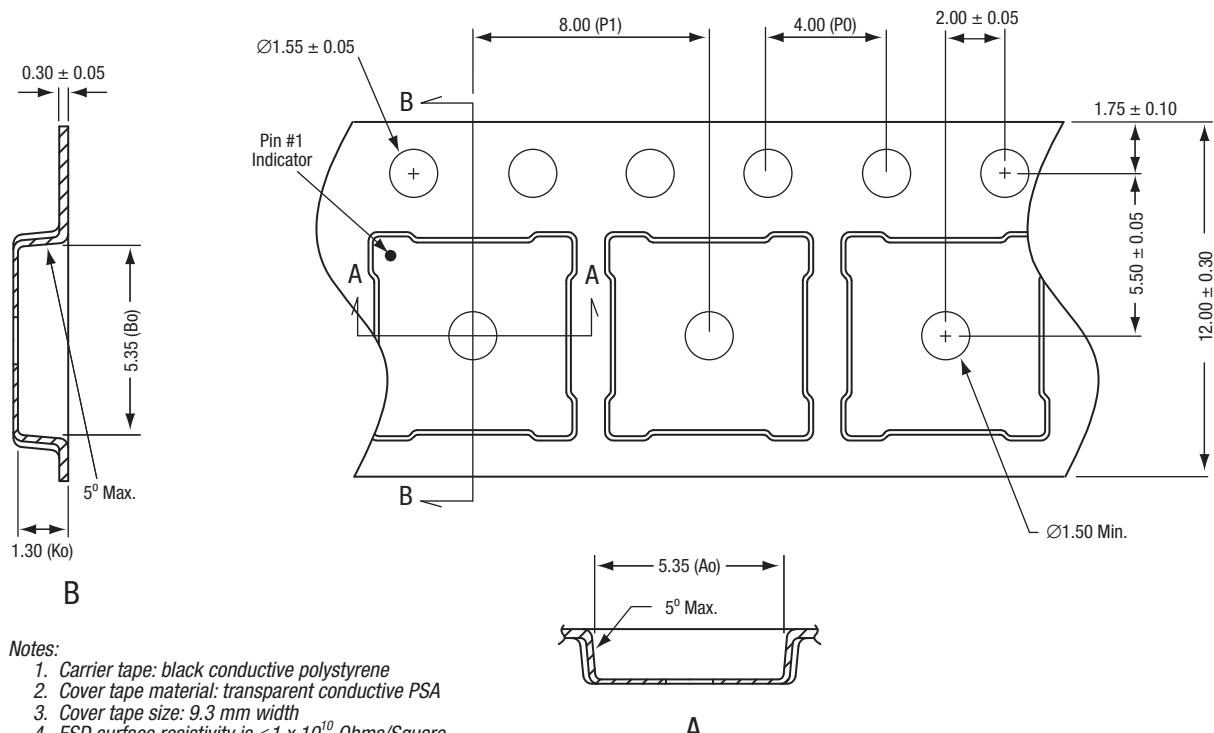

The PCB layout footprint for the SKY73134-11 is provided in Figure 23. Figure 24 shows the package dimensions for the 25-pin RFLGA and Figure 25 provides the tape and reel dimensions.

## Package and Handling Information

Since the device package is sensitive to moisture absorption, it is baked and vacuum packed before shipping. Instructions on the shipping container label regarding exposure to moisture after the container seal is broken must be followed. Otherwise, problems related to moisture absorption may occur when the part is subjected to high temperature during solder assembly.

THE SKY73134-11 is rated to Moisture Sensitivity Level 3 (MSL3) at 260 °C. It can be used for lead or lead-free soldering. For additional information, refer to the Skyworks Application Note, *PCB Design & SMT Assembly/Rework Guidelines for RFLGA Packages*, document number 103147.

Care must be taken when attaching this product, whether it is done manually or in a production solder reflow environment. Production quantities of this product are shipped in a standard tape and reel format.

Layer 1: Top – Metal

Layer 2: Ground

Layer 3: Power Plane

Layer 4: Solid Ground Plane

S1852

**Figure 21. SKY73134-11 Evaluation Board Layer Detail**

All dimensions are in millimeters

S2748

Figure 23. PCB Layout Footprint for the SKY73134-11 5 x 5 mm RFLGA

All measurements are in millimeters

Dimensioning and tolerancing according to ASME Y14.5M-1994

S2747

Figure 24. SKY73134-11 32-Pin RFLGA Package Dimensions

S461b

Figure 25. SKY73134-11 Tape and Reel Dimensions

## Ordering Information

| Model Name                        | Manufacturing Part Number | Evaluation Board Part Number |

|-----------------------------------|---------------------------|------------------------------|

| SKY73134-11 Frequency Synthesizer | SKY73134-11               | TW18-D170                    |

Copyright © 2009, 2010, 2011 Skyworks Solutions, Inc. All Rights Reserved.

Information in this document is provided in connection with Skyworks Solutions, Inc. ("Skyworks") products or services. These materials, including the information contained herein, are provided by Skyworks as a service to its customers and may be used for informational purposes only by the customer. Skyworks assumes no responsibility for errors or omissions in these materials or the information contained herein. Skyworks may change its documentation, products, services, specifications or product descriptions at any time, without notice. Skyworks makes no commitment to update the materials or information and shall have no responsibility whatsoever for conflicts, incompatibilities, or other difficulties arising from any future changes.

No license, whether express, implied, by estoppel or otherwise, is granted to any intellectual property rights by this document. Skyworks assumes no liability for any materials, products or information provided hereunder, including the sale, distribution, reproduction or use of Skyworks products, information or materials, except as may be provided in Skyworks Terms and Conditions of Sale.

THE MATERIALS, PRODUCTS AND INFORMATION ARE PROVIDED "AS IS" WITHOUT WARRANTY OF ANY KIND, WHETHER EXPRESS, IMPLIED, STATUTORY, OR OTHERWISE, INCLUDING FITNESS FOR A PARTICULAR PURPOSE OR USE, MERCHANTABILITY, PERFORMANCE, QUALITY OR NON-INFRINGEMENT OF ANY INTELLECTUAL PROPERTY RIGHT; ALL SUCH WARRANTIES ARE HEREBY EXPRESSLY DISCLAIMED. SKYWORKS DOES NOT WARRANT THE ACCURACY OR COMPLETENESS OF THE INFORMATION, TEXT, GRAPHICS OR OTHER ITEMS CONTAINED WITHIN THESE MATERIALS. SKYWORKS SHALL NOT BE LIABLE FOR ANY DAMAGES, INCLUDING BUT NOT LIMITED TO ANY SPECIAL, INDIRECT, INCIDENTAL, STATUTORY, OR CONSEQUENTIAL DAMAGES, INCLUDING WITHOUT LIMITATION, LOST REVENUES OR LOST PROFITS THAT MAY RESULT FROM THE USE OF THE MATERIALS OR INFORMATION, WHETHER OR NOT THE RECIPIENT OF MATERIALS HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

Skyworks products are not intended for use in medical, lifesaving or life-sustaining applications, or other equipment in which the failure of the Skyworks products could lead to personal injury, death, physical or environmental damage. Skyworks customers using or selling Skyworks products for use in such applications do so at their own risk and agree to fully indemnify Skyworks for any damages resulting from such improper use or sale.

Customers are responsible for their products and applications using Skyworks products, which may deviate from published specifications as a result of design defects, errors, or operation of products outside of published parameters or design specifications. Customers should include design and operating safeguards to minimize these and other risks. Skyworks assumes no liability for applications assistance, customer product design, or damage to any equipment resulting from the use of Skyworks products outside of stated published specifications or parameters.

Skyworks, the Skyworks symbol, and "Breakthrough Simplicity" are trademarks or registered trademarks of Skyworks Solutions, Inc., in the United States and other countries. Third-party brands and names are for identification purposes only, and are the property of their respective owners. Additional information, including relevant terms and conditions, posted at [www.skyworksinc.com](http://www.skyworksinc.com), are incorporated by reference.