PO. BOX 20912 • PHOENIX, ARIZONA 85036

# MC3417, MC3517 MC3418, MC3518

# Specifications and Applications Information

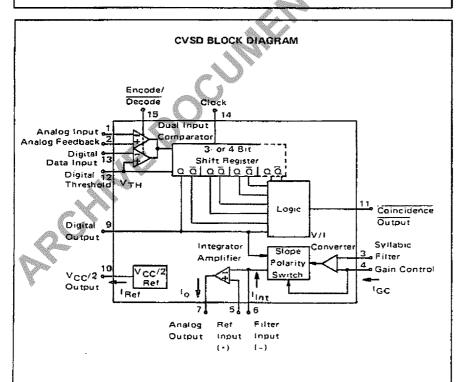

# CONTINUOUSLY VARIABLE SLOPE DELTA MODULATOR/DEMODULATOR

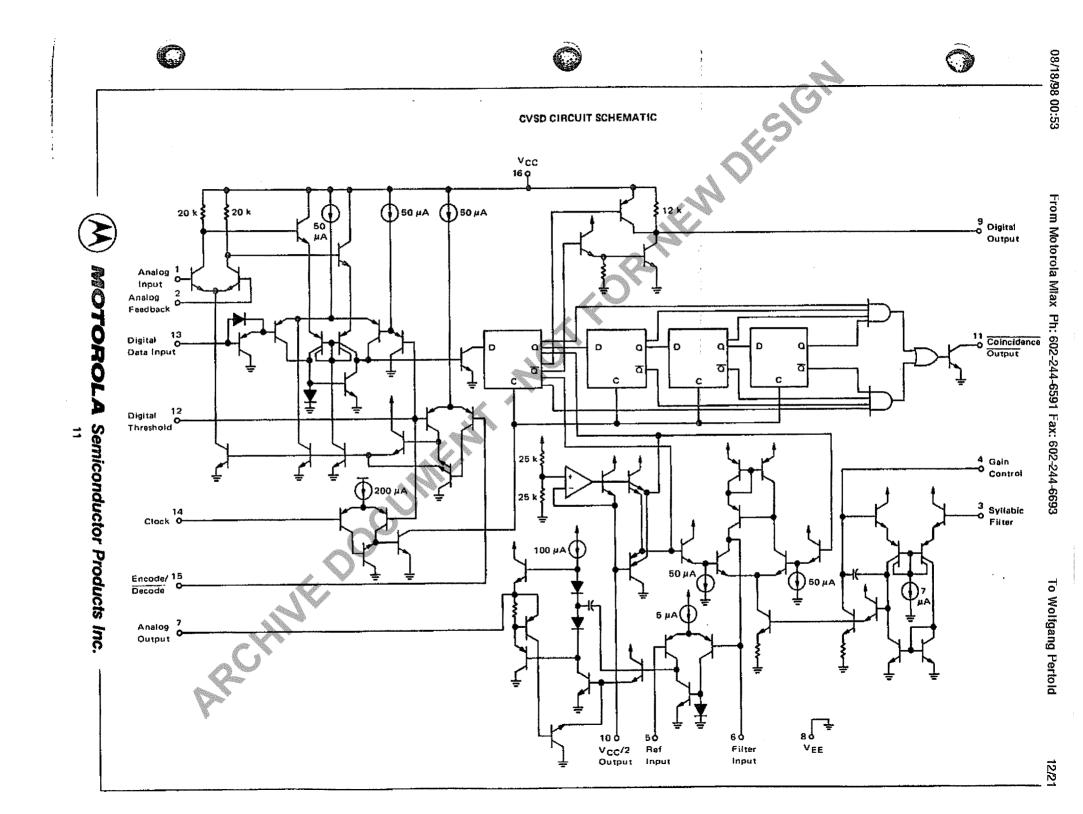

Providing a simplified approach to digital speech encoding/ decoding, the MC3517/18 series of CVSDs is designed for military secure communication and commercial telephone applications. A single IC provides both encoding and decoding functions.

- Encode and Decode Functions on the Same Chip with a Digital Input for Selection

- Utilization of Compatible I<sup>2</sup>L Linear Bipolar Technology

- CMOS Compatible Digital Output

- Digital Input Threshold Selectable (VCC/2 reference provided on chip)

- MC3417/MC3517 has a 3-Bit Algorithm (General Communications)

- MC3418/MC3518 has a 4-Bit Algorithm (Commercial Telephone)

### CONTINUOUSLY VARIABLE SLOPE DELTA MODULATOR/DEMODULATOR

LASER-TRIMMED INTEGRATED CIRCUIT

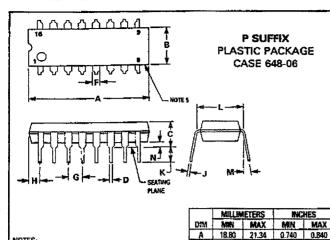

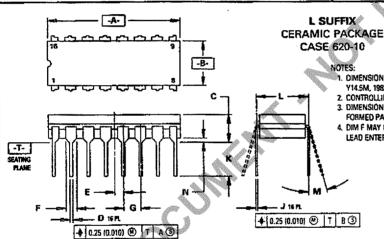

L SUFFIX CERAMIC PACKAGE CASE 620-10 P SUFFIX

PLASTIC PACKAGE

CASE 648-06

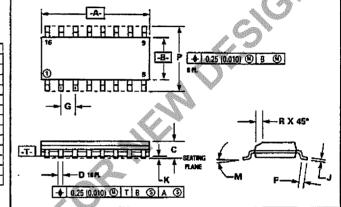

DW SUFFIX PLASTIC PACKAGE CASE 751G-01 SO-16L

### PIN CONNECTIONS 16 VCC Input Analog Encode/ 2 eedback Syllabic 3 Clock Filter Digital Data Gain 13 Control Input (-) Digital 5 12 Input (+) Threshold Filter Coincidance Ģ Output Input (-) Analog /CC/2 10 Output Output

### ORDERING INFORMATION

| Device   | Package      | Temperature<br>Range |  |

|----------|--------------|----------------------|--|

| MC3417L  | Ceramic DIP  | 0°C to +70°C         |  |

| MC3418DW | Plastic SOIC | 0°C to +70°C         |  |

| MC3418L  | Ceramic DIP  | 0°C to +70°C         |  |

| MC3418P  | Plastic DIP  | 0°C to +70°C         |  |

| MC3517L  | Ceramic DIP  | -55°C to +125°C      |  |

| MC3518L  | Ceramic DIP  | -55°C to +125°C      |  |

**@MOTOROLA INC., 1988**

VEE | 8

DS9488R2

Digital

Output

9

### **MAXIMUM RATINGS**

(All voltages referenced to VEE, TA = 25°C unless otherwise noted.)

| Rating                                                      | Symbol               | Value                                       | Unit |

|-------------------------------------------------------------|----------------------|---------------------------------------------|------|

| Power Supply Voltage                                        | Vcc                  | -0.4 to +18                                 | Vdc  |

| Differential Analog Input Voltage                           | VID                  | ± 5.0                                       | Vdc  |

| Digital Threshold Voltage                                   | VTH                  | -0.4 to V <sub>CC</sub>                     | Vdc  |

| Logic Input Voltage<br>(Clock, Digital Data, Encode/Decode) | VLogic               | -0.4 to +18                                 | Vdc  |

| Coincidence Output Voltage                                  | V <sub>O</sub> (Con) | -0.4 to +18                                 | Vďc  |

| Syllabic Filter Input Voltage                               | V <sub>I</sub> (SyI) | -0.4 to V <sub>CC</sub>                     | Vdc  |

| Gain Control Input Voltage                                  | VHGC)                | -0.4 to V <sub>CC</sub>                     | Vdc  |

| Reference Input Voltage                                     | V <sub>I</sub> (Ref) | V <sub>CC</sub> /2 - 1.0 to V <sub>CC</sub> | Vdc  |

| V <sub>CC</sub> /2 Output Current                           | Ref                  | -25                                         | mA   |

### **ELECTRICAL CHARACTERISTICS**

$(V_{CC} = 12 \text{ V}, V_{EE} = \text{Gnd}, T_A = 0^{\circ}\text{C to} + 70^{\circ}\text{C for MC3417/18}, T_A = -55^{\circ}\text{C to} + 125^{\circ}\text{C for MC3517/18 unless otherwise noted.})$

|                                                                                                       |                      | MC3417/MC3517 |            | 517                  | 7 MC3418/MC3518 |            |                       |      |

|-------------------------------------------------------------------------------------------------------|----------------------|---------------|------------|----------------------|-----------------|------------|-----------------------|------|

| Characteristic                                                                                        | Symbol               | Min           | Тур        | Max                  | Min             | Тур        | Max                   | Unit |

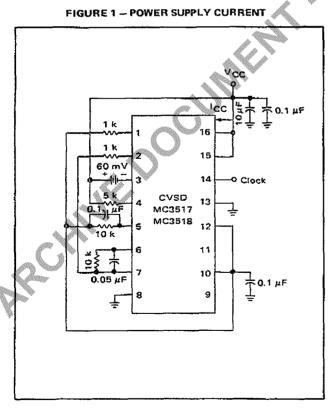

| Power Supply Voltage Range (Figure 1)                                                                 | VCCR                 | 4.75          | 12         | 16.5                 | 4.75            | 12         | 16.5                  | Vdc  |

| Power Supply Current (Figure 1)<br>(@ Idle Channel)                                                   | lcc                  |               |            | A                    |                 |            |                       | mA   |

| (VCC = 5.0 V, All except MC3418P,DW)                                                                  |                      | _             | 3.7        | 5.0                  |                 | 3.7        | 5.0                   |      |

| (V <sub>CC</sub> = 5.0 V, MC3418P,DW)<br>(V <sub>CC</sub> = 15 V, All except MC3418P,DW)              |                      |               | 6.0        | 10                   | _               | 3.7<br>6.0 | 5.5<br>10             |      |

| (V <sub>CC</sub> = 15 V, MC3418P,DW)                                                                  |                      | _             | -          |                      | _               | 6.0        | 11                    |      |

| Gain Control Current Range (Figure 2)                                                                 | IGCR                 | 0.002         | /          | 3.0                  | 0.002           |            | 3.0                   | mA   |

| Analog Comparator Input Range<br>(Pins 1 and 2)<br>(4.75 V ≤ V <sub>CC</sub> ≤ 16.5 V)                | VI                   | 1.3           | (5)        | V <sub>CC</sub> -1.3 | 1.3             |            | V <sub>CC</sub> - 1.3 | Vdc  |

| Analog Output Range (Pin 7)<br>(4.75 V ≤ V <sub>CC</sub> ≤ 16.5 V, l <sub>O</sub> = ±5.0 mA)          | v <sub>O</sub>       | 1.3           | -          | V <sub>CC</sub> -1.3 | 1.3             | _          | V <sub>CC</sub> -1.3  | Vdc  |

| Input Bias Currents (Figure 3)<br>(Comparator in Active Region)                                       | ηВ                   |               |            |                      | _               |            |                       | μΑ   |

| Analog Input (I1)                                                                                     | All the second       |               | 0.5        | 1.5                  |                 | 0.25       | 1.0                   |      |

| Analog Feedback (I2)                                                                                  |                      | _             | 0.5        | 1.5                  | _               | 0.25       | 1.0                   |      |

| Syllabic Filter Input (I3)                                                                            |                      | <b>№</b> —    | 0.06       | 0.5                  | _               | 0.06       | 0.3                   |      |

| Reference Input (I5)                                                                                  |                      |               | -0.06      | 0.5                  |                 | -0.06      | -0.3                  |      |

| Input Offset Current (Comparator in Active Region) Analog Input/Analog Feedback                       | lio                  |               | 0,15       | 0.6                  |                 | 0.05       | 0.4                   | μΑ   |

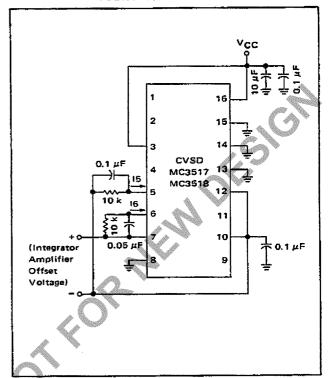

| 11 – 12  — Figure 3<br> Integrator Amplifier<br> 15 – 16  — Figure 4                                  |                      | _             | 0.02       | 0.2                  | -               | 0.05       | 0.1                   |      |

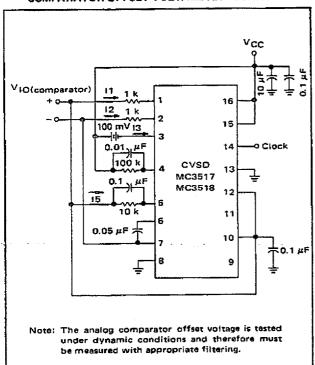

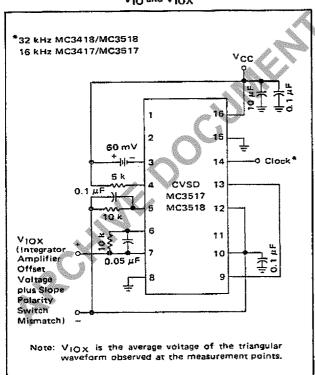

| Input Offset Voltage V/I Converter (Pins 3 and 4) — Figure 5                                          | VIO                  | _             | 2.0        | 6.0                  |                 | 2.0        | 6.0                   | mV   |

| Transconductance                                                                                      | gm                   |               |            |                      |                 |            | 1                     | mA/m |

| V/I Converter, 0 to 3.0 mA                                                                            | _                    | 0.1           | 0.3        | <b>–</b>             | 0.1             | 0.3        | -                     |      |

| Integrator Amplifier, 0 to ±5.0 mA Load                                                               |                      | 1.0           | 10         |                      | 1.0             | 10         | _                     |      |

| Propagation Delay Times (Note 1)                                                                      |                      |               |            |                      |                 |            |                       | μs   |

| Clock Trigger to Digital Output                                                                       | tPLH                 | _             | 1.0        | 2.5                  | _               | 1.0        | 2.5                   |      |

| (CL = 25 pF to Gnd) Clock Trigger to Coincidence Output                                               | tPHL                 | _             | 0.8<br>1.0 | 2.5<br>3.0           |                 | 0.8<br>1.0 | 2.5<br>3.0            |      |

| (C <sub>L</sub> = 25 pF to Gnd)                                                                       | tPLH<br>tPHL         | _             | 0.8        | 2.0                  |                 | 0.8        | 2.0                   |      |

| $(R_L = 4.0 \text{ k}\Omega \text{ to VCC})$                                                          | ירוקג.               |               | 2.0        |                      |                 | 0.0        |                       |      |

| Coincidence Output Voltage —                                                                          | VOL(Con)             | _             | 0.12       | 0.25                 | _               | 0.12       | 0.25                  | Vdc  |

| Low Logic State                                                                                       |                      |               |            |                      |                 |            |                       |      |

| $(I_{OL(Con)} = 3.0 \text{ mA})$                                                                      |                      |               |            |                      |                 |            | ļ                     |      |

| Coincidence Output Leakage Current —<br>High Logic State<br>(VOH = 15 V, 0°C ≤ T <sub>A</sub> ≤ 70°C) | <sup>I</sup> OH(Con) | _             | 0.01       | 0.5                  |                 | 0.01       | 0.5                   | μΑ   |

NOTE 1. All propagation delay times measured 50% to 50% from the negative going (from VCC to +0.4 V) edge of the clock.

### **ELECTRICAL CHARACTERISTICS (continued)**

|                                                                                                                                                   | ]                      | MC3417/MC3517                                  |                              | MC3418/MC3518           |                              |                              |                         |          |

|---------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------------------------------------------------|------------------------------|-------------------------|------------------------------|------------------------------|-------------------------|----------|

| Characteristic                                                                                                                                    | Symbol                 | Min                                            | Тур                          | Max                     | Min                          | Тур                          | Max                     | Uni      |

| Applied Digital Threshold Voltage Range<br>(Pin 12)                                                                                               | VTH                    | +1.2                                           | -                            | VCC - 2.0               | +1.2                         | -                            | V <sub>CC</sub> -2.0    | Vdo      |

| Digital Threshold Input Current (1.2 V ≤ V <sub>th</sub> ≤ V <sub>CC</sub> − 2.0 V) (V <sub>IL</sub> applied to Pins 13, 14 and 15)               | l(th)                  |                                                |                              | 5.0                     |                              |                              |                         | μΑ       |

| (V <sub>IH</sub> applied to Pins 13, 14 and 15)                                                                                                   |                        | =                                              | -10                          | 5.0<br>- 50             | =                            | -10                          | 5.0<br>- 50             |          |

| Maximum Integrator Amplifier Output Current                                                                                                       | lo                     | ± 5.0                                          | -                            | _                       | ±5.0                         | _                            |                         | mΑ       |

| V <sub>CC</sub> /2 Generator Maximum Output Current<br>(Source only)                                                                              | IRef                   | +10                                            | _                            | _                       | +10                          |                              | -                       | mA       |

| V <sub>CC</sub> /2 Generator Output Impedance<br>(0 to +10 mA)                                                                                    | <sup>z</sup> Ref       | _                                              | 3.0                          | 6.0                     | _                            | 3.0                          | 6.0                     | Ω        |

| V <sub>CC</sub> /2 Generator Tolerance<br>(4.75 V ≤ V <sub>CC</sub> ≤ 16.5 V)                                                                     | eΓ                     | -                                              |                              | ±3.5                    | _                            | - (                          | ±3.5                    | %        |

| Logic Input Voltage (Pins 13, 14 and 15)<br>Low Logic State<br>High Logic State                                                                   | V <sub>IL</sub><br>VIH | Gnd<br>V <sub>th</sub> + 0.4                   | =                            | V <sub>th</sub> - 0.4   | Gnd<br>V <sub>th</sub> + 0.4 | 3                            | V <sub>th</sub> ~ 0.4   | Vdc      |

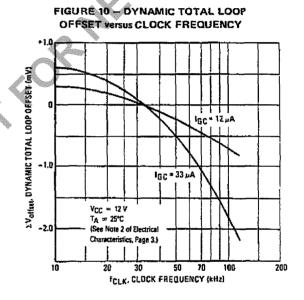

| Dynamic Total Loop Offset Voltage (Note 2) — Figures 3, 4 and 5  IGC = 12 μΑ, V <sub>CC</sub> = 12 V  Τ <sub>A</sub> = 25°C (All except 3418P,DW) | ∑Voffset               |                                                |                              |                         |                              |                              |                         | mV       |

| (MC3418P,DW)<br>$0^{\circ}C \leq T_{A} \leq +70^{\circ}C (MC3417/18L)$<br>(MC3418P,DW)                                                            |                        |                                                |                              |                         | Z                            | ±0.5<br>±0.5<br>±0.75        | ±1.5<br>±3.0<br>±2.3    |          |

| -55°C ≤ T <sub>A</sub> ≤ +125°C (MC3517/18)<br>I <sub>GC</sub> = 33 μA, V <sub>CC</sub> = 12 V<br>T <sub>A</sub> = 25°C                           |                        | <del></del>                                    |                              |                         | <b>=</b> .                   | ±0.75<br>±1.5                | ±3.8<br>±4.0            |          |

| $^{1}$ GC ≈ TA ≈ +70°C (MC3417/18)<br>$^{1}$ GC ≈ TA ≈ +125°C (MC3517/18)<br>$^{1}$ GC = 12 $\mu$ A, VCC = 5.0 V                                  |                        | =                                              | ±2.5<br>±3.0<br>±4.5         | ± 5.0<br>± 7.5<br>± 10  | =                            |                              |                         |          |

| T <sub>A</sub> = 25°C (All except MC3418P,DW)<br>(MC3418P,DW)<br>0°C ≤ T <sub>A</sub> ≤ +70°C (MC3417/18L)                                        |                        | _                                              |                              | _                       | _                            | ±1.0<br>±1.0                 | ± 2.0<br>± 3.5          |          |

| (MC3418P,DW)<br>-55°C ≤ T <sub>A</sub> ≤ + 125°C (MC3517/18)<br>I <sub>GC</sub> = 33 μA, V <sub>CC</sub> = 5.0 V                                  | !                      | =                                              | =                            | _                       |                              | ±1.3<br>±1.3<br>±2.5         | ± 2.8<br>± 4.3<br>± 5.0 |          |

| T <sub>A</sub> = 25°C<br>0°C ≤ T <sub>A</sub> ≤ +70°C (MC3417/18)<br>-55°C ≤ T <sub>A</sub> ≤ +125°C (MC3517/18)                                  |                        | <i>♣</i> = = = = = = = = = = = = = = = = = = = | ±4.0<br>±4.5<br>±5.5         | ± 6.0<br>± 8.0<br>± 10  | =                            |                              | _                       |          |

| Digital Output Voltage (IOL = 3.6 mA) (IOH = -0.35 mA)                                                                                            | V <sub>OL</sub><br>VOH | V <sub>CC</sub> = 1.0                          | 0.1<br>V <sub>CC</sub> – 0.2 | 0.4                     | -<br>V <sub>CC</sub> -1.0    | 0.1<br>V <sub>CC</sub> – 0.2 | 0.4                     | Vdc      |

| Syllabic Filter Applied Voltage (Pin 3)<br>(Figure 2)                                                                                             | VI(Syl)                | + 3.2                                          | -                            | Vcc                     | +3.2                         | -                            | VCC                     | Vdc      |

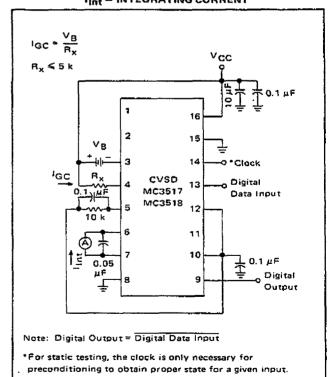

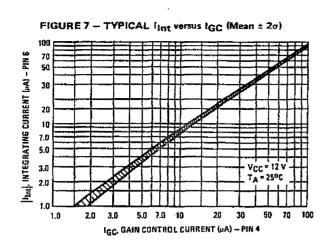

| ntegrating Current (Figure 2)<br>(IGC = 12 µA)                                                                                                    | I <sub>Int</sub>       | 8.0                                            | 10                           | 12                      | 8.0                          | 10                           | 12                      | μА       |

| (IGC = 1.5 mA) (All except 3418P,DW)<br>(MC3418P,DW)<br>(IGC = 3.0 mA)                                                                            |                        | 1.45<br><br>2.75                               | 1.5<br>—<br>3.0              | 1.55<br>—<br>3.25       | 1.45<br>1.42<br>2.75         | 1.5<br>1.5<br>3.0            | 1.55<br>1.58            | mA<br>mA |

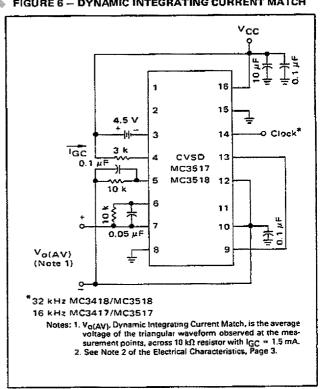

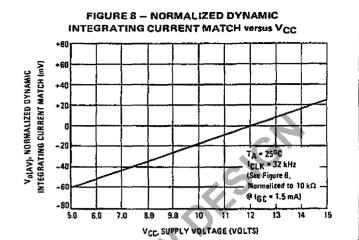

| lynamic Integrating Current Match (IGC = 1.5 mA) Figure 6                                                                                         | VO(Ave)                | ±.,,                                           | 5.0                          | 5.25                    | 2./3                         | 3.0                          | 3.25                    | mA<br>mV |

| (Åll except MC3418P,DW)<br>(MC3418P,DW)                                                                                                           |                        | _                                              | ± 100<br>—                   | ± 250                   | _                            | ± 100<br>± 100               | ± 250<br>± 280          |          |

| nput Current — High Logic State<br>(V <sub>IH</sub> = 18 V)<br>Digital Data Input                                                                 | lH                     |                                                |                              |                         |                              |                              | _                       | μΑ       |

| Clock Input Encode/Decode Input                                                                                                                   |                        | _                                              | _                            | + 5.0<br>+ 5.0<br>+ 5.0 | _                            | _                            | +5.0<br>+5.0<br>+5.0    |          |

| put Current — Low Logic State (V <sub> L</sub> = 0 V)                                                                                             | liL                    |                                                |                              |                         |                              |                              |                         | μА       |

| Digital Data Input Clock Input Encode/Decode Input                                                                                                |                        | _                                              |                              | - 10<br>- 360<br>- 36   |                              | _                            | - 10<br>- 360<br>- 36   |          |

NOTE 2. Dynamic total loop offset (ΣV<sub>offset</sub>) equals V<sub>IO</sub> (comparator) (Figure 3) minus V<sub>IOX</sub> (Figure 5). The input offset voltages of the analog comparator and of the integrator amplifier include the effects of input offset current through the input resistors. The slope polarity switch current mismatch appears as an average voltage across the 10 k integrator resistor. For the MC3417/MC3517, the clock frequency is 16 kHz. For the MC3418/ MC3518, the clock frequency is 32 kHz. Idle channel performance is guaranteed if this dynamic total loop offset is less than one-half of the change in integrator output voltage during one clock cycle (ramp step size). Laser trimming is used to insure good idle channel performance.

# MC3417 ● MC3517 ● MC3418 ● MC3518

### **DEFINITIONS AND FUNCTION OF PINS**

### Pin 1 - Analog Input

This is the analog comparator inverting input where the voice signal is applied. It may be ac or dc coupled depending on the application. If the voice signal is to be level shifted to the internal reference voltage, then a bias resistor between Pins 1 and 10 is used. The resistor is used to establish the reference as the new dc average of the ac coupled signal. The analog comparator was designed for low hysteresis (typically less than 0.1 mV) and high gain (typically 70 dB).

### Pin 2 - Analog Feedback

This is the noninverting input to the analog signal comparator within the IC. In an encoder application it should be connected to the analog output of the encoder circuit. This may be Pin 7 or a low pass filter output connected to Pin 7. In a decode circuit Pin 2 is not used and may be tied to VCC/2 on Pin 10, ground or left open. The analog input comparator has bias currents of 1.5 µA max, thus the driving impedances of Pins 1 and 2 should be equal to avoid disturbing the idle channel characteristics of the encoder.

### Pin 3 - Syllabic Filter

This is the point at which the syllabic filter voltage is returned to the IC in order to control the integrator step size. It is an NPN input to an op amp. The syllabic filter consists of an RC network between Pins 11 and 3. Typical time constant values of 6.0 ms to 50 ms are used in voice codecs.

### Pin 4 - Gain Control Input

The syllabic filter voltage appears across Cg of the syllabic filter and is the voltage between VCC and Pin 3. The active voltage to current (V-I) converter drives Pin 4 to the same voltage at a slew rate of typically 0.5 V/ $\mu$ s. Thus the current injected into Pin 4 (IGC) is the syllabic filter voltage divided by the R<sub>X</sub> resistance. Figure 7 shows the relationship between IGC (x-axis) and the integrating current, IInt (y-axis). The discrepancy, which is most significant at very low currents, is due to circuitry within the slope polarity switch which enables trimming to a low total loop offset. The R<sub>X</sub> resistor is then varied to adjust the loop gain of the codec, but should be no larger than 5.0 k $\Omega$  to maintain stability.

### Pin 5 - Reference Input

This pin is the noninverting input of the integrator amplifier. It is used to reference the dc level of the output signal. In an encoder circuit it must reference the same voltage as Pin 1 and is tied to Pin 10.

### Pin 6 — Filter Input

This inverting op amp input is used to connect the integrator external components. The integrating current (I<sub>Int</sub>) flows into Pin 6 when the analog input (Pin 1) is high with respect to the analog feedback (Pin 2) in

the encode mode or when the digital data input (Pin 13) is high in the decode mode. For the opposite states,  $I_{Int}$  flows out of Pin 6. Single integration systems require a capacitor and resistor between Pins 6 and 7. Multipole configurations will have different circuitry. The resistance between Pins 6 and 7 should always be between 8.0 k $\Omega$  and 13 k $\Omega$  to maintain good idle channel characteristics.

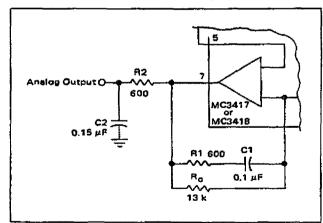

### Pin 7 — Analog Output

This is the integrator op amp output. It is capable of driving a 600-ohm load referenced to VCC/2 to +6.0 dBm and can otherwise be treated as an op amp output. Pins 5, 6, and 7 provide full access to the integrator op amp for designing integration filter networks. The slew rate of the internally compensated integrator op amp is typically 0.5  $V/\mu s$ . Pin 7 output is current limited for both polarities of current flow at typically 30 mA.

### Pin 8 - VEE

The circuit is designed to work in either single or dual power supply applications. Pin 8 is always connected to the most negative supply.

### Pin 9 — Digital Output

The digital output provides the results of the delta modulator's conversion. It swings between  $V_{CC}$  and VEE and is CMOS or TTL compatible. Pin 9 is inverting with respect to Pin 1 and non-inverting with respect to Pin 2. It is clocked on the falling edge of Pin 14. The typical 10% to 90% rise and fall times are 250 ns and 50 ns respectively for  $V_{CC}=12$  V and  $C_L=25$  pF to ground.

### Pin 10 - V<sub>CC</sub>/2 Output

An internal low impedance mid-supply reference is provided for use of the MC3417/18 in single supply applications. The internal regulator is a current source and must be loaded with a resistor to insure its sinking capability. If a +6.0 dBmo signal is expected across a 600 ohm input bias resistor, then Pin 10 must sink 2.2 V/600  $\Omega=3.66$  mA. This is only possible if Pin 10 sources 3.66 mA into a resistor normally and will source only the difference under peak load. The reference load resistor is chosen accordingly. A 0.1  $\mu\text{F}$  bypass capacitor from Pin 10 to VEE is also recommended. The VCC/2 reference is capable of sourcing 10 mA and can be used as a reference elsewhere in the system circuitry.

### Pin 11 — Coincidence Output

The duty cycle of this pin is proportional to the voltage across C<sub>S</sub>. The coincidence output will be low whenever the content of the internal shift register is all 1s or all 0s. In the MC3417 the register is 3 bits long while the MC3418 contains a 4 bit register. Pin 11 is an open collector of an NPN device and requires a pull-up resistor.

If the syllabic filter is to have equal charge and discharge time constants, the value of Rp should be much less than Rs. In systems requiring different charge and discharge constants, the charging constant is RsCs while the decaying constant is (Rs + Rp)Cs. Thus longer decays are easily achievable. The NPN device should not be required to sink more than 3.0 mA in any configuration. The typical 10% to 90% rise and fall times are 200 ns and 100 ns respectively for RL = 4.0 k $\Omega$  to +12 V and CL = 25 pF to ground.

### Pin 12 - Digital Threshold

This input sets the switching threshold for Pins 13, 14, and 15. It is intended to aid in interfacing different logic families without external parts. Often it is connected to the  $V_{\rm CC}/2$  reference for CMOS interface or can be biased two diode drops above  $V_{\rm EE}$  for TTL interface.

### Pin 13 - Digital Data Input

In a decode application, the digital data stream is applied to Pin 13. In an encoder it may be unused or may be used to transmit signaling message under the control of Pin 15. It is an inverting input with respect to Pin 9. When Pins 9 and 13 are connected, a toggle flipflop is formed and a forced idle channel pattern can be transmitted. The digital data input level should be main-

tained for 0.5  $\mu s$  before and after the clock trigger for proper clocking.

### Pin 14 — Clock Input

The clock input determines the data rate of the codec circuit. A 32K bit rate requires a 32 kHz clock. The switching threshold of the clock input is set by Pin 12. The shift register circuit toggles on the falling edge of the clock input. The minimum width for a positive-going pulse on the clock input is 300 ns, whereas for a negative-going pulse, it is 900 ns.

### Pin 15 — Encode/Decode

This pin controls the connection of the analog input comparator and the digital input comparator to the internal shift register. If high, the result of the analog comparison will be clocked into the register on the falling edge at Pin 14. If low, the digital input state will be entered. This allows use of the IC as an encoder/decoder or simplex codec without external parts. Furthermore, it allows non-voice patterns to be forced onto the transmission line through Pin 13 in an encoder.

### Pin 16 - VCC

The power supply range is from 4.75 to 16.5 volts between Pin V<sub>CC</sub> and V<sub>EE</sub>.

FIGURE 2 — IGCR. GAIN CONTROL RANGE and I<sub>Int</sub> — INTEGRATING CURRENT

### FIGURE 3 - INPUT BIAS CURRENTS, ANALOG COMPARATOR OFFSET VOLTAGE AND CURRENT

### FIGURES - V/I CONVERTER OFFSET VOLTAGE, VIO and VIOX

### FIGURE 4 - INTEGRATOR AMPLIFIER OFFSET **VOLTAGE AND CURRENT**

### FIGURE 6 - DYNAMIC INTEGRATING CURRENT MATCH

MOTOROLA Semiconductor Products Inc.

1

**TYPICAL PERFORMANCE CURVES**

# MC3417 • MC3517 • MC3418 • MC3518

FIGURE 9 - NORMALIZED DYNAMIC INTEGRATING **CURRENT MATCH versus CLOCK FREQUENCY** +25 V<sub>o(</sub>AV), NORMALIZED DYNAMIC INTEGRATING CURRENT MATCH ImV) -25 -50 TA = 25°C VCC = 12 V (See Figure 6. ~75 Normalized to 10 kΩ @ IgC = 1.5 mA) -100 20 40 50 ICLK, CLOCK FREQUENCY (kHz)

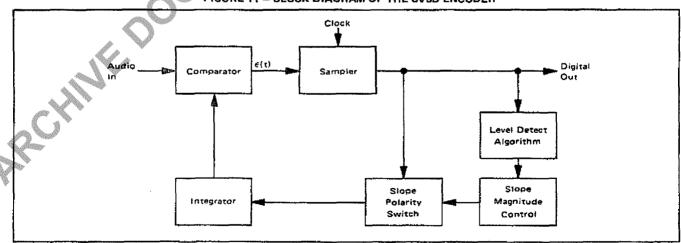

FIGURE 11 - BLOCK DIAGRAM OF THE CVSD ENCODER

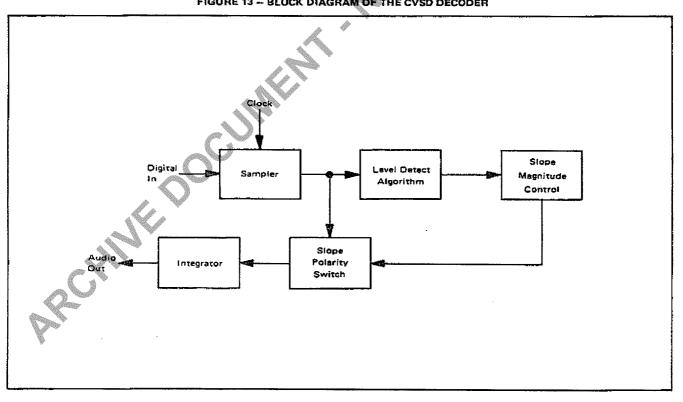

FIGURE 13 - BLOCK DIAGRAM OF THE CVSD DECODER

### CIRCUIT DESCRIPTION

The continuously variable slope delta modulator (CVSD) is a simple alternative to more complex conventional conversion techniques in systems requiring digital communication of analog signals. The human voice is analog, but digital transmission of any signal over great distance is attractive. Signal/noise ratios do not vary with distance in digital transmission and multiplexing, switching and repeating hardware is more economical and easier to design. However, instrumentation A to D converters do not meet the communications requirements. The CVSD A to D is well suited to the requirements of digital communications and is an economically efficient means of digitizing analog inputs for transmission.

### The Deita Modulator

The innermost control loop of a CVSD converter is a simple delta modulator. A block diagram CVSD Encoder is shown in Figure 11. A delta modulator consists of a comparator in the forward path and an integrator in the feedback path of a simple control loop. The inputs to the comparator are the input analog signal and the integrator output. The comparator output reflects the

sign of the difference between the input voltage and the integrator output. That sign bit is the digital output and also controls the direction of ramp in the integrator. The comparator is normally clocked so as to produce a synchronous and band limited digital bit stream.

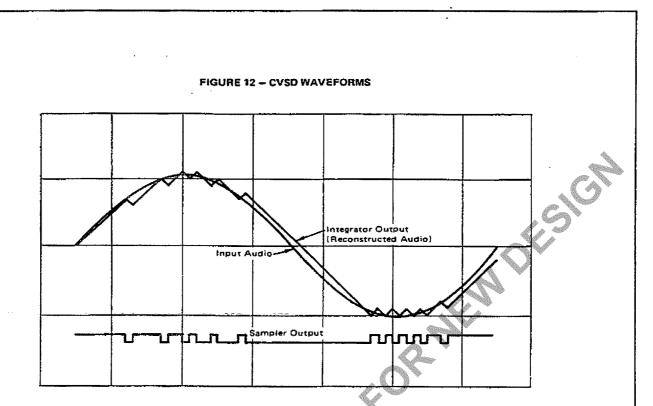

If the clocked serial bit stream is transmitted. received, and delivered to a similar integrator at a remote point, the remote integrator output is a copy of the transmitting control loop integrator output. To the extent that the integrator at the transmitting locations tracks the input signal, the remote receiver reproduces the input signal. Low pass filtering at the receiver output will eliminate most of the quantizing noise, if the clock rate of the bit stream is an octave or more above the bandwidth of the input signal. Voice bandwidth is 4 kHz and clock rates from 8 k and up are possible. Thus the delta modulator digitizes and transmits the analog input to a remote receiver. The serial, unframed nature of the data is ideal for communications networks. With no input at the transmitter, a continuous one zero alternation is transmitted. If the two integrators are made leaky, then during any loss of contact the receiver output decays to

### **CIRCUIT DESCRIPTION (continued)**

zero and receive restart begins without framing when the receiver reacquires. Similarly a delta modulator is tolerant of sporadic bit errors. Figure 12 shows the delta modulator waveforms while Figure 13 shows the corresponding CVSD decoder block diagram.

### The Companding Algorithm

The fundamental advantages of the delta modulator are its simplicity and the serial format of its output. Its limitations are its ability to accurately convert the input within a limited digital bit rate. The analog input must be band limited and amplitude limited. The frequency limitations are governed by the nyquist rate while the amplitude capabilities are set by the gain of the integrator.

The frequency limits are bounded on the upper end; that is, for any input bandwidth there exists a clock frequency larger than that bandwidth which will transmit the signal with a specific noise level. However, the amplitude limits are bounded on both upper and lower ends. For a signal level, one specific gain will achieve an optimum noise level. Unfortunately, the basic delta modulator has a small dynamic range over which the noise level is constant.

The continuously variable slope circuitry provides increased dynamic range by adjusting the gain of the integrator. For a given clock frequency and input bandwidth the additional circuitry increases the delta modulator's dynamic range. External to the basic delta modulator is an algorithm which monitors the past few outputs of the delta modulator in a simple shift register. The register is 3 or 4 bits long depending on the application. The accepted CVSD algorithm simply monitors the contents of the shift register and indicates

if it contains all 1s or 0s. This condition is called coincidence. When it occurs, it indicates that the gain of the integrator is too small. The coincidence output charges a single pole low pass filter. The voltage output of this syllabic filter controls the integrator gain through a pulse amplitude modulator whose other input is the sign bit or up/down control.

The simplicity of the all ones, all zeros algorithm should not be taken lightly. Many other control algorithms using the shift register have been tried. The key to the accepted algorithm is that it provides a measure of the average power or level of the input signal. Other techniques provide more instantaneous information about the shape of the input curve. The purpose of the algorithm is to control the gain of the integrator and to increase the dynamic range. Thus a measure of the average input level is what is needed.

The algorithm is repeated in the receiver and thus the level data is recovered in the receiver. Because the algorithm only operates on the past serial data, it changes the nature of the bit stream without changing the channel bit rate.

The effect of the algorithm is to compand the input signal. If a CVSD encoder is played into a basic delta modulator, the output of the delta modulator will reflect the shape of the input signal but all of the output will be at an equal level. Thus the algorithm at the output is needed to restore the level variations. The bit stream in the channel is as if it were from a standard delta modulator-with a constant level input.

The delta modulator encoder with the CVSD algorithm provides an efficient method for digitizing a voice input in a manner which is especially convenient for digital communications requirements.

# APPLICATIONS INFORMATION CVSD DESIGN CONSIDERATIONS

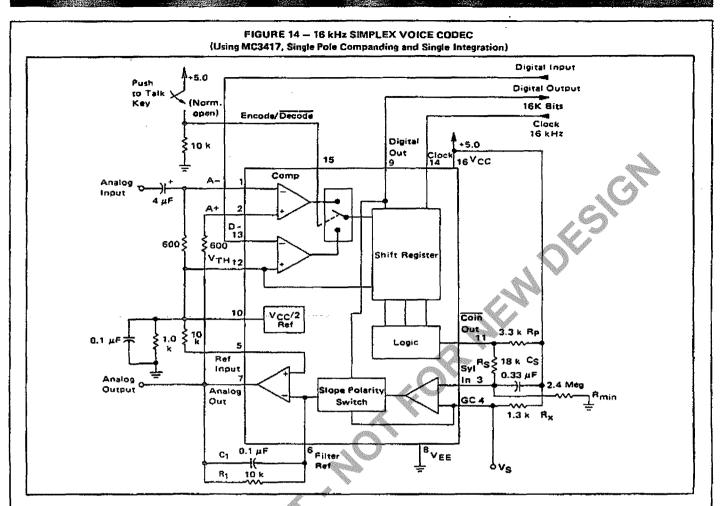

A simple CVSD encoder using the MC3417 or MC3418 is shown in Figure 14. These ICs are general purpose CVSD building blocks which allow the system designer to tailor the encoder's transmission characteristics to the application. Thus, the achievable transmission capabilities are constrained by the fundamental limitations of delta modulation and the design of encoder parameters. The performance is not dictated by the internal configuration of the MC3417 and MC3418. There are seven design considerations involved in designing these basic CVSD building blocks into a specific codec application, and they are as follows:

1. Selection of clock rate

- 2. Required number of shift register bits

- 3. Selection of loop gain

- 4. Selection of minimum step size

- 5. Design of integration filter transfer function

- 6. Design of syllabic filter transfer function

- 7. Design of low pass filter at the receiver

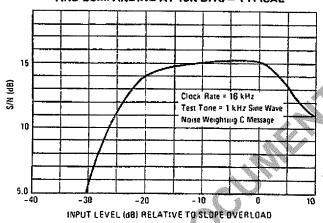

The circuit in Figure 14 is the most basic CVSD circuit possible. For many applications in secure radio or other intelligible voice channel requirements, it is entirely sufficient. In this circuit, items 5 and 6 are reduced to their simplest form. The syllabic and integration filters are both single pole networks. The selection of items 1 through 4 govern the codec performance.

### CVSD DESIGN CONSIDERATIONS (continued)

### **Layout Considerations**

Care should be exercised to isolate all digital signal paths (Pins 9, 11, 13, and 14) from analog signal paths (Pins 1–7 and 10) in order to achieve proper idle channel performance.

### **Clock Rate**

With minor modifications the circuit in Figure 14 may be operated anywhere from 9.6 kHz to 64 kHz clock rates. Obviously the higher the clock rate the higher the S/N performance. The circuit in Figure 14 typically produces the S/N performance shown in Figure 15. The selection of clock rate is usually dictated by the bandwidth of the transmission medium. Voice bandwidth systems will require no higher than 9600 Hz. Some radio systems will allow 12 kHz. Private 4-wire telephone systems are often operated at 16 kHz and commercial telephone performance can be achieved at 32K bits and above. Other codecs may use bit rates up to 200K bits/sec.

# FIGURE 15 — SIGNAL-TO-NOISE PERFORMANCE OF MC3417 WITH SINGLE INTEGRATION, SINGLE-POLE AND COMPANDING AT 16K BITS — TYPICAL

### Shift Register Length (Algorithm)

The MC3417 has a three-bit algorithm and the MC3418 has a four-bit algorithm. For clock rates of 16 kHz and below, the 3-bit algorithm is well suited. For 32 kHz and higher clock rates, the 4-bit system is preferred. Since the algorithm records a fixed past history of the input signal, a longer shift register is required to obtain the same internal history. At 16 bits and below, the 4-bit algorithm will produce a slightly wider dynamic range at the expense of level change response. Basically the MC3417 is designed for low bit rate systems and the MC3418 is intended for high performance, high bit rate system. At bit rates above 64K bits either part will work well.

### Selection of Loop Gain

The gain of the circuit in Figure 14 is set by resistor  $R_X$ .  $R_X$  must be selected to provide the proper integrator step size for high level signals such that the companding ratio does not exceed about 25%. The companding ratio is the active low duty cycle of the coincidence output on Pin 11 of the codec circuit. Thus the system gain is dependent on:

- The maximum level and frequency of the input signal.

- 2. The transfer function of the integration filter.

For voice codecs the typical input signal is taken to be a sine wave at 1 kHz of 0 dBmo level. In practice, the useful dynamic range extends about 6 dB above the design level. In any system the companding ratio should not exceed 30%.

To calculate the required step size current, we must describe the transfer characteristics of the integration filter. In the basic circuit of Figure 14, a single pole of 160 Hz is used.

R<sub>1</sub> = 10 kΩ, C<sub>1</sub> = 0.1 μF

$$\frac{V_0}{I_i} = \frac{1}{C(S + 1/RC)} \equiv \frac{K}{S + \omega_0}$$

$\omega_0 = 2\pi f$

$10^3 = \omega_0 = 2\pi f$

$f = 159.2 \text{ Hz}$

Note that the integration filter produces a single-pole response from 300 to 3 kHz. The current required to move the integrator output a specific voltage from zero is simply:

$$I_{j} = \frac{V_{Q}}{R_{1}} + \left(C_{1} \times \frac{dV_{Q}}{dt}\right)$$

Now a 0 dBmo sine wave has a peak value of 1.0954 volts. In 1/8 of a cycle of a sine wave centered around the zero crossing, the sine wave changes by approximately its peak value. The CVSD step should trace that change. The required current for a 0 dBm 1 kHz sine wave is:

$$I_i = \frac{1.1 \text{ V}}{*2(10 \text{ k}\Omega)} + \frac{0.1 \,\mu\text{F}\{1.1\}}{0.125 \text{ ms}} = 0.935 \text{ mA}$$

\*The maximum voltage across R<sub>1</sub> when maximum slew is required is:

Now the voltage range of the syllabic filter is the power supply voltage, thus:

$$R_X = 0.25(V_{CC}) \frac{1}{0.935 \text{ mA}}$$

A similar procedure can be followed to establish the proper gain for any input level and integration filter type.

### CVSD DESIGN CONSIDERATIONS (continued)

### Minimum Step Size

The final parameter to be selected for the simple codec in Figure 14 is idle channel step size. With no input signal, the digital output becomes a one-zero alternating pattern and the analog output becomes a small triangle wave. Mismatches of internal currents and offsets limit the minimum step size which will produce a perfect idle channel pattern. The MC3417 is tested to ensure that a 20 mVp-p minimum step size at 16 kHz will attain a proper idle channel. The idle channel step size must be twice the specified total loop offset if a one-zero idle pattern is desired. In some applications a much smaller minimum step size (e.g., 0.1 mV) can produce quiet performance without providing a 1-0 pattern.

To set the idle channel step size, the value of R<sub>min</sub> must be selected. With no input signal, the slope control algorithm is inactive. A long series of ones or zeros never occurs. Thus, the voltage across the syllabic filter capacitor (CS) would decay to zero. However, the voltage divider of RS and R<sub>min</sub> (see Figure 14) sets the minimum allowed voltage across the syllabic filter capacitor. That voltage must produce the desired ramps at the analog output. Again we write the filter input current equation:

$$I_i = \frac{V_0}{R_1} + C \frac{dV_Q}{dt}$$

For values of  $V_{\rm O}$  near  $V_{\rm CC}/2$  the  $V_{\rm O}/R$  term is negligible; thus

$$l_i = C_S \frac{\Delta V_o}{\Delta T}$$

where  $\Delta T$  is the clock period and  $\Delta V_O$  is the desired peak-to-peak value of the idle output. For a 16K-bit system using the circuit in Figure 14

$$I_i = \frac{0.1 \,\mu\text{F} \, 20 \,\text{mV}}{62.5 \,\mu\text{s}} = 33 \,\mu\text{A}$$

The voltage on  $C_S$  which produces a 33  $\mu A$  current is determined by the value of  $R_X$ .

$$I_iR_X = V_Smin$$

; for 33  $\mu$ A,  $V_Smin = 41.6 mV$

In Figure 14 Rg is 18 k $\Omega$ . That selection is discussed with the syllabic filter considerations. The voltage divider of Rg and Rmin must produce an output of 41.6 mV.

$$V_{CC} \frac{R_S}{R_S + R_{min}} = V_{Smin} \qquad R_{min} \approx 2.4 \text{ M}\Omega$$

Having established these four parameters — clock rate, number of shift register bits, loop gain and minimum step size — the encoder circuit in Figure 14 will function at near optimum performance for input levels around 0 dBm.

### **INCREASING CVSD PERFORMANCE**

### Integration Filter Design

The circuit in Figure 14 uses a single-pole integration network formed with a 0.1  $\mu$ F capacitor and a 10 k $\Omega$  resistor. It is possible to improve the performance of the circuit in Figure 14 by 1 or 2 dB by using a two-pole integration network. The improved circuit is shown.

The first pole is still placed below 300 Hz to provide the 1/S voice content curve and a second pole is placed somewhere above the 1 kHz frequency. For telephony circuits, the second pole can be placed above 1.8 kHz to exceed the 1633 touchtone frequency. In other communication systems, values as low as 1 kHz may be selected. In general, the lower in frequency the second pole is placed, the greater the noise improvement. Then, to ensure the encoder loop stability, a zero is added to keep the phase shift less than 180°. This zero should be placed slightly above the low-pass output filter break frequency so as not to reduce the effectiveness of the second pole. A network of 235 Hz, 2 kHz and 5.2 kHz is typical for telephone applications while 160 Hz, 1.2 kHz and 2.8 kHz might be used in voice only channels. (Voice only channels can use an output low-pass filter which breaks at about 2.5 kHz.) The two-pole network in Figure 16 has a transfer function of:

$$\frac{V_0}{I_i} = \frac{R_0R_1\left(S + \frac{1}{R_1C_1}\right)}{R_2C_2(R_0 + R_1)\left(S + \frac{1}{(R_0 + R_1)C_1}\right)S + \left(\frac{1}{R_2C_2}\right)}$$

### FIGURE 16 - IMPROVED FILTER CONFIGURATION

These component values are for the telephone channel circuit poles described in the text. The R2, C2 product can be provided with different values of R and C. R2 should be chosen to be equal to the termination resistor on Pin 1.

### INCREASING CVSD PERFORMANCE (continued)

Thus the two poles and the zero can be selected arbitrarily as long as the zero is at a higher frequency than the first pole. The values in Figure 16 represent one implementation of the telephony filter requirement.

The selection of the two-pole filter network effects the selection of the loop gain value and the minimum step size resistor. The required integrator current for a given change in voltage now becomes:

$$I_i = \frac{V_o}{R_0} + \left(\frac{R_2C_2}{R_0} + \frac{R_1C_1}{R_0} + C_1\right)\frac{\Delta V_o}{\Delta T} +$$

$$\left(R_2C_2C_1 + \frac{R_1C_1R_2C_2}{R_0}\right) \frac{\Delta V_0^2}{\Delta T^2}$$

.

The calculation of desired gain resistor R<sub>X</sub> then proceeds exactly as previously described.

### Syllabic Filter Design

The syllabic filter in Figure 14 is a simple single-pole network of 18 k $\Omega$  and 0.33  $\mu$ F. This produces a 6.0 ms time constant for the averaging of the coincidence output signal. The voltage across the capacitor determines the integrator current which in turn establishes the step size. The integrator current and the resulting step size determine the companding ratio and the S/N performance. The companding ratio is defined as the voltage across Cs/Vcc.

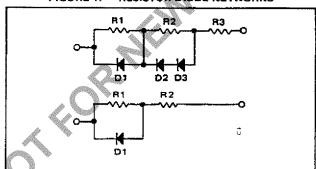

The S/N performance may be improved by modifying the voltage to current transformation produced by By. If different portions of the total Rx are shunted by diodes, the integrator current can be other than (VCC - VS)/Rx. These breakpoint curves must be designed experimentally for the particular system application. In general, one would wish that the current would double with input level. To design the desired curve, supply current to Pin 4 of the codec from an external source. Input a signal level and adjust the current until the S/N perfor-

mance is optimum. Then record the syllabic filter voltage and the current. Repeat this for all desired signal levels. Then derive the resistor diode network which produces that curve on a curve tracer.

Once the network is designed with the curve tracer, it is then inserted in place of Rx in the circuit and the forced optimum noise performance will be achieved from the active syllabic algorithm.

Diode breakpoint networks may be very simple or moderately complex and can improve the usable dynamic range of any codec. In the past they have been used in high performance telephone codecs.

Typical resistor-diode networks are shown in Figure 17.

FIGURE 17 - RESISTOR-DIODE NETWORKS

If the performance of more complex diode networks is desired, the circuit in Figure 18 should be used. It simulates the companding characteristics of nonlinear R<sub>X</sub> elements in a different manner.

### **Output Low Pass Filter**

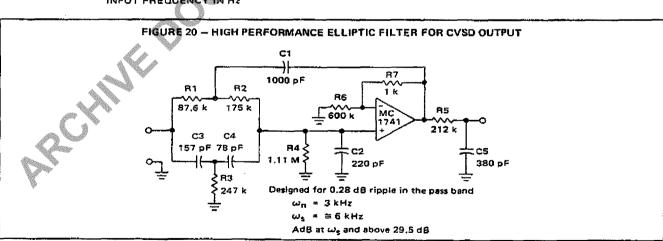

A low pass filter is required at the receiving circuit output to eliminate quantizing noise. In general, the lower the bit rate, the better the filter must be. The filter in Figure 20 provides excellent performance for 12 kHz to 40 kHz systems.

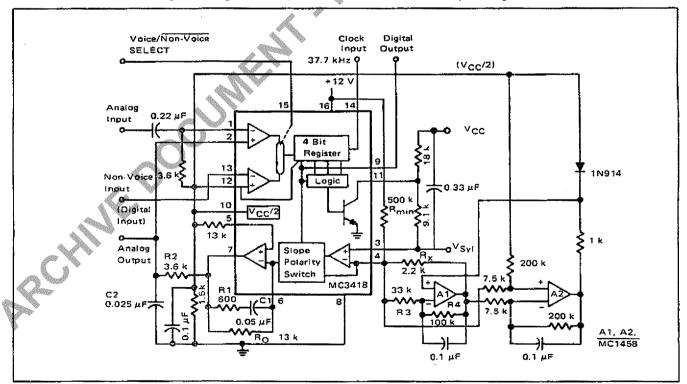

### TELEPHONE CARRIER QUALITY CODEC USING MC3418

Two specifications of the integrated circuit are specifically intended to meet the performance requirements of commercial telephone systems. First, slope polarity switch current matching is laser trimmed to guarantee proper idle channel performance with 5 mV minimum step size and a typical 1% current match from 15 µA to 3 mA. Thus a 300 to 1 range of step size variation is possible. Second, the MC3418 provides the four-bit algorithm currently used in subscriber loop telephone systems. With these specifications and the circuit of Figure 18, a telephone quality codec can be mass produced.

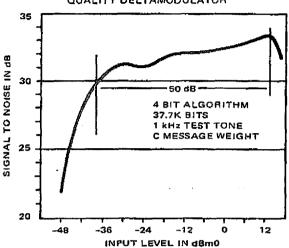

The circuit in Figure 18 provides a 30 dB S/Nc ratio over 50 dB of dynamic range for a 1 kHz test tone at a 37.7K bit rate. At 37.7K bits, 40 voice channels may be multiplexed on a standard 1.544 megabit T1 facility. This codec has also been tested for 10-7 error rates with asynchronous and synchronous data up to 2400 baud and for reliable performance with DTMF signaling. Thus, the design is applicable in telephone quality subscriber loop carrier systems, subscriber loop concentrators and small PABX installations.

### TELEPHONE CARRIER QUALITY CODEC USING MC3418 (continued)

### The Active Companding Network

The unique feature of the codec in Figure 18 is the step size control circuit which uses a companding ratio reference, the present step size, and the present syllabic filter output to establish the optimum companding ratios and step sizes for any given input level. The companding ratio of a CVSD codec is defined as the duty cycle of the coincidence output. It is the parameter measured by the syllabic filter and is the voltage across Cs divided by the voltage swing of the coincidence output. In Figure 18, the voltage swing of Pin 11 is 6.0 volts. The operating companding ratio is analoged by the voltage between Pins 10 and 4 by means of the virtual short across Pins 3 and 4 of the V to I op amp within the integrated circuit. Thus, the instantaneous companding ratio of the codec is always available at the negative input of A1.

The diode D1 and the gain of A1 and A2 provide a companding ratio reference for any input level. If the output of A2 is more than 0.7 volts below  $V_{CC}/2$ , then the positive input of A1 is  $(V_{CC}/2 - 0.7)$ . The on diode drop at the input of A1 represents a 12% companding ratio (12% = 0.7 V/6.0 V).

The present step size of the operating codec is directly related to the voltage across  $R_{\chi}$ , which established the

integrator current. In Figure 18, the voltage across  $R_X$  is amplified by the differential amplifier A2 whose output is single ended with respect to Pin 10 of the IC.

For large signal inputs, the step size is large and the output of A2 is lower than 0.7 volts. Thus D1 is fully on. The present step size is not a factor in the step size control. However, the difference between 12% companding ratio and the instantaneous companding ratio at Pin 4 is amplified by A1. The output of A1 changes the voltage across  $R_{\rm X}$  in a direction which reduces the difference between the companding reference and the operating ratio by changing the step size. The ratio of R4 and R3 determines how closely the voltage at Pin 4 will be forced to 12%. The selection of R3 and R4 is initially experimental. However, the resulting companding control is dependent on  $R_{\rm X}$ , R3, R4, and the full diode drop D1. These values are easy to reproduce from codec to codec.

For small input levels, the companding ratio reference becomes the output of A2 rather than the diode drop. The operating companding ratio on Pin 4 is then compared to a companding ratio smaller than 12% which is determined by the voltage drop across  $R_{\rm X}$  and the gain of A2 and A1. The gain of A2 is also experimentally determined, but once determined, the circuitry is easily

### FIGURE 18 - TELEPHONE QUALITY DELTAMOD CODER

(Both double integration and active companding control are used to obtain improved CVSD performance. Laser trimming of the integrated circuit provides reliable idle channel and step size range characteristics.)

### TELEPHONE CARRIER QUALITY CODEC USING MC3418 (continued)

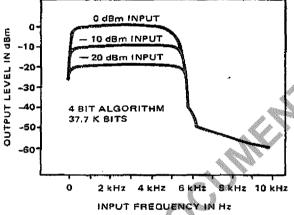

### FIGURE 19 – SIGNAL-TO-NOISE PERFORMANCE AND FREQUENCY RESPONSE

(Showing the improvement realized with the circuit in Figure 18.)

a. SIGNAL-TO-NOISE PERFORMANCE OF TELEPHONY QUALITY DELTAMODULATOR

b. FREQUENCY RESPONSE versus INPUT LEVEL (SLOPE OVERLOAD CHARACTERISTIC)

repeated.

With no input signal, the companding ratio at Pin 4 goes to zero and the voltage across  $R_{\rm X}$  goes to zero. The voltage at the output of A2 becomes zero since there is no drop across  $R_{\rm X}$ . With no signal input, the actively controlled step size vanished.

The minimum step size is established by the 500 k resistor between V<sub>CC</sub> and V<sub>CC</sub>/2 and is therefore independently selectable.

The signal to noise results of the active companding network are shown in Figure 19. A smooth 2 dB drop is realized from +12 dBm to -24 under the control of A1. At -24 dBm, A2 begins to degenerate the companding reference and the resulting step size is reduced so as to extend the dynamic range of the codec by 20 dBm.

The slope overload characteristic is also shown. The active companding network produces improved performance with frequency. The 0 dBm slope overload point is raised to 4.8 kHz because of the gain available in controlling the voltage across  $R_{\rm X}$ . The curves demonstrate that the level linearity has been maintained or improved.\*

The coded in Figure 18 is designed specifically for 37.7K bit systems. However, the benefits of the active companding network are not limited to high bit rate systems. By modifying the crossover region (changing the gain of A2), the active technique may be used to improve the performance of lower bit rate systems.

The performance and repeatability of the codec in Figure 18 represents a significant step forward in the art and cost of CVSD codec designs.

<sup>\*</sup>A larger value for C2 is required in the decoder circuit than in the encoder to adjust the level linearity with frequency. In Figure 18, 0.050  $\mu$ F would work well.

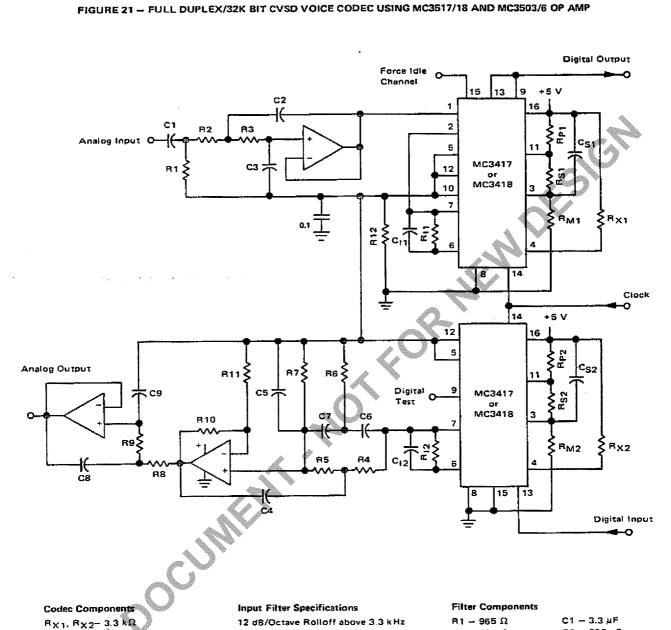

$R_{P1}$ ,  $R_{P2} = 3.3 \text{ k}\Omega$   $R_{P1}$ ,  $R_{P2} = 3.3 \text{ k}\Omega$   $R_{S1}$ ,  $R_{S2} = 100 \text{ k}\Omega$   $R_{11}$ ,  $R_{12} = 20 \text{ k}\Omega$   $R_{12} = 1 \text{ k}\Omega$   $R_{M1}$ ,  $R_{M2} = 5 \text{ M}\Omega$  (MC3417)

Minimum step size = 20 mV R<sub>M1</sub>, R<sub>M2</sub> - 15 MΩ (MC3418)

Minimum step síze = 6 mV

C<sub>S1</sub>, C<sub>S2</sub> - 0.05 μF C<sub>11</sub>, C<sub>12</sub> - 0.05 μF 2 MC3417 (or MC3418) 1 MC3403 (or MC3406)

Note: All Res. 5% All Cap. 5%

6 d8/Octave Rolloff below 50 Hz

# **Output Filter Specifications**

Break Frequency - 3.3 kHz Stop Band - 9 kHz Stop Band Atten. - 50 dB Rolloff - > 40 dB/Octave

R2 - 72 kΩ C2 - 837 pF R3 - 72 kΩ C3 - 536 pF R4 - 63.46 kΩ C4 - 1000 pF C5 - 222 pF R5 – 127 k $\Omega$ C6 - 77 pF R6 - 365.5  $k\Omega$ C7 - 38 pF  $87-1.645~\mathrm{M}\Omega$ R8 - 72 kΩ C8 - 837 pF  $R9 = 72 \ k\Omega$ C9 - 536 pf

R10 - 29.5 k $\Omega$  $\text{R11} = 72 \text{ k}\Omega$

Note: All Res. 0.1% to 1%. All Cap. 1.0%

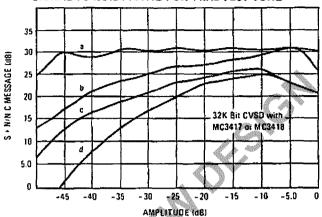

### COMPARATIVE CODEC PERFORMANCE

The salient feature of CVSD codecs using the MC3517 and MC3518 family is versatility. The range of codec complexity tradeoffs and bit rate is so wide that one cannot grasp the interdependency of parameters for voice applications in a few pages.

Design of a specific codec must be tailored to the digital channel bandwidth, the analog bandwidth, the quality of signal transmission required and the cost objectives. To illustrate the choices available, the data in Figure 22 compares the signal-to-noise ratios and dynamic range of various codec design options at 32K bits. Generally, the relative merits of each design feature will remain intact in any application. Lowering the bit rate will reduce the dynamic range and noise performance of all techniques. As the bit rate is increased, the overall performance of each technique will improve and the need for more complex designs diminishes.

Non-voice applications of the MC3517 and MC3518 are also possible. In those cases, the signal bandwidth and amplitude characteristics must be defined before the specification of codec parameters can begin. However, in general, the design can proceed along the lines of the voice applications shown here, taking into account the different signal bandwidth requirements.

### FIGURE 22 – COMPARATIVE CODEC PERFORMANCE – SIGNAL-TO-NOISE RATIO FOR 1 kHz TEST TONE

These curves demonstrate the improved performance obtained with several codec designs of varying complexity.

Curve a — Complex companding and double integration (Figure 18 — MC3418)

Curve b — Double integration (Figure 14 using Figure 16 — MC3418)

Curve c — Single integration (Figure 14 — MC3418) with 6.0 mV step size

Curve d Single integration (Figure 14 — MC3417) with 25 mV step size

# MC3417 MG3517 MG3418 MC3518

18.80

6.10

0.38

1.02 1.78

0.20

7.62 BSC

2.41

10°

В

6.60 0.240 0.260 4.69 0.145 0.185

0.53 0.015 0.021

0.38 0.008 0.015 3.43 0.115 0.135

0.040 | 0.070

0.015 0.095

0.300 BSC 0° 10°

- LEADS WITHIN 0.13 mm (0.005) RADIUS OF TRUE

POSITION AT SEATING PLANE AT MAXIMUM MATERIAL CONDITION.

- 2. DIMENSION "L" TO CENTER OF LEADS WHEN FORMED PARALLEL. 3. DIMENSION "B" DOES NOT INCLUDE MOLD

- FLASH. 4. "F" DIMENSION IS FOR FULL LEADS.

- 5. ROUNDED CORNERS OPTIONAL.

### DW SUFFIX PLASTIC PACKAGE CASE 751G-01

- DIMENSIONS A AND B ARE DATUMS AND T IS A DATUM SURFACE.

- 2. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M. 1982.

- 3. CONTROLLING DIMENSION: MILLIMETER.

- 4. DIMENSION A AND B DO NOT INCLUDE MOLD PROTRUSION.

- 5. MAXIMUM MOLD PROTRUSION 0.15 (0.006) PER SIDE

| DIM | MIN   | _MAX  | MIN       | MAX   |  |

|-----|-------|-------|-----------|-------|--|

|     | 10.15 | 10.45 | 0.400     | 0.411 |  |

| 8   | 7.40  | 7.60  | 0.292     | 1,299 |  |

| ပ   | 2.35  | 2.65  | 0.093     | 0.104 |  |

| ۵   | 0.35  | 0.49  | 0.014     | 0.019 |  |

| F   | 0.50  | 0.90  | 0.020     | 0.035 |  |

| G   | 1,27  | 8SC   | 0.050 BSC |       |  |

| 7   | 0.25  | 0.32  | 0.010     | 0.012 |  |

| K   | 0,10  | 0.25  | 0.004     | 0.009 |  |

| M   | O°    | 7°    | 0.        |       |  |

| P   | 10.05 | 10.55 | 0.395     | 0.415 |  |

|     | 0.25  | 0.75  | 0.010     | 0.029 |  |

MILLIMETERS

1. DIMENSIONING AND TOLERANCING PER ANSI

- Y14.5M, 1982. 2. CONTROLLING DIMENSION: INCH.

3. DIMENSION L TO CENTER OF LEAD WHEN

- FORMED PARALLEL. 4. DIM F MAY NARROW TO 0.76 (0.030) WHERE THE LEAD ENTERS THE CERAMIC BODY.

| DIM . | MEN      | _MAX  | MIN       | MAX   |

|-------|----------|-------|-----------|-------|

| A     | 19.05    | 19.93 | 0.750     | 0.785 |

| B     | 6.10     | 7.49  | 0.240     | 0.295 |

| Ċ     |          | 5,08  | -         | 0.200 |

| D     | 0.39     | 0.50  | 0.015     | 0,020 |

| E     | 1,27     | BSC   | 0.050 BSC |       |

| F     | 1.40     | 1.65_ | 0,055     | 0.065 |

| G     | 2.54 BSC |       | 0,100 BSC |       |

| J     | 0.21     | 0,38  | 0.008     | 0.015 |

| K     | 3.18     | 4.31  | 0.125     | 0,170 |

| L     | 7.62 BSC |       | 0.300 BSC |       |

| M     | O.       | 15°   | 0°        | 15°   |

| N     | 0.51     | 1.01  | 0.020     | 0.040 |

INCHES

MILLIMETERS

~~~~

change of the control Motorola reserves the right to make changes without further notice to any products herein. Motorola makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Motorola assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters can and do vary in different and specifically diselaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters can and do vary in different applications. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Motorola does not convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part. Motorola and (A) are registered trademarks of Motorola, Inc. Motorola, Inc. is an Equal Opportunity/Affirmative Action Employer.

### Literature Distribution Centers:

USA: Motorola Literature Distribution; P.O. Box 20912; Phoenix, Arizona 85036.

EUROPE: Motorola Ltd.; European Literature Centre; 88 Tanners Drive, Blakelands, Milton Keynes, MK14 5BP, England.

JAPAN: Nippon Motorola Ltd.; 4-32-1, Nishi-Gotanda, Shinagawa-ku, Tokyo 141, Japan.

ASIA PACIFIC: Motorola Semiconductors H.K. Ltd.; Silicon Harbour Center, No. 2 Dai King Street, Tai Po Industrial Estate, Tai Po, N.T., Hong Kong.

MOTOROLA

10771-4 PRINTED IN USA (1894) MPS/POD

MC3417/D A ANNONE THE CONTRACT OF STREET STREET, STREET STREET