**DESCRIPTION** — The '153 is a high speed dual 4-input multiplexer with common select inputs and individual enable inputs for each section. It can select two lines of data from four sources. The two buffered outputs present data in the true (non-inverted) form. In addition to multiplexer operation, the '153 can generate any two functions of three variables.

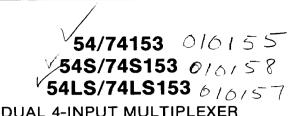

**ORDERING CODE:** See Section 9

|                    | PIN | COMMERCIAL GRADE                                                                            | MILITARY GRADE                                                                                  | PKG  |  |

|--------------------|-----|---------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|------|--|

| PKGS               | оит | $V_{CC} = +5.0 \text{ V} \pm 5\%,$<br>$T_A = 0^{\circ} \text{ C to } +70^{\circ} \text{ C}$ | $V_{CC} = +5.0 \text{ V} \pm 10\%,$<br>$T_A = -55^{\circ} \text{ C to} + 125^{\circ} \text{ C}$ | TYPE |  |

| Plastic<br>DIP (P) | А   | 74153PC, 74S153PC<br>74LS153PC                                                              |                                                                                                 | 9B   |  |

| Ceramic<br>DIP (D) | Α   | 74153DC, 74S153DC<br>74LS153DC                                                              | 54153DM, 54S153DM<br>53LS153DM                                                                  | 6B   |  |

| Flatpak<br>(F)     | А   | 74153FC, 74S153FC<br>74LS153FC                                                              | 54153FM, 54S153FM<br>54LS153FM                                                                  | 4L   |  |

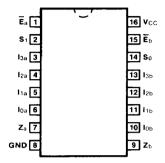

## CONNECTION DIAGRAM PINOUT A

## INPUT LOADING/FAN-OUT: See Section 3 for U.L. definitions

| PIN NAMES                                          | DESCRIPTION                                                                                                                                | <b>54/74 (U.L.)</b><br>HIGH/LOW                              | <b>54/74S (U.L.)</b><br>HIGH/LOW                                         | 54/74LS (U.L.)<br>HIGH/LOW                                                  |  |

|----------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|--------------------------------------------------------------------------|-----------------------------------------------------------------------------|--|

| loa — 13a<br>lob — 13b<br>So, S1<br>Ea<br>Eb<br>Za | Side A Data Inputs Side B Data Inputs Common Select Inputs Side A Enable Input (Active LOW) Side B Enable Input (Active LOW) Side A Output | 1.0/1.0<br>1.0/1.0<br>1.0/1.0<br>1.0/1.0<br>1.0/1.0<br>20/10 | 1.25/1.25<br>1.25/1.25<br>1.25/1.25<br>1.25/1.25<br>1.25/1.25<br>25/12.5 | 0.5/0.25<br>0.5/0.25<br>0.5/0.25<br>0.5/0.25<br>0.5/0.25<br>10/5.0<br>(2.5) |  |

| Z <sub>b</sub>                                     | Side B Output                                                                                                                              | 20/10                                                        | 20/12.5                                                                  | (2.5)                                                                       |  |

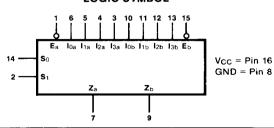

## LOGIC SYMBOL

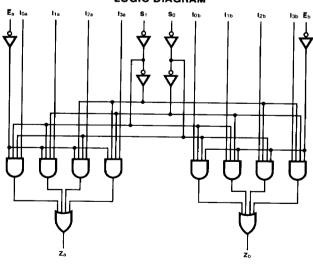

**FUNCTIONAL DESCRIPTION** — The '153 is a dual 4-input multiplexer. It can select two bits of data from up to four sources under the control of the common Select inputs  $(S_0, S_1)$ . The two 4-input multiplexer circuits have individual active LOW Enables  $(\overline{E}_a, \overline{E}_b)$  which can be used to strobe the outputs independently. When the Enables  $(\overline{E}_a, \overline{E}_b)$  are HIGH, the corresponding outputs  $(Z_a, Z_b)$  are forced LOW. The '153 is the logic implementation of a 2-pole, 4-position switch, where the position of the switch is determined by the logic levels supplied to the two Select inputs. The logic equations for the outputs are shown below.

$$\begin{split} Z_a &= \overline{E}_a \bullet (I_{0a} \bullet \overline{S}_1 \bullet \overline{S}_0 + I_{1a} \bullet \overline{S}_1 \bullet S_0 + I_{2a} \bullet S_1 \bullet \overline{S}_0 + I_{3a} \bullet S_1 \bullet S_0) \\ Z_b &= \overline{E}_b \bullet (I_{0b} \bullet \overline{S}_1 \bullet \overline{S}_0 + I_{1b} \bullet \overline{S}_1 \bullet S_0 + I_{2b} \bullet S_1 \bullet \overline{S}_0 + I_{3b} \bullet S_1 \bullet S_0) \end{split}$$

The '153 can be used to move data from a group of registers to a common output bus. The particular register from which the data came would be determined by the state of the Select inputs. A less obvious application is a function generator. The '153 can generate two functions of three variables. This is useful for implementing highly irregular random logic.

TRUTH TABLE

| SELECT<br>INPUTS |                |     | INP | OUTPUT |    |    |   |  |

|------------------|----------------|-----|-----|--------|----|----|---|--|

| S <sub>0</sub>   | S <sub>1</sub> | E   | lo  | 11     | 12 | lз | Z |  |

| х                | X              | I   | Х   | Х      | X  | Х  | L |  |

| L                | L              | L,  | L   | Х      | Х  | Х  | L |  |

| L                | L              | L   | н   | Х      | Х  | Х  | н |  |

| Н                | L              | ᅵᅵ  | Х   | L      | Х  | Х  | Ĺ |  |

| Н                | L              | L   | Х   | Н      | х  | х  | н |  |

| L                | Н              | L   | Х   | Х      | L  | Х  | L |  |

| L                | Н              | L   | Х   | Х      | Н  | Х  | н |  |

| H                | Н              | ᅵᅵᅵ | X   | Х      | Х  | L. | L |  |

| H                | Н              | L   | Х   | Х      | X  | н  | н |  |

H = HIGH Voltage Level

L = LOW Voltage Level

X = Immaterial

## LOGIC DIAGRAM

| SYMBOL | PARAMETER                       |     |            | 54/74      |            | 54/74S       |            | 74LS         | UNITS | CONDITIONS            |

|--------|---------------------------------|-----|------------|------------|------------|--------------|------------|--------------|-------|-----------------------|

|        |                                 | Min | Max        | Min        | Max        | Min          | Max        |              |       |                       |

| los    | Output Short Circuit<br>Current | XM  | -20<br>-18 | -55<br>-57 | -40<br>-40 | -100<br>-100 | -20<br>-20 | -100<br>-100 | mA    | V <sub>CC</sub> = Max |

| lcc    | Power Supply Current            | XM  |            | 52<br>60   |            | 70<br>70     |            | 10<br>10     | mA    | V <sub>CC</sub> = Max |

AC CHARACTERISTICS: V<sub>CC</sub> = +5.0 V, T<sub>A</sub> = +25° C (See Section 3 for waveforms and load configuration)

|              |                                                       | 54/74    | 54/74S                                           | 54/74LS  | UNITS |                 |

|--------------|-------------------------------------------------------|----------|--------------------------------------------------|----------|-------|-----------------|

| SYMBOL       | PARAMETER                                             |          | C <sub>L</sub> = 15 pF<br>R <sub>L</sub> = 280 Ω |          |       | CONDITIONS      |

|              |                                                       | Min Max  | Min Max                                          | Min Max  |       |                 |

| tplH<br>tpHL | Propagation Delay $S_n$ to $Z_n$                      | 34<br>34 | 18<br>18                                         | 29<br>29 | ns    | Figs. 3-1, 3-20 |

| tpLH<br>tpHL | Propagation Delay<br>E <sub>n</sub> to Z <sub>n</sub> | 30<br>23 | 15<br>13.5                                       | 29<br>32 | ns    | Figs. 3-1, 3-4  |

| tpLH<br>tpHL | Propagation Delay<br>In to Zn                         | 18<br>23 | 9.0<br>9.0                                       | 15<br>20 | ns    | Figs. 3-1, 3-5  |