## 20-OUTPUT CLOCK DRIVER / INVERTER

SC3502

### **GENERAL DESCRIPTION**

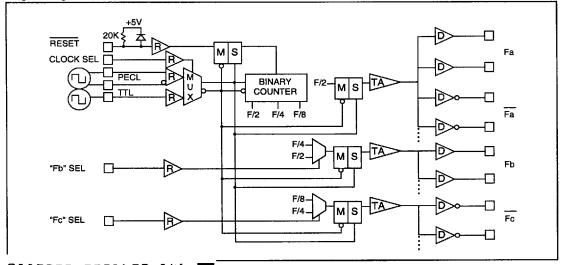

The SC3502 is a precision clock fan-out driver. It requires a 2X frequency clock input from a single ended TTL or an ECL differential source operating between +5V and ground (PECL). This 2X reference frequency input is received and distributed to symmetrical, divide-by-two master-slave flip-flops. The resultant output is distributed to the clock output drivers.

The 20-clock outputs are divided into four groups. The first group of five (5) outputs are unconditionally at the primary frequency, "Fa" =F input/2. The second group of five (5) outputs, "Fa", are set at the same frequency, but are inverted. The third group of five (5) outputs, "Fb", can be selected to be either identical to "Fa" or at 1/2 the frequency of "Fa". The fourth group of five (5) outputs, "Fc", are inverted and can be selected to be at either 1/2 or 1/4 of "Fa".

Applied Micro Circuits Corporation (AMCC) uses proprietary complementary (source and sink) 24 mA peak output drivers. In addition to their drive capability, these circuits provide "source (series) termination" at the TTL outputs that minimize overshoot and undershoot without requiring on-board termination networks. They are designed for a maximum output slew rate of =1.5V/ns to minimize simultaneous output switching noise and distortion.

### **FEATURES**

- Twenty (20) clock outputs:

- Five (5) outputs at primary frequency, up to 80 MHz

- Five (5) inverted outputs at the primary frequency, up to 80 MHz

- Five (5) outputs at primary or 1/2 primary frequency

- Five (5) inverted outputs at either 1/2 or 1/4 primary frequency

- Leading edge skew for all outputs ≤1.0 ns

- · Proprietary output drivers with:

- Complementary 24 mA peak outputs, source and sink

- 50-75Ω source series termination

- Dynamic drive adjustment to match load conditions

- Edge rates less than 1.5 ns

- Eliminates the ground-bounce, overshoot, and ringing problems often encountered when using CMOS and Bipolar drivers

0889002 0001672 146 🔳

Applied Micro Circuits Corporation 6195 Lusk Blvd., San Diego, CA 92121 • (619) 450-9333

# 20-OUTPUT CLOCK DRIVER/INVERTER

### **Absolute Maximum Ratings**

| Storage Temperature                 | 55° to +150°C            |

|-------------------------------------|--------------------------|

| V <sub>CC</sub> Potential to Ground | 0.5V to +7.0V            |

| Input Voltage                       | 0.5V to +V <sub>CC</sub> |

| Static Discharge Voltage            | >1750V                   |

| Maximum Junction Temperature        | +140°C                   |

| Latch-up Current                    | >200 mA                  |

| Operating Ambient Temperature       | 0° to +70°C              |

## Capacitance (package)

| Input Pins      | . 5.0 pF |

|-----------------|----------|

| TTL Output Pins | .5.0 pF  |

### **Electrical Characteristics**

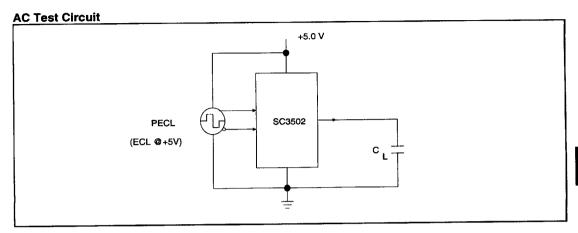

$V_{CC}$  = +5.0V  $\pm$  5%,  $T_a$  = 0°C to + 70°C (reference AC Test Circuit, Page 3-21)

|                    |                               | 1                                                  |                      |                      |      |

|--------------------|-------------------------------|----------------------------------------------------|----------------------|----------------------|------|

| Symbol             | Parameter                     | Conditions                                         | Min                  | Max                  | Unit |

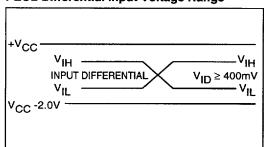

| V <sub>IH</sub>    | Input HIGH Voltage (PECL)     | Differential Source-PECL                           | V <sub>IL</sub> +0.4 | +V <sub>CC</sub>     | ٧    |

|                    | Input HIGH Voltage (TTL)      | All TTL Inputs including Clock                     | 2.0                  | Vcc                  | ٧    |

| VıL                | Input LOW Voltage (PECL)      | Differential Source-PECL                           | V <sub>CC</sub> -2.0 | V <sub>IH</sub> -0.4 | ٧    |

|                    | Input LOW Voltage (TTL)       | All TTL Inputs including Clock                     | -0.5                 | 0.8                  | ٧    |

| ItH                | Input HIGH Current (PECL)     | V <sub>IN</sub> = V <sub>CC</sub> (max)            |                      | 200                  | uA   |

|                    | CLKSEL                        | V <sub>IN</sub> = V <sub>CC</sub> (max)            |                      | 350                  | uA   |

|                    | Reset                         | V <sub>IN</sub> = 2.4V                             |                      | -250                 | uA   |

|                    | TTL, CSEL, BSEL               | V <sub>IN</sub> = 2.4V                             |                      | 15                   | uA   |

| lլլ                | Input LOW Current (PECL)      | V <sub>IN</sub> = V <sub>CC</sub> -2.0V            |                      | 15                   | uA   |

|                    | CLKSEL                        | V <sub>IN</sub> = 0.4V                             |                      | 50                   | uA   |

|                    | Reset                         | $V_{IN} = 0.5V$                                    |                      | -375                 | uA   |

|                    | TTL, CSEL, BSEL               | $V_{IN} = 0.4V$                                    |                      | 15                   | uA   |

| V <sub>OH</sub>    | Output HIGH Voltage           | F <sub>OUT</sub> = 80MHz max C <sub>L</sub> = 10pF | 2.4                  |                      | V    |

| V <sub>OL</sub>    | Output LOW Voltage            | F <sub>OUT</sub> = 80MHz max C <sub>L</sub> = 10pF |                      | 0.6                  | V    |

| lons1              | Output HIGH Short Ckt Current | Output High, V <sub>OUT</sub> = 0V Typ             | -55                  |                      | mA   |

| I <sub>OLS</sub> 1 | Output LOW Short Ckt Current  | Output Low, V <sub>OUT</sub> = V <sub>CC</sub> Typ | 55                   |                      | mA   |

| PWR                | Static Power Dissipation      | Reference Page 3-19 @ 70°C                         |                      | 400                  | mW   |

|                    |                               |                                                    |                      |                      |      |

<sup>1.</sup> Maximum test duration, one second.

The SC3502 features source series termination of approximately 40 Ohms to assist in matching 50–75 Ohm P.C. board environments.

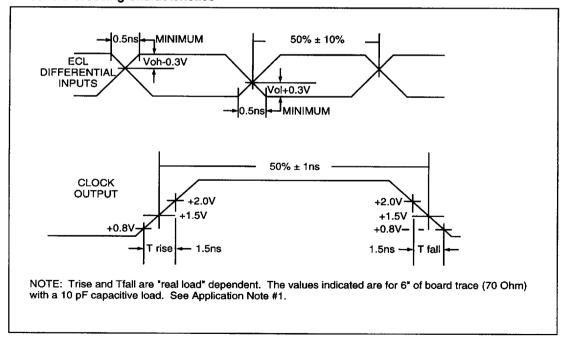

### **PECL Differential Input Voltage Range**

### **DC Characteristics**

The SC3502 has been designed specifically for clock distribution. In the development of this product, AMCC has made several trade-offs between the historic "high drive, totem pole outputs" and AMCC's dynamically adjusting source series terminated outputs. As a result of this, the SC3502 will dynamically source and sink a symmetrical 24 mA of current. In a DC state, it exhibits the following specifications:

|                 | Conditions             | Min  | Max  |

|-----------------|------------------------|------|------|

| V <sub>OH</sub> | I <sub>OH</sub> = -8mA | 2.4V |      |

| V <sub>OL</sub> | I <sub>OL</sub> = 4mA  |      | 0.6V |

0889002 0001673 082 **m**

Applied Micro Circuits Corporation 6195 Lusk Blvd., San Diego, CA 92121 • (619) 450-9333

## 20-OUTPUT CLOCK DRIVER / INVERTER

# AC Specifications - Using AC Test Circuit (Page 3-21)

$Vcc = +5.0V \pm 5\%$ ,  $Ta = 0^{\circ}C$  to  $+70^{\circ}C$ ,  $C_{LOAD} = 10pF$

| Parameter                                 | SC3502-1 | SC3502 | UNITS |

|-------------------------------------------|----------|--------|-------|

| Maximum Skew Across All Outputs           | 1.0      | 1.5    | ns    |

| Maximum Skew Chip To Chip                 | 2.0      |        | ns    |

| Maximum Skew Across Fa Outputs            | 0.25     | 0.25   | ns    |

| Maximum Skew Across Fa Outputs            | 0.25     | 0.25   | ns    |

| Maximum Skew Across Fb Outputs            | 0.25     | 0.25   | ns    |

| Maximum Skew Across Fc Outputs            | 0.25     | 0.25   | ns    |

| Maximum Output Duty Cycle Asymmetry       | ±1.0     | ±1.0   | ns    |

| Maximum TTL Input Frequency               | 80       | 80     | MHz   |

| Maximum PECL Differential Input Frequency | 160      | 160    | MHz   |

| Maximum Rising/Falling Edge Rates         | 1.5      | 1.5    | ns    |

#### Notes:

- Skew is referenced to the rising edges of all non-inverted copies and the falling edge of all

inverted copies

- Chip to chip skew specification valid only for parts operating at the same voltage and temperature. It is derated at 0.5 ns/V and 10 ps/°C. Chip to chip skew tested at 70°C.

- Output Duty Cycle Asymmetry is defined as the Duty Cycle deviation from 50%, measured at 1.5V. Duty Cycle will be affected by voltage, temperature, and load (including the length of the PC trace).

- Typical skew derating factor for different loads is 50ps/pF at 1.5V threshold. For example, a 5pF load difference equals a 250 ps skew difference.

- Edge rates are measured from 0.8V to 2.0V. Load consists of a 6" board trace (70 Ohm)

with a 10 pF capacitive load. See "Real Load" evaluation circuit. Synchronous outputs may

be paralleled for higher loads.

## 20-OUTPUT CLOCK DRIVER / INVERTER

# **DESCRIPTION OF OPERATION** (Refer to Logic Diagram)

AMCC has developed a twenty-output fan-out device using AMCC's advanced BiCMOS process. This design has optimized the device for clock symmetry and absolute minimum skew across all twenty outputs. Three harmonic clock frequency groups are provided that are user selectable.

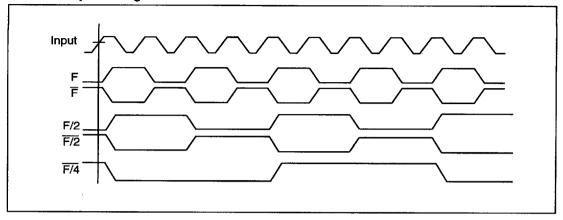

For highest performance this approach requires a 2X clock source input from a crystal controlled oscillator (XCO) located adjacent to this clock driver. This oscillator can provide either differential ECL inputs (referenced to +5V - PECL) to AMCC's Clock Driver or TTL (CMOS) levels. The input selection is accomplished via the "Clock Sel" input where a "HIGH" level activates the differential ECL input and a "LOW" activates the TTL input. This 2X input clock will be fanned out to a divide down counter and to master-slave flip-flops for synchronization, refer to the logic diagram preceding. Using this methodology the output duty cycle asymmetry becomes largely a function of output driver slew rate into the AC load.

Two user select pins, "B select" and "C select", provide the "Fb" and "Fc" output (sub-harmonic) frequencies by way of multiplexor selection into the final resynchronizing flip-flops. The divide down counter outputs are 50% duty cycle decoded. The output resynchronizing flip-flops are keyed for leading edge alignment. These outputs are amplified to fan out to AMCC's complementary source terminated TTL output drivers.

The RESET input is provided to hold off or clear the outputs as may be required by the user's system. This pin may be logically driven from a TTL output. Optionally, if a capacitor (4.7uF = ~100 ms) is connected between this pin and ground, the device will respond with a "power up reset" - a delay in the clock outputs becom-

ing active. On the first falling edge clock input after RESET goes low, the outputs will go low in sequence (the output divide count continues, but once an output goes low, it is held low). When RESET is released (high), the outputs will resume counting, after five falling edge clock input delays, from their low state (see "Relative Output Timing", Page 3-20 and "Reset To Output Timing", in Clock Driver Application Note #1).

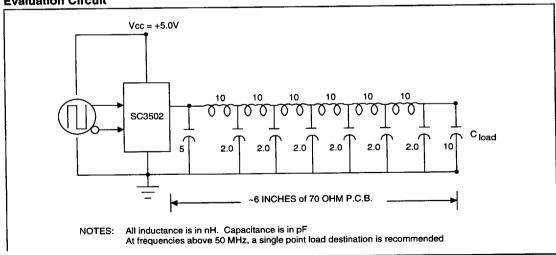

The output drivers are rise and fall slew rate controlled to ~1.5V/ns to minimize noise and distortion resulting from simultaneous switching of the 20 outputs. These outputs also feature series termination (~40 Ohms) to significantly reduce the overshoot and undershoot of non-terminated transmission lines. This will satisfy printed circuit line impedances of 50–75 Ohms terminated into 15 pF (two IC input package receiver pins). When applications require large load capacitance (>25pF with 50 ohm P.C. board impedance) and/or large peak voltage amplitudes (>3.5 Volts), two adjacent drivers may be paralleled, thereby halving the series resistance and doubling the peak current.

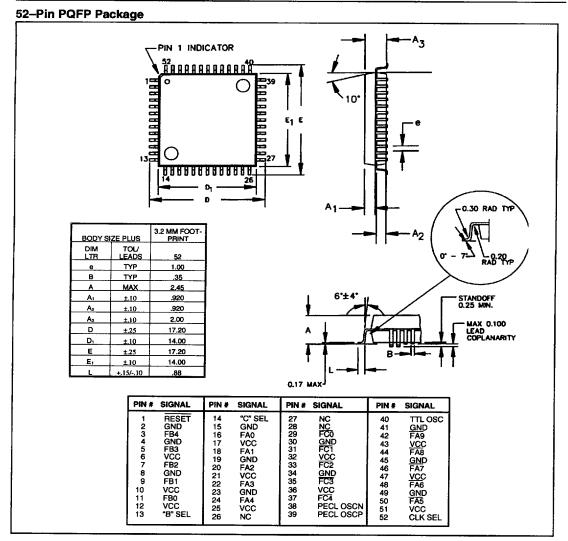

Power and ground are interdigitated with the outputs. Of the 52 package pins, 22 are used for low impedance on-chip power distribution. Due to the simultaneous switching of outputs, low impedance  $+V_{CC}$  and ground planes within the P.C. board are recommended, as well as substantial decoupling capacitance (see Clock Driver Application Note #1 for recommendations).

The IC package and die layouts are tightly coupled to assure precise matching of all of the outputs. Collectively, the resistance, inductance and capacitance of the package and wire bonding is managed to insure that the SC3502 will exhibit skews less than the specified maximum. A plastic 52 lead quad flat pack with .039" lead pitch is employed with an outer lead square footprint of approximately 0.7" per side.

0889002 0001675 955

Applied Micro Circuits Corporation 6195 Lusk Blvd., San Diego, CA 92121 • (619) 450-9333

## 20-OUTPUT CLOCK DRIVER/INVERTER

### **Output Clock Frequency Selection**

| "B" SEL | "C" SEL | XCO FREQ | Fa  | Fa  | Fb  | Fc  |

|---------|---------|----------|-----|-----|-----|-----|

| LO      | LO      | F        | F/2 | F/2 | F/4 | F/8 |

| HI      | LO      | F        | F/2 | F/2 | F/2 | F/8 |

| LO      | HI      | F        | F/2 | F/2 | F/4 | F/4 |

| HI      | н       | F        | F/2 | F/2 | F/2 | F/4 |

Note: XCO is the input frequency for either the PECL Inputs or the TTL Input. Non-crystal oscillator sources may be used at the user's discretion. See Application Note #1.

## **Power Management**

The overall goal of managing the power dissipated by the SC3502 is to limit it's junction (die) temperature to 140°C. A major component of the power dissipated internally by the SC3502 is determined by the load that each output drives and the frequency that each output is running. The following table summarizes these dependencies (see Evaluation Circuit on Page 3-21 for complete load definition).

| FREQUENCY | C <sub>LOAD</sub> =5pF | C <sub>LOAD</sub> =10pF | C <sub>LOAD</sub> =15pF | C <sub>LOAD</sub> =25pF | C <sub>LOAD</sub> =40pF | NO LOAD |

|-----------|------------------------|-------------------------|-------------------------|-------------------------|-------------------------|---------|

| 80 MHz    | 42 mW                  | 51 mW                   | 61 mW                   | 88 mW                   | 132 mW                  | 18 mW   |

| 66 MHz    | 38 mW                  | 47 mW                   | 55 mW                   | 75mW                    | 110 mW                  | 16 mW   |

| 50 MHz    | 28 mW                  | 33 mW                   | 39 mW                   | 60 mW                   | 85 mW                   | 14 mW   |

| 40 MHz    | 25 mW                  | 30 mW                   | 36 mW                   | 52 mW                   | 70 mW                   | 13 mW   |

| 33 MHz    | 19 mW                  | 22 mW                   | 24 mW                   | 46 mW                   | 60 mW                   | 12 mW   |

| 25 MHz    | 16 mW                  | 18 mW                   | 20 mW                   | 32 mW                   | 52 mW                   | 11 mW   |

| 20 MHz    | 14 mW                  | 16 mW                   | 18 mW                   | 24 mW                   | 44 mW                   | 10 mW   |

The above output power must then be added to the core power (400 mW) of the SC3502 to determine the total power being dissipated by the SC3502. This total power is then multiplied by the SC3502's thermal resistance, with the result being added to the ambient temperature to determine the junction temperature of the SC3502. For greatest reliability, this junction temperature should not exceed 140°C.

|                    | STILL AIR | 100 LIN FT/MIN | 200 LIN FT/MIN |

|--------------------|-----------|----------------|----------------|

| THERMAL RESISTANCE | 50°C/WATT | 40°C/WATT      | 35°C/WATT      |

For example: You have a SC3502 with 4 of the Fa and 4 of the Fa outputs running at 66 MHz with 10 pF loads  $(8 \times 47 = 376 \text{ mW} + 2 \times 16 = 32 \text{ mW})$  for an Fa and Fa Total of 408 mW), 3 of the Fb outputs are running at 33 MHz with 5 pF loads  $(3 \times 19 = 57 \text{ mW} + 2 \times 12 = 24 \text{ mW})$  for an Fb Total of 81 mW), and 2 Fc outputs running at 33 MHz with 15 pF loads  $(2 \times 24 = 48 \text{ mW} + 3 \times 12 = 36 \text{ mW})$  for an Fc Total of 84 mW). The Total Chip Power is Core Power (400 mW) + Fa and Fa Power (408 mW) + Fb Power (81 mW) + Fc Power (84 mW) = 973 mW. Your design calls for a 70°C Still Air ambient. The SC3502's junction temperature would then be: 70°C + (.973 Watts  $\times 50^{\circ}$ C/Watt = 49°C) = 119°C, below the 140°C maximum.

0889002 0001676 891 📟

Applied Micro Circuits Corporation 6195 Lusk Blvd., San Diego, CA 92121 • (619) 450-9333

## **Relative Output Timing**

### **Symmetry**

The outputs of the SC3502 are nominally centered to provide a clean 50% duty cycle, symmetrical waveform at the +1.5V threshold reference. (See Threshold Crossing Characteristics diagram below, for the conditions.)

### **Threshold Crossing Characteristics**

| 0889002 0001677 728 🖿

Applied Micro Circuits Corporation 6195 Lusk Blvd., San Diego, CA 92121 • (619) 450-9333

# Designing the SC3502 for "Real Loads"

While the AC Test Circuit presented above be adequate for initial device evaluation and incoming inspection, it does not represent "real loads" in products.

AMCC has designed the SC3502 to provide clean clock transitions when presented with a realistic reactive load. AMCC's assumptions are that the SC3502 will be driving a selected length(s) of 70 Ohm (Zo) P.C. board trace terminated by a small number of end of line clustered TTL or CMOS input receiver pins. This end of line

capacitive loading will cause overall impedance to drop to under 50 Ohms. Therefore, to a first approximation, this clock output driver will cleanly drive P.C. line lengths of 6" to 12" with input capacitive loads ranging up to 15 pF at frequencies up to 80 MHz.

Within this general circuit model, AMCC has developed the Evaluation Circuit presented below. This is a midpoint model and can be modified to reflect a specific end use. More details concerning this are presented in the Application Note #1.

### **Evaluation Circuit**

0889002 0001678 664 🖿

Applied Micro Circuits Corporation 6195 Lusk Blvd., San Diego, CA 92121 • (619) 450-9333

# 20-OUTPUT CLOCK DRIVER / INVERTER

# **Ordering Codes**

| Package Type                   | Max Skew Across All Outputs | Part Number |

|--------------------------------|-----------------------------|-------------|

| 52 Lead Plastic Quad Flat Pack | 1.0 ns                      | SC3502Q-1   |

| 52 Lead Plastic Quad Flat Pack | 1.5 ns                      | SC3502Q     |

Applied Micro Circuits Corporation 6195 Lusk Blvd., San Diego, CA 92121 • (619) 450-9333