TEL:805-498-2111 FAX:805-498-3804 WEB:http://www.semtech.com

#### DESCRIPTION

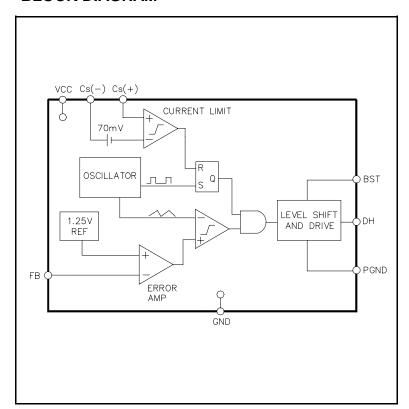

The SC1101 is a versatile, low-cost, voltage-mode PWM controller designed for use in single ended DC/DC power supply applications. A simple, fixed-voltage buck regulator can be implemented using the SC1101 with a minimum of external components. Internal level shift and drive circuitry eliminates the need for an expensive p-channel, high-side switch. The small device footprint allows for compact circuit design.

SC1101 features include a temperature compensated voltage reference, triangle wave oscillator, current limit comparator, frequency shift over-current protection, and an internally compensated error amplifier. Pulse by pulse current limiting is implemented by sensing the differential voltage across an external resistor, or an appropriately sized PC board trace.

The SC1101 operates at a fixed frequency of 200kHz, providing an optimum compromise between efficiency, external component size, and cost.

#### **FEATURES**

- Low cost / small size

- Switch mode efficiency (90%)

- 1% reference voltage accuracy

- Over current protection

- 500mA output drive

- SO-8 package

## **APPLICATIONS**

- Pentium® P55 Core Supply

- Low Cost Microprocessor Supplies

- Peripheral Card Supplies

- Industrial Power Supplies

- High Density DC/DC Conversion

### ORDERING INFORMATION

| DEVICE <sup>(1)</sup> | PACKAGE | TEMP RANGE (T <sub>J</sub> ) |  |  |

|-----------------------|---------|------------------------------|--|--|

| SC1101CS              | SO-8    | 0° to 125°C                  |  |  |

#### Note:

(1) Add suffix 'TR' for tape and reel.

## **PIN CONFIGURATION**

# Top View GND Vcc [ 8 Cs(-) 2 7 FΒ 3 **BST** Cs(+) \_\_ 6 GND [ 4 DH 5 (8 LEAD PLASTIC SOIC)

## **BLOCK DIAGRAM**

# **PIN DESCRIPTION**

| Pin # | Pin Name          | Pin Function                             |  |

|-------|-------------------|------------------------------------------|--|

| 1     | V <sub>CC</sub>   | Device Input Voltage                     |  |

| 2     | C <sub>s(-)</sub> | Current Sense Input (Negative)           |  |

| 3     | $C_{s(+)}$        | Current Sense Input (Positive)           |  |

| 4     | $P_{GND}$         | Device Power Ground                      |  |

| 5     | DH                | High Side Driver Output                  |  |

| 6     | BST               | High Side Driver V <sub>CC</sub> (Boost) |  |

| 7     | FB                | Error Amplifier Input (-)                |  |

| 8     | GND               | Small Signal Ground                      |  |

# **ABSOLUTE MAXIMUM RATINGS**

| Parameter                               | Symbol                  | Maximum     | Units |

|-----------------------------------------|-------------------------|-------------|-------|

| Input Voltage                           | V <sub>cc</sub> to GND  | -0.3 to +7  | V     |

| Ground Differential                     | P <sub>GND</sub> to GND | ± 1         | V     |

| Boost Input Voltage                     | BST to GND              | -0.3 to +15 | V     |

| Operating Temperature                   | T <sub>A</sub>          | 0 to +70    | °C    |

| Storage Temperature                     | T <sub>J</sub>          | -45 to +125 | °C    |

| Lead Temperature (Soldering) 10 seconds | T <sub>L</sub>          | 300         | °C    |

| Thermal Resistance, Junction to Ambient | θ <sub>JA</sub>         | 165         | °C/W  |

| Thermal Resistance, Junction to Case    | θ <sub>JC</sub>         | 40          | °C/W  |

# **ELECTRICAL CHARACTERISTICS**

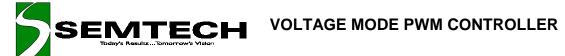

$V_{CC}$  = 4.75V to 5.25V; GND =  $P_{GND}$  = 0V;  $V_{O}$  = 3.3V;  $T_{A}$  = 25°C; BST = 12V; Output current = 2A. Per test circuit, unless otherwise specified.

| PARAMETER                  | SYMBOL              | CONDITIONS                                                | MIN   | TYP   | MAX   | UNITS |

|----------------------------|---------------------|-----------------------------------------------------------|-------|-------|-------|-------|

| Reference                  | $V_{REF}$           |                                                           | 1.238 | 1.250 | 1.263 | V     |

|                            |                     | Over Temp                                                 | 1.225 | 1.250 | 1.275 | V     |

| Feedback Bias Current      | I <sub>FB</sub>     |                                                           |       | 2.0   | 8.0   | uA    |

| Quiescent Current          | IQ                  | Current into V <sub>CC</sub> pin                          |       | 5.0   | 8.0   | mA    |

| Regulation Load            | REG <sub>LOAD</sub> | I <sub>O</sub> =1A to 12A                                 |       | 0.5   | 1.0   | %     |

| Regulation Line            | REG <sub>LINE</sub> |                                                           |       |       | 0.5   | %     |

| Current Limit Threshold    | CLT                 | CS(+) to CS(-)                                            | 60    | 70    | 80    | mV    |

| Oscillator Frequency       | OSC                 |                                                           | 180   | 200   | 220   | kHz   |

| Oscillator Frequency Shift | OFS                 | $V_{FB} < V_{REF}/2$                                      |       | 50    |       | kHz   |

| Max Duty Cycle             | d.c.                |                                                           | 90    | 95    |       | %     |

| DH Sink/Source Current     | Io                  | $V_{BST} - V_{DH} = 4.5V$<br>( $V_{DH} - V_{PGND} = 2V$ ) | 500   |       |       | mA    |

| UVLO Threshold             | V <sub>UVLO</sub>   |                                                           |       | 3.8   |       | V     |

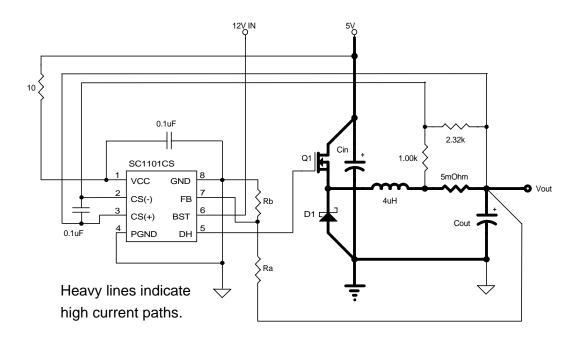

# **TEST CIRCUIT**

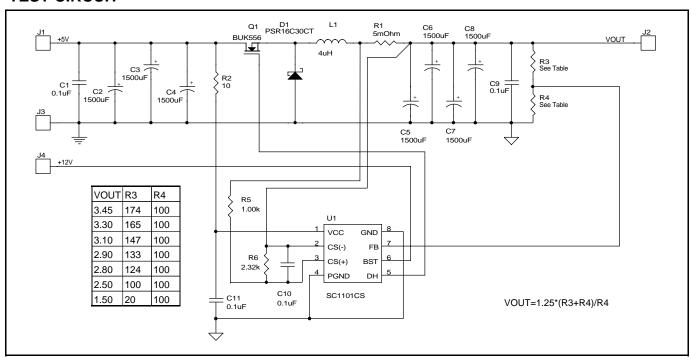

Fig.1: Error Amplifier, Gain and Phase

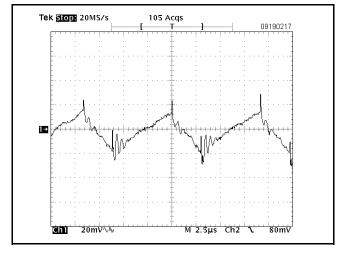

Fig.3: Ripple; Vo=2.90V; Io=10A

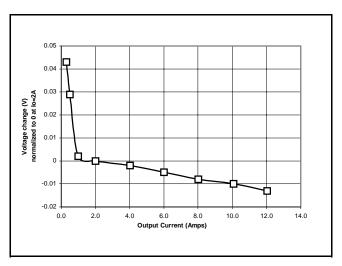

Fig.2: Load Regulation Characteristic

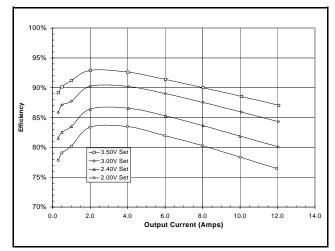

Fig.4: Efficiency

# **LAYOUT GUIDELINES**

Careful attention to layout requirements are necessary for successful implementation of the SC1101 PWM controller. High currents switching at 200kHz are present in the application and their effect on ground plane voltage differentials must be understood and minimized.

- 1). The high power parts of the circuit should be laid out first. A ground plane should be used, the number and position of ground plane interruptions should be such as to not unnecessarily compromise ground plane integrity. Isolated or semi-isolated areas of the ground plane may be deliberately introduced to constrain ground currents to particular areas, for example the input capacitor and bottom Schottky ground.

- 2). The loop formed by the Input Capacitor(s) (Cin), the Top FET (Q1) and the Schottky (D1) must be kept as small as possible. This loop contains all the high current, fast transition switching. Connections should be as wide and as short as possible to minimize loop inductance. Minimizing this loop area will reduce EMI, lower ground injection currents, resulting in electrically "cleaner" grounds for the rest of the system and minimize source ringing, resulting in more reliable gate switching signals.

- 3). The connection between the junction of Q1, D1 and the output inductor should be a wide trace or copper region. It should be as short as practical. Since this con-

- nection has fast voltage transitions, keeping this connection short will minimize EMI. The connection between the output inductor and the sense resistor should be a wide trace or copper area, there are no fast voltage or current transitions in this connection and length is not so important, however adding unnecessary impedance will reduce efficiency.

- 4) The Output Capacitor(s) (Cout) should be located as close to the load as possible, fast transient load currents are supplied by Cout only, and connections between Cout and the load must be short, wide copper areas to minimize inductance and resistance.

- 5) The SC1101 is best placed over an isolated ground plane area. GND and PGND should be returned to this isolated ground. This isolated ground area should be connected to the main ground by a trace that runs from the GND pin to the ground side of (one of) the output capacitor(s). If this is not possible, the GND pin may be connected to the ground path between the Output Capacitor(s) and the Cin, Q1, D1 loop. Under no circumstances should GND be returned to a ground inside the Cin, Q1, D1 loop.

- 6) Vcc for the SC1101 should be supplied from the 5V supply through a  $10\Omega$  resistor, the Vcc pin should be decoupled directly to GND by a  $0.1\mu F$  ceramic capacitor, trace lengths should be as short as possible.

Fig. 5 Layout diagram for the SC1101

- 7) The Current Sense resistor and the divider across it should form as small a loop as possible, the traces running back to CS(+) and CS(-) on the SC1101 should run parallel and close to each other. The  $0.1\mu F$  capacitor should be mounted as close to the CS(+) and CS(-) pins as possible.

- 8) To minimize noise pickup at the sensitive FB pin, the feedback resistors should both be close to the SC1101 with the bottom resistor (Rb) returned to ground at the GND pin.

# **Under Voltage Lockout**

The under voltage lockout circuit of the SC1101 assures that the high-side MOSFET driver outputs remain in the off state whenever the supply voltage drops below set parameters. Lockout occurs if  $V_{\rm CC}$  falls below 3.8V. Normal operation resumes once  $V_{\rm CC}$  rises above 3.8V.

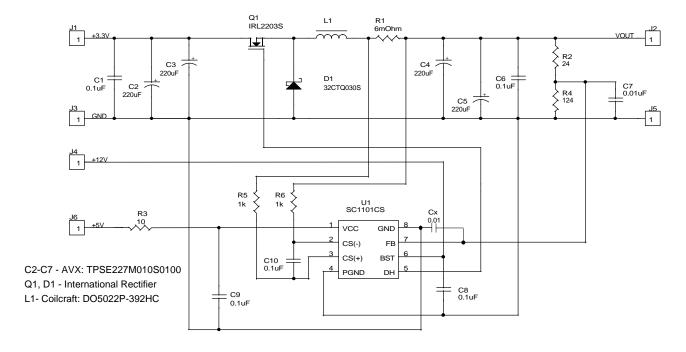

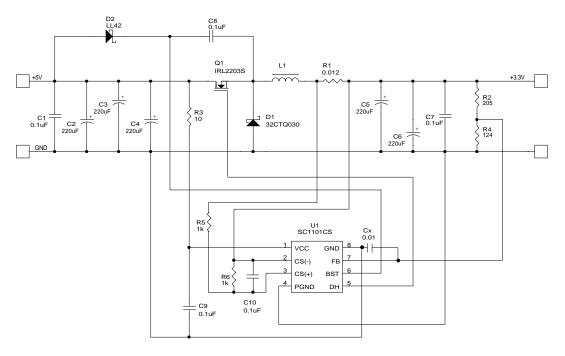

## TYPICAL APPLICATIONS

Fig. 6: GTL+ 3.3V to 1.5V 8A Application

# **TYPICAL APPLICATIONS (cont.)**

C2-C7 - AVX: TPSE227M01S0100 Q1, D1 - International Rectifier L1 - Coilcraft: DO5022P-392HC

Fig. 7: 5V to 3.3V 8A Application with flying capacitor boost

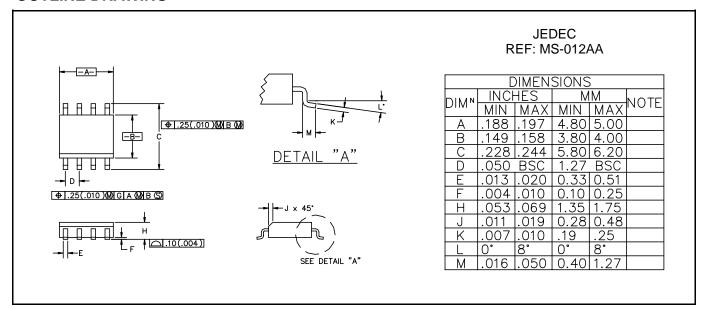

## **OUTLINE DRAWING**

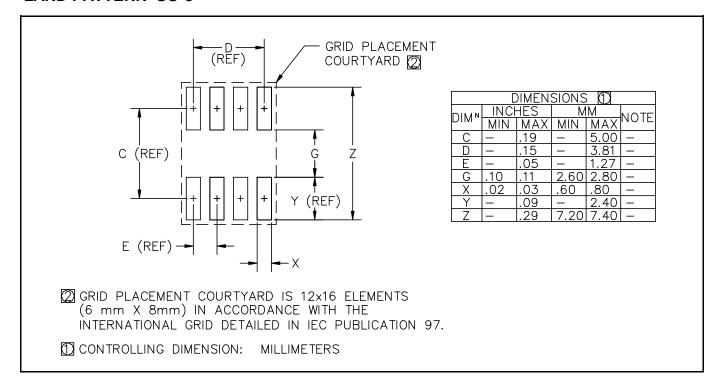

# **LAND PATTERN SO-8**

ECN00-900