# **ASI** Au

### UVEPROM SMJ27C256

Austin Semiconductor, Inc.

### 256K UVEPROM

UV Erasable Programmable Read-Only Memory

### AVAILABLE AS MILITARY SPECIFICATIONS

- SMD 5962-86063

- MIL-STD-883

#### **FEATURES**

- Organized 32,768 x 8

- Single  $+5V \pm 10\%$  power supply

- Pin-compatible with existing 256K ROM's and EPROM's

- All inputs/outputs fully TTL compatible

- · Power-saving CMOS technology

- Very high-speed SNAP! Pulse Programming

- 3-state output buffers

- 400-mV DC assured noise immunity with standarad TTL loads

- Latchup immunity of 250 mA on all input and output pins

- Low power dissipation (CMOS Input Levels)

- ✓ Active 165mW Worst Case

- ✓ Standby 1.7mW Worst Case (CMOS-input levels)

| OPTIONS               | MARKING |       |

|-----------------------|---------|-------|

| • Timing              |         |       |

| 150ns access          | -15     |       |

| 170ns access          | -17     |       |

| 200ns access          | -20     |       |

| 250ns access          | -25     |       |

| 300ns access          | -30     |       |

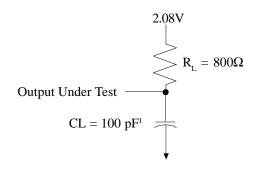

| • Package(s)          |         | 440   |

| Ceramic DIP (600mils) | J No    | . 110 |

• Operating Temperature Ranges Military (-55°C to +125°C) M

> For more products and information please visit our web site at www.austinsemiconductor.com

### **GENERAL DESCRIPTION**

The SMJ27C256 series is a set of 262,144 bit, ultraviolet-light erasable, electrically programmable read-only memories. These devices are fabricated using power-saving CMOS technology for high speed and simple interface with MOS and bipolar circuits. All inputs (including program data inputs) can be driven by Series 54 TTL circuits without the use of external pullup resistors. Each output can drive one Series 54 TTL circuit without external resistors. The data outputs are 3-state for connecting multiple devices to a common bus. The SMJ27C256 is pin-compatible with 28-pin 256K ROMs and EPROMs. It is offered in a 600mil dual-in-line ceramic pagackage (J suffix) rated for operation from -55°C to 125°C.

Because this EPROM operates from a single 5V supply (in the read mode), it is ideal for use in microprocessor-based systems. One other supply (13V) is needed for programming. All programming signals are TTL level. This device is programmable by the SNAP! Pulse programming algorithm. The SNAP! Pulse programming algorithm uses a  $V_{\rm PP}$  of 13V and a  $V_{\rm CC}$  of 6.5V for a nominal programming time of four seconds. For programming outside the system, existing EPROM programmers can be used. Locations can be programmed singly, in blocks, or at random.

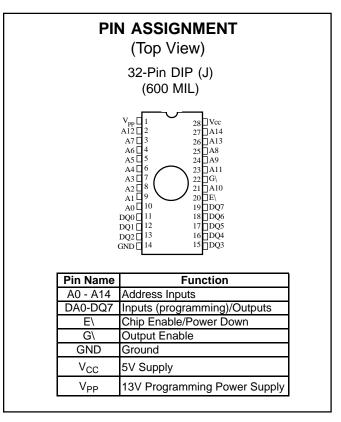

### **FUNCTIONAL BLOCK DIAGRAM\***

<sup>\*</sup> This symbol is in accordance with ANSI/IEEE std 91-1984 and IEC Publication 617-12.

#### **OPERATION**

The seven modes of operation for the SMJ27C256 are listed in Table 1. The read mode requires a single 5V supply. All inputs are TTL level except for  $V_{pp}$  during programming (13V for SNAP! Pulse), and (12V) on A9 for signature mode.

### **TABLE 1. OPERATION MODES**

| FUNCTION             |                 | MODE*             |                 |                 |                 |                 |          |          |  |

|----------------------|-----------------|-------------------|-----------------|-----------------|-----------------|-----------------|----------|----------|--|

| (PINS)               | READ            | OUTPUT<br>DISABLE | STANDBY         | PROGRAMMING     | VERIFY          | PROGRAM INHIBIT | SIGNATU  | RE MODE  |  |

| E\ (20)              | $V_{IL}$        | $V_{IL}$          | $V_{IH}$        | $V_{IL}$        | $V_{IH}$        | $V_{IH}$        | V        | IL.      |  |

| G\ (22)              | $V_{IL}$        | $V_{IH}$          | Χ               | V <sub>IH</sub> | $V_{IL}$        | Χ               | V        | IL.      |  |

| V <sub>PP</sub> (1)  | V <sub>CC</sub> | V <sub>CC</sub>   | $V_{CC}$        | $V_{PP}$        | $V_{PP}$        | $V_{PP}$        | V        | CC       |  |

| V <sub>CC</sub> (28) | V <sub>CC</sub> | V <sub>CC</sub>   | V <sub>CC</sub> | $V_{CC}$        | V <sub>CC</sub> | V <sub>CC</sub> | V        | CC       |  |

| A9 (24)              | Х               | Х                 | Х               | X               | Χ               | Х               | $V_{ID}$ | $V_{ID}$ |  |

| A0 (10)              | Х               | Х                 | X               | X               | X               | Χ               | $V_{IL}$ | $V_{IH}$ |  |

| DQ0-DQ7              |                 |                   |                 |                 |                 |                 | CC       | DE       |  |

| (11-13, 15-19)       | Data Out        | High-Z            | High-Z          | Data In         | Data Out        | High-Z          | MFG      | DEVICE   |  |

| (11 10, 10 10)       |                 |                   |                 |                 |                 |                 | 97       | 04       |  |

<sup>\*</sup> X can be  $V_{IL}$  or  $V_{IH}$ .

# **ASI** Au

### UVEPROM SMJ27C256

Austin Semiconductor, Inc.

#### READ/OUTPUT DISABLE

When the outputs of two or more SMJ27C256s are connected in parallel on the same bus, the output of any particular device in the circuit can be read with no interference from the competing outputs of the other devices. To read the output of the selected SMJ27C256, a low-level signal is applied to  $E\setminus$  and  $G\setminus$ . All other devices in the circuit should have their outputs disabled by applying a high-level signal to one of these pins. Output data is accessed at pins DQ0 through DQ7.

#### **LATCHUP IMMUNITY**

Latchup immunity on the SMJ27C256 is a minimum of 250mA on all inputs and outputs. This feature provides latchup immunity beyond any potential transients at the printed circuit board level when the EPROM is interfaced to industry standard TTL or MOS logic devices. Input/output layout approach controls latchup without compromising performance or packing density.

#### **POWER DOWN**

Active  $I_{CC}$  supply current can be reduced from 25mA (SMJ27C256-15 through SMJ27C256-25) to 500 $\mu$ A (TTL-level inputs) or 300 $\mu$ A (CMOS-level inputs) by applying a high TTL/CMOS signal to the  $E \setminus pin$ . In this mode all outputs are in the high-impedance state.

#### **ERASURE**

Before programming, the SMJ27C256 is erased by exposing the chip through the transparent lid to a high-intensity ultraviolet light (wavelength 2537 Å). EPROM erasure before programming is necessary to ensure that all bits are in the logic-high state. Logic-lows are programmed into the desired locations. A programmed logic-low can be erased only by ultraviolet light. The recommended minimum exposure dose (UV intensity x exposure time) is 15W•s/cm². A typical 12mW/cm², filterless UV lamp erases the device in 21 minutes. The lamp should be located about 2.5cm above the chip during erasure. After erasure, all bits are in the high state. It should be noted that normal ambient light contains the correct wavelength for erasure; therefore, when using the SMJ27C256, the window should be covered with an opaque label.

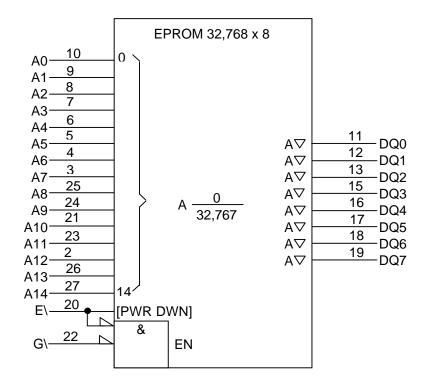

#### SNAP! PULSE PROGRAMMING

The SMJ27C256 EPROM is programmed by using the SNAP! Pulse programming algorithm as illustrated by the flowchart in Figure 1. This algorithm programs the device in a nominal time of 4 seconds. Actual programming time varies as a function of the programmer used.

Data is presented in parallel (eight bits) on pins DQ0 to DQ7. Once addresses and data are stable, E\ is pulsed.

The SNAP! Pulse programming algorithm uses initial pulses of 100 microseconds (µs) followed by a byte-verification step to determine when the addressed byte has been successfully programmed. Up to ten 100µs pulses per byte are provided before a failure is recognized.

The programming mode is achieved when  $V_{PP} = 13V$ ,  $V_{CC} = 6.5V$ ,  $G \setminus = V_{IH}$ , and  $E \setminus = V_{IL}$ . More than one device can be programmed when the devices are connected in parallel. Locations can be programmed in any order. When the SNAP! Pulse programming routine is completed, all bits are verified with  $V_{CC} = V_{PP} = 5V$ .

#### **PROGRAM INHIBIT**

Programming can be inhibited by maintaining a high-level input on  $E \setminus .$

### **PROGRAM VERIFY**

Programmed bits can be verified with  $V_{pp}=13V$  when  $G \setminus = V_{II}$ , and  $E \setminus = V_{IH}$ .

#### SIGNATURE MODE

The signature mode provides access to a binary code identifying the manufacturer and device type. This mode is activated when A9 is forced to  $12V\pm0.5V$ . Two identifier bytes are accessed by A0 (terminal 10); i.e.,  $A0=V_{IL}$  accesses the manufacturer code, which is output on DQ0-DQ7;  $A0=V_{IH}$  accesses the device code, which is also output on DQ0-DQ7. All other addresses must be held at VIL. Each byte contains odd parity on bit DQ7. The manufacturer code for these devices is 97h and the device code is 04h.

### FIGURE 1. SNAP! PULSE PROGRAMMING FLOW CHART

### UVEPROM SMJ27C256

### Austin Semiconductor, Inc.

#### **ABSOLUTE MAXIMUM RATINGS\***

| Supply Voltage Range, $V_{CC}^{**}$ 0.6V to +7.0V         |

|-----------------------------------------------------------|

| Supply Voltage Range, V <sub>pp</sub> **0.6V to +14.0V    |

| Input Voltage Range, All inputs except A9**0.6V to +6.5V  |

| A90.6V to +13.5V                                          |

| Output Voltage Range**0.6V to $V_{CC}$ +1V                |

| Minimum Operating Free-air Temperature, $T_A$ 55°C        |

| Maximum Operating Case Temperature, T <sub>C</sub> 125°C  |

| Storage Temperature Range, T <sub>stg</sub> 65°C to 150°C |

|                                                           |

\*Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operation section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

\*\* All voltage values are with respect to GND.

### RECOMMENDED OPERATING CONDITIONS

|                 |                                                        |                           |                        | MIN                  | TYP | MAX                  | UNIT |

|-----------------|--------------------------------------------------------|---------------------------|------------------------|----------------------|-----|----------------------|------|

| V <sub>CC</sub> | Supply Voltage                                         | Read Mode <sup>1</sup>    | Read Mode <sup>1</sup> |                      | 5   | 5.5                  | V    |

| VCC             | oupply voltage                                         | SNAP! Pulse programming a | lgorithm               | 6.25                 | 6.5 | 6.75                 | V    |

| $V_{PP}$        | Supply Voltage                                         | Read Mode <sup>2</sup>    |                        |                      |     | V <sub>CC</sub> -0.6 | V    |

| * PP            | Cuppiy Vollage                                         | SNAP! Pulse programming a | lgorithm               | 12.75                | 13  | 13.25                | V    |

| V <sub>IH</sub> | V <sub>IH</sub> High-level input voltage               |                           | TTL inputs             | 2                    |     | V <sub>CC</sub> +1   | V    |

| VIH             | i ligii-level liiput v                                 | CMOS inputs               |                        | V <sub>CC</sub> -0.2 |     | V <sub>CC</sub> +1   | V    |

| V <sub>IL</sub> | Low-level input vo                                     | oltage                    | TTL inputs             | -0.5                 |     | 0.8                  | V    |

| ۷IL             | Low-level illput vo                                    | Jilage                    | CMOS inputs            | -0.5                 |     | 0.2                  | V    |

| $V_{ID}$        | V <sub>ID</sub> Voltage level on A9 for signature mode |                           |                        | 11.5                 |     | 13                   | V    |

| T <sub>A</sub>  | T <sub>A</sub> Operating free-air temperature          |                           | -55                    |                      |     | °C                   |      |

| T <sub>C</sub>  | Operating case te                                      | mperature                 |                        | ·                    |     | +125                 | °C   |

#### NOTES

### ELECTRICAL CHARACTERISTICS OVER RECOMMENDED RANGES OF SUPPLY VOLTAGE AND OPERATING FREE-AIR TEMPERATURE

|                  | PARAMETER                                                          | TEST CONDITIONS                                      | MIN                                                                       | TYP <sup>1</sup> | MAX | UNIT |    |

|------------------|--------------------------------------------------------------------|------------------------------------------------------|---------------------------------------------------------------------------|------------------|-----|------|----|

| V <sub>OH</sub>  | High-level output voltage                                          |                                                      | $I_{OH} = -400 \mu A$                                                     | 2.4              |     |      | V  |

| V <sub>OL</sub>  | Low-level output voltage                                           |                                                      | $I_{OL} = 2.1 \text{mA}$                                                  |                  |     | 0.4  | V  |

| I <sub>I</sub>   | Input current (leakage)                                            |                                                      | $V_{I} = 0V \text{ to } 5.5V$                                             |                  |     | ±1   | μΑ |

| Ιo               | Output current (leakage)                                           |                                                      | $V_O = 0V$ to $V_{CC}$                                                    |                  |     | ±1   | μΑ |

| I <sub>PP1</sub> | PP1 VPP supply current                                             |                                                      | $V_{PP} = V_{CC} = 5.5V$                                                  |                  |     | 10   | μΑ |

| I <sub>PP2</sub> | V <sub>PP</sub> supply current (during program pulse) <sup>2</sup> |                                                      | V <sub>PP</sub> = 13V                                                     |                  | 35  | 50   | mA |

| 1                | V <sub>CC</sub> supply current (standby)                           | TTL-Input Level                                      | $V_{CC} = 5.5V, E = V_{IH}$                                               |                  |     | 500  | μA |

| I <sub>CC1</sub> | VCC supply current (standby)                                       | CMOS-Input Level                                     | $V_{CC} = 5.5V$ , $E = V_{CC}$                                            |                  |     | 300  | μA |

| I <sub>CC2</sub> | V <sub>CC</sub> supply current (active)                            | '27C256-15<br>'27C256-17<br>'27C256-20<br>'27C256-25 | $E = V_{IL}$ , $V_{CC} = 5.5V$<br>$t_{cycle} = minimum$ , outputs<br>open |                  | 15  | 25   | mA |

| Ios              | Output current (leakage)                                           | •                                                    |                                                                           |                  |     | 100  | mA |

### NOTES:

- 1. Typical values are at  $T_A$ =25°C and nominal voltages.

- 2. This parameter has been characterized at 25°C and is not tested.

<sup>1.</sup>  $V_{CC}$  must be applied before or at the same time as  $V_{pp}$  and removed after or at the same time as  $V_{pp}$ . The deivce must not be inserted into or removed from the board when  $V_{pp}$  or  $V_{CC}$  is applied.

<sup>2.</sup>  $V_{pp}$  can be connected to  $V_{CC}$  directly (except in the program mode).  $V_{CC}$  supply current in this case would be  $I_{CC} + I_{pp_1}$ .

### UVEPROM SMJ27C256

Austin Semiconductor, Inc.

### CAPACITANCE OVER RECOMMENDED RANGES OF SUPPLY VOLTAGE AND OPERATING FREE-AIR TEMPERATURE, $f = 1 \text{MHz}^*$

| PARAMETER      |                    | PARAMETER TEST CONDITIONS |    | MAX | UNIT |

|----------------|--------------------|---------------------------|----|-----|------|

| C <sub>i</sub> | Input capacitance  | $V_I = 0V$                | 6  | 10  | pF   |

| Co             | Output capacitance | $V_O = 0V$                | 10 | 14  | pF   |

<sup>\*</sup> Capacitance measurements are made on a sample basis only.

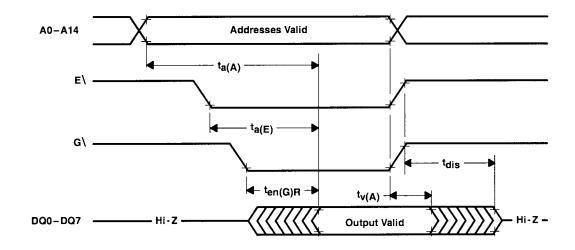

### SWITCHING CHARACTERISTICS OVER RECOMMENDED RANGES OF SUPPLY VOLTAGE AND OPERATING FREE-AIR TEMPERATURE<sup>1,2</sup>

|                     | DARAMETER                                                                                  |                            | -15 |     | -17 |     | LINIT |

|---------------------|--------------------------------------------------------------------------------------------|----------------------------|-----|-----|-----|-----|-------|

|                     | PARAMETER                                                                                  | CONDITIONS <sup>1, 2</sup> | MIN | MAX | MIN | MAX | UNIT  |

| t <sub>a(A)</sub>   | Access time from address                                                                   |                            |     | 150 |     | 170 | ns    |

| t <sub>a(E)</sub>   | Access time from E\                                                                        |                            |     | 150 |     | 170 | ns    |

| t <sub>en(G)R</sub> | Output enable time from G\                                                                 |                            |     | 70  |     | 70  | ns    |

| t <sub>dis</sub>    | Disable time of output from G\ or E whichever occurs first <sup>3</sup>                    | see Figure 2               | 0   | 55  | 0   | 55  | ns    |

| t <sub>v(A)</sub>   | Output data valid time after change of address, E or G whichever occurs first <sup>3</sup> |                            | 0   |     | 0   |     | ns    |

|                     | DADAMETER                                                                                  |                            | _   | 20  | -2  | 25  | -3  | 30  | LINUT |

|---------------------|--------------------------------------------------------------------------------------------|----------------------------|-----|-----|-----|-----|-----|-----|-------|

| PARAMETER           |                                                                                            | CONDITIONS <sup>1, 2</sup> | MIN | MAX | MIN | MAX | MIN | MAX | UNIT  |

| t <sub>a(A)</sub>   | Access time from address                                                                   |                            |     | 200 |     | 250 |     | 300 | ns    |

| t <sub>a(E)</sub>   | Access time from E\                                                                        |                            |     | 200 |     | 250 |     | 300 | ns    |

| t <sub>en(G)R</sub> | Output enable time from G\                                                                 |                            |     | 75  |     | 100 |     | 120 | ns    |

| t <sub>dis</sub>    | Disable time of output from G\ or E whichever occurs first <sup>3</sup>                    | see Figure 2               | 0   | 60  | 0   | 60  | 0   | 105 | ns    |

| t <sub>v(A)</sub>   | Output data valid time after change of address, E or G whichever occurs first <sup>3</sup> |                            | 0   |     | 0   |     | 0   |     | ns    |

#### NOTES:

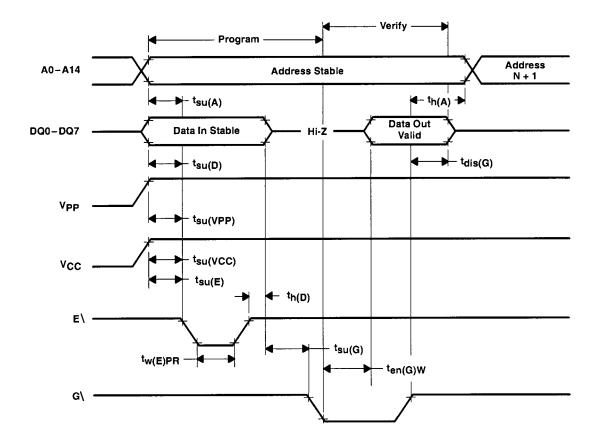

### SWITCHING CHARACTERISTICS FOR PROGRAMMING: $V_{cc} = 6.5V$ and $V_{pp} = 13V$ (SNAP! Pulse), $T_{\Delta} = 25^{\circ}C$

|                     | PARAMETER                   | MIN | MAX | UNIT |

|---------------------|-----------------------------|-----|-----|------|

| t <sub>dis(G)</sub> | Output disable time from G\ | 0   | 130 | ns   |

| t <sub>en(G)W</sub> | Output enable time from G\  |     | 150 | ns   |

<sup>\*\*</sup> Typical values are at  $T_A = 25$ °C and nominal voltages.

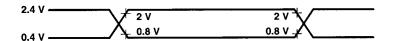

$<sup>1.</sup> Timing\ measurements\ are\ made\ at\ 2V\ for\ logic\ high\ and\ 0.8V\ for\ logic\ low\ (see\ figure\ 2).$

<sup>2.</sup> Common test conditions apply for  $\mathbf{t}_{\mathrm{dis}}$  except during programming.

<sup>3.</sup> Value calculated from 0.5V delta to measured output level. This parameter is only sampled and not 100% tested.

### **UVEPROM** SMJ27C256

Austin Semiconductor, Inc.

### RECOMMENDED TIMING REQUIREMENTS FOR PROGRAMMING: $V_{CC} = 6.5$ and $V_{PP} = 13$ (SNAP! Pulse), $T_{\Delta} = 25^{\circ}C$ (See Figure 2)

|                      |                                 | MIN | TYP | MAX | UNIT |

|----------------------|---------------------------------|-----|-----|-----|------|

| t <sub>h(A)</sub>    | Hold Time, Address              | 0   |     |     | μs   |

| t <sub>h(D)</sub>    | Hold Time, Data                 | 2   |     |     | μs   |

| t <sub>w(E)PR</sub>  | Pulse Duration, Initial Program | 95  | 100 | 105 | μs   |

| t <sub>su(A)</sub>   | Setup Time, Address             | 2   |     |     | μs   |

| t <sub>su(G)</sub>   | Setup Time, G\                  | 2   |     |     | μs   |

| t <sub>su(E)</sub>   | Setup Time, E\                  | 2   |     |     | μs   |

| t <sub>su(D)</sub>   | Setup Time, Data                | 2   |     |     | μs   |

| t <sub>su(VPP)</sub> | Setup Time, V <sub>PP</sub>     | 2   |     |     | μs   |

| t <sub>su(VCC)</sub> | Setup Time, V <sub>CC</sub>     | 2   |     |     | μs   |

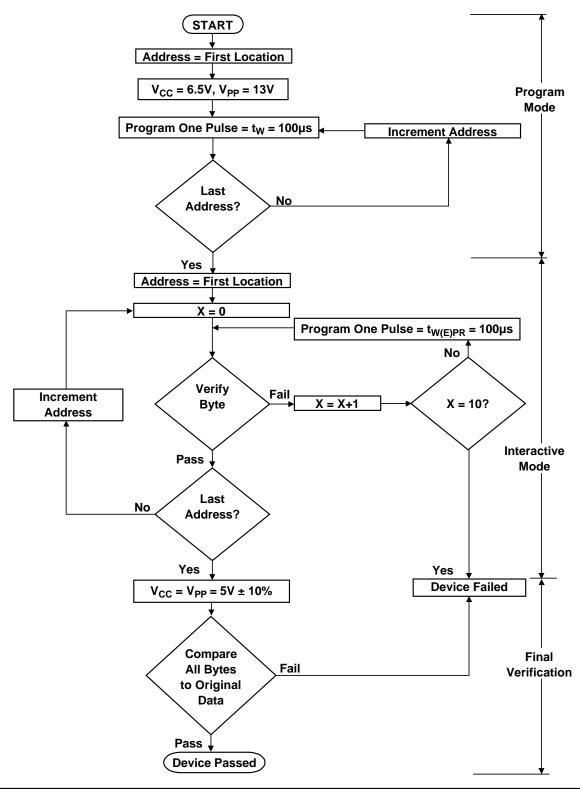

### PARAMETER MEASUREMENT INFORMATION

### NOTES:

$1. C_{\rm I}$  includes probe and fixture capacitance.

The AC testing inputs are driven at 2.4V for logic high and 0.4V for logic low. Timing measurements are made at 2V for logic high and 0.8V for logic low for both inputs and outputs.

### FIGURE 2. LOAD CIRCUIT AND VOLTAGE WAVEFORMS

### FIGURE 3. READ-CYCLETIMING

### FIGURE 4. PROGRAM-CYCLE TIMING (SNAP! PULSE PROGRAMMING)

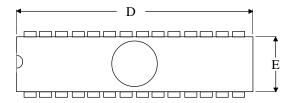

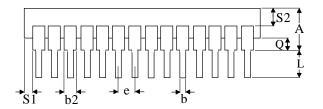

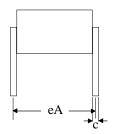

### **MECHANICAL DEFINITION\***

## ASI Case #110 (Package Designator CW) SMD 5962-86063, Case Outline X

|        | SMD SPECIFICATIONS |       |  |  |  |  |

|--------|--------------------|-------|--|--|--|--|

| SYMBOL | MIN                | MAX   |  |  |  |  |

| Α      |                    | 0.232 |  |  |  |  |

| b      | 0.014              | 0.026 |  |  |  |  |

| b2     | 0.045              | 0.065 |  |  |  |  |

| С      | 0.008              | 0.018 |  |  |  |  |

| D      |                    | 1.490 |  |  |  |  |

| E      | 0.500              | 0.610 |  |  |  |  |

| eA     | 0.600              | BSC   |  |  |  |  |

| е      | 0.100              | ) BSC |  |  |  |  |

| L      | 0.125              | 0.200 |  |  |  |  |

| Q      | 0.015              | 0.060 |  |  |  |  |

| S1     | 0.005              |       |  |  |  |  |

| S2     | 0.005              |       |  |  |  |  |

**NOTE:** These dimensions are per the SMD. ASI's package dimensional limits may differ, but they will be within the SMD limits.

### ORDERING INFORMATION

EXAMPLE: SMJ27C256-30JM

| Device<br>Number | Speed ns | Package<br>Type | Operating Temp. |

|------------------|----------|-----------------|-----------------|

| SMJ27C256        | -15      | J               | *               |

| SMJ27C256        | -17      | J               | *               |

| SMJ27C256        | -20      | J               | *               |

| SMJ27C256        | -25      | J               | *               |

| SMJ27C256        | -30      | J               | *               |

### \*AVAILABLE PROCESSES

M = Extended Temperature Range

-55°C to +125°C

## ASI Austin Semiconductor, Inc.

UVEPROM SMJ27C256

## ASI TO DSCC PART NUMBER CROSS REFERENCE\*

### **ASI Package Designator J**

| TI Part #**    | SMD Part #     |

|----------------|----------------|

| SMJ27C256-15JM | 5962-8606305XA |

| SMJ27C256-17JM | 5962-8606304XA |

| SMJ27C256-20JM | 5962-8606301XA |

| SMJ27C256-25JM | 5962-8606302XA |

| SMJ27C256-30JM | 5962-8606303XA |

<sup>\*</sup> ASI part number is for reference only. Orders received referencing the SMD part number will be processed per the SMD.

<sup>\*\*</sup> Parts are listed on SMD under the old Texas Instruments part number. ASI purchased this product line in November of 1999.