**NXP Semiconductors**

Data Sheet: Technical Data

#### Document Number: MPC5777C

Rev. 11, 04/2017

# **MPC5777C**

# **MPC5777C Microcontroller Data Sheet**

#### Features

• This document provides electrical specifications, pin assignments, and package diagram information for the MPC5777C series of microcontroller units (MCUs).

• For functional characteristics and the programming model, see the MPC5777C Reference Manual.

# **Table of Contents**

| 1 Introd | duction    | 3                                            |        | 3.11.1        | Power management electrical characteristics 40 |

|----------|------------|----------------------------------------------|--------|---------------|------------------------------------------------|

| 1.1      | Feature    | s summary3                                   |        | 3.11.2        | Power management integration43                 |

| 1.2      | Block di   | agram4                                       |        | 3.11.3        | Device voltage monitoring44                    |

| 2 Pino   | uts        | 5                                            |        | 3.11.4        | Power sequencing requirements46                |

| 2.1      | 416-ball   | MAPBGA pin assignments5                      | 3.12   | Flash mer     | mory specifications47                          |

| 2.2      | 516-ball   | MAPBGA pin assignments6                      |        | 3.12.1        | Flash memory program and erase                 |

| 3 Elect  | rical char | racteristics7                                |        |               | specifications                                 |

| 3.1      | Absolute   | e maximum ratings7                           |        | 3.12.2        | Flash memory Array Integrity and Margin        |

| 3.2      | Electron   | nagnetic interference (EMI) characteristics9 |        |               | Read specifications48                          |

| 3.3      | Electros   | static discharge (ESD) characteristics9      |        | 3.12.3        | Flash memory module life specifications49      |

| 3.4      | Operatir   | ng conditions9                               |        | 3.12.4        | Data retention vs program/erase cycles50       |

| 3.5      | DC elec    | trical specifications12                      |        | 3.12.5        | Flash memory AC timing specifications50        |

| 3.6      | I/O pad    | specifications                               |        | 3.12.6        | Flash memory read wait-state and address-      |

|          | 3.6.1      | Input pad specifications13                   |        |               | pipeline control settings51                    |

|          | 3.6.2      | Output pad specifications15                  | 3.13   | AC timing     | 52                                             |

|          | 3.6.3      | I/O pad current specifications19             |        | 3.13.1        | Generic timing diagrams52                      |

| 3.7      | Oscillato  | or and PLL electrical specifications19       |        | 3.13.2        | Reset and configuration pin timing53           |

|          | 3.7.1      | PLL electrical specifications20              |        | 3.13.3        | IEEE 1149.1 interface timing54                 |

|          | 3.7.2      | Oscillator electrical specifications21       |        | 3.13.4        | Nexus timing57                                 |

| 3.8      | Analog-    | to-Digital Converter (ADC) electrical        |        | 3.13.5        | External Bus Interface (EBI) timing59          |

|          | specifica  | ations23                                     |        | 3.13.6        | External interrupt timing (IRQ/NMI pin)63      |

|          | 3.8.1      | Enhanced Queued Analog-to-Digital            |        | 3.13.7        | eTPU timing64                                  |

|          |            | Converter (eQADC)23                          |        | 3.13.8        | eMIOS timing65                                 |

|          | 3.8.2      | Sigma-Delta ADC (SDADC)25                    |        | 3.13.9        | DSPI timing with CMOS and LVDS pads66          |

| 3.9      | Temper     | ature Sensor34                               |        | 3.13.10       | FEC timing78                                   |

| 3.10     | LVDS F     | ast Asynchronous Serial Transmission (LFAST) | 4 Pack | kage informa  | ation83                                        |

|          | pad elec   | ctrical characteristics34                    | 4.1    | Thermal o     | haracteristics83                               |

|          | 3.10.1     | LFAST interface timing diagrams34            |        | 4.1.1         | General notes for thermal characteristics84    |

|          | 3.10.2     | LFAST and MSC/DSPI LVDS interface            | 5 Orde | ering informa | ation87                                        |

|          |            | electrical characteristics36                 | 6 Docu | ument revisi  | ion history88                                  |

|          | 3.10.3     | LFAST PLL electrical characteristics39       |        |               |                                                |

| 3.11     | Power n    | nanagement: PMC, POR/LVD, power              |        |               |                                                |

|          | sequenc    | cing40                                       |        |               |                                                |

### 1 Introduction

# 1.1 Features summary

On-chip modules available within the family include the following features:

- Three dual issue, 32-bit CPU core complexes (e200z7), two of which run in lockstep

- Power Architecture embedded specification compliance

- Instruction set enhancement allowing variable length encoding (VLE), optional encoding of mixed 16-bit and 32-bit instructions, for code size footprint reduction

- On the two computational cores: Signal processing extension (SPE1.1) instruction support for digital signal processing (DSP)

- Single-precision floating point operations

- On the two computational cores: 16 KB I-Cache and 16 KB D-Cache

- Hardware cache coherency between cores

- 16 hardware semaphores

- 3-channel CRC module

- 8 MB on-chip flash memory

- Supports read during program and erase operations, and multiple blocks allowing EEPROM emulation

- 512 KB on-chip general-purpose SRAM including 64 KB standby RAM

- Two multichannel direct memory access controllers (eDMA)

- 64 channels per eDMA

- Dual core Interrupt Controller (INTC)

- Dual phase-locked loops (PLLs) with stable clock domain for peripherals and frequency modulation (FM) domain for computational shell

- Crossbar Switch architecture for concurrent access to peripherals, flash memory, or RAM from multiple bus masters with End-To-End ECC

- External Bus Interface (EBI) for calibration and application use

- System Integration Unit (SIU)

- Error Injection Module (EIM) and Error Reporting Module (ERM)

- Four protected port output (PPO) pins

- Boot Assist Module (BAM) supports serial bootload via CAN or SCI

- Three second-generation Enhanced Time Processor Units (eTPUs)

- 32 channels per eTPU

- Total of 36 KB code RAM

- Total of 9 KB parameter RAM

VD 0 . . . . . .

MPC5777C Microcontroller Data Sheet Data Sheet, Rev. 11, 04/2017.

#### Introduction

- Enhanced Modular Input/Output System (eMIOS) supporting 32 unified channels with each channel capable of single action, double action, pulse width modulation (PWM) and modulus counter operation

- Two Enhanced Queued Analog-to-Digital Converter (eQADC) modules with:

- Two separate analog converters per eQADC module

- Support for a total of 70 analog input pins, expandable to 182 inputs with offchip multiplexers

- Interface to twelve hardware Decimation Filters

- Enhanced "Tap" command to route any conversion to two separate Decimation Filters

- Four independent 16-bit Sigma-Delta ADCs (SDADCs)

- 10-channel Reaction Module

- Ethernet (FEC)

- Two PSI5 modules

- Two SENT Receiver (SRX) modules supporting 12 channels

- Zipwire: SIPI and LFAST modules

- Five Deserial Serial Peripheral Interface (DSPI) modules

- Five Enhanced Serial Communication Interface (eSCI) modules

- Four Controller Area Network (FlexCAN) modules

- Two M\_CAN modules that support FD

- Fault Collection and Control Unit (FCCU)

- Clock Monitor Units (CMUs)

- Tamper Detection Module (TDM)

- Cryptographic Services Engine (CSE)

- Complies with Secure Hardware Extension (SHE) Functional Specification Version 1.1 security functions

- Includes software selectable enhancement to key usage flag for MAC verification and increase in number of memory slots for security keys

- PASS module to support security features

- Nexus development interface (NDI) per IEEE-ISTO 5001-2003 standard, with some support for 2010 standard

- Device and board test support per Joint Test Action Group (JTAG) IEEE 1149.1 and 1149.7

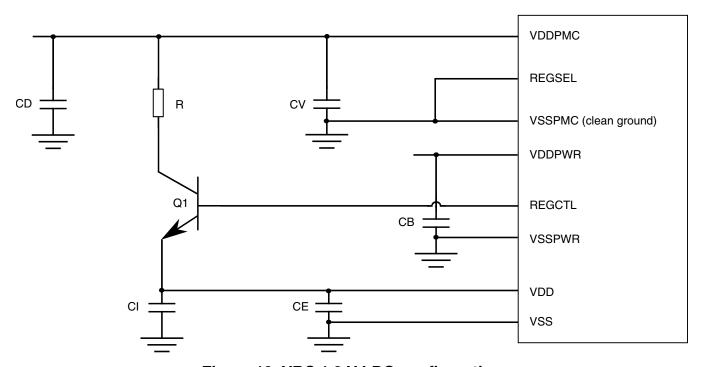

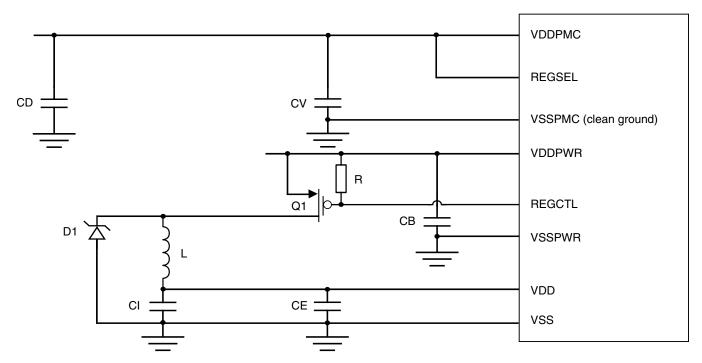

- On-chip voltage regulator controller (VRC) that derives the core logic supply voltage from the high-voltage supply

- On-chip voltage regulator for flash memory

- Self Test capability

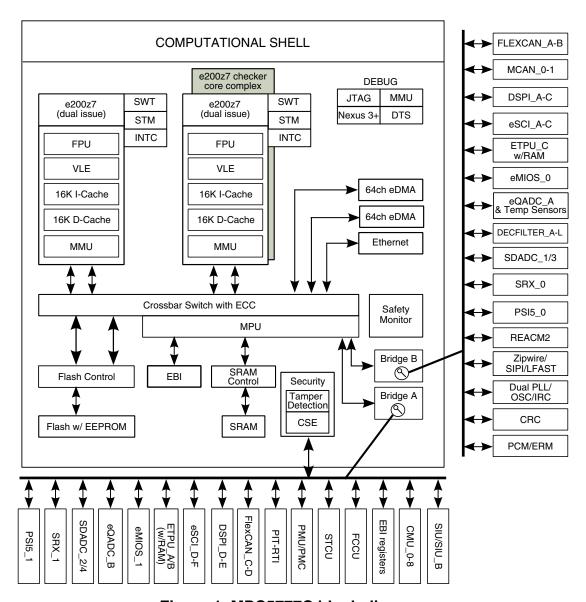

# 1.2 Block diagram

The following figure shows a top-level block diagram of the MPC5777C. The purpose of the block diagram is to show the general interconnection of functional modules through the crossbar switch.

Figure 1. MPC5777C block diagram

### 2 Pinouts

# 2.1 416-ball MAPBGA pin assignments

Figure 2 shows the 416-ball MAPBGA pin assignments.

MPC5777C Microcontroller Data Sheet Data Sheet, Rev. 11, 04/2017.

# **Pinouts** ANB15 ANB18 AN30 AN34 ANSS ANB12 ANB16 ANB19 ETPUC2 ETPUA25 ETPUA23 ETPUC5 ETPUA21 ETPUC9 ETPUA1 WKPCFG TXDB PLLCFG2

Figure 2. MPC5777C 416-ball MAPBGA (full diagram)

# 2.2 516-ball MAPBGA pin assignments

Figure 3 shows the 516-ball MAPBGA pin assignments.

Figure 3. MPC5777C 516-ball MAPBGA (full diagram)

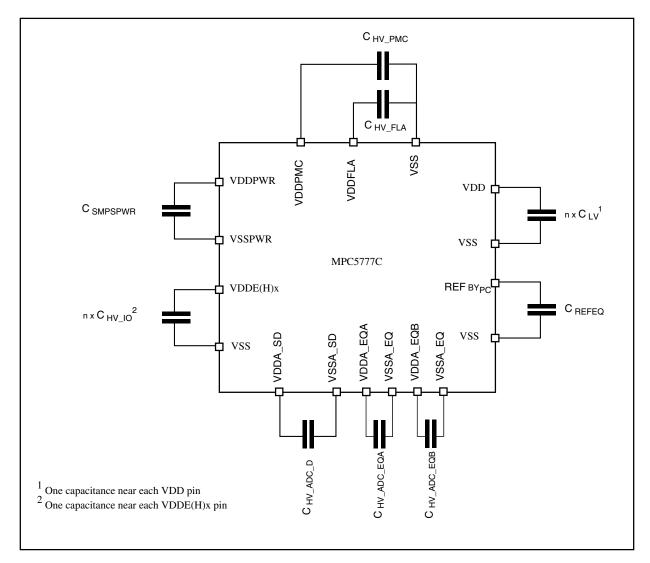

The following information includes details about power considerations, DC/AC electrical characteristics, and AC timing specifications.

# 3.1 Absolute maximum ratings

Absolute maximum specifications are stress ratings only. Functional operation at these maxima is not guaranteed.

#### CAUTION

Stress beyond listed maxima may affect device reliability or cause permanent damage to the device.

See Operating conditions for functional operation specifications.

MPC5777C Microcontroller Data Sheet Data Sheet, Rev. 11, 04/2017.

Table 1. Absolute maximum ratings

| Cumbal                                | Dorometer                                                | Conditions <sup>1</sup>                                 | Va   | alue  | 1154  |

|---------------------------------------|----------------------------------------------------------|---------------------------------------------------------|------|-------|-------|

| Symbol                                | Parameter                                                | Conditions                                              | Min  | Max   | Unit  |

| Cycle                                 | Lifetime power cycles                                    | _                                                       | _    | 1000k | _     |

| $V_{DD}$                              | 1.2 V core supply voltage <sup>2, 3, 4</sup>             | _                                                       | -0.3 | 1.5   | V     |

| $V_{DDEHx}$                           | I/O supply voltage (medium I/O pads) <sup>5</sup>        | _                                                       | -0.3 | 6.0   | V     |

| $V_{DDEx}$                            | I/O supply voltage (fast I/O pads) <sup>5</sup>          | _                                                       | -0.3 | 6.0   | V     |

| $V_{DDPMC}$                           | Power Management Controller supply voltage <sup>5</sup>  | _                                                       | -0.3 | 6.0   | V     |

| $V_{DDFLA}$                           | Decoupling pin for flash regulator <sup>6</sup>          | _                                                       | -0.3 | 4.5   | V     |

| V <sub>STBY</sub>                     | RAM standby supply voltage <sup>5</sup>                  | _                                                       | -0.3 | 6.0   | V     |

| V <sub>SSA_SD</sub>                   | SDADC ground voltage                                     | Reference to V <sub>SS</sub>                            | -0.3 | 0.3   | V     |

| V <sub>SSA_EQ</sub>                   | eQADC ground voltage                                     | Reference to V <sub>SS</sub>                            | -0.3 | 0.3   | V     |

| V <sub>DDA_EQA/B</sub>                | eQADC supply voltage                                     | Reference to V <sub>SSA_EQ</sub>                        | -0.3 | 6.0   | V     |

| $V_{DDA\_SD}$                         | SDADC supply voltage                                     | Reference to V <sub>SSA_SD</sub>                        | -0.3 | 6.0   | V     |

| $V_{RL\_SD}$                          | SDADC ground reference                                   | Reference to V <sub>SS</sub>                            | -0.3 | 0.3   | V     |

| $V_{RL_EQ}$                           | eQADC ground reference                                   | Reference to V <sub>SS</sub>                            | -0.3 | 0.3   | V     |

| $V_{RH\_EQ}$                          | eQADC alternate reference                                | Reference to V <sub>RL_EQ</sub>                         | -0.3 | 6.0   | V     |

| V <sub>RH_SD</sub>                    | SDADC alternate reference                                | Reference to V <sub>RL_SD</sub>                         | -0.3 | 6.0   | V     |

| V <sub>REFBYPC</sub>                  | eQADC reference decoupling capacitor pins                | REFBYPCA25, REFBYPCA75,<br>REFBYPCB25, REFBYPC75        | -0.3 | 6.0   | V     |

| V <sub>DDA_MISC</sub>                 | TRNG and IRC supply voltage                              | _                                                       | -0.3 | 6.0   | V     |

| $V_{DDPWR}$                           | SMPS driver supply pin                                   | _                                                       | -0.3 | 6.0   | V     |

| V <sub>SSPWR</sub>                    | SMPS driver supply pin                                   | Reference to V <sub>SS</sub>                            | -0.3 | 0.3   | V     |

| V <sub>SS</sub> – V <sub>SSA_EQ</sub> | V <sub>SSA_EQ</sub> differential voltage                 | _                                                       | -0.3 | 0.3   | V     |

| V <sub>SS</sub> – V <sub>SSA_SD</sub> | V <sub>SSA_SD</sub> differential voltage                 | _                                                       | -0.3 | 0.3   | V     |

| V <sub>SS</sub> – V <sub>RL_EQ</sub>  | V <sub>RL_EQ</sub> differential voltage                  | _                                                       | -0.3 | 0.3   | V     |

| V <sub>SS</sub> – V <sub>RL_SD</sub>  | V <sub>RL_SD</sub> differential voltage                  | _                                                       | -0.3 | 0.3   | V     |

| V <sub>IN</sub>                       | I/O input voltage range <sup>7</sup>                     | _                                                       | -0.3 | 6.0   | V     |

|                                       |                                                          | Relative to V <sub>DDEx</sub> /V <sub>DDEHx</sub>       | _    | 0.3   | V     |

|                                       |                                                          | Relative to V <sub>SS</sub>                             | -0.3 | _     | V     |

| I <sub>INJD</sub>                     | Maximum DC injection current for digital pad             | Per pin, applies to all digital pins                    | -5   | 5     | mA    |

| I <sub>INJA</sub>                     | Maximum DC injection current for analog pad              | Per pin, applies to all analog pins                     | -5   | 5     | mA    |

| I <sub>MAXSEG</sub> <sup>8, 9</sup>   | Maximum current per I/O power segment                    | _                                                       | -120 | 120   | mA    |

| T <sub>STG</sub>                      | Storage temperature range and non-<br>operating times    | _                                                       | -55  | 175   | °C    |

| STORAGE                               | Maximum storage time, assembled part programmed in ECU   | No supply; storage temperature in range –40 °C to 60 °C | _    | 20    | years |

| T <sub>SDR</sub>                      | Maximum solder temperature <sup>10</sup> Pb-free package | _                                                       | _    | 260   | °C    |

Table 1. Absolute maximum ratings (continued)

| Symbol |        | Parameter                                | Conditions <sup>1</sup> | Va  | lue | Unit |

|--------|--------|------------------------------------------|-------------------------|-----|-----|------|

|        | Symbol | Faranielei                               | Conditions              | Min | Max |      |

|        | MSL    | Moisture sensitivity level <sup>11</sup> | _                       | _   | 3   | _    |

- 1. Voltages are referred to V<sub>SS</sub> if not specified otherwise

- 2. Allowed 1.45 V 1.5 V for 60 seconds cumulative time at maximum  $T_J = 150$  °C; remaining time as defined in note 3 and note 4

- 3. Allowed 1.375 V 1.45 V for 10 hours cumulative time at maximum T<sub>J</sub> = 150 °C; remaining time as defined in note 4

- 4. 1.32 V 1.375 V range allowed periodically for supply with sinusoidal shape and average supply value below 1.275 V at maximum T<sub>.I</sub> = 150 °C

- 5. Allowed 5.5 V 6.0 V for 60 seconds cumulative time with no restrictions, for 10 hours cumulative time device in reset, T<sub>J</sub> = 150 °C; remaining time at or below 5.5 V

- 6. Allowed 3.6 V 4.5 V for 60 seconds cumulative time with no restrictions, for 10 hours cumulative time device in reset,  $T_J$  = 150 °C; remaining time at or below 3.6 V

- 7. The maximum input voltage on an I/O pin tracks with the associated I/P supply maximum. For the injection current condition on a pin, the voltage will be equal to the supply plus the voltage drop across the internal ESD diode from I/O pin to supply. The diode voltage varies greatly across process and temperature, but a value of 0.3V can be used for nominal calculations.

- 8. The sum of all controller pins (including both digital and analog) must not exceed 200 mA. A V<sub>DDEx</sub>/V<sub>DDEHx</sub> power segment is defined as one or more GPIO pins located between two V<sub>DDEx</sub>/V<sub>DDEHx</sub> supply pins.

- 9. The average current values given in I/O pad current specifications should be used to calculate total I/O segment current.

- 10. Solder profile per IPC/JEDEC J-STD-020D

- 11. Moisture sensitivity per JEDEC test method A112

# 3.2 Electromagnetic interference (EMI) characteristics

Test reports with EMC measurements to IC-level IEC standards are available on request.

To find application notes that provide guidance on designing your system to minimize interference from radiated emissions, go to nxp.com and perform a keyword search for "radiated emissions."

# 3.3 Electrostatic discharge (ESD) characteristics

Table 2. ESD Ratings<sup>1, 2</sup>

| Symbol           | Parameter                          | Conditions      | Value | Unit |

|------------------|------------------------------------|-----------------|-------|------|

| $V_{HBM}$        | ESD for Human Body Model (HBM)     | All pins        | 2000  | V    |

| V <sub>CDM</sub> | ESD for Charged Device Model (CDM) | Corner pins     | 750   | V    |

|                  |                                    | Non-corner pins | 500   |      |

- 1. All ESD testing is in conformity with CDF-AEC-Q100 Stress Test Qualification for Automotive Grade Integrated Circuits.

- A device will be defined as a failure if after exposure to ESD pulses the device no longer meets the device specification requirements.

MPC5777C Microcontroller Data Sheet Data Sheet, Rev. 11, 04/2017.

# 3.4 Operating conditions

The following table describes the operating conditions for the device, and for which all specifications in the data sheet are valid, except where explicitly noted.

If the device operating conditions are exceeded, the functionality of the device is not guaranteed.

Table 3. Device operating conditions

| 0 1 1                            |                                                                                | 0 - 100                                |        | Value |                      | Unit |

|----------------------------------|--------------------------------------------------------------------------------|----------------------------------------|--------|-------|----------------------|------|

| Symbol                           | Parameter                                                                      | Conditions                             | Min    | Тур   | Max                  | Unit |

|                                  |                                                                                | Frequency                              | •      |       | •                    | •    |

| f <sub>SYS</sub>                 | Device operating frequency <sup>1</sup>                                        | _                                      | _      | _     | 264 <sup>2</sup>     | MHz  |

| f <sub>PLATF</sub>               | Platform operating frequency                                                   | _                                      | _      | _     | 132                  | MHz  |

| f <sub>ETPU</sub>                | eTPU operating frequency                                                       | _                                      | _      | _     | 200                  | MHz  |

| f <sub>EBI</sub>                 | EBI operating frequency                                                        | _                                      | _      | _     | 66                   | MHz  |

| f <sub>PER</sub>                 | Peripheral block operating frequency                                           | _                                      | _      | _     | 132                  | MHz  |

| f <sub>FM_PER</sub>              | Frequency-modulated peripheral block operating frequency                       | _                                      | _      | _     | 132                  | MHz  |

| t <sub>CYC</sub>                 | Platform clock period                                                          | _                                      | 1 –    | _     | 1/f <sub>PLATF</sub> | ns   |

| t <sub>CYC_ETPU</sub>            | eTPU clock period                                                              | _                                      | 1 –    | _     | 1/f <sub>ETPU</sub>  | ns   |

| t <sub>CYC_PER</sub>             | Peripheral clock period                                                        | _                                      | T —    | _     | 1/f <sub>PER</sub>   | ns   |

|                                  |                                                                                | Temperature                            |        |       | 1                    | 1    |

| TJ                               | Junction operating temperature range                                           | Packaged devices                       | -40.0  | _     | 150.0                | °C   |

| $T_A$ ( $T_L$ to $T_H$ )         | Ambient operating temperature range                                            | Packaged devices                       | -40.0  | _     | 125.0 <sup>3</sup>   | °C   |

|                                  |                                                                                | Voltage                                |        |       |                      | _I   |

| $V_{DD}$                         | External core supply voltage <sup>4, 5</sup>                                   | LVD/HVD enabled                        | 1.2    | _     | 1.32                 | V    |

|                                  |                                                                                | LVD/HVD disabled <sup>6, 7, 8, 9</sup> | 1.2    | _     | 1.38                 |      |

| V <sub>DDA_MISC</sub>            | TRNG and IRC supply voltage                                                    | _                                      | 3.5    | _     | 5.5                  | V    |

| $V_{DDEx}$                       | I/O supply voltage (fast I/O pads)                                             | 5 V range                              | 4.5    | _     | 5.5                  | V    |

|                                  |                                                                                | 3.3 V range                            | 3.0    | _     | 3.6                  |      |

| V <sub>DDEHx</sub> 9             | I/O supply voltage (medium I/O                                                 | 5 V range                              | 4.5    | _     | 5.5                  | V    |

|                                  | pads)                                                                          | 3.3 V range                            | 3.0    | _     | 3.6                  |      |

| V <sub>DDEH1</sub>               | eTPU_A, eSCI_A, eSCI_B, and configuration I/O supply voltage (medium I/O pads) | 5 V range                              | 4.5    | _     | 5.5                  | V    |

| V <sub>DDPMC</sub> <sup>10</sup> | Power Management Controller (PMC) supply voltage                               | Full functionality                     | 3.15   | _     | 5.5                  | V    |

| $V_{DDPWR}$                      | SMPS driver supply voltage                                                     | Reference to V <sub>SSPWR</sub>        | 3.0    | _     | 5.5                  | V    |

| $V_{DDFLA}$                      | Flash core voltage                                                             | _                                      | 3.15   | _     | 3.6                  | V    |

| V <sub>STBY</sub>                | RAM standby supply voltage                                                     | _                                      | 0.9511 | _     | 5.5                  | V    |

Table continues on the next page...

Table 3. Device operating conditions (continued)

| Combal                                         | Parameter                                            | Conditions                   |                     | Value               |                   |      |  |

|------------------------------------------------|------------------------------------------------------|------------------------------|---------------------|---------------------|-------------------|------|--|

| Symbol                                         | Parameter                                            | Conditions                   | Min                 | Тур Мах             |                   | Unit |  |

| V <sub>STBY_BO</sub>                           | Standby RAM brownout flag trip point voltage         | _                            | _                   | _                   | 0.9 <sup>12</sup> | V    |  |

| V <sub>RL_SD</sub>                             | SDADC ground reference voltage                       | _                            | V <sub>SSA_SD</sub> |                     |                   | V    |  |

| V <sub>DDA_SD</sub>                            | SDADC supply voltage <sup>13</sup>                   | _                            | 4.5                 | _                   | 5.5               | V    |  |

| V <sub>DDA_EQA/B</sub>                         | eQADC supply voltage                                 | _                            | 4.75                | _                   | 5.25              | V    |  |

| $V_{RH\_SD}$                                   | SDADC reference                                      | _                            | 4.5                 | V <sub>DDA_SD</sub> | 5.5               | V    |  |

| V <sub>DDA_SD</sub> – V <sub>RH_SD</sub>       | SDADC reference differential voltage                 | _                            | _                   | _                   | 25                | mV   |  |

| V <sub>SSA_SD</sub> – V <sub>RL_SD</sub>       | V <sub>RL_SD</sub> differential voltage              | _                            | -25                 | _                   | 25                | mV   |  |

| $V_{RH\_EQ}$                                   | eQADC reference                                      | _                            | 4.75                | _                   | 5.25              | V    |  |

| V <sub>DDA_EQA/B</sub> –<br>V <sub>RH_EQ</sub> | eQADC reference differential voltage                 | _                            | _                   | _                   | 25                | mV   |  |

| V <sub>SSA_EQ</sub> – V <sub>RL_EQ</sub>       | V <sub>RL_EQ</sub> differential voltage              | _                            | -25                 | _                   | 25                | mV   |  |

| V <sub>SSA_EQ</sub> – V <sub>SS</sub>          | V <sub>SSA_EQ</sub> differential voltage             | _                            | -25                 | _                   | 25                | mV   |  |

| V <sub>SSA_SD</sub> – V <sub>SS</sub>          | V <sub>SSA_SD</sub> differential voltage             | _                            | -25                 | _                   | 25                | mV   |  |

| $V_{RAMP}$                                     | Slew rate on power supply pins                       | _                            | <u> </u>            | _                   | 100               | V/ms |  |

|                                                |                                                      | Current                      |                     | •                   |                   | '    |  |

| I <sub>IC</sub>                                | DC injection current (per pin) <sup>14,</sup> 15, 16 | Digital pins and analog pins | -3.0                | _                   | 3.0               | mA   |  |

| I <sub>MAXSEG</sub>                            | Maximum current per power segment <sup>17, 18</sup>  | _                            | -80                 | _                   | 80                | mA   |  |

- Maximum operating frequency is applicable to the computational cores and platform for the device. See the Clocking chapter in the MPC5777C Microcontroller Reference Manual for more information on the clock limitations for the various IP blocks on the device.

- 2. If frequency modulation (FM) is enabled, the maximum frequency still cannot exceed this value.

- The maximum specification for operating junction temperature T<sub>J</sub> must be respected. Thermal characteristics provides details.

- 4. Core voltage as measured on device pin to guarantee published silicon performance

- 5. During power ramp, voltage measured on silicon might be lower. Maximum performance is not guaranteed, but correct silicon operation is guaranteed. See power management and reset management for description.

- 6. Maximum core voltage is not permitted for entire product life. See absolute maximum rating.

- 7. When internal LVD/HVDs are disabled, external monitoring is required to guarantee device operation. Failure to monitor externally supply voltage may result in erroneous operation of the device.

- 8. This LVD/HVD disabled supply voltage condition only applies after LVD/HVD are disabled by the application during the reset sequence, and the LVD/HVD are active until that point.

- 9. This spec does not apply to V<sub>DDEH1</sub>.

- 10. When internal flash memory regulator is used:

- Flash memory read operation is supported for a minimum  $V_{DDPMC}$  value of 3.15 V.

- Flash memory read, program, and erase operations are supported for a minimum V<sub>DDPMC</sub> value of 3.5 V.

When flash memory power is supplied externally (V<sub>DDPMC</sub> shorted to V<sub>DDFLA</sub>): The V<sub>DDPMC</sub> range must be within the limits specified for LVD\_FLASH and HVD\_FLASH monitoring. Table 29 provides the monitored LVD\_FLASH and HVD\_FLASH limits

- 11. If the standby RAM regulator is not used, the V<sub>STBY</sub> supply input pin must be tied to ground.

- 12. V<sub>STBY\_BO</sub> is the maximum voltage that sets the standby RAM brownout flag in the device logic. The minimum voltage for RAM data retention is guaranteed always to be less than the V<sub>STBY\_BO</sub> maximum value.

#### MPC5777C Microcontroller Data Sheet Data Sheet, Rev. 11, 04/2017.

- 13. For supply voltages between 3.0 V and 4.0 V there will be no guaranteed precision of ADC (accuracy/linearity). ADC will recover to a fully functional state when the voltage rises above 4.0 V.

- 14. Full device lifetime without performance degradation

- 15. I/O and analog input specifications are only valid if the injection current on adjacent pins is within these limits. See the absolute maximum ratings table for maximum input current for reliability requirements.

- 16. The I/O pins on the device are clamped to the I/O supply rails for ESD protection. When the voltage of the input pin is above the supply rail, current will be injected through the clamp diode to the supply rail. For external RC network calculation, assume a typical 0.3 V drop across the active diode. The diode voltage drop varies with temperature.

- 17. The sum of all controller pins (including both digital and analog) must not exceed 200 mA. A V<sub>DDEX</sub>/V<sub>DDEHx</sub> power segment is defined as one or more GPIO pins located between two V<sub>DDEX</sub>/V<sub>DDEHx</sub> supply pins.

- 18. The average current values given in I/O pad current specifications should be used to calculate total I/O segment current.

# 3.5 DC electrical specifications

#### NOTE

$I_{DDA\_MISC}$  is the sum of current consumption of IRC,  $I_{TRNG}$ , and  $I_{STBY}$  in the 5 V domain. IRC current is provided in the IRC specifications.

#### NOTE

I/O, XOSC, EQADC, SDADC, and Temperature Sensor current specifications are in those components' dedicated sections.

Table 4. DC electrical specifications

| Cumbal              | Parameter                                                                             | Conditions                                          |     | Value |      | Unit |

|---------------------|---------------------------------------------------------------------------------------|-----------------------------------------------------|-----|-------|------|------|

| Symbol              | Farameter                                                                             | Conditions                                          | Min | Тур   | Max  |      |

| I <sub>DD</sub>     | Operating current on the V <sub>DD</sub> core logic supply <sup>1</sup>               | LVD/HVD enabled, V <sub>DD</sub> = 1.2 V to 1.32 V  | _   | 0.65  | 1.35 | Α    |

|                     |                                                                                       | LVD/HVD disabled, V <sub>DD</sub> = 1.2 V to 1.38 V | _   | 0.65  | 1.4  |      |

| I <sub>DD_PE</sub>  | Operating current on the V <sub>DD</sub> supply for flash memory program/erase        | _                                                   | _   | _     | 85   | mA   |

| I <sub>DDPMC</sub>  | Operating current on the V <sub>DDPMC</sub> supply <sup>2</sup>                       | Flash memory read                                   | _   | _     | 40   | mA   |

|                     |                                                                                       | Flash memory program/erase                          | _   | _     | 70   |      |

|                     |                                                                                       | PMC only                                            | _   | _     | 35   |      |

|                     | Operating current on the V <sub>DDPMC</sub> supply (internal core regulator bypassed) | Flash memory read                                   | _   | _     | 10   | mA   |

|                     |                                                                                       | Flash memory program/erase                          | _   | _     | 40   |      |

|                     |                                                                                       | PMC only                                            | _   | _     | 5    | ]    |

| I <sub>REGCTL</sub> | Core regulator DC current output on V <sub>REGCTL</sub> pin                           | _                                                   | _   | _     | 25   | mA   |

| I <sub>STBY</sub>   | Standby RAM supply current (T <sub>J</sub> = 150°C)                                   | 1.08 V                                              | _   | _     | 1140 | μΑ   |

|                     |                                                                                       | 1.25 V to 5.5 V                                     | _   | _     | 1170 | ]    |

| I <sub>DD_PWR</sub> | Operating current on the V <sub>DDPWR</sub> supply                                    | _                                                   | _   | _     | 50   | mA   |

| I <sub>BG_REF</sub> | Bandgap reference current consumption <sup>3</sup>                                    |                                                     | _   | _     | 600  | μΑ   |

| I <sub>TRNG</sub>   | True Random Number Generator current                                                  | _                                                   | _   | _     | 2.1  | mA   |

- I<sub>DD</sub> measured on an application-specific pattern with all cores enabled at full frequency, T<sub>J</sub> = 40°C to 150°C. Flash memory program/erase current on the V<sub>DD</sub> supply not included.

- This value is considering the use of the internal core regulator with the simulation of an external transistor with the minimum value of h<sub>FE</sub> of 60.

- 3. This bandgap reference is for EQADC calibration and Temperature Sensors.

# 3.6 I/O pad specifications

The following table describes the different pad types on the chip.

Table 5. I/O pad specification descriptions

| Pad type                 | Description                                                                                                                      |

|--------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| General-purpose I/O pads | General-purpose I/O and EBI data bus pads with four selectable output slew rate settings; also called SR pads                    |

| EBI pads                 | Provide necessary speed for fast external memory interfaces on the EBI CLKOUT, address, and control signals; also called FC pads |

| LVDS pads                | Low Voltage Differential Signal interface pads                                                                                   |

| Input-only pads          | Low-input-leakage pads that are associated with the ADC channels                                                                 |

#### NOTE

Each I/O pin on the device supports specific drive configurations. See the signal description table in the device reference manual for the available drive configurations for each I/O pin.

#### NOTE

Throughout the I/O pad specifications, the symbol  $V_{DDEx}$  represents all  $V_{DDEx}$  and  $V_{DDEHx}$  segments.

### 3.6.1 Input pad specifications

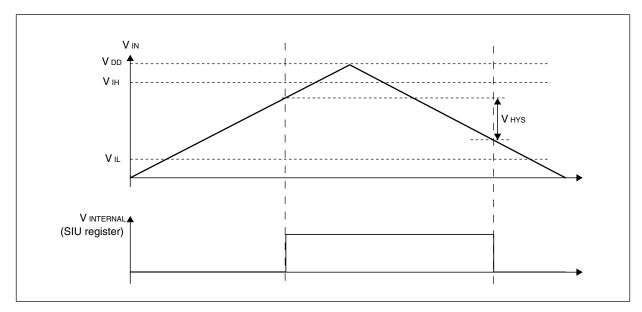

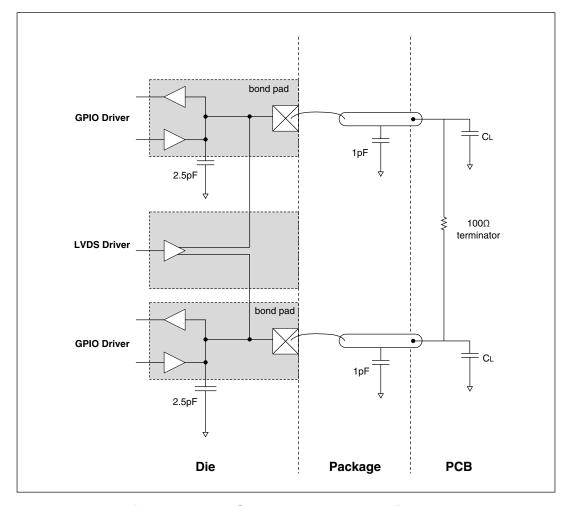

Table 6 provides input DC electrical characteristics as described in Figure 4.

MPC5777C Microcontroller Data Sheet Data Sheet, Rev. 11, 04/2017.

Figure 4. I/O input DC electrical characteristics definition

Table 6. I/O input DC electrical characteristics

| Cumbal                | Davamatar                                                 | Conditions                                                                       |                          | Value |                          | Unit |

|-----------------------|-----------------------------------------------------------|----------------------------------------------------------------------------------|--------------------------|-------|--------------------------|------|

| Symbol                | Parameter                                                 | Conditions                                                                       | Min                      | Тур   | Max                      | Unit |

| V <sub>IHCMOS_H</sub> | Input high level CMOS (with                               | 3.0 V < V <sub>DDEx</sub> < 3.6 V and                                            | 0.65 * V <sub>DDEx</sub> | _     | $V_{DDEx} + 0.3$         | V    |

|                       | hysteresis)                                               | 4.5 V < V <sub>DDEx</sub> < 5.5 V                                                |                          |       |                          |      |

| V <sub>IHCMOS</sub>   | Input high level CMOS (without                            | 3.0 V < V <sub>DDEx</sub> < 3.6 V and                                            | 0.55 * V <sub>DDEx</sub> | _     | $V_{DDEx} + 0.3$         | V    |

|                       | hysteresis)                                               | 4.5 V < V <sub>DDEx</sub> < 5.5 V                                                |                          |       |                          |      |

| V <sub>ILCMOS_H</sub> | Input low level CMOS (with                                | 3.0 V < V <sub>DDEx</sub> < 3.6 V and                                            | -0.3                     | _     | 0.35 * V <sub>DDEx</sub> | V    |

|                       | hysteresis)                                               | $4.5 \text{ V} < \text{V}_{\text{DDEx}} < 5.5 \text{ V}$                         |                          |       |                          |      |

| V <sub>ILCMOS</sub>   | Input low level CMOS (without                             | 3.0 V < V <sub>DDEx</sub> < 3.6 V and                                            | -0.3                     | _     | 0.4 * V <sub>DDEx</sub>  | V    |

|                       | hysteresis)                                               | $4.5 \text{ V} < \text{V}_{\text{DDEx}} < 5.5 \text{ V}$                         |                          |       |                          |      |

| V <sub>HYSCMOS</sub>  | Input hysteresis CMOS                                     | $3.0 \text{ V} < \text{V}_{\text{DDEx}} < 3.6 \text{ V} \text{ and}$             | 0.1 * V <sub>DDEx</sub>  | _     | _                        | V    |

|                       |                                                           | $4.5 \text{ V} < \text{V}_{\text{DDEx}} < 5.5 \text{ V}$                         |                          |       |                          |      |

|                       |                                                           | Input Characteristics <sup>1</sup>                                               |                          |       |                          |      |

| I <sub>LKG</sub>      | Digital input leakage                                     | $V_{SS} < V_{IN} < V_{DDEx}/V_{DDEHx}$                                           | _                        | _     | 2.5                      | μΑ   |

| I <sub>LKG_FAST</sub> | Digital input leakage for EBI address/control signal pads | $V_{SS} < V_{IN} < V_{DDEx}/V_{DDEHx}$                                           | _                        | _     | 2.5                      | μΑ   |

| I <sub>LKGA</sub>     | Analog pin input leakage (5 V range)                      | $V_{SSA\_SD} < V_{IN} < V_{DDA\_SD},$<br>$V_{SSA\_EQ} < V_{IN} < V_{DDA\_EQA/B}$ | _                        | _     | 220                      | nA   |

| C <sub>IN</sub>       | Digital input capacitance                                 | GPIO and EBI input pins                                                          | _                        | _     | 7                        | pF   |

<sup>1.</sup> For LFAST, microsecond bus, and LVDS input characteristics, see dedicated communication module sections.

Table 7 provides current specifications for weak pullup and pulldown.

Table 7. I/O pullup/pulldown DC electrical characteristics

| Symbol           | Parameter             | Conditions                                               |     | Value |     |      |  |

|------------------|-----------------------|----------------------------------------------------------|-----|-------|-----|------|--|

| Syllibol         | raiaillelei           | Conditions                                               | Min | Тур   | Max | Unit |  |

| I <sub>WPU</sub> | Weak pullup current   | $V_{IN} = 0.35 * V_{DDEx}$                               | 40  | _     | 120 | μA   |  |

|                  |                       | $4.5 \text{ V} < \text{V}_{\text{DDEx}} < 5.5 \text{ V}$ |     |       |     |      |  |

|                  |                       | V <sub>IN</sub> = 0.35 * V <sub>DDEx</sub>               | 25  | _     | 80  |      |  |

|                  |                       | $3.0 \text{ V} < \text{V}_{\text{DDEx}} < 3.6 \text{ V}$ |     |       |     |      |  |

| I <sub>WPD</sub> | Weak pulldown current | V <sub>IN</sub> = 0.65 * V <sub>DDEx</sub>               | 40  | _     | 120 | μA   |  |

|                  |                       | $4.5 \text{ V} < \text{V}_{\text{DDEx}} < 5.5 \text{ V}$ |     |       |     |      |  |

|                  |                       | V <sub>IN</sub> = 0.65 * V <sub>DDEx</sub>               | 25  | _     | 80  |      |  |

|                  |                       | $3.0 \text{ V} < \text{V}_{\text{DDEx}} < 3.6 \text{ V}$ |     |       |     |      |  |

The specifications in Table 8 apply to the pins ANA0\_SDA0 to ANA7, ANA16\_SDB0 to ANA23\_SDC3, and ANB0\_SDD0 to ANB7\_SDD7.

Table 8. I/O pullup/pulldown resistance electrical characteristics

| Symbol            | Parameter                                             | Conditions |     | Unit |     |    |

|-------------------|-------------------------------------------------------|------------|-----|------|-----|----|

| Symbol            |                                                       | Conditions | Min | Тур  | Max | 5  |

| R <sub>PUPD</sub> | Analog input bias / diagnostic pullup/                | 200 kΩ     | 130 | 200  | 280 | kΩ |

|                   | pulldown resistance                                   | 100 kΩ     | 65  | 100  | 140 |    |

|                   |                                                       | 5 kΩ       | 1.4 | 5    | 7.5 |    |

| $\Delta_{PUPD}$   | R <sub>PUPD</sub> pullup/pulldown resistance mismatch | _          | _   | _    | 5   | %  |

# 3.6.2 Output pad specifications

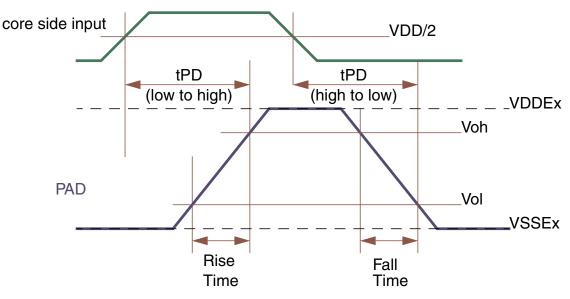

Figure 5 shows output DC electrical characteristics.

Figure 5. I/O output DC electrical characteristics definition

The following tables specify output DC electrical characteristics.

Table 9. GPIO and EBI data pad output buffer electrical characteristics (SR pads)<sup>1</sup>

| Symbol          | Parameter Conditions <sup>2</sup> |                                                          |                       |      | Value <sup>3</sup> |     | Unit |

|-----------------|-----------------------------------|----------------------------------------------------------|-----------------------|------|--------------------|-----|------|

| Symbol          | Farameter                         | Conditions                                               |                       | Min  | Тур                | Max |      |

| I <sub>OH</sub> | GPIO pad output high              | V <sub>OH</sub> = 0.8 * V <sub>DDEx</sub>                | PCR[SRC] = 11b or 01b | 25   | _                  | _   | mA   |

|                 | current                           | $4.5 \text{ V} < \text{V}_{\text{DDEx}} < 5.5 \text{ V}$ | PCR[SRC] = 10b or 00b | 15   | _                  | _   |      |

|                 |                                   | $V_{OH} = 0.8 * V_{DDEx}$                                | PCR[SRC] = 11b or 01b | 13   | _                  | _   |      |

|                 |                                   | $3.0 \text{ V} < \text{V}_{\text{DDEx}} < 3.6 \text{ V}$ | PCR[SRC] = 10b or 00b | 8    | _                  | _   |      |

| I <sub>OL</sub> | GPIO pad output low               | V <sub>OL</sub> = 0.2 * V <sub>DDEx</sub>                | PCR[SRC] = 11b or 01b | 48   | _                  | _   | mA   |

|                 | current                           | $4.5 \text{ V} < \text{V}_{\text{DDEx}} < 5.5 \text{ V}$ | PCR[SRC] = 10b or 00b | 22   | _                  | _   |      |

|                 |                                   | $V_{OL} = 0.2 * V_{DDEx}$                                | PCR[SRC] = 11b or 01b | 17   | _                  | _   |      |

|                 |                                   | $3.0 \text{ V} < \text{V}_{\text{DDEx}} < 3.6 \text{ V}$ | PCR[SRC] = 10b or 00b | 10.5 | _                  | _   |      |

Table 9. GPIO and EBI data pad output buffer electrical characteristics (SR pads)<sup>1</sup> (continued)

| Symbol Boro         | Parameter                                   | Conditions <sup>2</sup>                                  |                         |   | Value <sup>3</sup> |      | Un   |

|---------------------|---------------------------------------------|----------------------------------------------------------|-------------------------|---|--------------------|------|------|

| Symbol              | raiailletei                                 | Conditions*                                              | Conditions              |   | Тур                | Max  | ] Un |

| t <sub>R_F</sub>    | GPIO pad output                             | PCR[SRC] = 11b                                           | C <sub>L</sub> = 25 pF  | _ | _                  | 1.2  | ns   |

|                     | GPIO pad output transition time (rise/fall) | 4.5 V < V <sub>DDEx</sub> < 5.5 V                        | C <sub>L</sub> = 50 pF  | _ |                    | 2.5  |      |

|                     |                                             |                                                          | C <sub>L</sub> = 200 pF | _ | _                  | 8    |      |

|                     |                                             | PCR[SRC] = 11b                                           | C <sub>L</sub> = 25 pF  | _ | _                  | 1.7  |      |

|                     |                                             | $3.0 \text{ V} < \text{V}_{\text{DDEx}} < 3.6 \text{ V}$ | C <sub>L</sub> = 50 pF  | _ | _                  | 3.25 |      |

|                     |                                             |                                                          | C <sub>L</sub> = 200 pF | _ | _                  | 12   |      |

|                     |                                             | PCR[SRC] = 10b                                           | C <sub>L</sub> = 50 pF  | _ | _                  | 5    |      |

|                     |                                             | 4.5 V < V <sub>DDEx</sub> < 5.5 V                        | C <sub>L</sub> = 200 pF | _ | _                  | 18   |      |

|                     |                                             | PCR[SRC] = 10b                                           | C <sub>L</sub> = 50 pF  |   | _                  | 7    |      |

|                     |                                             | $3.0 \text{ V} < \text{V}_{\text{DDEx}} < 3.6 \text{ V}$ | C <sub>L</sub> = 200 pF | _ | _                  | 25   |      |

|                     |                                             |                                                          | C <sub>L</sub> = 50 pF  | _ | _                  | 13   |      |

|                     |                                             | 4.5 V < V <sub>DDEx</sub> < 5.5 V                        | C <sub>L</sub> = 200 pF | _ | _                  | 24   |      |

|                     |                                             |                                                          | C <sub>L</sub> = 50 pF  |   | _                  | 25   |      |

|                     |                                             | $3.0 \text{ V} < \text{V}_{\text{DDEx}} < 3.6 \text{ V}$ | C <sub>L</sub> = 200 pF | _ | _                  | 30   |      |

|                     |                                             |                                                          | C <sub>L</sub> = 50 pF  | _ | _                  | 24   |      |

|                     |                                             | 4.5 V < V <sub>DDEx</sub> < 5.5 V                        | C <sub>L</sub> = 200 pF | _ | _                  | 50   |      |

|                     |                                             |                                                          | C <sub>L</sub> = 50 pF  | _ | _                  | 40   |      |

|                     |                                             | 3.0 V < V <sub>DDEx</sub> < 3.6 V                        | C <sub>L</sub> = 200 pF | _ | _                  | 51   |      |

| t <sub>PD</sub>     | GPIO pad output                             |                                                          | C <sub>L</sub> = 50 pF  | _ | _                  | 6    | n    |

|                     | propagation delay time                      | 4.5 V < V <sub>DDEx</sub> < 5.5 V                        | C <sub>L</sub> = 200 pF | _ | _                  | 13   |      |

|                     |                                             |                                                          | C <sub>L</sub> = 50 pF  | _ | _                  | 8.25 |      |

|                     |                                             | $3.0 \text{ V} < \text{V}_{\text{DDEx}} < 3.6 \text{ V}$ | C <sub>L</sub> = 200 pF |   | _                  | 19.5 |      |

|                     |                                             |                                                          | C <sub>L</sub> = 50 pF  | _ | _                  | 9    |      |

|                     |                                             | 4.5 V < V <sub>DDEx</sub> < 5.5 V                        | C <sub>L</sub> = 200 pF |   | _                  | 22   |      |

|                     |                                             |                                                          | C <sub>L</sub> = 50 pF  | _ | _                  | 12.5 |      |

|                     |                                             | $3.0 \text{ V} < \text{V}_{\text{DDEx}} < 3.6 \text{ V}$ | C <sub>L</sub> = 200 pF |   | _                  | 35   |      |

|                     |                                             | PCR[SRC] = 01b                                           | C <sub>L</sub> = 50 pF  | _ |                    | 27   |      |

|                     |                                             | 4.5 V < V <sub>DDEx</sub> < 5.5 V                        | C <sub>L</sub> = 200 pF | _ | _                  | 40   |      |

|                     |                                             | PCR[SRC] = 01b                                           | C <sub>L</sub> = 50 pF  | _ | _                  | 45   |      |

|                     |                                             | 3.0 V < V <sub>DDEx</sub> < 3.6 V                        |                         | _ | _                  | 65   |      |

|                     |                                             | PCR[SRC] = 00b                                           | C <sub>L</sub> = 50 pF  | _ | _                  | 40   |      |

|                     |                                             | 4.5 V < V <sub>DDEx</sub> < 5.5 V                        | -                       | _ | _                  | 65   | 1    |

|                     |                                             | PCR[SRC] = 00b                                           | C <sub>L</sub> = 50 pF  |   | _                  | 75   | 1    |

|                     |                                             | 3.0 V < V <sub>DDEx</sub> < 3.6 V                        |                         | _ | _                  | 100  |      |

| t <sub>SKEW_W</sub> | Difference between rise and fall time       | _                                                        | <u>.</u>                | _ | _                  | 25   | 9,   |

<sup>1.</sup> All GPIO pad output specifications are valid for 3.0 V <  $V_{DDEx}$  < 5.5 V, except where explicitly stated.

- 2. PCR[SRC] values refer to the setting of that register field in the SIU.

- 3. All values to be confirmed during device validation.

The following table shows the EBI CLKOUT, address, and control signal pad electrical characteristics. These pads can also be used for GPIO.

Table 10. GPIO and EBI CLKOUT, address, and control signal pad output buffer electrical characteristics (FC pads)

| Cumbal               | Donomotor                                | Conditions1                                              |                         |                           | Value |      | l lm!± |

|----------------------|------------------------------------------|----------------------------------------------------------|-------------------------|---------------------------|-------|------|--------|

| Symbol               | Parameter                                | Conditions <sup>1</sup>                                  |                         | Min                       | Тур   | Max  | Unit   |

|                      | EBI Mod                                  | e Output Specification                                   | ns: valid for 3.0 V < \ | / <sub>DDEx</sub> < 3.6 V | ,     |      |        |

| C <sub>DRV</sub>     | External bus load                        | PCR[DSC] = 01b                                           |                         | _                         | _     | 10   | pF     |

|                      | capacitance                              | PCR[DSC] = 10b                                           |                         | _                         | _     | 20   |        |

|                      |                                          | PCR[DSC] = 11b                                           |                         | _                         | _     | 30   | 1      |

| f <sub>MAX_EBI</sub> | External bus maximum operating frequency | $C_{DRV} = 10/20/30 \text{ pF}$                          |                         | _                         | _     | 66   | MHz    |

|                      | 1                                        | GPIO and EBI Mode                                        | Output Specification    | ns                        | -     |      | ļ      |

| I <sub>OH_EBI</sub>  | GPIO and external bus                    | $V_{OH} = 0.8 * V_{DDEx}$                                | PCR[DSC] = 11b          | 30                        | _     | _    | mA     |

|                      | pad output high current                  | 4.5 V < V <sub>DDEx</sub> < 5.5 V                        | PCR[DSC] = 10b          | 22                        | _     | _    |        |

|                      |                                          |                                                          | PCR[DSC] = 01b          | 13                        | _     | _    |        |

|                      |                                          |                                                          | PCR[DSC] = 00b          | 2                         | _     | _    | 1      |

|                      |                                          | V <sub>OH</sub> = 0.8 * V <sub>DDEx</sub>                | PCR[DSC] = 11b          | 16                        | _     | _    |        |

|                      |                                          | $3.0 \text{ V} < \text{V}_{\text{DDEx}} < 3.6 \text{ V}$ | PCR[DSC] = 10b          | 12                        | _     | _    |        |

|                      |                                          |                                                          | PCR[DSC] = 01b          | 7                         | _     | _    | 1      |

|                      |                                          |                                                          | PCR[DSC] = 00b          | 1                         |       | _    | 1      |

| I <sub>OL_EBI</sub>  | GPIO and external bus                    | $V_{OL} = 0.2 * V_{DDEx}$                                | PCR[DSC] = 11b          | 54                        | _     | _    | mA     |

|                      | pad output low current                   | 4.5 V < V <sub>DDEx</sub> < 5.5 V                        | PCR[DSC] = 10b          | 25                        | _     | _    |        |

|                      |                                          |                                                          | PCR[DSC] = 01b          | 16                        | _     | _    | 1      |

|                      |                                          |                                                          | PCR[DSC] = 00b          | 2                         | _     | _    |        |

|                      |                                          | V <sub>OL</sub> = 0.2 * V <sub>DDEx</sub>                | PCR[DSC] = 11b          | 17                        | _     | _    |        |

|                      |                                          | $3.0 \text{ V} < \text{V}_{\text{DDEx}} < 3.6 \text{ V}$ | PCR[DSC] = 10b          | 14                        | _     | _    |        |

|                      |                                          |                                                          | PCR[DSC] = 01b          | 8                         | _     | _    |        |

|                      |                                          |                                                          | PCR[DSC] = 00b          | 1                         | _     | _    |        |

| t <sub>R_F_EBI</sub> | GPIO and external bus                    | PCR[DSC] = 11b                                           | C <sub>L</sub> = 30 pF  | _                         | _     | 1.5  | ns     |

|                      | pad output transition time (rise/fall)   |                                                          | C <sub>L</sub> = 50 pF  | _                         | _     | 2.4  |        |

|                      | time (nse/iaii)                          | PCR[DSC] = 10b                                           | C <sub>L</sub> = 20 pF  | _                         | _     | 1.5  |        |

|                      |                                          | PCR[DSC] = 01b                                           | C <sub>L</sub> = 10 pF  | -                         | _     | 1.85 |        |

|                      |                                          | PCR[DSC] = 00b                                           | C <sub>L</sub> = 50 pF  | _                         | _     | 45   |        |

| t <sub>PD_EBI</sub>  | GPIO and external bus                    | PCR[DSC] = 11b                                           | C <sub>L</sub> = 30 pF  | _                         | _     | 4.2  | ns     |

|                      | pad output propagation                   |                                                          | C <sub>L</sub> = 50 pF  | _                         | _     | 5.5  | 1      |

|                      | delay time                               | PCR[DSC] = 10b                                           | C <sub>L</sub> = 20 pF  | _                         | _     | 4.2  | 1      |

|                      |                                          | PCR[DSC] = 01b                                           | C <sub>L</sub> = 10 pF  | _                         | _     | 4.4  | 1      |

|                      |                                          | PCR[DSC] = 00b                                           | C <sub>L</sub> = 50 pF  | <u> </u>                  |       | 59   | 1      |

1. PCR[DSC] values refer to the setting of that register field in the SIU.

### 3.6.3 I/O pad current specifications

The I/O pads are distributed across the I/O supply segments. Each I/O supply segment is associated with a  $V_{DDEx}$  supply segment.

Table 11 provides I/O consumption figures.

To ensure device reliability, the average current of the I/O on a single segment should remain below the  $I_{MAXSEG}$  value given in Table 1.

To ensure device functionality, the average current of the I/O on a single segment should remain below the  $I_{MAXSEG}$  value given in Table 3.

#### NOTE

The MPC5777C I/O Signal Description and Input Multiplexing Tables are contained in a Microsoft Excel® file attached to the Reference Manual. In the spreadsheet, select the I/O Signal Table tab.

| Symbol                | Parameter                         | Conditions                                          | Value |     |      | Unit |

|-----------------------|-----------------------------------|-----------------------------------------------------|-------|-----|------|------|

| Symbol                | raiailletei                       | Conditions                                          | Min   | Тур | Max  |      |

| I <sub>AVG_GPIO</sub> | Average I/O current for GPIO pads | C <sub>L</sub> = 25 pF, 2 MHz                       | _     | _   | 0.42 | mA   |

|                       | (per pad)                         | $V_{DDEx} = 5.0 \text{ V} \pm 10\%$                 |       |     |      |      |

|                       |                                   | C <sub>L</sub> = 50 pF, 1 MHz                       | _     | _   | 0.35 |      |

|                       |                                   | $V_{DDEx} = 5.0 \text{ V} \pm 10\%$                 |       |     |      |      |

| I <sub>AVG_EBI</sub>  | Average I/O current for external  | C <sub>DRV</sub> = 10 pF, f <sub>EBI</sub> = 66 MHz | _     | _   | 9    | mA   |

|                       | bus output pins (per pad)         | $V_{DDEx} = 3.3 \text{ V} \pm 10\%$                 |       |     |      |      |

|                       |                                   | C <sub>DRV</sub> = 20 pF, f <sub>EBI</sub> = 66 MHz | _     | _   | 18   |      |

|                       |                                   | $V_{DDEx} = 3.3 \text{ V} \pm 10\%$                 |       |     |      |      |

|                       |                                   | C <sub>DRV</sub> = 30 pF, f <sub>EBI</sub> = 66 MHz | _     | _   | 30   |      |

|                       |                                   | $V_{DDEx} = 3.3 \text{ V} \pm 10\%$                 |       |     |      |      |

Table 11. I/O consumption

### 3.7 Oscillator and PLL electrical specifications

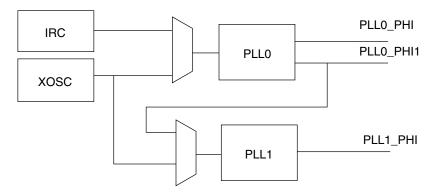

The on-chip dual PLL—consisting of the peripheral clock and reference PLL (PLL0) and the frequency-modulated system PLL (PLL1)—generates the system and auxiliary clocks from the main oscillator driver.

MPC5777C Microcontroller Data Sheet Data Sheet, Rev. 11, 04/2017.

Figure 6. PLL integration

# 3.7.1 PLL electrical specifications

Table 12. PLL0 electrical characteristics

| Symbol                  | Parameter                                 | Conditions                                                                 | Value |     |                  | Unit |

|-------------------------|-------------------------------------------|----------------------------------------------------------------------------|-------|-----|------------------|------|

| Symbol                  | Parameter                                 | Conditions                                                                 | Min   | Тур | Max              | Unit |

| f <sub>PLL0IN</sub>     | PLL0 input clock <sup>1, 2</sup>          | _                                                                          | 8     | _   | 44               | MHz  |

| $\Delta_{PLL0IN}$       | PLL0 input clock duty cycle <sup>2</sup>  | _                                                                          | 40    | _   | 60               | %    |

| f <sub>PLL0VCO</sub>    | PLL0 VCO frequency                        | _                                                                          | 600   | _   | 1250             | MHz  |

| f <sub>PLL0PHI</sub>    | PLL0 output frequency                     | _                                                                          | 4.762 | _   | 200              | MHz  |

| t <sub>PLL0LOCK</sub>   | PLL0 lock time                            | _                                                                          | _     | _   | 110              | μs   |

| $ \Delta_{PLL0PHISPJ} $ | PLL0_PHI single period jitter             | f <sub>PLL0PHI</sub> = 200 MHz, 6-sigma                                    | _     | _   | 200              | ps   |

|                         | f <sub>PLL0IN</sub> = 20 MHz (resonator)  |                                                                            |       |     |                  |      |

| \Delta PLLOPHI1SPJ      | PLL0_PHI1 single period jitter            | f <sub>PLL0PHI1</sub> = 40 MHz, 6-sigma                                    | _     | _   | 300 <sup>3</sup> | ps   |

|                         | f <sub>PLL0IN</sub> = 20 MHz (resonator)  |                                                                            |       |     |                  |      |

| $\Delta_{PLL0LTJ}$      | PLL0 output long term jitter <sup>3</sup> | 10 periods accumulated jitter (80 MHz                                      | _     | _   | ±250             | ps   |

|                         | f <sub>PLLOIN</sub> = 20 MHz (resonator), | equivalent frequency), 6-sigma pk-pk                                       |       |     |                  |      |

|                         | VCO frequency = 800 MHz                   | 16 periods accumulated jitter (50 MHz equivalent frequency), 6-sigma pk-pk | _     | _   | ±300             | ps   |

|                         |                                           | long term jitter (< 1 MHz equivalent frequency), 6-sigma pk-pk)            | _     | _   | ±500             | ps   |

| I <sub>PLL0</sub>       | PLL0 consumption                          | FINE LOCK state                                                            | _     | _   | 7.5              | mA   |

- f<sub>PLLOIN</sub> frequency must be scaled down using PLLDIG\_PLL0DV[PREDIV] to ensure PFD input signal is in the range 8 MHz to 20 MHz.

- 2. PLL0IN clock retrieved directly from either internal IRC or external XOSC clock. Input characteristics are granted when using internal IRC or external oscillator is used in functional mode.

- 3. Noise on the  $V_{DD}$  supply with frequency content below 40 kHz and above 50 MHz is filtered by the PLL. Noise on the  $V_{DD}$  supply with frequency content in the range of 40 kHz 50 MHz must be filtered externally to the device.

MPC5777C Microcontroller Data Sheet Data Sheet, Rev. 11, 04/2017.

Table 13. PLL1 electrical characteristics

| Cymbal                  | Parameter                                      | Conditions                                  |       | Unit |                  |      |

|-------------------------|------------------------------------------------|---------------------------------------------|-------|------|------------------|------|

| Symbol                  | Parameter                                      | Conditions                                  | Min   | Тур  | Max              | Unit |

| f <sub>PLL1IN</sub>     | PLL1 input clock <sup>1</sup>                  | _                                           | 38    | _    | 78               | MHz  |

| $\Delta_{PLL1IN}$       | PLL1 input clock duty cycle <sup>1</sup>       | _                                           | 35    | _    | 65               | %    |

| f <sub>PLL1VCO</sub>    | PLL1 VCO frequency                             | _                                           | 600   | _    | 1250             | MHz  |

| f <sub>PLL1PHI</sub>    | PLL1 output clock PHI                          | _                                           | 4.762 | _    | 264              | MHz  |

| t <sub>PLL1LOCK</sub>   | PLL1 lock time                                 | _                                           | _     | _    | 100              | μs   |

| Δ <sub>PLL1PHISPJ</sub> | PLL1_PHI single period peak-to-<br>peak jitter | f <sub>PLL1PHI</sub> = 200 MHz, 6-<br>sigma | _     | _    | 500 <sup>2</sup> | ps   |

| f <sub>PLL1MOD</sub>    | PLL1 modulation frequency                      | _                                           | _     | _    | 250              | kHz  |

| δ <sub>PLL1MOD</sub>    | PLL1 modulation depth (when                    | Center spread                               | 0.25  | _    | 2                | %    |

|                         | enabled)                                       | Down spread                                 | 0.5   | _    | 4                | %    |

| I <sub>PLL1</sub>       | PLL1 consumption                               | FINE LOCK state                             | _     | _    | 6                | mA   |

- 1. PLL1IN clock retrieved directly from either internal PLL0 or external XOSC clock. Input characteristics are granted when using internal PLL0 or external oscillator in functional mode.

- 2. Noise on the  $V_{DD}$  supply with frequency content below 40 kHz and above 50 MHz is filtered by the PLL. Noise on the  $V_{DD}$  supply with frequency content in the range of 40 kHz 50 MHz must be filtered externally to the device.

# 3.7.2 Oscillator electrical specifications

#### **NOTE**

All oscillator specifications in Table 14 are valid for  $V_{DDEH6} = 3.0 \text{ V}$  to 5.5 V.

Table 14. External oscillator (XOSC) electrical specifications

| Symbol               | Parameter                                                 | Conditions                                   | Value                  |                                                              | Unit |

|----------------------|-----------------------------------------------------------|----------------------------------------------|------------------------|--------------------------------------------------------------|------|

| Syllibol             | Farameter                                                 | Conditions                                   | Min                    | Max 40 5 0.5 V <sub>REF</sub> - 0.6 3.0 2.8 3.0 2.9 10 27 35 |      |

| f <sub>XTAL</sub>    | Crystal frequency range                                   | _                                            | 8                      | 40                                                           | MHz  |

| t <sub>cst</sub>     | Crystal start-up time <sup>1, 2</sup>                     | T <sub>J</sub> = 150 °C                      | _                      | 5                                                            | ms   |

| t <sub>rec</sub>     | Crystal recovery time <sup>3</sup>                        | _                                            | _                      | 0.5                                                          | ms   |

| V <sub>IHEXT</sub>   | EXTAL input high voltage (external reference)             | V <sub>REF</sub> = 0.28 * V <sub>DDEH6</sub> | V <sub>REF</sub> + 0.6 | _                                                            | V    |

| V <sub>ILEXT</sub>   | EXTAL input low voltage (external reference)              | V <sub>REF</sub> = 0.28 * V <sub>DDEH6</sub> | _                      | V <sub>REF</sub> – 0.6                                       | V    |

| C <sub>S_EXTAL</sub> | Total on-chip stray capacitance on EXTAL pin <sup>4</sup> | 416-ball MAPBGA                              | 2.3                    | 3.0                                                          | pF   |

|                      |                                                           | 516-ball MAPBGA                              | 2.1                    | 2.8                                                          |      |

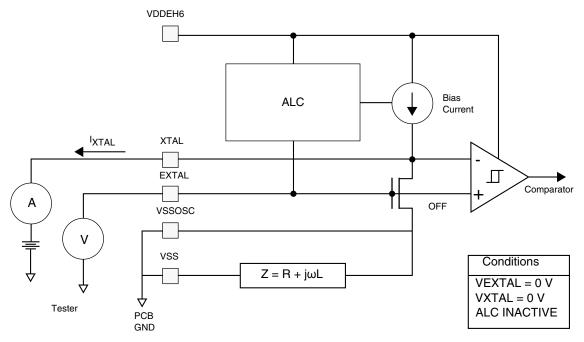

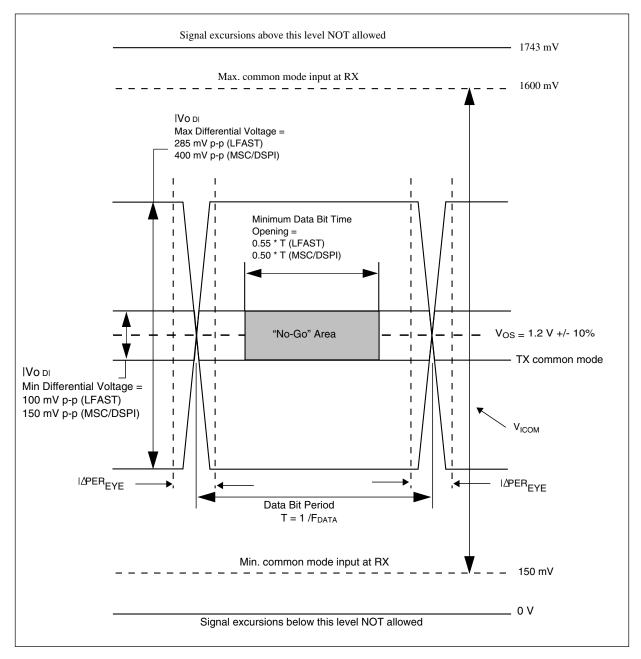

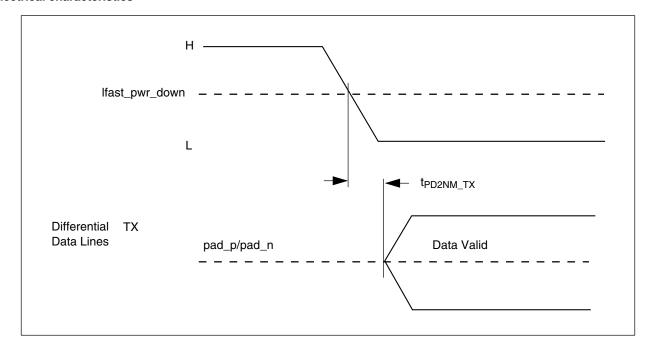

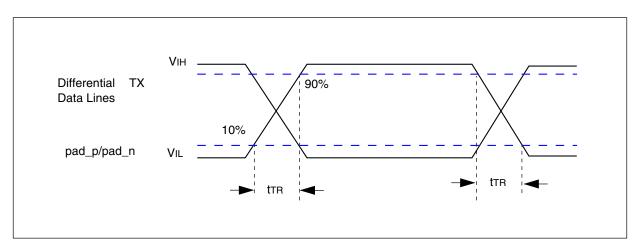

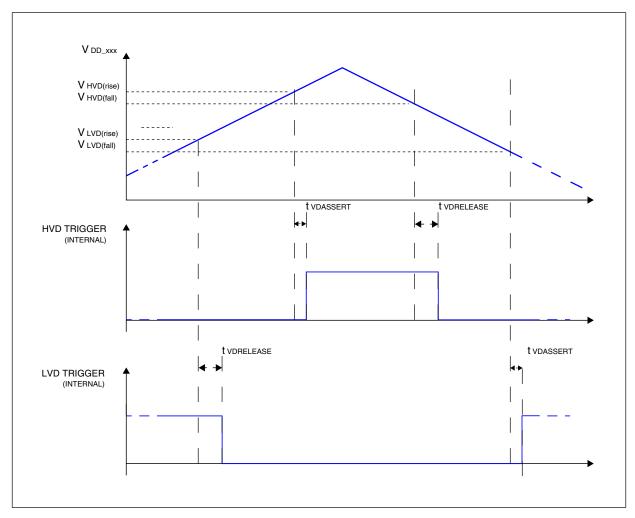

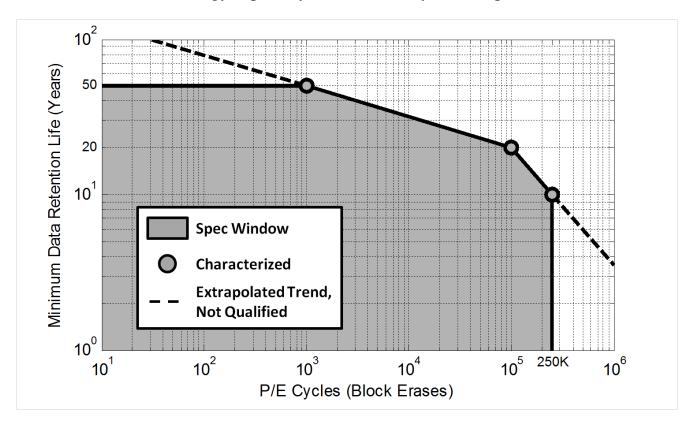

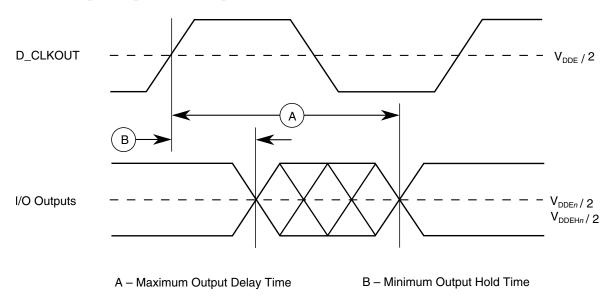

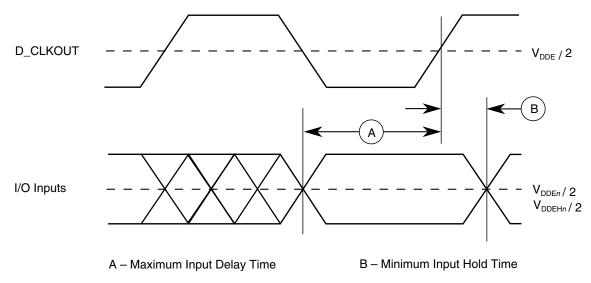

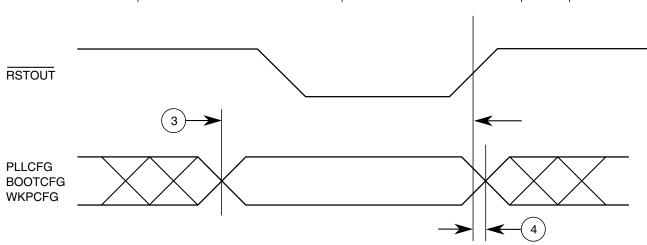

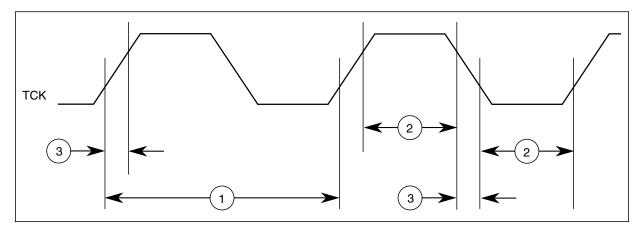

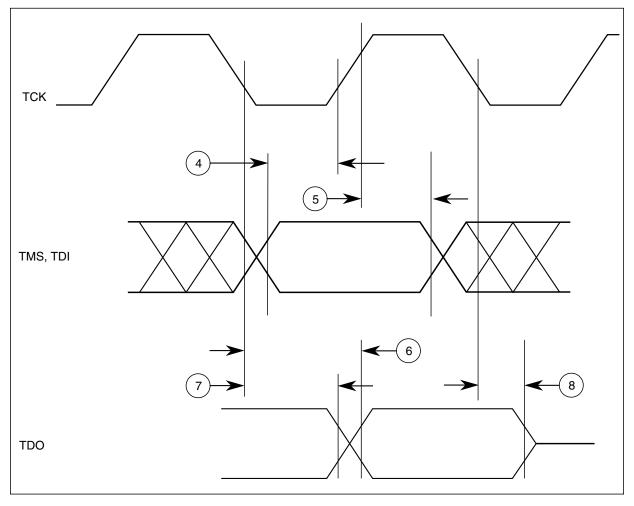

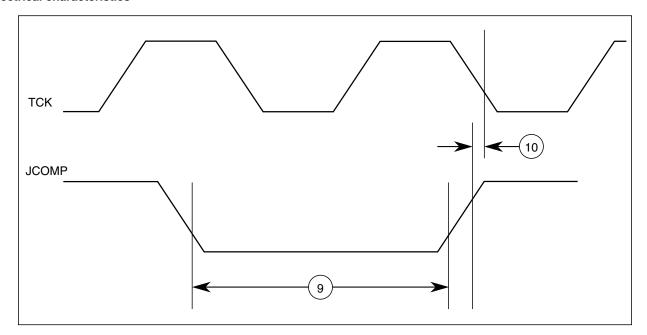

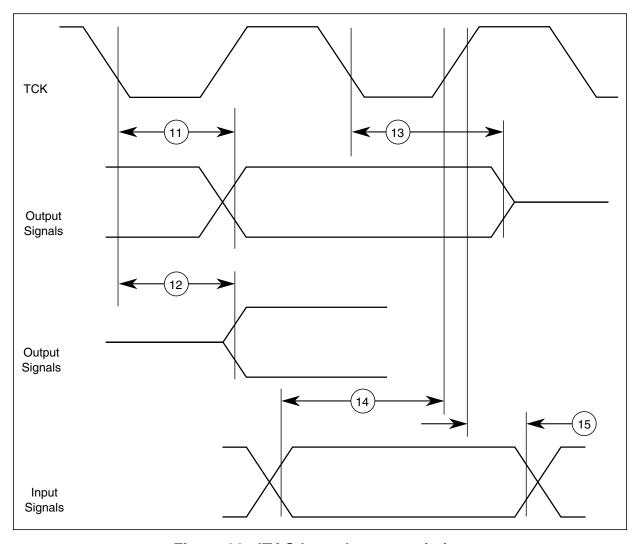

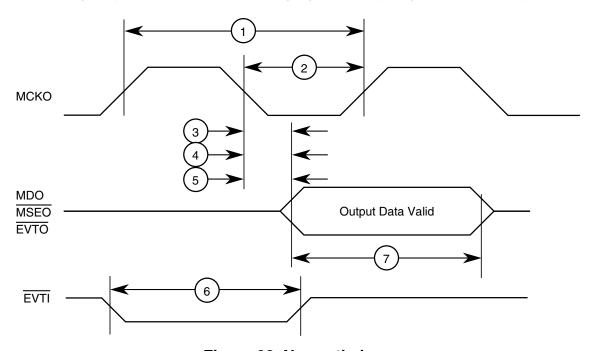

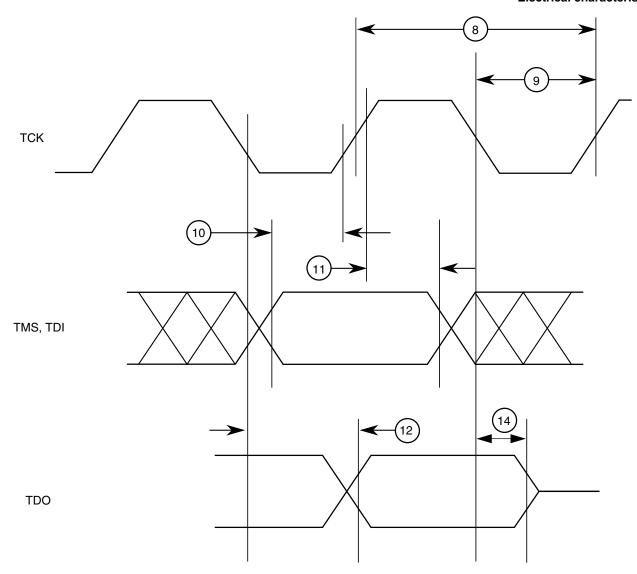

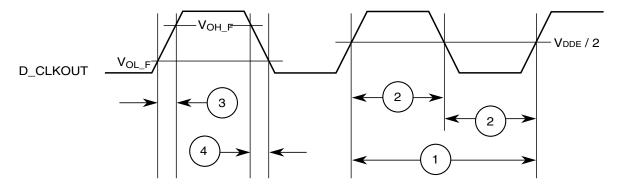

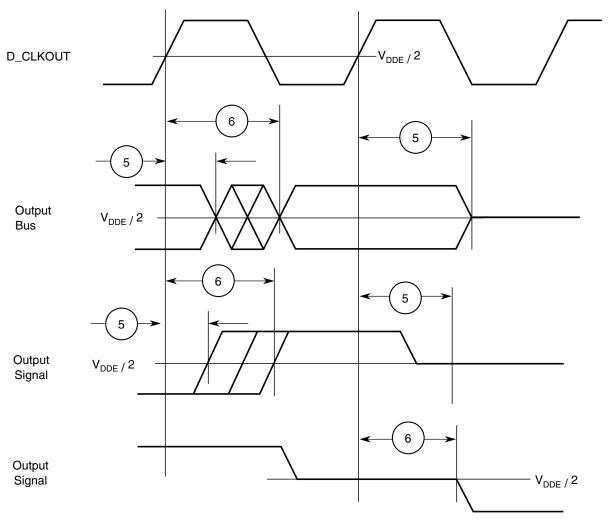

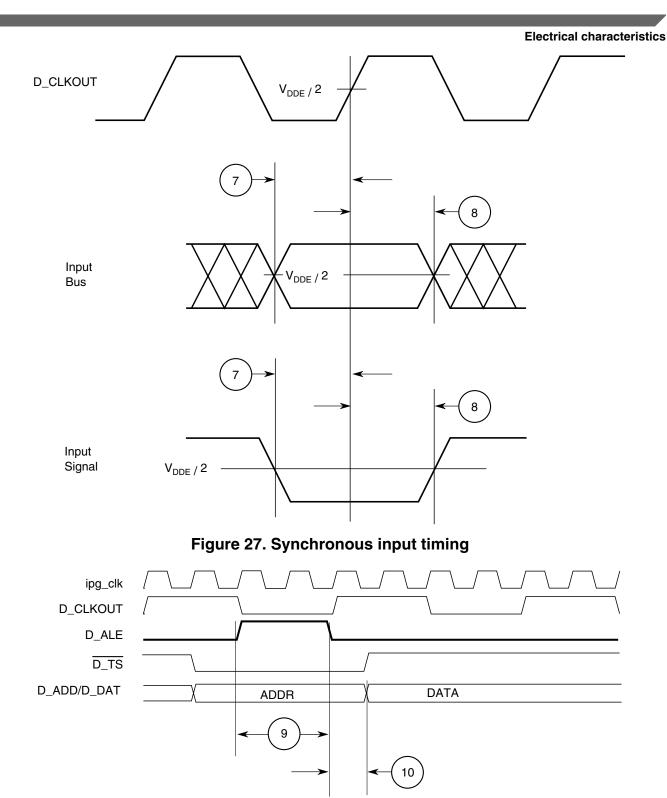

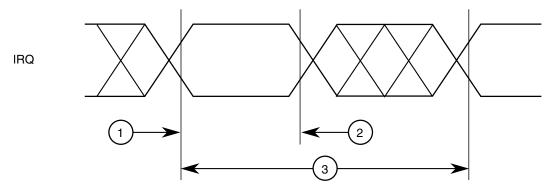

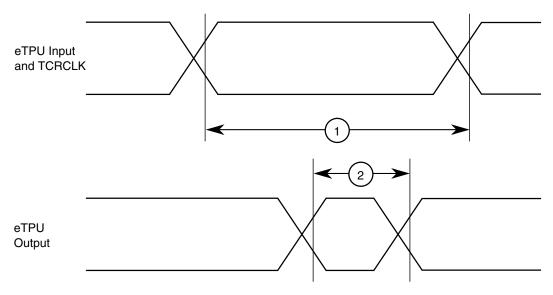

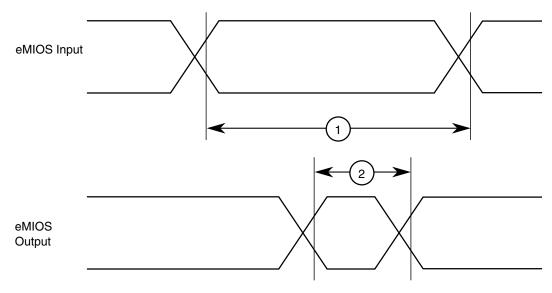

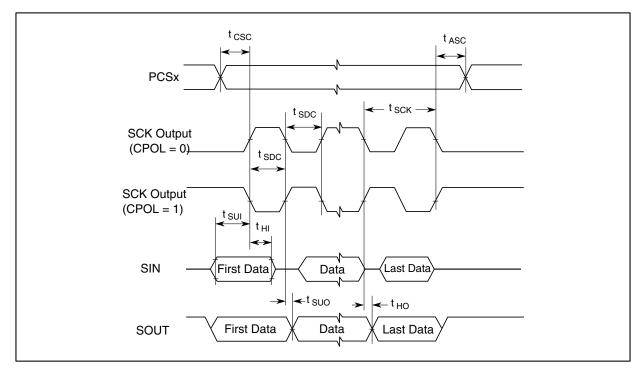

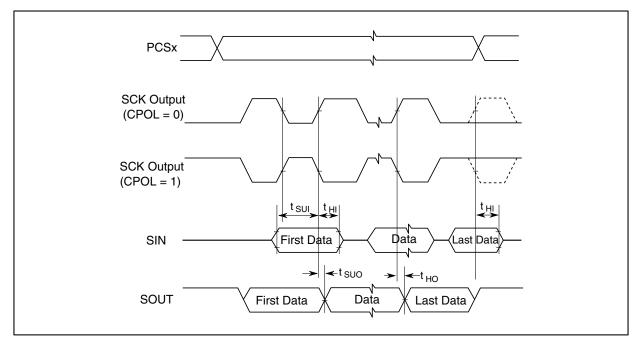

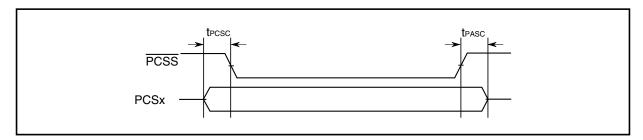

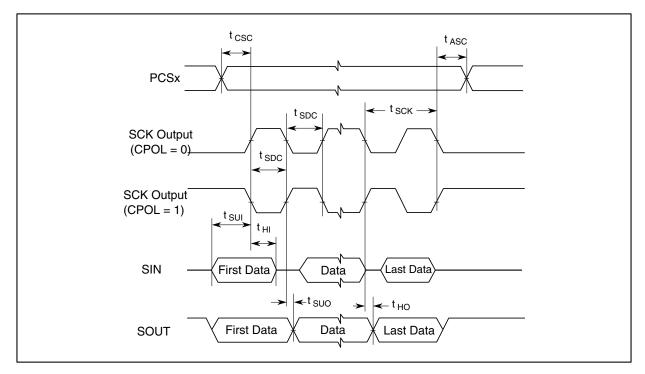

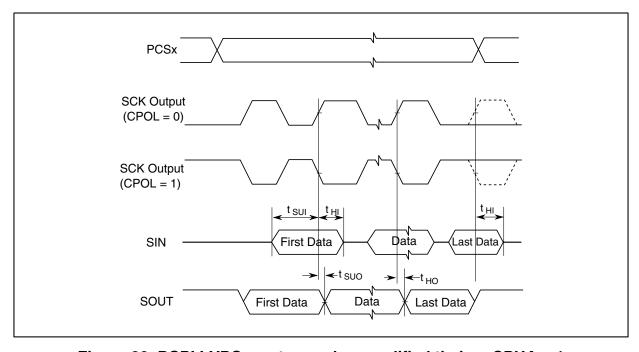

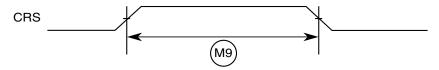

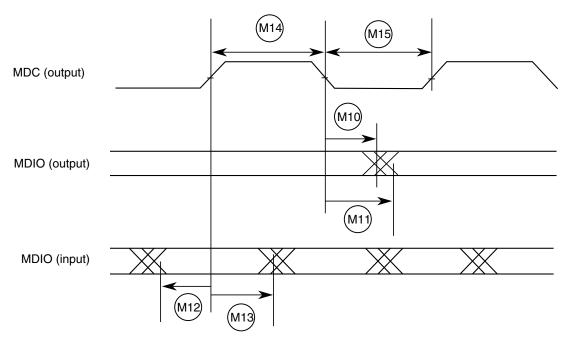

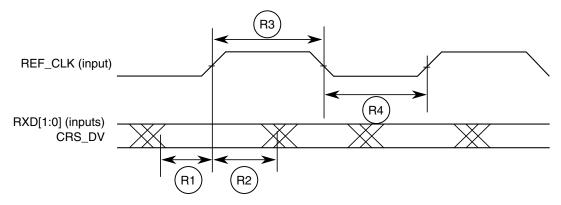

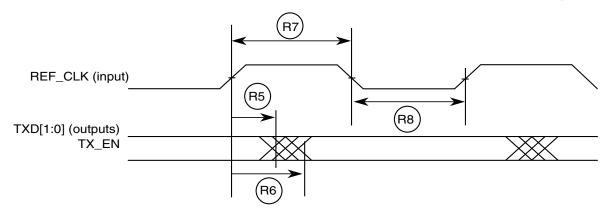

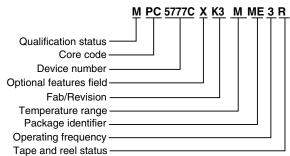

| C <sub>S_XTAL</sub>  | Total on-chip stray capacitance on XTAL pin <sup>4</sup>  | 416-ball MAPBGA                              | 2.3                    | 3.0                                                          | pF   |