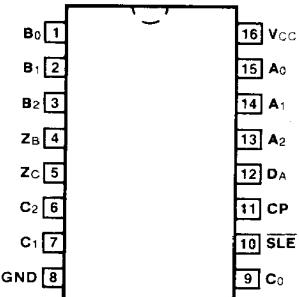

CONNECTION DIAGRAM

PINOUT A

9338

93L38 010225

## 8-BIT MULTIPLE PORT REGISTER

**DESCRIPTION** — The '38 is an 8-bit multiple port register designed for high speed random access memory applications where the ability to simultaneously read and write is desirable. A common use would be as a register bank in a three address computer. Data can be written into any one of the eight bits and read from any two of the eight bits simultaneously. The circuit uses TTL technology and is compatible with all TTL families.

- **MASTER/SLAVE OPERATION PERMITTING SIMULTANEOUS WRITE/READ WITHOUT RACE PROBLEMS**

- **SIMULTANEOUSLY READ TWO BITS AND WRITE ONE BIT IN ANY ONE OF EIGHT BIT POSITIONS**

- **READILY EXPANDABLE TO ALLOW FOR LARGER WORD SIZES**

**ORDERING CODE:** See Section 9

| PKGS               | PIN<br>OUT | COMMERCIAL GRADE                                                    | MILITARY GRADE                                                          | PKG<br>TYPE |

|--------------------|------------|---------------------------------------------------------------------|-------------------------------------------------------------------------|-------------|

|                    |            | V <sub>CC</sub> = +5.0 V $\pm$ 5%,<br>T <sub>A</sub> = 0°C to +70°C | V <sub>CC</sub> = +5.0 V $\pm$ 10%,<br>T <sub>A</sub> = -55°C to +125°C |             |

| Plastic<br>DIP (P) | A          | 9338PC, 93L38PC                                                     |                                                                         | 9B          |

| Ceramic<br>DIP (D) | A          | 9338DC, 93L38DC                                                     | 9338DM, 93L38DM                                                         | 7B          |

| Flatpak<br>(F)     | A          | 9338FC, 93L38FC                                                     | 9338FM, 93L38FM                                                         | 4L          |

**INPUT LOADING/FAN-OUT:** See Section 3 for U.L. definitions

| PIN NAMES                       | DESCRIPTION                            | 93XX (U.L.)<br>HIGH/LOW | 93L (U.L.)<br>HIGH/LOW |

|---------------------------------|----------------------------------------|-------------------------|------------------------|

| A <sub>0</sub> — A <sub>2</sub> | Write Address Inputs                   | 0.67/0.68               | 0.33/0.17              |

| D <sub>A</sub>                  | Data Input                             | 0.67/0.68               | 0.33/0.17              |

| B <sub>0</sub> — B <sub>2</sub> | B Read Address Inputs                  | 0.67/0.68               | 0.33/0.17              |

| C <sub>0</sub> — C <sub>2</sub> | C Read Address Inputs                  | 0.67/0.68               | 0.33/0.17              |

| CP                              | Clock Pulse Input (Active Rising Edge) | 0.67/0.68               | 0.33/0.17              |

| SLE                             | Slave Enable Input (Active LOW)        | 0.67/0.68               | 0.33/0.17              |

| Z <sub>B</sub>                  | B Output                               | 20/10                   | 10/5.0<br>(3.0)        |

| Z <sub>C</sub>                  | C Output                               | 20/10                   | 10/5.0<br>(3.0)        |

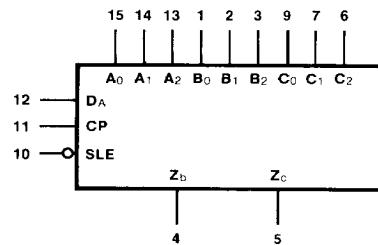

## LOGIC SYMBOL

V<sub>CC</sub> = Pin 16

GND = Pin 8

6

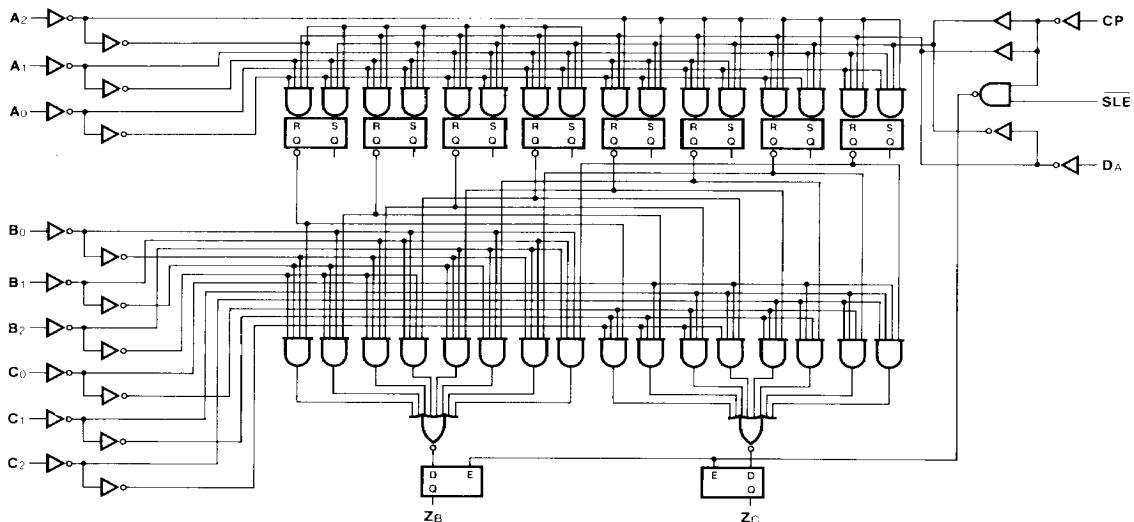

## LOGIC DIAGRAM

**FUNCTIONAL DESCRIPTION** — The '38 8-bit multiple port register can be considered a 1-bit slice of eight high speed working registers. Data can be written into any one and read from any two of the eight locations simultaneously. Master/slave operation eliminates all race problems associated with simultaneous read/write activity from the same location. When the clock input (CP) is LOW data applied to the data input line ( $D_A$ ) enters the selected master. This selection is accomplished by coding the three write input select lines ( $A_0 — A_2$ ) appropriately. Data is stored synchronously with the rising edge of the clock pulse.

The information for each of the two slaved (output) latches is selected by two sets of read address inputs ( $B_0 — B_2$  and  $C_0 — C_2$ ). The information enters the slave while the clock is HIGH and is stored while the clock is LOW. If Slave Enable is LOW (SLE), the slave latches are continuously enabled. The signals are available on the output pins ( $Z_B$  and  $Z_C$ ). The input bit selection and the two output bit selections can be accomplished independently or simultaneously. The data flows into the device, is demultiplexed according to the state of the write address lines and is clocked into the selected latch. The eight latches function as masters and store the input data. The two output latches are slaves and hold the data during the read operation. The state of each slave is determined by the state of the master selected by its associated set of read address inputs.

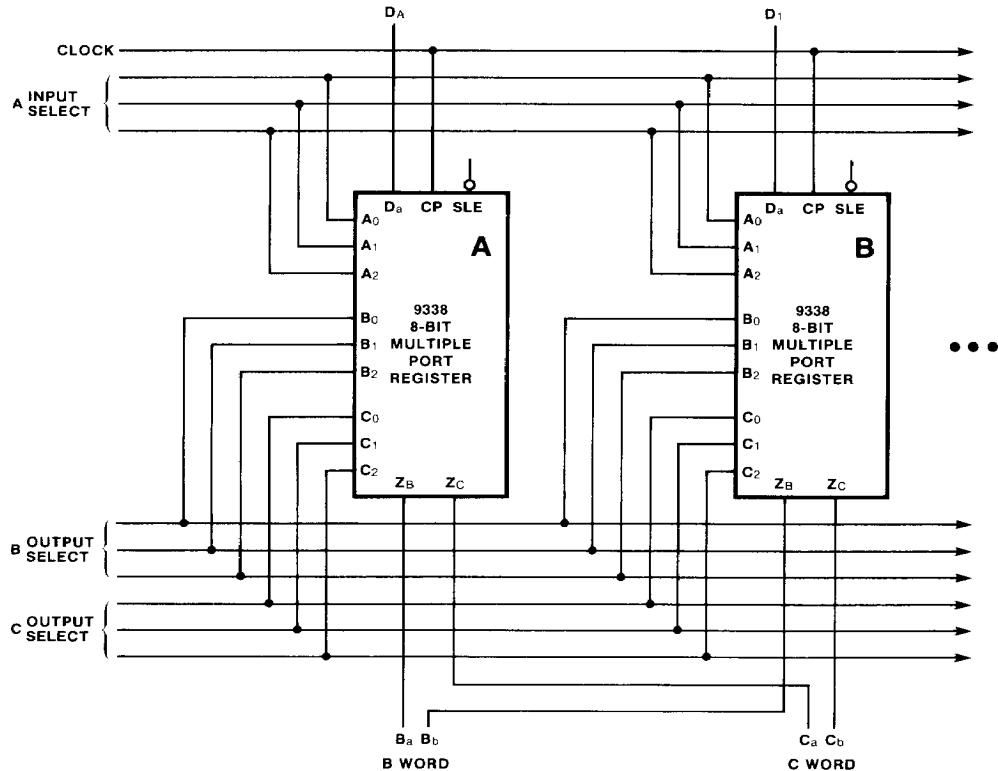

The method of parallel expansion is shown in *Figure a*. One '38 is needed for each bit of the required word length. The read and write input lines should be connected in common on all of the devices. This register configuration provides two words of  $n$ -bits each at one time, where  $n$  devices are connected in parallel.

Fig. a Parallel Expansion

**DC CHARACTERISTICS OVER OPERATING TEMPERATURE RANGE (unless otherwise specified)**

| SYMBOL   | PARAMETER                    | 93XX |     | 93L  |     | UNITS | CONDITIONS            |

|----------|------------------------------|------|-----|------|-----|-------|-----------------------|

|          |                              | Min  | Max | Min  | Max |       |                       |

| $I_{OS}$ | Output Short Circuit Current | -10  | -70 | -2.5 | -25 | mA    | $V_{CC} = \text{Max}$ |

| $I_{CC}$ | Power Supply Current         | 135  |     | 33   |     | mA    | $V_{CC} = \text{Max}$ |

**AC CHARACTERISTICS:  $V_{CC} = +5.0$  V,  $T_A = +25^\circ\text{C}$  (See Section 3 for waveforms and load configurations)**

| SYMBOL    | PARAMETER                                    | 93XX                  |     | 93L                   |     | UNITS | CONDITIONS      |  |  |

|-----------|----------------------------------------------|-----------------------|-----|-----------------------|-----|-------|-----------------|--|--|

|           |                                              | $C_L = 15 \text{ pF}$ |     | $C_L = 15 \text{ pF}$ |     |       |                 |  |  |

|           |                                              | Min                   | Max | Min                   | Max |       |                 |  |  |

| $t_{PLH}$ | Propagation Delay<br>$B_n$ or $C_n$ to $Z_n$ | 13                    | 40  | 68                    |     | ns    | Figs. 3-1, 3-20 |  |  |

| $t_{PHL}$ |                                              | 18                    | 35  | 95                    |     | ns    |                 |  |  |

| $t_{PLH}$ | Propagation Delay<br>$D_A$ to $Z_n$          | 25                    | 45  | 70                    |     | ns    | Figs. 3-1, 3-5  |  |  |

| $t_{PHL}$ |                                              | 25                    | 50  | 92                    |     | ns    |                 |  |  |

| $t_{PLH}$ | Propagation Delay<br>$CP$ to $Z_n$           | 18                    | 35  | 65                    |     | ns    | Figs. 3-1, 3-8  |  |  |

| $t_{PHL}$ |                                              | 13                    | 30  | 57                    |     | ns    |                 |  |  |

**AC OPERATING REQUIREMENTS:  $V_{CC} = +5.0$  V,  $T_A = +25^\circ\text{C}$**

| SYMBOL   | PARAMETER                  | 93XX |     | 93L  |     | UNITS | CONDITIONS |

|----------|----------------------------|------|-----|------|-----|-------|------------|

|          |                            | Min  | Max | Min  | Max |       |            |

| $t_s(H)$ | Setup Time HIGH or LOW     | 20   |     | 30   |     | ns    |            |

| $t_s(L)$ | $D_A$ to $CP$              | 12   |     | 22   |     | ns    |            |

| $t_h(H)$ | Hold Time HIGH or LOW      | 0    |     | 0    |     | ns    | Fig. 3-6   |

| $t_h(L)$ | $D_A$ to $CP$              | -8.0 |     | -4.0 |     | ns    |            |

| $t_s(H)$ | Setup Time HIGH or LOW     | 10   |     | 0    |     | ns    |            |

| $t_s(L)$ | $A_n$ to $CP$              | 10   |     | 0    |     | ns    | Fig. 3-21  |

| $t_h(H)$ | Hold Time HIGH or LOW      | 0    |     | 0    |     | ns    |            |

| $t_h(L)$ | $A_n$ to $CP$              | 0    |     | 0    |     | ns    |            |

| $t_w(H)$ | CP Pulse Width HIGH or LOW | 23   |     | 40   |     | ns    |            |

| $t_w(L)$ |                            | 13   |     | 30   |     | ns    | Fig. 3-8   |