#### 4. DSP RAM ACCESS

The modem DSP contains a 16-bit wide random access memory (RAM). The host processor can access (read or write) the RAM through a 12-bit memory address in registers 1D and 1C.

# 4.1. INTERFACE MEMORY ACCESS TO DSP RAM

The interface memory acts as an intermediary during host to DSP RAM or DSP RAM to host data exchanges. The address stored in interface memory RAM address registers MEADDH and MEADDL by the host is the DSP RAM address for data access. The data is transferred through data registers MEDAM and MEDAL.

One or two bytes (1 byte = 8 bits) are transferred between DSP RAM and DSP interface memory once each device cycle. The DSP operates at a 7200 Hz sample rate.

The RAM access bit (MEACC) in the interface memory instructs the DSP to access the RAM. The transfer is initiated by the host setting the MEACC bit. The DSP tests this bit each sample period.

RAM can be accessed using one of four methods:

- 1. 8-bit read 8-bit write.

- 2. 16-bit read 8-bit write.

- 3. 16-bit read 16-bit write.

- 4. 16-bit read only (modern diagnostics).

Parameters transferred under the first method have only 8 bits of significance. The data is written to and read from MEDAL. Data in MEDAM is ignored.

Parameters transferred using the second method have 16 bits of significance but can be written only 8 bits at a time. These parameters have two access codes associated with them, one for the least significant 8-bits and and for the most significant 8 bits. The host need read only the low address to obtain both the most significant and the least significant bytes of the data if the two access codes are in consecutive order.

Parameters transferred using the third method involve 16bit read or write operations using one access code.

Finally, all diagnostic read operations using the fourth method use only one access code. Data is read from MEDAM and MEDAL.

The parameters available in DSP RAM are listed in Table 4-1.

# 4.2. HOST DSP READ AND WRITE PROCEDURES

#### **DSP RAM Write Procedure**

- Set MEMW to inform the DSP that a RAM write will occur when MEACC is set.

- Load the RAM address into the MEADDH and MEADDL registers.

- 3. Write the desired data into the interface memory RAM data registers MEDAM and/or MEDAL

- Set MEACC to signal the DSP to perform the RAM write.

- 5. When the DSP has transferred the contents of the interface memory RAM data registers into RAM, the modem resets the MEACC bit and sets the NEWS bit to indicate DSP RAM write completion. If the NSIE bit is a 1, IRQ is asserted and NSIA is set to inform the host that setting of the NEWS bit is the source of the interrupt request.

- 6. Upon the completion of IRQ servicing, write a 0 into the NEWS bit to clear the NSIA bit and to negate IRQ if no other interrupt requests are pending.

#### **DSP RAM Read Procedure**

- Reset MEMW to inform the DSP that a RAM read will occur when MEACC is set.

- Load the RAM address code into the MEADDH and MEADDL registers.

- Set MEACC to signal the DSP to perform the RAM read.

- 4. When the DSP has transferred the contents of RAM into the interface memory RAM data registers MEDAM and/or MEDAL, the modem resets the MEACC bit and sets the NEWS bit to indicate DSP RAM read completion. If the NSIE bit is a 1, IRQ is asserted and NSIA is set to inform the host that setting of the NEWS bit is the source of the interrupt request.

- 6. Upon the completion of IRQ servicing, write a 0 into the NEWS bit to clear the NSIA bit and to negate IRQ if no other interrupt requests are pending.

#### 4.3. RAM READ AND WRITE EXAMPLES

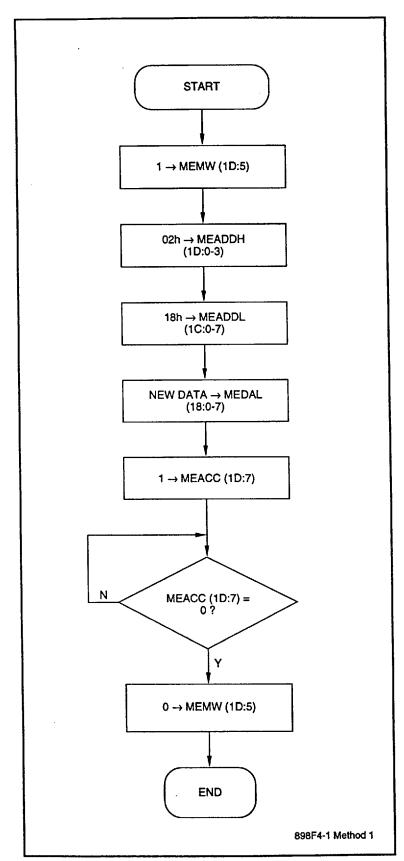

Figure 4-1 shows a flowchart of a procedure to change the DTMF tone duration using method 1.

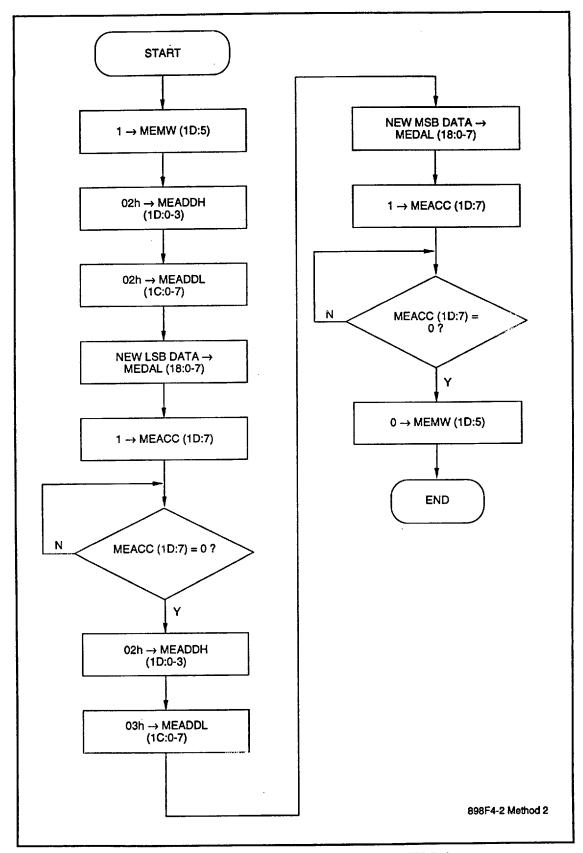

Figure 4-2 shows a flowchart of a procedure to change the RTS-CTS delay using method 2.

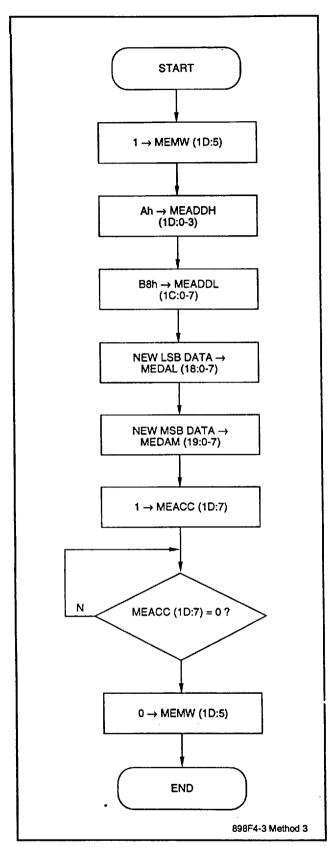

Figure 4-3 shows a flowchart of a procedure to change the THRESHU value for TONEA using method 3.

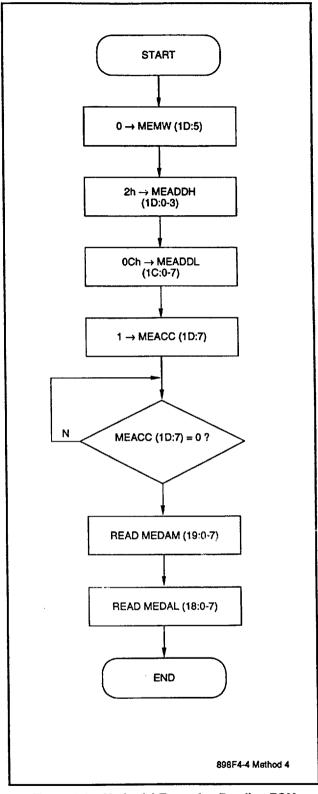

Figure 4-4 shows a flowchart of a procedure to read EQM using method 4.

Table 4-1. Interface Memory RAM Addresses

| No.      | Function                                                | Method       | Address (Hex)                                 |

|----------|---------------------------------------------------------|--------------|-----------------------------------------------|

| 1        | Transmitter Compromise Equalizer Coefficients           |              |                                               |

|          | First Coefficient Tap                                   | 3            | AE8                                           |

|          | Last Coefficient Tap                                    | 3            | AD0                                           |

|          | Number of Taps                                          | 3            | B47                                           |

| 2        | Rate Sequence                                           |              |                                               |

|          | Received R                                              | 4            | 208                                           |

|          | Received E                                              | 4            | 20A                                           |

|          | Transmitted R                                           | 2 (RO)       | 204, 205 (see Note 1)                         |

|          | Transmitted E                                           | 2 (RO)       | 206, 207 (see Note 1)                         |

|          | V.32/V.32 bis R1 Mask                                   | 2            | 2C0, 2C1 (see Note 1)                         |

|          | V.32/V.32 bis R2 Mask                                   | 2            | 2C2, 2C3 (see Note 1)                         |

|          | V.32 bis R4 Mask                                        | 2            | 2C4, 2C5 (see Note 1)                         |

|          | V.32 bis R5 Mask                                        | 2            | 2C6, 2C7 (see Note 1)                         |

|          | V.33 R33 Mask                                           | 2            | 2C8, 2C9 (see Note 1)                         |

| 3        | DTMF Tone Duration                                      | 2            | 218, 2DB (see Note 1)                         |

| 4        | DTMF Interdigit Delay                                   | 2 2          | 219, 2DC(see Note 1)<br>29B, 29C (see Note 1) |

| 5        | DTMF Low Band Power Level                               |              | 29D, 29E (see Note 1)                         |

| 6        | DTMF High Band Power Level                              | 1            | 22C (See Note 1)                              |

| 7        | Pulse Relay Make Time                                   | 1            | 21C                                           |

| 8        | Pulse Relay Break Time                                  | 2            | 21A, 21B                                      |

| 9        | Pulse Interdigit Delay                                  | 2            | 290, 2D9 (see Note 1)                         |

| 10<br>11 | Calling Tone On Time Calling Tone Off Time              | 2            | 291, 2DA (see Note 1)                         |

| 11       | Transmitter Output Level Gain (G)                       | -            |                                               |

| 12       | Transmitter Output Level Gain (G) - All Modes           | 3            | A48                                           |

|          | Transmitter Output Level Gain (G) - FSK Modes           | 3            | B57                                           |

| 13       | Dual Tone 1 Frequency                                   | 2            | 280, 281 (see Note 1)                         |

| 14       | Dual Tone 2 Frequency                                   | 2            | 282, 283 (see Note 1)                         |

| 15       | Dual Tone 1 Power Level                                 | 2            | 284, 285 (see Note 1)                         |

| 16       | Dual Tone 2 Power Level                                 | 2            | 286, 287 (see Note 1)                         |

| 17       | New Status (NEWS) Masking Registers                     |              |                                               |

|          | Masking Register for 01                                 | 1            | 247                                           |

|          | Masking Register for 0A and 0B                          | 2            | 246, 245                                      |

|          | Masking Register for 0C and 0D                          | 2            | 244, 243                                      |

|          | Masking Register for 0E and 0F                          | 2            | 242, 241                                      |

|          | Masking Register for 12 (set bit 7 to enable interrupt) | 1            | 089 (bit 7)                                   |

|          | Masking Register for 14                                 | 1            | 38A                                           |

|          | Masking Register for 16                                 | 1            | 370<br>371                                    |

|          | Masking Register for 17                                 | 1 2          | 27D, 27C                                      |

|          | Masking Register for 1A and 1B                          |              | 270,270                                       |

|          | Masking Register for Memory Access                      | <del> </del> | 089 (bit 6)                                   |

|          | (Set bit 6 to disable interrupt)                        | 4            | 852                                           |

| 22<br>23 | Far-End Echo Frequency Offset Far-End Echo Level        | 1 4          | B52                                           |

| 23       | CTS OFF-to-ON Response Time (RTS-CTS Delay)             | 2            | 202, 203 (see Note 1)                         |

| 25       | Answer Tone Length                                      | 2            | 228, 229 (see Note 1)                         |

| 26       | Silence after Answer Tone Period                        | 2            | 22A, 22B (see Note 1)                         |

| 27       | Tone Detector A Bandpass Filter Coefficients            | 3            | See Table 4-6                                 |

| 28       | Tone Detector B Bandpass Filter Coefficients            | 3            | See Table 4-6                                 |

| 29       | Tone Detector C Bandpass Filter Coefficients            | 3            | See Table 4-6                                 |

| 30       | RLSD Drop Out Timer                                     | 1            | 270 and 271                                   |

| 31       | RLSD Turn-On Threshold (RLSD_ON)                        | 2            | 134, 135                                      |

| 32       | RLSD Turn-Off Threshold (RLSD_OFF)                      | 2            | 136, 137                                      |

|          | RLSD Threshold Offset                                   | 2            | 138, 139                                      |

|          | RLSD Overwrite Control                                  | 1            | 10D (Bit 2)                                   |

|          | Extended RTH Control                                    | 11           | 10D (Bit 6)                                   |

|          | Receiver Gain                                           | 1            | A03                                           |

|          | Receiver Threshold                                      | 3            | A04, A05                                      |

|          | RTH0 Offset                                             | 2            | 2D0, 2D1 (see Note 1)                         |

|          | RTH1 Offset                                             | 2            | 2D2, 2D3 (see Note 1)                         |

|          | RTH2 Offset                                             | 2            | 2D4, 2D5 (see Note 1)                         |

|          | RTH3 Offset                                             | 2            | 2D6, 2D7 (see Note 1)                         |

Table 4-1. Interface Memory RAM Addresses (Cont'd)

| No.  | Function                                            | Method | Address (Hex)         |

|------|-----------------------------------------------------|--------|-----------------------|

| 34   | V.32 PN Length                                      | 2      | 288, 289 (see Note 1) |

| 36   | AGC Gain Word                                       | 4      | A00                   |

| 37   | Round Trip Far Echo Delay                           | 4      | 239                   |

| 45   | Equalizer Frequency Correction                      | 4      | 811                   |

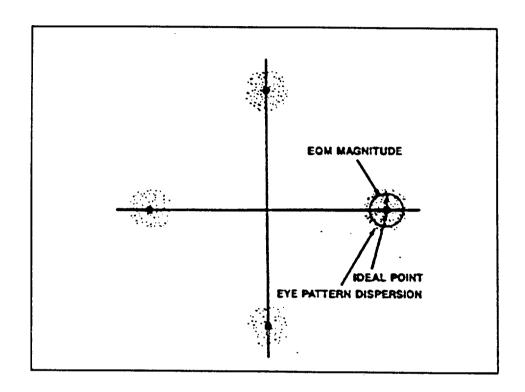

| 46   | Eye Quality Monitor (EQM)                           | 4      | 20C                   |

| 47   | Maximum Period of Valid Ring Signal                 | 1      | 21F                   |

| 48   | Minimum Period of Valid Ring Signal                 | 1      | 21E                   |

| 49   | Phase Jitter Frequency                              | 4      | 80E                   |

| 50   | Phase Jitter Amplitude                              | 4      | 80D                   |

| 51   | Guard Tone Level                                    | 3      | B46                   |

| 52   | CCITT CRC 32 Select                                 | 1      | 0B3                   |

| 53   | Secondary Channel Transmitter Speed Select          | 1      | 28E                   |

| •    | Secondary Channel Receiver Speed Select             | 1      | 28B                   |

| 58   | V.FC Automatic Carrier Select (ACS)                 | 1      | 13F (bit 4)           |

| 55   | V.FC Carrier Deviation Negotiation (CDN)            | 1      | 100 (bit 4)           |

|      | V.FC Carrier Deviation Offset                       | 1      | 10A                   |

| 59   | V.FC Carrier Bias                                   | 1      | 212                   |

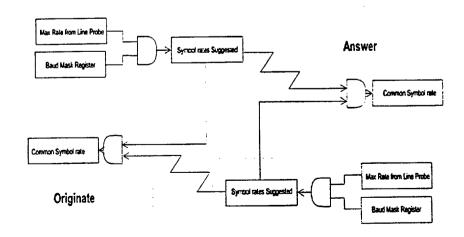

| 60   | V.34/V.FC Symbol Rate Value                         | 1      | 2E3                   |

| 61   | V.34/V.FC Baud Rate Mask (BRM)                      | 1      | 101                   |

| 62   | V.34/V.FC Pre-Emphasis Value                        | 4      | B44                   |

| 63   | V.34/V.FC Pre-Emphasis Override                     | 1      | 0E6                   |

| - 00 | V.34/V.FC Pre-Emphasis Disable (PREDIS)             | 1      | 100 (bit 1)           |

| 64   | V.34/V.FC Transmit Level Deviation Disable (TLDDIS) | 1      | 100 (bit 3)           |

| 65   | V.FC Transmit Level Deviation Bias                  | 1      | 216                   |

| 68   | EQM Above Threshold                                 | 1      | 133                   |

| 69   | EQM Scale Factor (Gain)                             | 3      | A29                   |

| 03   | EQM ARA Bias (Offset)                               | 2      | 2A4, 2A5              |

| 70   | V.21/V.23 CTS Mark Qualify                          | 1      | 10D (bit 3)           |

| 71   | V.FC Symbol Rate Offset                             | 1      | 13B and 13C           |

| 72   | V.FC Data Rate Sequence Mask                        | 2      | 116, 117              |

| 73   | No Automode to FSK                                  | 1      | 13F (bit 0)           |

| 74   | Receive FIFO Trigger Level                          | 1      | 32C                   |

| 75   | V.FC GSTN Cleardown Option                          | 1      | 10D (bit 4)           |

| 81   | V.34 Spectral Parameters Control                    | 1      | 105                   |

| 82   | V.34 Phase 2 Power Reduction                        | 1      | 0E2                   |

| 83   | V.34 Low Band Symbol Rate Edge Estimate Offset      | 1      | 13B                   |

|      | V.34 High Band Symbol Rate Edge Estimate Offset     | 1      | 13C                   |

| 84   | V.34 Receiver Speed Indication                      | 1      | 384                   |

| 85   | V.34 Data Rate Mask                                 | 2      | 382, 383              |

| 86   | V.34 Asymmetric Data Rates Enable                   | 1      | 13F Bit 6             |

| 87   | V.34 Remote Mode Data Rate Capability               | 2 (RO) | 208, 209              |

| - 01 | V.34 Remote Modern Asymmetric Data Rate Indicator   | 1 (RO) | 209 Bit 7             |

Table 4-1. Interface Memory RAM Addresses (Cont'd)

| No.        | Function                                                                                                     | Method                                           | Address (Hex) |

|------------|--------------------------------------------------------------------------------------------------------------|--------------------------------------------------|---------------|

| 88         | V.8 Status Registers - See Section 9                                                                         |                                                  |               |

| •          | V.8 Status Register 1                                                                                        | 1                                                | 301           |

|            | V.8 Status Register 2                                                                                        | 1                                                | 302           |

|            | V.8 Status Register 3                                                                                        | 1                                                | 303           |

| 89         | V.8 Control Registers - See Section 9                                                                        |                                                  |               |

| •          | V.8 Control Register 1                                                                                       | 1                                                | 304           |

|            | V.8 Control Register 2                                                                                       | 1                                                | 305           |

|            | V.8 Control Register 3                                                                                       | 1                                                | 306           |

|            | V.8 Control Register 4                                                                                       | 1                                                | 307           |

|            | V.8 Control Register 5                                                                                       | 1                                                | 308           |

| 90         | Modulation Modes- See Section 9                                                                              |                                                  |               |

| 30         | V.34 Full-Duplex configuration - See Section 9                                                               | 1                                                | 309           |

|            | V.32bis configuration                                                                                        | 1                                                | 30B           |

|            | V.22 bis configuration                                                                                       | 1                                                | 30C           |

|            | V.17 configuration                                                                                           | 1                                                | 30D           |

|            | V.29 configuration                                                                                           | 1                                                | 30E           |

|            | V.27 configuration                                                                                           | 1                                                | 30F           |

|            | V.26 ter configuration                                                                                       | 1                                                | 310           |

|            | V.26 bis configuration                                                                                       | 1                                                | 311           |

|            | V.23 Full-Duplex configuration                                                                               | 1                                                | 312           |

|            | V.23 Half-Duplex configuration                                                                               | 1                                                | 313           |

|            | V.23 Hall-Duplex corniguration                                                                               | 1                                                | 314           |

|            | V.FC configuration                                                                                           | i                                                | 315           |

|            | V.8 MaxFrameByteCount- See Section 9                                                                         | 1                                                | 31C           |

| 91         | V.8 Call Functions- See Section 9                                                                            | 1 i                                              | 32A           |

| 92<br>93   | CM/JM/CI Frame - See Section 9                                                                               |                                                  |               |

| 93         | SYNC CM/JM/CI                                                                                                | 1                                                | 32D           |

|            | Data Call Function                                                                                           | 1                                                | 32E           |

|            | modulation 0                                                                                                 | 1 1                                              | 32F           |

|            | modulation 1                                                                                                 | 1                                                | 330           |

|            |                                                                                                              | <del>                                     </del> | 331           |

|            | modulation 2                                                                                                 | i                                                | 332           |

|            | Protocol (optional) GSTN (optional)                                                                          | 1                                                | 333           |

|            | Frame End                                                                                                    | 1                                                | 334           |

| 100        | Minimum On Time (DTMF)                                                                                       | 3                                                | A78           |

| 100        | Minimum Off Time (DTMF)                                                                                      | 3                                                | 878           |

| 101        | Minimum Oit Time (DTMF)  Minimum Cycle Time (DTMF)                                                           | 3                                                | 978           |

|            | Minimum Dropout Time (DTMF)                                                                                  | 3                                                | B78           |

| 103<br>104 | Maximum Speech Energy (DTMF)                                                                                 | 3                                                | A77           |

| 104        | Frequency Deviation, Low Group (DTMF)                                                                        | 3                                                | 876           |

|            | Frequency Deviation, Low Group (DTMF)                                                                        | 3                                                | A76           |

| 106<br>107 | Negative Twist Control, TWIST4 (DTMF)                                                                        | 3                                                | 977           |

|            | Positive Twist Control, TWIST8 (DTMF)                                                                        | 3                                                | 877           |

| 108        | Maximum Energy Hit Time (DTMF)                                                                               | 3                                                | A67           |

| 109        | ADC Speech Sample Scaling Parameter, ADCS (ADPCM)                                                            | 3                                                | BD1           |

| 110        | White Noise Output Scaling Parameter, RANOISE (ADPCM)                                                        | 3                                                | A35           |

| 111        | Minimum Silence Magnitude Threshold, MTHRESH (ADPCM)                                                         | 3                                                | A36           |

| 112        |                                                                                                              | 3                                                | B37           |

| 113        | Detecting Silence in Speech Parameter, SILSPE (ADPCM)  Detecting Speech in Silence Parameter, SPESIL (ADPCM) | 3                                                | B38           |

| 114        | Minimum Silence Magnitude Adaptation Parameter, MADAPT                                                       | 3                                                | B39           |

| 115        | (ADPCM)                                                                                                      |                                                  |               |

#### Notes:

- 1. High address = MSB of data; low address = LSB of data.

- 2. The host may access only the X or Y data on any given read cycle, i.e., X and Y data cannot be accessed simultaneously.

- 3. RO = read-only.

Figure 4-1. Method 1 Example - Changing DTMF Tone Duration (LSB)

Figure 4-2. Method 2 Example - Changing RTS-CTS Delay

Figure 4-3. Method 3 Example - Changing TONEA THRESHU

Figure 4-4. Method 4 Example - Reading EQM

#### 4.4. DSP RAM DATA SCALING

Function 1A: Transmitter Compromise Equalizer Coefficients

Function 1B: Number of Taps

Acc. Method: 3 Acc. Method: 3 Addr.: AD0-AE8 Addr.: B47

The transmitter compromise equalizer can be programmed by the host in modes other than V.34, V.FC, V.32 bis/V.32, or FSK. The equalizer is a 25-tap finite impulse response (FIR) digital filter. The first tap is at address AE8h (h denotes a hexadecimal number) and the last tap is at AD0h. The sampling rate for the filter is 7200 Hz. New coefficients should be loaded while the modem is in idle mode before turning on DTR (2-wire full-duplex modes) or RTS (4-wire full-duplex modes). The coefficients have to be loaded only once. They are re-initialized to the default values only if a POR occurs. The user should ensure that the overall gain of any filter designed is 1. Set NEWC after new taps have been loaded.

Format:

16-bit, signed, 2s complement

Function 2:

V.32 bis and V.33 Rate Sequence

Acc Method: Table 4-1

Addr. 208-2C9

V.32 bis Rate Sequence Bits. CCITT defines the V.32 bis rate sequence bits as follows:

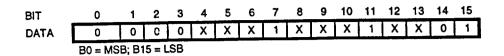

12 13 14 15 BIT X X X 0 0 0 0 X DATA 0 0 B0 = MSB: B15 = LSB

| Bit                 | Description                                     |  |

|---------------------|-------------------------------------------------|--|

| B0-B3, B7, B11, B15 | For synchronizing on rate signal                |  |

| B4                  | -A 1 (Note 1)                                   |  |

| B8                  | -A 1 (Note 1)                                   |  |

| B5                  | A 1 denotes the ability to receive at 4800 bps  |  |

| B6                  | A 1 denotes the ability to receive at 9600 bps  |  |

| B9                  | A 1 denotes the ability to receive at 7200 bps  |  |

| B10                 | A 1 denotes the ability to receive at 12000 bps |  |

| B12                 | A 1 denotes the ability to receive at 14400 bps |  |

| B13, B14            | 0,0 (Note 2)                                    |  |

#### Notes

- 1. When B4 or B8 is set to zero in a transmitted or received rate signal, then interworking can proceed only in accordance with

- B13 and B14 shall be set to zero when transmitting and ignored during the reception of a rate signal; they are reserved for future definition by the CCITT and must not be used by the manufacturers.

- 3. B4-B6, B9-B10, B12 set to zero calls for a GSTN Cleardown.

V.32 Rate Sequence Bits. CCITT defines the V.32 rate sequence bits as follows:

BIT 0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

DATA 0 0 0 1 X X 1 1 X X 1 X 0 0 1

B0 = MSB; B15 = LSB

| Bit                 | Description                                                                                          |

|---------------------|------------------------------------------------------------------------------------------------------|

| B0-B3, B7, B11, B15 | For synchronizing on the rate sequence                                                               |

| B4                  | A 1 denotes the ability to receive at 2400 bps                                                       |

| B5                  | A 1 denotes the ability to receive at 4800 bps                                                       |

| B6                  | A 1 denotes the ability to receive at 9600 bps                                                       |

| B4-B6               | 0 0 0 calls for a GSTN clear down                                                                    |

| B8                  | A 1 denotes the ability of trellis encoding and decoding at the highest data rate indicated in B3-B6 |

| B9-B14              | 0 0 1 0 0 0 denotes absence of special operational modes.                                            |

#### Note

When using the modem in a 7200 bps or 12000 bps proprietary configuration, B9 = 1 denotes the ability to receive at 7200 bps and B10 = 1 denotes the ability to receive at 12000 bps.

V.33 Rate Sequence Bits. CCITT defines the V.33 rate sequence bits as follows:

#### For B14 = 0:

| Bit                  | Description                                     |

|----------------------|-------------------------------------------------|

| B0-B3, B7, B11, B15  | For synchronizing on the rate sequence          |

| B4-B6, B10, B12, B13 | Not defined                                     |

| B8                   | A 1 denotes the ability to receive at 12000 bps |

| B9                   | A 1 denotes the ability to receive at 14400 bps |

#### For B14 = 1:

| Bit                 | Description                                                                                     |

|---------------------|-------------------------------------------------------------------------------------------------|

| B0-B3, B7, B11, B15 | For synchronizing on the rate sequence                                                          |

| B4, B5              | A 00 denotes that B6, B10, B12, and B13 define multiplexer configuration selection              |

| B8                  | A 1 denotes the ability to transmit and receive at 12000 bps                                    |

| B9                  | A 1 denotes the ability to transmit and receive at 14400 bps                                    |

| B6, B10, B12, B13   | Multiplexer configuration selection (see the V.33 specification for multiplexer configurations) |

The V.32 and V.33 rate sequences contain undefined codes and/or bits. The user can use these bits to convey information to the remote modem during training (e.g., remote configuration, multiplexer configuration, test mode configuration, etc.).

The 16-bit rate sequence word in the modem's RAM corresponds exactly to the 16-bit rate sequences defined in V.32 and V.33. The MSB of the word in RAM is 80 of the rate sequence and the LSB is 815 of the rate sequence.

## V.32/V.32 bis Rate Sequence

The V.32/V.32 bis rate sequence is available in RAM during the handshake when the RSEQ bit is a 1. The RSEQ bit will turn on when the E-sequence is available as well. The rate sequence(s) and E-sequence are read from two different RAM locations (see Table 4-1, Function 2). The RSEQ bit must be reset by the host after reading the rate sequence(s).

The host may modify the rate sequence in one of two ways.

Method 1 Description. The first and simplest method is to use the rate sequence mask (see Table 4-1, function 2). The rate sequence masks are available for R1, R2, R4, and R5. Rate sequences R1 and R2 are used during the initial handshake and retrains; R4 and R5 are used during rate renegotiations. The mask written to the appropriate RAM location will be logically ANDed to the out-going rate sequence. A power-on-reset will clear the masks to FFFFh.

Example of Method 1. To request or limit the modem speed to 9600 bps, the host would write 0B91h (see page 4-8 for rate sequence bit assignments) to address 2C0, 2C1 if R1 is to be modified. The same value could be written to address 2C4, 2C5 if R4 is to be modified to limit the speed during a rate renegotiation. The available rates of the remote must be considered by the host before limiting speeds. If the modem determines no common rate is available between both modems during a rate change, the modem will send a clear down and turn off RLSD.

Method 2 Description. The second method for modifying the rate sequence is compatible with the RC144DP and is accomplished through address 204, 205. R1 and R3 are sent by the answering modem and R2 is sent by the originating modem.

To modify R1, the host must write a 0 at this address then wait for the value to equal non-zero. The host then has 1.5 seconds to change R1 (through address 204, 205) before it is sent.

To modify R2, the host must wait until the RSEQ bit is set to a 1 by the DSP. The host then has 1.5 seconds to modify R2 (through address 204, 205).

To modify R3, the host must wait until the RSEQ bit is set to a 1 by the DSP, then change R3 (through address 204, 205).

4-9

In the case of rate renegotiations, R4 (sent by the requesting modem) is modified in the same manner as R3 after setting the RREN bit. R5 (sent by the responding modem) is also modified in the same manner after RREDT is set. The host has approximately 5 ms to modify R4 or R5 after the value in address 204, 205 equals zero.

Typical rate sequences and E sequences shown in Table 4-2 and 4-3. The ARC bit is set on both modems. R1 and R3 are read on the originating modem, R2 is read on the answering modem. Refer to Section 5.3 of CCITT Recommendation V.32/V.32 bis for additional information on the V.32/V.32 bis rate sequence.

Table 4-2. R and E Rate Sequences - V.32 to V.32 (V32BS = 0)

| Originate Set at | R1 (Hex) | R2 (Hex) | R3 (Hex) | E (Hex)<br>(ANS and ORG) | Answering<br>Configuration | Resulting<br>Configuration |

|------------------|----------|----------|----------|--------------------------|----------------------------|----------------------------|

| V.32T/9600       | 0791     | 0791     | 0391     | F391                     | V.32T/9600                 | V.32T/9600                 |

|                  | 0711     | 0711     | 0311     | F311                     | V.32/9600                  | V.32/9600                  |

|                  | 0511     | 0511     | 0511     | F511                     | V.32/4800                  | V.32/4800                  |

| V.32/9600        | 0791     | 0711     | 0311     | F311 .                   | V.32T/9600                 | V.32/9600                  |

|                  | 0711     | 0711     | 0311     | F311                     | V.32/9600                  | V.32/9600                  |

|                  | 0511     | 0511     | 0511     | F511                     | V.32/4800                  | V.32/4800                  |

| V.32/4800        | 0791     | 0511     | 0511     | F511                     | V.32T/9600                 | V.32/4800                  |

|                  | 0711     | 0511     | 0511     | F511                     | V.32/9600                  | V.32/4800                  |

|                  | 0511     | 0511     | 0511     | F511                     | V.32/4800                  | V.32/4800                  |

Table 4-3. R and E Rate Sequences - V.32 bis to V.32 bis (V32BS = 1)

|                  | Table 4-3. |          |          | 7.02 DIS tO 7.02 D       |                         |                            |

|------------------|------------|----------|----------|--------------------------|-------------------------|----------------------------|

| Originate Set at | R1 (Hex)   | R2 (Hex) | R3 (Hex) | E (Hex)<br>(ANS and ORG) | Answering Configuration | Resulting<br>Configuration |

| V.32T/14400      | 0FF9       | 0FF9     | 0999     | F999                     | V.32T/14400             | V.32T/14400                |

|                  | 0FF1       | 0FF1     | 09B1     | F9B1                     | V.32T/12000             | V.32T/12000                |

|                  | 0FD1       | 0FD1     | 0B91     | FB91                     | V.32T/9600              | V.32T/9600                 |

|                  | 0DD1       | 0DD1     | 09D1     | F9D1                     | V.32T/7200              | V.32T/7200                 |

|                  | 0D91       | 0D91     | 0D91     | FD91                     | V.32/4800               | V.32/4800                  |

| V.32T/12000      | 0FF9       | 0FF1     | 09B1     | F9B1                     | V.32T/14400             | V.32T/12000                |

| į                | OFF1       | 0FF1     | 09B1     | F9B1                     | V.32T/12000             | V.32T/12000                |

|                  | 0FD1       | 0FD1     | 0B91     | FB91                     | V.32T/9600              | V.32T/9600                 |

|                  | 0DD1       | 0DD1     | 09D1     | F9D1                     | V.32T/7200              | V.32T/7200                 |

|                  | 0D91       | 0D91     | 0D91     | FD91                     | V.32/4800               | V.32/4800                  |

| V.32T/9600       | 0FF9       | 0FD1     | 0B91     | FB91                     | V.32T/14400             | V.32T/9600                 |

| İ                | 0FF1       | 0FD1     | 0B91     | FB91                     | V.32T/12000             | V.32T/9600                 |

|                  | 0FD1       | 0FD1     | 0B91     | FB91                     | V.32T/9600              | V.32T/9600                 |

| ł                | 0DD1       | 0DD1     | 09D1     | F9D1                     | V.32T/7200              | V.32T/7200                 |

| İ                | 0D91       | 0D91     | 0D91     | FD91                     | V.32/4800               | V.32/4800                  |

| V.32T/7200       | 0FF9       | 0DD1     | 09D1 °   | F9D1                     | V.32T/14400             | V.32T/7200                 |

|                  | 0FF1       | 0DD1     | 09D1     | F9D1                     | V.32T/12000             | V.32T/7200                 |

| 1                | 0FD1       | 0DD1     | 09D1     | F9D1                     | V.32T/7200              | V.32T/7200                 |

| Ç.               | 0DD1       | 0DD1     | 09D1     | F9D1                     | V.32T/7200              | V.32T/7200                 |

|                  | 0D91       | 0D91     | 0D91     | FD91                     | V.32/4800               | V.32/4800                  |

| V.32/4800        | 0FF9       | 0D91     | 0D91     | FD91                     | V.327/14400             | V.32T/4800                 |

|                  | 0FF1       | 0D91     | 0D91     | FD91                     | V.32T/12000             | V.32T/4800                 |

| İ                | 0FD1       | 0D91     | 0D91     | FD91                     | V.32T/9600              | V.32T/4800                 |

|                  | 0DD1       | 0D91     | 0D91     | FD91                     | V.32T/7200              | V.32T/4800                 |

| ļ                | 0D91       | 0D91     | 0D91     | FD91                     | V.32/4800               | V.32/4800                  |

Functions 3-11: Dialing Parameters

Acc. Method: See Below

Addr.: See Below

For Functions 3, 4, 7, 8, and 9, the time T (in ms) is calculated as follows:

Equation:

$N = T \times 2.4$

Where: N is the decimal value of the hex number written to RAM (1-FFh).

A value of 0000 for the DTMF or calling tone on time will cause the modem to transmit the tone continuously until FFh is written into TBUFFER.

For functions 10 and 11, the time (in ms) is calculated as follows:

Equation:

N = T/10

For Functions 5 and 6, the DTMF low band or high band power level (P) in dBm is calculated as follows:

Equation

$N = \log - 1(P/20) \times 10143$

Where: N is the decimal value of the hex number written to RAM.

#### Notes:

The compromise equalizer is automatically disabled by the transmitter when sending DTMF tones, single tones, or dual tones. The DTMF levels are not affected by the transmit level bits (TLVL). The calling tones, however, are affected by the TLVL bits.

2. Maximum output power = -0.5 dBm.

The dialing parameters and their default values are:

| Function | Parameter                  | Method | Address  | Default (Hex) | Default (Dec) |

|----------|----------------------------|--------|----------|---------------|---------------|

| 3        | DTMF Tone Duration         | 2      | 218, 2DB | 00DD          | 92 ms         |

| 4        | DTMF Interdigit Delay      | 2      | 219, 2DC | 00AD          | 72 ms         |

| 5        | DTMF Low Band Power Level  | 2      | 29B, 29C | 19C0          | – 4.0 dBm     |

| 6        | DTMF High Band Power Level | 2      | 29D, 29E | 2085          | - 2.0 dBm     |

| 7        | Pulse Relay Make Time      | 1      | 22C      | 56            | 36 ms         |

| 8        | Pulse Relay Break Time     | 1      | 21C      | 99            | 64 ms         |

| 9        | Pulse Interdigit Delay     | 2      | 21A, 21B | 0708          | 750 ms        |

| 10       | Calling Tone On Time       | 2      | 290, 2D9 | 0032          | 500 ms        |

| 11       | Calling Tone Off Time      | 2      | 291, 2DA | 00C8          | 2 sec         |

Some DTMF power level values are:

| L (dBm)    | N (Hex) |

|------------|---------|

| -1         | 2350    |

| -2         | 1F78    |

| <b>-</b> 3 | 1C0C    |

| -4         | 1900    |

| <b>-</b> 5 | 1648    |

| -6         | 13DB    |

**Transmitter Output Level Gain-All Modes**

Acc. Method: 3

Addr.: A48

Transmitter Output Level Gain-FSK Modes Acc. Method: 3 Addr.: B57

a. Transmitter Output Level Gain-All Modes (Addr. A48)

The transmitter output level gain constant (G) in dBm is calculated as follows:

Equation:

N = log-1 [G/20] x 16384

Where: N is the decimal value of the hex number written to RAM.

Range:

0 - 7FFFh

Default:

4000h

The transmitter output level gain constant directly controls the output level of all configurations. It is used for fine tuning the output level which is controlled by the TLVL bits. Therefore,

Output Level = TLVL Setting + Transmitter Output Gain in dBm

Example gain values are:

| G (dBm) | N (Hex) | G (dBm) | N (Hex) |

|---------|---------|---------|---------|

| +6      | 7FB2    | -8      | 197A    |

| +5      | 71CF    | -9      | 16B5    |

| +4      | 656E    | -10     | 143D    |

| +3      | 5A67    | -11     | 1209    |

| +2      | 5092    | -12     | 1013    |

| +1      | 47CF    | -13     | 0E53    |

| 0       | 4000    | -14     | 0CC5    |

| -1      | 390A    | -15     | 0B61    |

| -2      | 32D6    | -16     | 0A24    |

| -3      | 2D4E    | -17     | 090A    |

| -4      | 2861    | -18     | 080E    |

| -5      | 23FD    | -19     | 072E    |

| -6      | 2013    | -20     | 0666    |

| -7      | 1C96    | -21     | 05B4    |

For example, if TLVL is set for -9 dBm and the required level is -30 dBm, the difference is -21 dBm. Therefore, load address A48 with 5B4h.

The dynamic range of the scale factor is effective from +6 dB down to approximately -60 dB, with a resolution of 0.5E-3 dB. Setting NEWC to a 1 will reset this parameter to the default value.

## b. Transmitter Output Level Gain-FSK Modes (Addr. B57)

Equation:

$N = log - 1 [PO/20] \times C$

Where: PO is based on TLVL = 9 and transmit output gain constant (all modes) and A48 = 4000h.

N is the decimal value of the hex number written to RAM.

C = See the following table:

| Configuration | CEQ     | C (Dec) - Answer | C (Dec) -Originate |

|---------------|---------|------------------|--------------------|

| V.21          | CEQ = 1 | 9728             | 10608              |

| · <del></del> | ©EQ = 0 | 8448             | 8448               |

| Bell 103      | CEQ = 1 | 9072             | 10496              |

|               | CEQ = 0 | 8704             | 8352               |

| V.23/1200 TX  | CEQ = 1 | 12800            | 12800              |

|               | CEQ = 0 | 12544            | 12544              |

| V.23/75 TX    | CEQ = 1 | 10496            | 10496              |

|               | CEQ = 0 | 8448             | 8448               |

Setting NEWC to a 1 will reset this parameter to the default value.

Function 13: Dual Tone 1 Frequency

Function 14: Dual Tone 2 Frequency

Acc. Method: 2

Acc. Method: 2

Addr.: 280, 281 Addr.: 282, 283

Frequency F (in Hz) is calculated as follows:

Equation: N = F/0.109863

Where: N is the decimal value of the hex number written to RAM.

Default = C

A single or dual tone is transmitted by writing 80h (single tone) or 83h (dual tone) to the CONF register, programming the tone transmit location in RAM, and then activating RTS. The tone will be transmitted as long as RTS is active.

#### Example values are:

| F (Hz) | N (Hex) | F (Hz) | N (Hex) |

|--------|---------|--------|---------|

| 400    | 0E39    | 2100   | 4AAB    |

| 445    | 0FD2    | 2250   | 5000    |

| 600    | 1555    | 2400   | 5555    |

| 1200   | 2AAB    | 3000   | 6AAB    |

| 1800   | 4000    | 3600   | 8000    |

Function 15:

**Dual Tone 1 Power Level**

Acc. Method: 2

Addr.: 284, 285

Function 16:

Dual Tone 2 Power Level

Acc. Method: 2

Addr.: 286, 287

Dual tone power level in dBm (PO) is calculated as follows:

Equation:

N = 22304 [ $10^{\text{Po}/20}$ ] (Based on TLVL = 0 and 600  $\Omega$  termination.)

Where: N is the decimal value of the hex number written to RAM.

Range:

0 - 7FFFh (Default = 2000h)

#### Notes:

- 1. The modem accepts change only when RTS is off.

- 2. The Transmit Level bits (TLVL) affect output level.

- 3. Power out = PO + TLVL setting + transmitter output gain constant.

Function 17A: New Status (NEWS) Masking Registers Function 17B: Memory Access Masking Register

Acc. Method: See Table 4-1 Addr.: See Below

Acc. Method: 1

Addr.: 089 (Bit 6)

Writing a 1 in the bit location corresponding to the desired bit will cause NEWS to go active when a status change occurs for the selected bit. All bits default to 0 at power-on-reset. Figure 4-5 shows the applicable masking register bits.

In addition, address 089 (bit 6) controls memory access interrupt (set bit 6 to clasable interrupt; reset bit 6 to enable interrupt).

| Register | 1                |                                                             |                  | В                | it              |                 |        |       | Mask Address   |

|----------|------------------|-------------------------------------------------------------|------------------|------------------|-----------------|-----------------|--------|-------|----------------|

| Address  | 7                | 6                                                           | 5                | 4                | 3               | 2               | 1      | 0     | (Hex)          |

| 1B       | EDET             | DTDET                                                       | OTS              | DTMFD            |                 | DTM             | IFW    |       | 27C            |

| 1A       | <b>—</b>         |                                                             |                  | _                | DTMFW           | SCOBF           | SCIBE  | -     | 27D            |

| 17       |                  | Secondary Transmit Data Buffer/V.34 Transmit Status(SECTXB) |                  |                  |                 |                 |        |       | 371            |

| 16       | 1                |                                                             |                  |                  |                 | e Status (SE    |        |       | 370            |

| 14       | †                | ASCODE                                                      |                  |                  |                 |                 |        | 38A   |                |

| 12       |                  | Configuration (CONF)                                        |                  |                  |                 |                 |        |       | 089, bit 7 = 1 |

| 0F       | ALSD             | FED                                                         | CTS              | DSR              | RI              | TM              | RTSDT  | V54DT | 241            |

| 0E       | RTDET            | BRKD                                                        | RREDT            | V32BDT           |                 | SPE             | ED     |       | 242            |

| 0D       | P2DET            | PNDET                                                       | S1DET            | SCR1             | U1DET/<br>ECTRN | SADET/<br>DETID | TXFNE  | HKAB  | 243            |

| 0C       | AADET/<br>PROBED | ACDET/<br>MODEOK                                            | CADET/<br>NEGDET | CCDET/<br>DET800 | SDET            | SNDET           | RXFNE  | RSEQ  | 244            |

| 08       | TONEA            | TONEB                                                       | TONEC            | ATV25            | ATBEL           |                 | DISDET | EQMAT | 245            |

| 0A       | PNSUC            | FLAGDT                                                      | PE               | FE               | OE              | CRCS            | FLAGS  | SYNCD | 246            |

| 01       |                  | _                                                           | _                | _                | -               | TXHF            | RXHF   |       | 247            |

Figure 4-5. NEWS Masking Registers

Function 22: Far-End Echo Frequency Offset

Acc. Method: 4

Addr.: 852

Function 22 provides the far-end echo frequency offset (FO), sometimes known as phase roll, in V.34/V.FC/V.32 configurations.

Equation:

$FO = (N * SYMBOL RATE)/2^{22}$

Where: SYMBOL RATE = 2400, 2800, 3000, 3200, or 3429 (V.34/V.FC) (See Function 60.)

2400 (V.32 bis)

N is the decimal value of the hex number read from RAM.

Function 22 is a 16-bit 2s complement number. It is not valid until rate sequence R3 is detected in the originate modem, or rate sequence R2 is detected in the answer modem for V.32 or until RLSD = 1 for V.34 and V.FC.

Function 23: Far-End Echo Level

Acc. Method: 4

Addr.: B52

Function 23 provides the far-end echo power level at RXA in V.34/V.FC/V.32 configurations.

The following table lists average values read from RAM and the corresponding far end echo level in dBm:

| Echo Level (dBm) | V.34/V.FC Average Value (Hex) | V.32 bis Average Value (Hex) |

|------------------|-------------------------------|------------------------------|

| -8               | 1100                          | 1300                         |

| -9               | 0F00                          | 1100                         |

| -10              | 0D00                          | 0F00                         |

| -11              | 0000                          | 0D00                         |

| -12              | 0A00                          | 0C00                         |

| -13              | 0900                          | <b>0</b> A00                 |

| -15              | 0700                          | 0800                         |

| -20              | 0400                          | 0500                         |

| -25              | 0250                          | 0300                         |

| -30              | 0150                          | 0180                         |

| -35              | 0000                          | 00D0                         |

| -40              | 0070                          | 0080                         |

| -45              | 0045                          | 0040                         |

Note: Function 23 is not valid until RLSD is ON.

Function 24: CTS OFF-to-ON Response Time (RTS-CTS Delay)

Acc. Method: 2

Addr.: 202, 203

Function 24 determines the CTS off-to-on response time in 2-wire full-duplex configurations.

The response time equations and default values are:

| Configuration             | Equation                          | Default Value (Hex) | Default Value (Dec) |

|---------------------------|-----------------------------------|---------------------|---------------------|

| V.34, V.FC, V.32          | N = (Response time x 2.4 ms) -1   | 0000                | 0.4 ms              |

| V.22 bis, V.22, Bell 212A | N = (Response time x 0.6 ms) -1   | 0000                | 3 ms                |

| Bell 103                  | N = (Response time x 0.298 ms) -1 | 003F                | 215 ms              |

| V.21                      | N = (Response time x 0.298 ms) -1 | 0098                | 525 ms              |

| V.23/1200Tx               | N = Response time x 1.2 ms        | 00FC                | 210 ms              |

| V.23/75Tx                 | N = Response time x 0.072 rns     | 0010                | 235 ms              |

Example: For an RTS-CTS delay of 20 ms in V.22 bis, N = [(20)(0.6)]-1 = 11 = 000Bh.

Note: Response time may vary by ± 2 baud times.

Function 25:

**Answer Tone Length**

Acc. Method: 2

Addr.: 228, 229

Function 26:

Silence After Answer Tone Period

Acc. Method: 2

Addr.: 22A 22B

The CCITT 2100 Hz answer tone length and silence after answer tone are calculated as follows:

| Configuration                      | Equation                                                   |  |  |  |

|------------------------------------|------------------------------------------------------------|--|--|--|

| V.8, V.FC, V.32, V.21, Bell 103    | N = T x 300 (V.32 silence: N = T x 2400)                   |  |  |  |

| V.22 bis, V.22, Bell 212           | N = T x 600                                                |  |  |  |

| V.23/75Tx, V.23/1200Rx N = T x 75  |                                                            |  |  |  |

| V.23/1200Tx, V.23/75Rx             | N = T x 1200                                               |  |  |  |

| Where: N is the decimal value of t | he hex number written to RAM and T is the time is seconds. |  |  |  |

The modem will rewrite the default values when DTR is turned off or the NEWC bit is set.

The end of answer tone transmission may be determined by monitoring address 051, bit 3. This bit will be set to a 1 when the answer has finished and the silence period has commenced. Unless a power-on reset is performed, this bit must be reset by the host if it is to be monitored again on the following connection.

Note: Address 228, 229 lengthens individual phase reversal times in V.8, V.FC/V.32 bis/V.32. The answer tone length may be adjusted by increasing or decreasing the number of phase reversals at address 04B. The default value at address 04B is 08h (8 phase reversals). This value may be changed only after DTR is set.

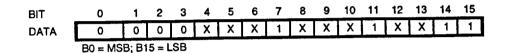

## Functions 27 - 29: Tone Detector Bandpass Filter Coefficients

Acc. Method: 3

Addr.: See Table 4-4

A block diagram of the three tone detectors is shown in Figure 4-6. Tone detector C is preceded by a prefilter and a squarer. The purpose of the prefilter and squarer is to allow dual tones to be detected while rejecting the main channel energy. For example, TONEC can be programmed to detect a difference frequency generated by the squarer for detection of 350 Hz and 440 Hz. The prefilter would be designed to reject the energy in the 600 to 3000 Hz band. If the dual tone pair of 350 and 440 Hz appeared (or any other frequency pair in the range of 300 to 600 Hz with a difference of 90 Hz) TONEC would turn on.

The SQDIS bit (02:6) allows the squarer in front of tone detector C to be disabled. If the squarer is disabled then tone detector C will have four cascaded biquads (since there is a prefilter consisting of two biquads), forming an 8-order IIR filter with user programmable coefficients. To make the prefilter transparent (to use TONEC as a 4th order filter), write 7FFFh in coefficients A1 and write 0000 to all other biquad coefficients.

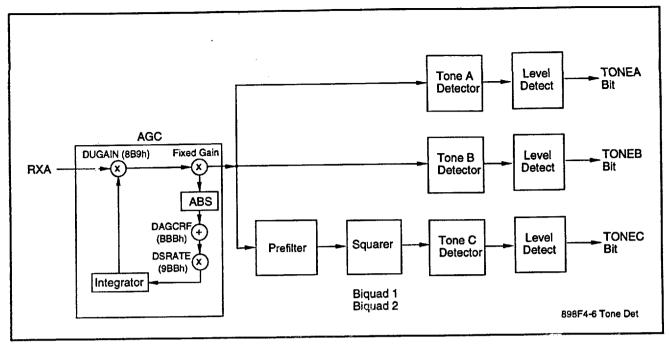

The implementation of the filters allows user definition of the characteristics of the prefilter and the three tone detectors. Table 4-4 provides the DSP RAM address codes for the filter coefficients. Table 4-5 shows the default values. Figure 4-6 shows that the prefilter and the main filter sections of the tone detectors are fourth order (two second-order biquads in cascade), thereby allowing a wide variety of filter characteristics to be synthesized. The only limitation on these user-definable shapes is that their gain should be around unity at the pass frequencies to avoid problems of saturation at one extreme (gain too high) and digital noise at the other (gain too low). Computation of the filter coefficients can be performed by any infinite impulse response (IIR) filter design program which outputs the coefficients in cascaded second-order sections.

The default sample rate is 7200 Hz, however, in the V.8, V.34, or V.FC modes, the sample rate is changed to 9600 Hz and all filter coefficients are changed by the modem. A soft or hard reset is recommended after a V.34 or V.FC connection to restore default filter coefficients.

The level detector in each of the tone detectors flags the detection of a tone if it is in the tone detector passband and if it is above an upper threshold defined by THRESHU. The tone detected flag will remain set until, or unless, the tone falls below a lower threshold defined by THRESHL.

The tone detectors are preceded by an AGC. The gain of the AGC may be read at address 8B9 (DUGAIN). By default, DUGAIN reaches its maximum gain, at a value of 7FFFh, when the receive level is -26 dBm or lower. Signal levels below -26 dBm are thus not affected by the AGC, therefore, the threshold comparator will see a decreasing signal level as the input signal is lowered. The THRESHU and THRESHL adjustments are limited to signal levels below the AGC cut-off point (-26 dBm). If the THRESHU value is adjusted to try to limit the detection threshold to -20 dBm, the AGC will not allow it.

To raise the AGC cut-off point, decrease the value in address BBB (DAGCRF). The DAGCRF default value is FF00h, which results in the -26 dBm cut-off. Decreasing DAGCRF to FE00h raises the AGC cut-off to -20 dBm, thus allowing THRESHU to be adjusted for a minimum detection level of -20 dBm or lower.

The AGC may be disabled by first writing 0 to address 9BB (DSRATE), then writing a 07FFh to address 8B9 (DUGAIN).

The first-order low pass filter in each level detector, defined by the coefficients LPGAIN and LPFBK, controls the response time of each tone detector. Normally, these coefficients will not require alteration, but if, for example, a rapid cadence must be detected on a tone, then the 3 dB cutoff is approximately the reciprocal of the on-time or off-time of the tone, whichever is shorter. Decreasing LPFBK will speed up the response time. If LPFBK is decremented, then LPGAIN should be increase by the same amount. The gain of the filter should be set to unity (LPGAIN + LPFBK ≈ 7FFFh). The default response time is in the order of 0.01 seconds.

Figure 4-6. Tone Detectors

Table 4-4. TONEA, TONEB, and TONEC DSP RAM Addresses

|           | TO      | NEA     | TO      | NEB     | TO      | NEC     | Pre     | filter  |

|-----------|---------|---------|---------|---------|---------|---------|---------|---------|

| Parameter | Biguad1 | Biguad2 | Biquad1 | Biquad2 | Biquad1 | Biquad2 | Biquad1 | Biquad2 |

| A3        | AA1     | BA1     | AA7     | BA7     | AAD     | BAD     | AB2     | BB2     |

| A2        | AA2     | BA2     | AA8     | BA8     | AAE     | BAE     | AB3     | BB3     |

| A1        | AA3     | BA3     | AA9     | BA9     | AAF     | BAF     | AB4     | BB4     |

| B2        | AA4     | BA4     | AAA     | BAA     | AB0     | BB0     | AB5     | BB5     |

| B1        | AA5     | BA5     | AAB     | BAB     | AB1     | BB1     | AB6     | BB6     |

Table 4-5. TONEA, TONEB, and TONEC Default Values

|           | TONEA TONEB |             | TONEC   |             |         |             |

|-----------|-------------|-------------|---------|-------------|---------|-------------|

| Parameter | Address     | Value (Hex) | Address | Value (Hex) | Address | Value (Hex) |

| LPFBK     | BA0         | 7F30        | BA6     | 7E67        | BAC     | 7F30        |

| LPGAIN    | AAO         | 00CF        | AA6     | 02DF        | AAC     | 00CF        |

| THRESHU   | AB8         | 0880        | AB9     | 2A00        | ABA     | 1600        |

| THRESHL   | BB8         | 0580        | BB9     | 1C00        | BBA     | 0A00        |

#### Example:

A call-progress tone detector is required for the US telephone network to detect appropriate tones that exceed -35 dBm.

The requirement can be met by detecting tones in the 245 Hz-650 Hz range. A bandpass filter with a passband of 245 Hz-650 Hz must be designed. Any filter up to fourth order can be implemented and, normally, it is best to choose the highest order available, especially for bandpass designs. A biquad filter design package could carry out this function by defining the passband frequencies, the filter order, the filter gain (chose unity), and the filter sampling rate (7200 Hz). An example of suitable coefficients is:

| Function | A1     | A2      | A3     | B1     | B2      |

|----------|--------|---------|--------|--------|---------|

| Biquad 1 | 0.1368 | -0.2736 | 0.1368 | 1.8281 | -0.8835 |

| Biquad 2 | 0.1368 | 0.2736  | 0.1368 | 1.5716 | -0.7920 |

These values should first be divided by two because coefficients greater than one are unrealized in the actual filter implementation. This division should be done even if none of the coefficients in the design are greater than one. This is because the biquad sections have been implemented as shown in Figure 4-7. The modified values are, therefore:

| Function | A1'    | A2'     | A3'    | B1'    | B2'     |

|----------|--------|---------|--------|--------|---------|

| Biquad 1 | 0.0684 | -0.1368 | 0.0684 | 0.9140 | -0.4418 |

| Biquad 2 | 0.0684 | 0.1368  | 0.0684 | 0.7858 | -0.3960 |

Next, convert the above numbers to fractional 2s complement numbers. In this case, the default coefficient values for TONEA:

| Function | A1'  | A2'  | A3'  | B1'  | B2'  |

|----------|------|------|------|------|------|

| Biquad 1 | 08C2 | EE7C | 08C2 | 74FE | C774 |

| Biquad 2 | 08C2 | 1184 | 08C2 | 6495 | CD4F |

The second part of the requirement is to detect tones that exceed -35 dBm. The approximate values of THRESHU and the corresponding tone level detected for TONEA at 500 Hz are:

| THRESHU (Hex) | Tone Level Detected (dBm) |

|---------------|---------------------------|

| 1100          | -29                       |

| 0000          | -32                       |

| 0880          | <b>–35</b>                |

| 0600          | -38                       |

THRESHU should be 0880h. If no hysteresis is required in the tone detector, then set THRESHL to 0880h (see Table 4-5). If hysteresis is required, then make THRESHL < THRESHU. Threshold levels stated in the data sheets are measured at the band edges. Other filter designs may require different values to those shown above. Note that changing threshold coefficients may change the bandwidth response of tone detectors.

Table 4-6 shows the filter coefficient values for specific filters. Adjust THRESHL and THRESHU as necessary (see Table 4-5).

Figure 4-7. Biquad Filter and Level Detector

Table 4-6. Example Tone Detector Filter Coefficients

|                           |      | Biquad1 Coefficients (Hex) |      |      |      | Biquad2 | Coefficie | nts (Hex) |      |      |

|---------------------------|------|----------------------------|------|------|------|---------|-----------|-----------|------|------|

| Sampling Rate/Filter      | A3   | A2                         | A1   | B2   | B1   | A3      | A2        | A1        | B2   | B1   |

| 7200 Hz                   |      |                            |      |      |      |         |           |           |      |      |

| (Non-V.FC Modes)          |      |                            |      |      |      |         |           |           |      |      |

| 1100 Hz                   | 01B3 | FC9C                       | 01B4 | C147 | 48C6 | 01B3    | 0097      | 01B4      | C147 | 4897 |

| 1800 Hz                   | 0184 | FCFB                       | 0185 | C147 | 001C | 0184    | 01BD      | 0185      | C147 | FFE4 |

| 2250 Hz                   | 0205 | FBF9                       | Ç206 | C147 | CF9C | 0205    | 0380      | 0206      | C147 | CF68 |

| 2100 Hz                   | 01E8 | FC32                       | 01E9 | C167 | DF4F | 01E8    | 034E      | 01E9      | C147 | DF19 |

| 2225 Hz                   | 0205 | FBF9                       | 0206 | C147 | D22D | 0205    | 0380      | 0206      | C147 | D1F8 |

| 1270 Hz                   | 02B2 | FAA1                       | 02B3 | C147 | 38A4 | 02B2    | 00F0      | 02B3      | C147 | 3871 |

| 1650 Hz                   | 0306 | F9F9                       | 0307 | C147 | 10A6 | 0306    | 010D      | 0307      | C147 | 106E |

| 980 Hz                    | 0205 | FBF9                       | 0206 | C147 | 5337 | 0205    | 00B4      | 0206      | C147 | 530D |

| 1300 Hz                   | 0244 | FB7B                       | 0245 | C147 | 35A7 | 0244    | 00CA      | 0245      | C147 | 3574 |

| 245-650 Hz <sup>1</sup>   | 08C2 | EE7C                       | 08C2 | C774 | 74FE | 08C2    | 1184      | 08C2      | CD4F | 6495 |

| 360-440 Hz <sup>2</sup>   | 0000 | FD36                       | 02CA | C63E | 7243 | 02CA    | 0593      | 02CA      | C63E | 7243 |

| 9600 Hz                   |      |                            |      |      |      |         |           |           |      |      |

| (V.8, V.34, & V.FC Modes) |      |                            | l    | 1    |      |         |           |           |      |      |

| 1800 Hz                   | 0372 | FEA6                       | 0372 | C063 | 30D6 | 00C4    | FFDA      | 00C4      | C063 | 30D6 |

| 2250 Hz                   | 0119 | FE72                       | 0130 | C063 | 0C82 | 02D9    | FEE3      | 02D9      | C063 | 0C82 |

| 2100 Hz                   | 0397 | F8D3                       | 0399 | C3C9 | 1905 | 0397    | 02C0      | 0399      | C3C9 | 176  |

| 2225 Hz                   | 0884 | EF47                       | 0889 | C147 | 0E90 | 0884    | FE54      | 0889      | C147 | 0266 |

| 1270 Hz                   | 0123 | FDBA                       | 0123 | C147 | 55B6 | 0123    | 00DF      | 0123      | C147 | 5596 |

| 1650 Hz                   | 028B | FAEA                       | 028C | C289 | 3BDA | 028B    | 01F3      | 028C      | C289 | 3A68 |

| 980 Hz                    | 0224 | FBB8                       | 0225 | C289 | 64FF | 0224    | 01A4      | 0225      | C289 | 6403 |

| 1300 Hz                   | 0112 | FDDB                       | 0113 | C147 | 536D | 0112    | 00D2      | 0113      | C147 | 5330 |

| 245-650 Hz                | F8EA | 0000                       | 0716 | C63E | 6FE1 | 0716    | F5FB      | 0716      | C774 | 7601 |

| 360-440 Hz                | 01AA | FEBC                       | 01AA | C7CD | 7438 | FF5C    | 0000      | 00A4      | C148 | 7A60 |

#### Notes:

- 1. TONEA default.

- TONEB default.

Function 30: RLSD Drop Out Timer Acc. Method: 1 Addr.: 270, 271

## a. VFC, V.32 bis, V33, V17, V29, V27, V.26 and V.21 channel 2

RAM address 270, 271 holds the value for a 16-bit counter which decrements at a baud interval when energy is removed from RXA. When the counter reaches 0000, RLSD turns off. The count down may be observed in RAM addresses 389 (value from address 388) and 046 (value from address 270). The value in address 271 (MSB), 270 (LSB) may be changed anytime after RLSD = 1. The default time may be read in address 271, 270 after RLSD = 1. See Table 1-1 to obtain baud rates for individual modes. By prolonging the RLSD on-off time, the modem can be kept in a freeze mode which can be used to bridge long dropouts. Dropouts of several seconds can be bridged by extending this timer. The default RLSD on-off time for V.FC and V.32bis is approximately 500 ms. Note that in VFC and V.32 bis modes, it is possible for the receiver to lock onto the local transmit signal when the received signal is lost. (See the DISDET description in Table 3-1.)

#### b. V.22 bis, V.22. Bell 212/1200

The 8-bit value in RAM address 270 controls the RLSD on-off time. The value counts down to 0 in address 046. Once this value starts to decrement, after the signal has been removed from RXA, the host may continuously write a large value in address 046, not allowing the counter to decrement, in order to prolong the RLSD on-off time if the 8-bit counter is not sufficient. This, however, requires the host to monitor address 046 during the connection until it starts to decrement.

The 8-bit value in RAM address 271 controls the time the modem will wait for energy to return after RLSD has turned off. This value is loaded into address 049 and starts to count up until it reaches a value of 63h. The default value in address 271 is 0 which gives the maximum freeze time of 63h bauds. After RLSD = 0, the host may continuously write 00 in address 049, not allowing the counter to increment, in order to prolong the freeze time. Both addresses 271 and 270 may be written to after RLSD = 1.

| Function 31: | RLSD Turn-On Threshold (RLSD_ON)   | Acc. Method: 2 | Addr.: 134, 135    |

|--------------|------------------------------------|----------------|--------------------|

| Function 32: | RLSD Turn-Off Threshold (RLSD_OFF) | Acc. Method: 2 | Addr.: 136, 137    |

|              | RLSD Threshold Offset              | Acc. Method: 2 | Addr.: 138, 139    |

|              | RLSD Overwrite Control             | Acc. Method: 1 | Addr.: 10D (Bit 2) |

|              | Extended RTH Control               | Acc. Method: 1 | Addr.: 10D (Bit 6) |

|              | Receiver Gain                      | Acc. Method: 1 | Addr.: A03         |

|              | Receiver Turn-off Threshold        | Acc. Method: 3 | Addr.: A04         |

|              | Receiver Turn-on Threshold         | Acc. Method: 3 | Addr.: A05         |

The receive RLSD thresholds may be modified by altering the internal receiver gain (address A03) or threshold values (address A04, A05) to shift the turn-on and or turn-off threshold up or down.

#### Method 1

A control bit (address 10D, bit 2) enables or disables the over-writing of the RLSD thresholds by the modem's own default threshold table [0 = overwriting enabled (default); 1 = overwriting disabled]. The default state is initialized only by power on or a soft reset.

The RLSD thresholds are loaded into memory locations RLSD\_ON and RLSD\_OFF. During the Idle mode initialization, the 2-byte value stored in RLSD\_ON is used as the RLSD on threshold. When the modem is in Data mode, the 2-byte RLSD\_OFF value is used for the RLSD off threshold.

During reset, the respective thresholds for V.32 bis 14400 bps are loaded into RLSD\_ON and RLSD\_OFF as initial values. After reset, the host may then alter these values using the following procedure:

- 1. Set 10D, bit 2 (to prevent custom values from being overwritten by default values).

- 2. Load in the custom RLSD values.

- Set NEWC.

Note: the thresholds can be over-written at any time, but this method ensures that the first connection after a NEWC uses the correct value of ON threshold.

### Extended RLSD Threshold Selection:

The Extended RTH bit (XRTH) (address 10D, bit 6) controls the reduction of RLSD thresholds by approximately 5 dBm [0 = disables reduction (default); 1 = enables reduction]. If XRTH is a 1, RTH must be reset to 0. This extended RLSD threshold method affects all configurations while preserving the hysteresis.

The amount of threshold reduction (offset) can be controlled manually by the host writing a 16-bit offset value into address 138, 139. For example, this offset is useful for compensating for any loss or gain that may be introduced by the DAA/hybrid used. Note that if a negative offset is wanted, then the twos complement number should be entered. The maximum amount of offset that can safely be subtracted is 900h (F700h, 2s complement).

1026 4-19

#### Method 2

The RTH bit field selects a default threshold setting for the modem's receiver (see RTH description in Table 3-1). The receiver gain is adjusted automatically for each of the four RTH values and switches between a turn-on and a turn-off value depending if the modem is in an idle mode (RLSD off) or connect mode (RLSD on). A threshold offset is associated with each RTH setting (see Function 32) which in turn offsets the receiver gain by a given amount. The higher the gain value, the higher the threshold. The following are the RTH offset RAM addresses and the corresponding default offset.

| RTH Code | Parameter   | Method | Address (Hex) | Default (Hex) |

|----------|-------------|--------|---------------|---------------|

| 0        | RTH0 Offset | 2      | 2D0, 2D1      | 0000          |

| 1        | RTH1 Offset | 2      | 2D2, 2D3      | 1AC0          |

| 2        | RTH2 Offset | 2      | 2D4, 2D5      | 2CC0          |

| 3        | RTH3 Offset | 2      | 2D6, 2D7      | 4640          |

Note: A power-on-reset will return the offset values to their default states.

The following are the default idle receiver gain values (turn-on values) for the corresponding modes. The gain values are increased by the modern when in data mode. In V.34, V.FC, and V.32 bis configurations, this value may change several times during the handshake.

|                | Gain Value (Hex) in Address A03h * |           |  |  |

|----------------|------------------------------------|-----------|--|--|

| Mode           | Answer                             | Originate |  |  |

| V.34           | OAAF                               | 0AAF      |  |  |

| V.FC           | 1070                               | 1A08      |  |  |

| V.32bis, V.32  | 186E                               | 1533      |  |  |

| V.22 bis       | 13F9                               | 16B2      |  |  |