## NS32FX100-15/NS32FX100-20/NS32FV100-20/ NS32FV100-25/NS32FX200-20/NS32FX200-25 System Controller

### General Description

The NS32FX200, NS32FV100 and NS32FX100 are highly integrated system chips designed for a FAX system based on National Semiconductor's embedded processors—NS32FX161, NS32FV16 or NS32FX164. The NS32FX100 is the common core for all three system chips. The NS32FV100 and NS32FX200 offer additional functions. Throughout this document, references to the NS32FX100 also apply to both the NS32FV100 and the NS32FX200. Specific NS32FV100 or NS32FX200 features are explicitly indicated.

The NS32FX200, NS32FV100 and NS32FX100 feature an interface to devices like stepper motors, printers and scanners, a Sigma-Delta CODEC, an elapsed-time counter, a DMA controller, an interrupt controller, and a UART.

The NS32FX200 is optimized for high-end FAX applications, such as plain-paper FAX and multifunctional peripherals. The NS32FX100, is optimized for low-cost FAX applications. The NS32FV100 is optimized for thermal paper FAX machines with Digital Answering Machine support.

### Features

- Direct interface to the NS32FX161, NS32FV16 and NS32FX164 embedded processors

- Supports a variety of Contact Image Sensor (CIS) and Charge Coupled Device (CCD) scanners

- Direct interface to a variety of Thermal Print Head (TPH) printers. Bitmap shifter and DMA channels facilitate the connection of other types of printers

- Supports two stepper motors

- Direct interface to ROM and SRAM. The NS32FX200 and NS32FV100, in addition, interface to DRAM devices

- Programmable wait state generator

- Demultiplexed address and data buses

- Multiplexed DRAM address bus (NS32FX200 and NS32FV100)

- Supports 3V freeze mode by maintaining only elapsed time counter

- Control of power consumption by disabling inactive modules and reducing the clock frequency

- Operating frequency

- Normal mode: 19.6608 MHz—24.576 MHz in steps of 1.2288 MHz. (NS32FX200)

- Normal mode: 19.6608 MHz—24.576 MHz in steps of 1.2288 MHz. (NS32FV100)

- Normal mode: 14.7456 MHz—19.6608 MHz in steps of 1.2288 MHz. (NS32FX100)

- Power Save mode: Normal mode frequency divided by sixteen

- On-Chip full duplex Sigma-Delta CODEC with:

- Total harmonic distortion better than -70 dB

- Programmable hybrid balance filter

- Programmable reception and transmission filters

- Programmable gain control

- On-Chip Interrupt Control Unit with:

- 16 interrupt sources

- Programmable triggering mode

- On-Chip counters, WATCHDOG™, UART, MICROWIRE™, System Clock Generator, and I/O ports

- On-Chip DMA controller (NS32FX200—four channels, NS32FX100, NS32FV100—three channels)

- Up to 37 on-chip general purpose I/O pins, expandable externally

- Flexible allocation of I/O and modules' pins

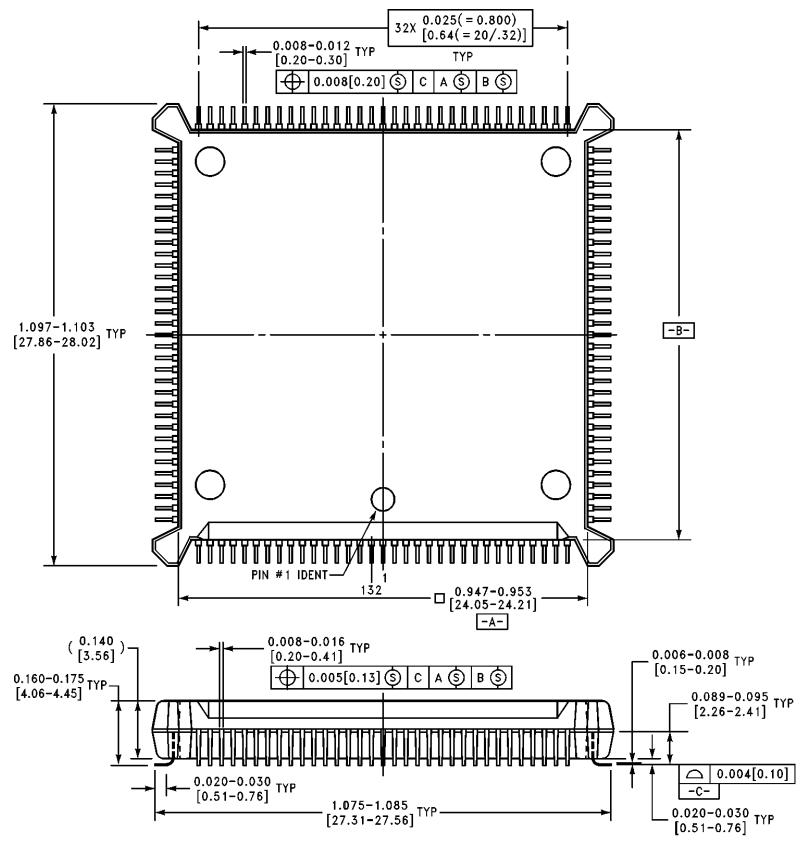

- 132-pin JEDEC PQFP package

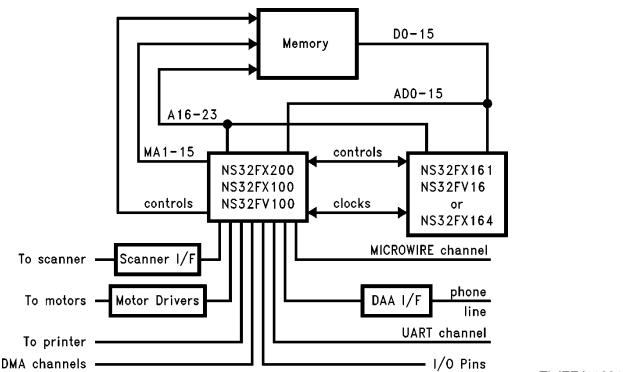

TL/EE/11331-1

**FIGURE 1-1. A FAX Controller Block Diagram**

TRI-STATE® is a registered trademark of National Semiconductor Corporation.

MICROWIRE™ and WATCHDOG™ are trademarks of National Semiconductor Corporation.

## Table of Contents

|                                                                          |           |

|--------------------------------------------------------------------------|-----------|

| <b>1.0 FAX SYSTEM CONFIGURATION</b> .....                                | <b>6</b>  |

| 1.1 Block Diagram Description .....                                      | 6         |

| 1.2 Module Diagram .....                                                 | 7         |

| 1.2.1 Bus and Memory Controller (BMC) .....                              | 8         |

| 1.2.2 Timing Control Unit (TCU) .....                                    | 8         |

| 1.2.3 Sigma-Delta CODEC (SDC) .....                                      | 8         |

| 1.2.4 Scanner Controller (SCANC) .....                                   | 8         |

| 1.2.5 Printer Controller (PRNTC) .....                                   | 8         |

| 1.2.6 DMA Controller (DMAC) .....                                        | 8         |

| 1.2.7 Universal Asynchronous Receiver-Transmitter (UART) .....           | 8         |

| 1.2.8 MICROWIRE (MWIRE) .....                                            | 8         |

| 1.2.9 Interrupt Control Unit (ICU) .....                                 | 8         |

| 1.2.10 Ports .....                                                       | 8         |

| 1.3 Operation Modes .....                                                | 8         |

| 1.3.1 Functionality .....                                                | 9         |

| <b>2.0 ARCHITECTURE</b> .....                                            | <b>10</b> |

| 2.1 MCFG—Module Configuration Register .....                             | 10        |

| 2.2 Timing Control Unit (TCU) .....                                      | 10        |

| 2.2.1 Features .....                                                     | 10        |

| 2.2.2 Operation .....                                                    | 10        |

| 2.2.2.1 External Clocks .....                                            | 11        |

| 2.2.2.2 Internal Clocks .....                                            | 11        |

| 2.2.3 Registers .....                                                    | 12        |

| 2.2.3.1 Usage Recommendations .....                                      | 13        |

| 2.3 Sigma-Delta CODEC (SDC) .....                                        | 13        |

| 2.3.1 Features .....                                                     | 13        |

| 2.3.2 Operation .....                                                    | 13        |

| 2.3.2.1 Block Diagram .....                                              | 13        |

| 2.3.2.2 On-Chip Digital Blocks .....                                     | 15        |

| 2.3.3 Programmable Functions .....                                       | 15        |

| 2.3.3.1 Sigma-Delta ON/OFF .....                                         | 15        |

| 2.3.4 Off-Chip Analog Circuits .....                                     | 15        |

| 2.3.4.1 Analog Transmitter .....                                         | 17        |

| 2.3.4.2 Analog Receiver .....                                            | 17        |

| 2.3.5 Registers .....                                                    | 17        |

| 2.3.6 Usage Recommendations .....                                        | 18        |

| 2.4 Scanner Controller (SCANC) .....                                     | 18        |

| 2.4.1 Features .....                                                     | 18        |

| 2.4.2 Operation .....                                                    | 18        |

| 2.4.2.1 Scanner Signals Generator Block ..                               | 19        |

| 2.4.2.2 Scanner Period Pulse (SPP) Generation .....                      | 20        |

| 2.4.2.3 Video Handling Block .....                                       | 21        |

| 2.4.2.4 Threshold DAC (Dithering and Automatic Background Control) ..... | 22        |

| 2.4.2.5 Stepper Motor Control Block .....                                | 23        |

| <b>2.0 ARCHITECTURE (Continued)</b>                                      |           |

| 2.4.3 Registers .....                                                    | 23        |

| 2.4.4 Usage Recommendations .....                                        | 24        |

| 2.5 Printer Controller (PRNTC) .....                                     | 25        |

| 2.5.1 Features .....                                                     | 25        |

| 2.5.2 Operation .....                                                    | 25        |

| 2.5.2.1 Printer Bitmap Shifter Block .....                               | 25        |

| 2.5.2.2 Thermal Print-Head Control Block .....                           | 25        |

| 2.5.3 Registers .....                                                    | 28        |

| 2.5.4 Usage Recommendations .....                                        | 28        |

| 2.6 Direct Memory Access Controller (DMAC) .....                         | 29        |

| 2.6.1 Features .....                                                     | 29        |

| 2.6.2 Description .....                                                  | 29        |

| 2.6.2.1 A General DMA Channel .....                                      | 29        |

| 2.6.2.2 Transfer Types .....                                             | 29        |

| 2.6.2.3 Operation Modes .....                                            | 29        |

| 2.6.3 Detailed Operation Flow .....                                      | 29        |

| 2.6.4 NS32FX200 DMA Channels .....                                       | 30        |

| 2.6.5 Registers .....                                                    | 30        |

| 2.6.6 Usage Recommendations .....                                        | 32        |

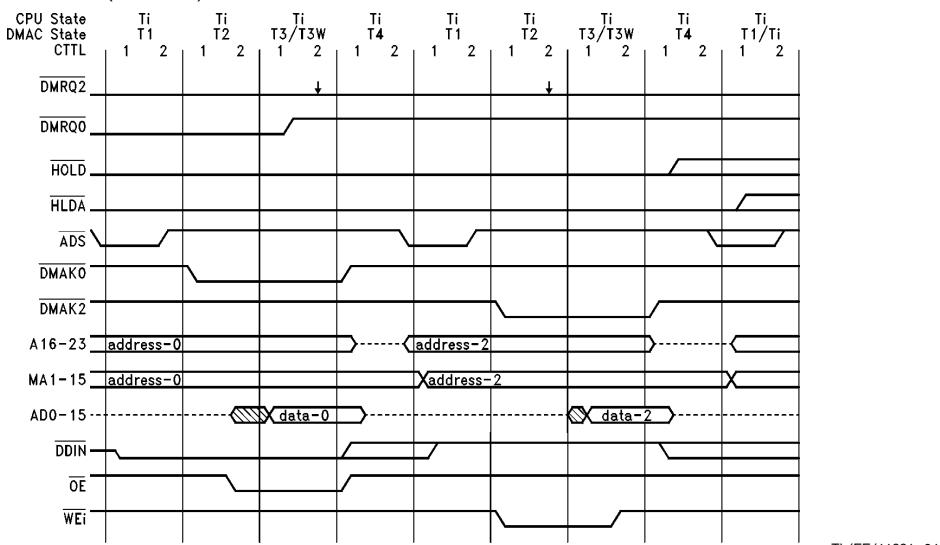

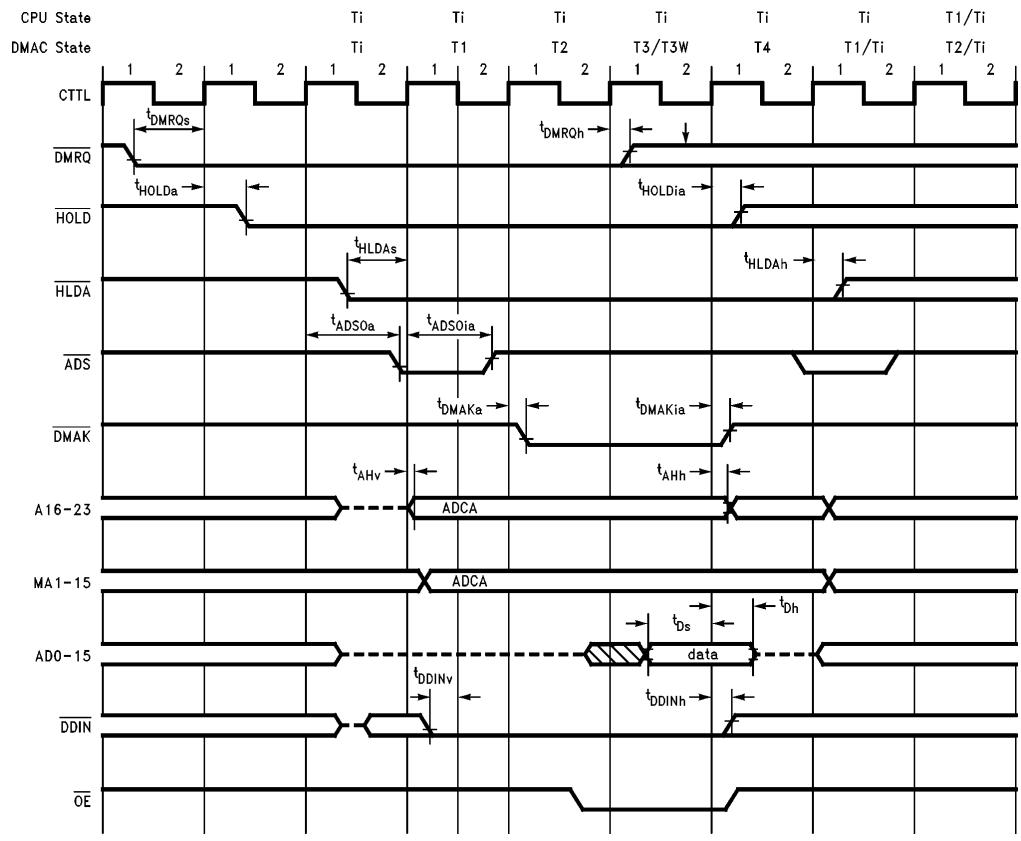

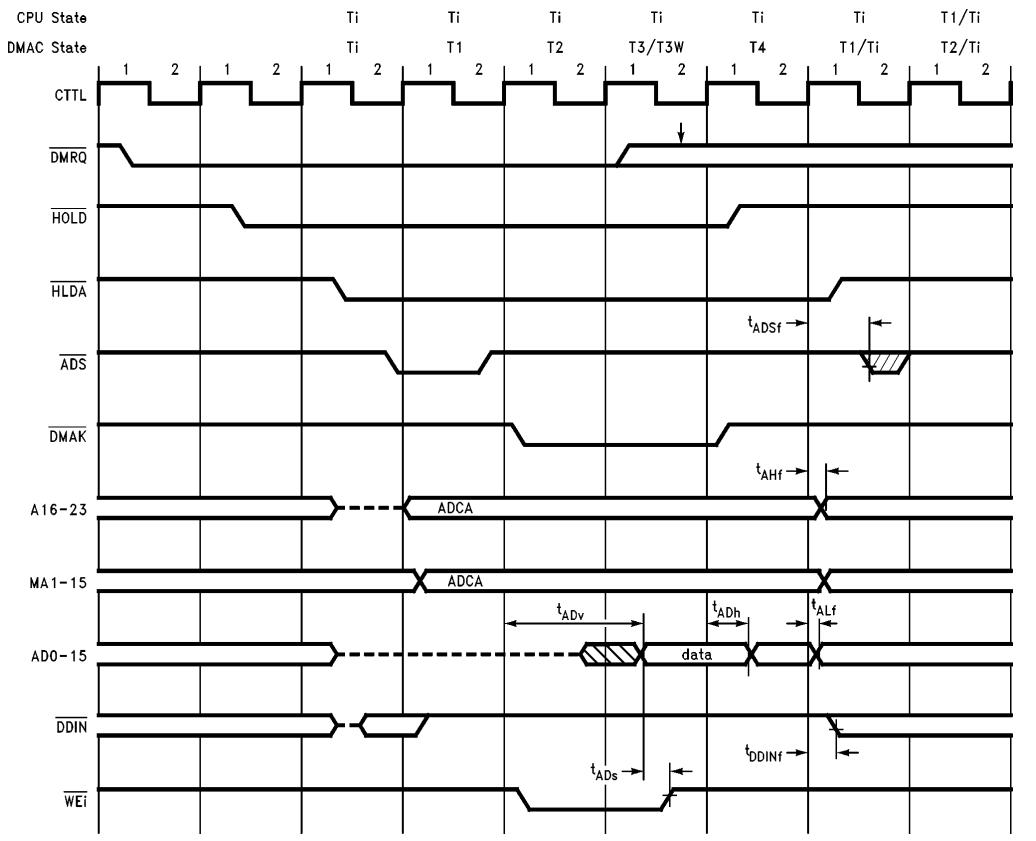

| 2.6.7 DMAC Bus Cycles .....                                              | 32        |

| 2.7 Universal Asynchronous Receiver-Transmitter (UART) .....             | 36        |

| 2.7.1 Features .....                                                     | 36        |

| 2.7.2 Operation .....                                                    | 36        |

| 2.7.3 Registers .....                                                    | 37        |

| 2.7.4 Usage Recommendations .....                                        | 38        |

| 2.8 MICROWIRE (MWIRE) .....                                              | 38        |

| 2.8.1 Features .....                                                     | 38        |

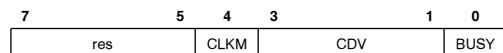

| 2.8.2 Operation .....                                                    | 38        |

| 2.8.3 Registers .....                                                    | 38        |

| 2.8.4 Usage Recommendations .....                                        | 40        |

| 2.9 Interrupt Control Unit (ICU) .....                                   | 40        |

| 2.9.1 Features .....                                                     | 40        |

| 2.9.2 Operation .....                                                    | 40        |

| 2.9.3 Registers .....                                                    | 41        |

| 2.9.4 Usage Recommendations .....                                        | 41        |

| 2.10 Ports Module .....                                                  | 41        |

| 2.10.1 Features .....                                                    | 41        |

| 2.10.2 Operation .....                                                   | 41        |

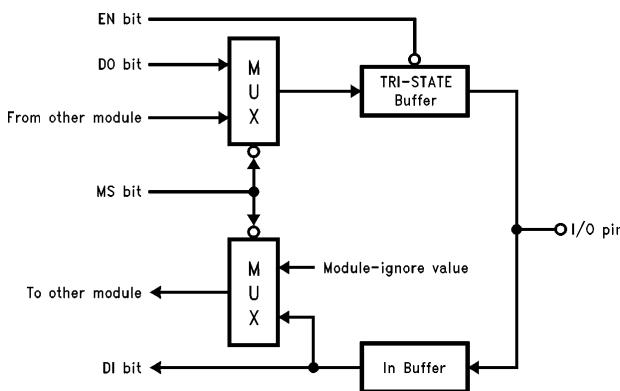

| 2.10.2.1 General Purpose Input/Output Ports .....                        | 41        |

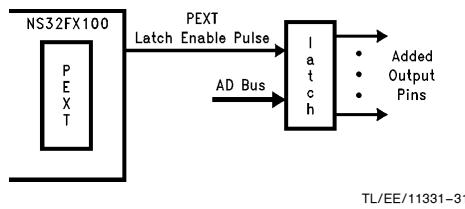

| 2.10.2.2 External Output Port Extension .....                            | 43        |

| 2.10.2.3 Stepper Motors Output Ports .....                               | 43        |

| 2.10.3 Registers .....                                                   | 43        |

| 2.10.4 Usage Recommendations .....                                       | 45        |

## Table of Contents (Continued)

|                                                                                    |           |

|------------------------------------------------------------------------------------|-----------|

| <b>2.0 ARCHITECTURE (Continued)</b>                                                |           |

| 2.11 Bus and Memory Controller (BMC) .....                                         | 45        |

| 2.11.1 Features .....                                                              | 45        |

| 2.11.2 Operation .....                                                             | 45        |

| 2.11.2.1 Zones 0, 1 (ROM and SRAM) Transactions .....                              | 46        |

| 2.11.2.2 Zone 2 (Dynamic Memory) Transactions (NS32FX200 and NS32FV100 only) ..... | 46        |

| 2.11.2.3 Zone 3 (I/O) Transactions .....                                           | 47        |

| 2.11.2.4 Operation in Freeze Mode.....                                             | 47        |

| 2.11.2.5 On-Chip Registers Access .....                                            | 47        |

| 2.11.3 Registers .....                                                             | 47        |

| 2.11.4 Usage Recommendations .....                                                 | 48        |

| 2.12 Register Summary .....                                                        | 48        |

| 2.12.1 NS32FX100 Registers Access Method ..                                        | 48        |

| 2.12.2 NS32FX200, NS32FV100 and NS32FX100 Registers .....                          | 48        |

| <b>3.0 SYSTEM INTERFACE</b> .....                                                  | <b>53</b> |

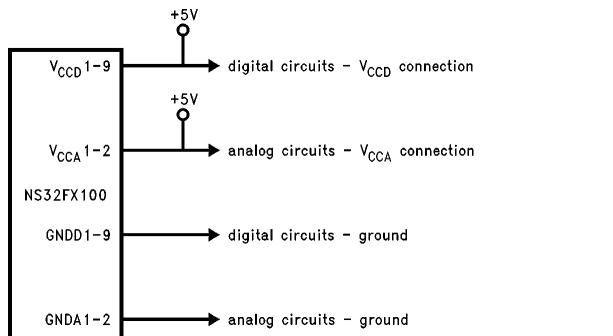

| 3.1 Power and Grounding .....                                                      | 53        |

| 3.2 Clocks and Traps Connectivity.....                                             | 53        |

| <b>3.0 SYSTEM INTERFACE (Continued)</b>                                            |           |

| 3.3 Control of Power Consumption .....                                             | 53        |

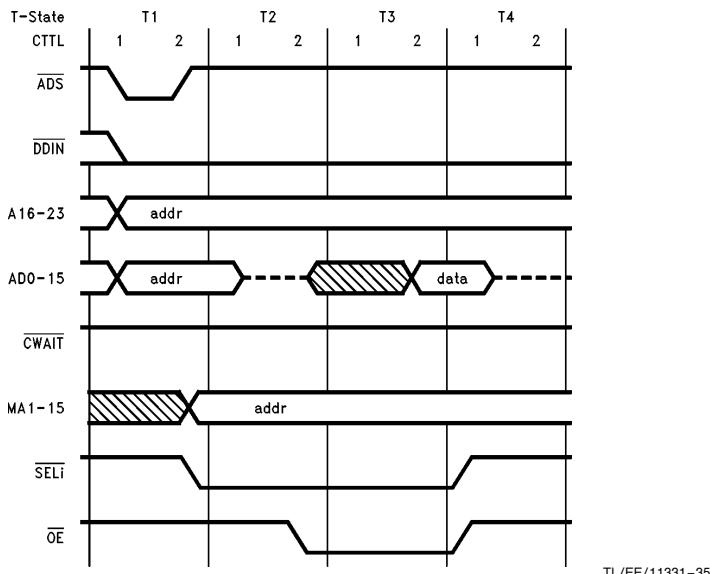

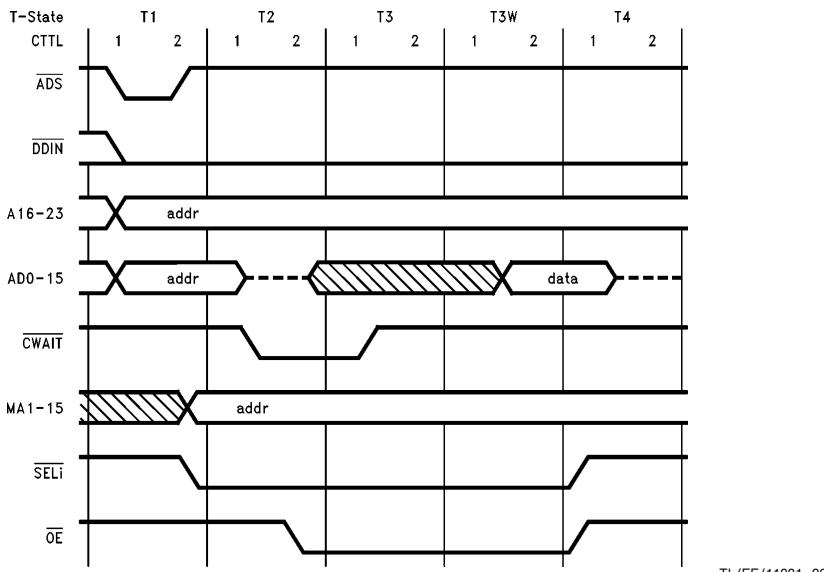

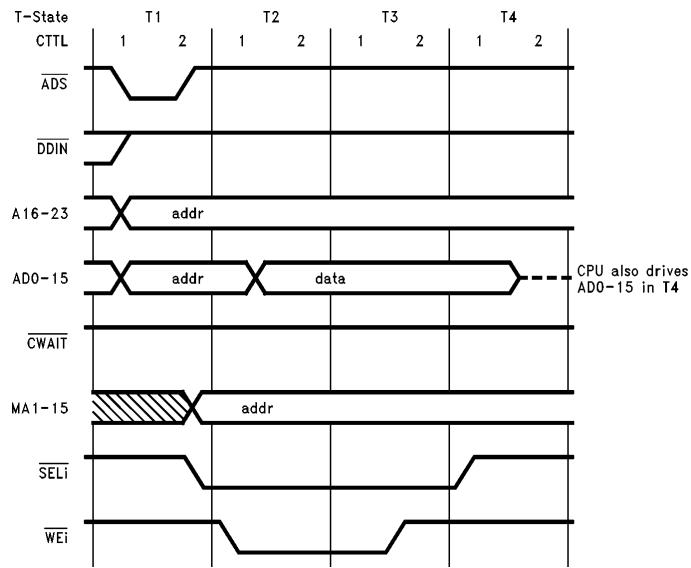

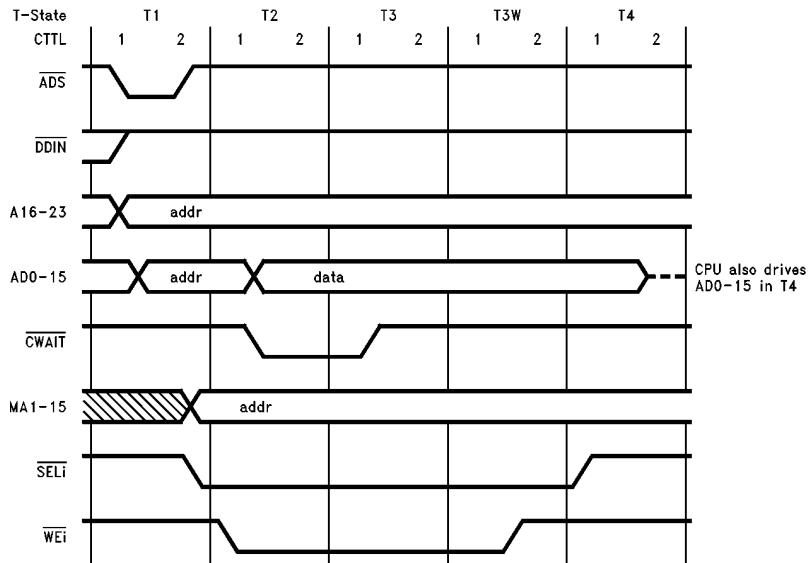

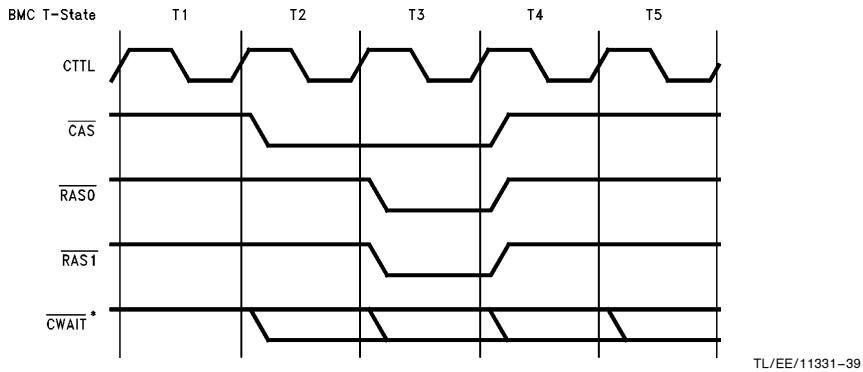

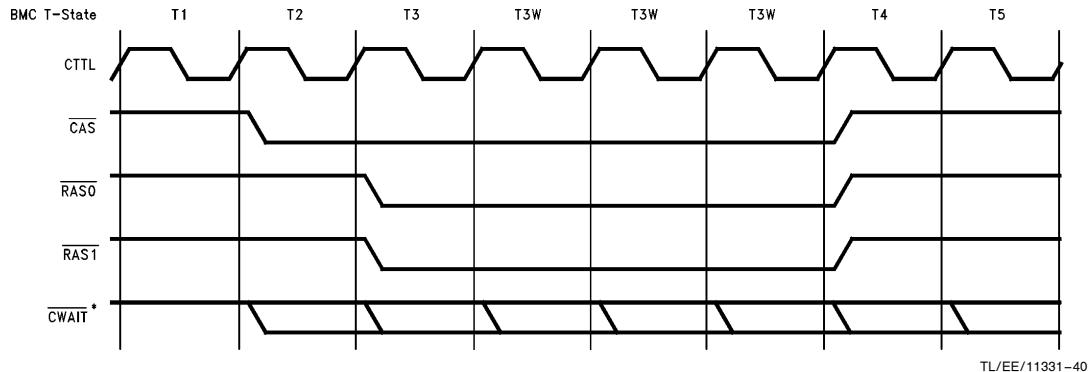

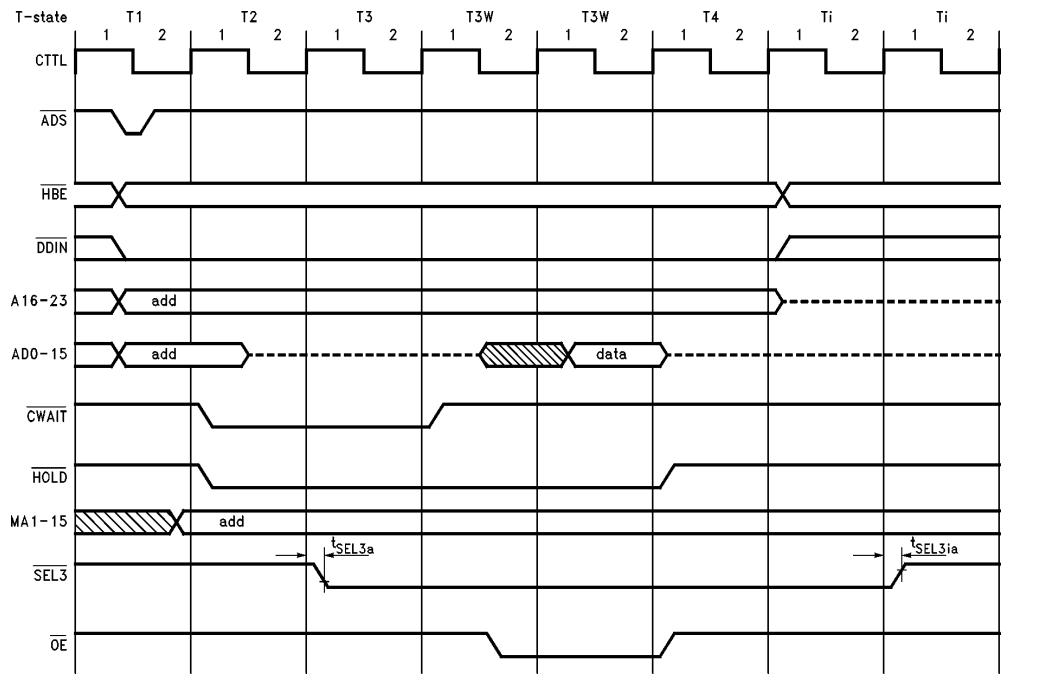

| 3.4 Bus Cycles.....                                                                | 54        |

| <b>4.0 DEVICE SPECIFICATIONS</b> .....                                             | <b>62</b> |

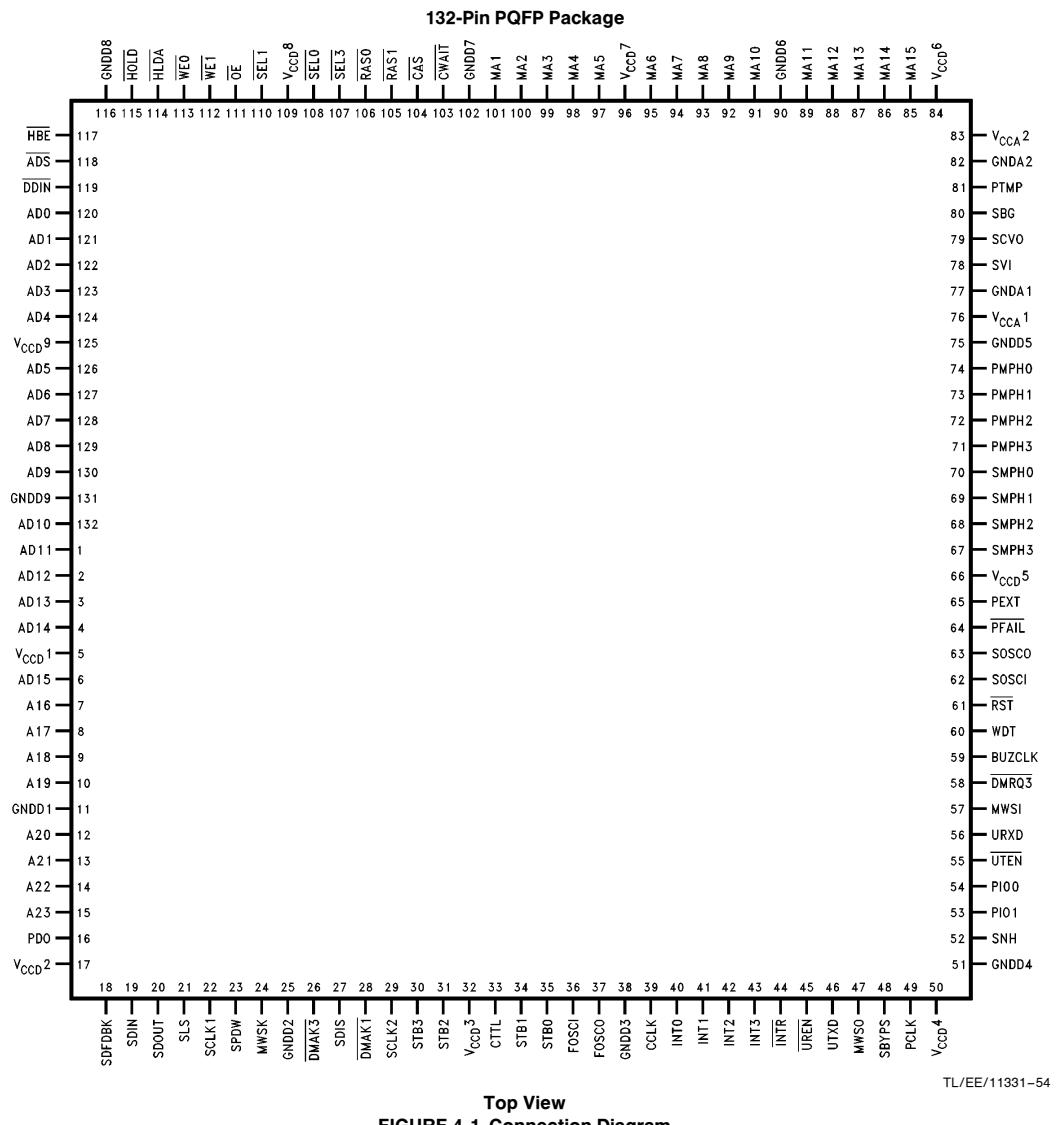

| 4.1 NS32FX100 Pin Descriptions .....                                               | 62        |

| 4.1.1 Supplies .....                                                               | 62        |

| 4.1.2 Input Signals.....                                                           | 62        |

| 4.1.3 Output Signals .....                                                         | 63        |

| 4.1.4 Input/Output Signals.....                                                    | 64        |

| 4.2 Output Signal Levels .....                                                     | 64        |

| 4.2.1 Freeze Mode Output Signals .....                                             | 65        |

| 4.2.2 Reset/Power Restore Output Signals .....                                     | 65        |

| 4.3 Absolute Maximum Ratings .....                                                 | 67        |

| 4.4 Electrical Characteristics .....                                               | 67        |

| 4.5 Analog Electrical Characteristics .....                                        | 69        |

| 4.6 Switching Characteristics .....                                                | 70        |

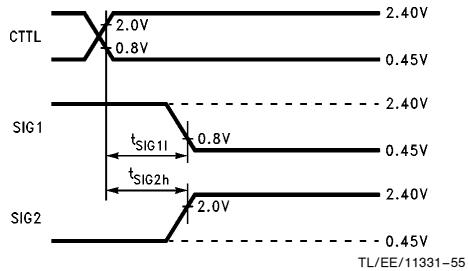

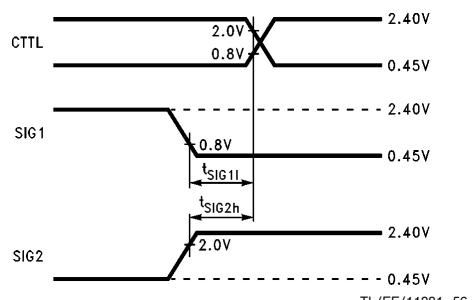

| 4.6.1 Definitions .....                                                            | 70        |

| 4.6.2 Timing Tables .....                                                          | 71        |

| 4.6.2.1 Output Signals: Internal Propagation Delays .....                          | 71        |

| 4.6.2.2 Input Signal Requirements.....                                             | 76        |

| <b>APPENDIX A: CODEC TRANSMISSION PERFORMANCE</b> .....                            | <b>92</b> |

## List of Figures

|             |                                                              |    |

|-------------|--------------------------------------------------------------|----|

| FIGURE 1-1  | A FAX Controller Block Diagram                               | 1  |

| FIGURE 1-2  | NS32FX100 Module Diagram                                     | 7  |

| FIGURE 1-3  | NS32FV100 Module Diagram                                     | 7  |

| FIGURE 1-4  | NS32FX200 Module Diagram                                     | 7  |

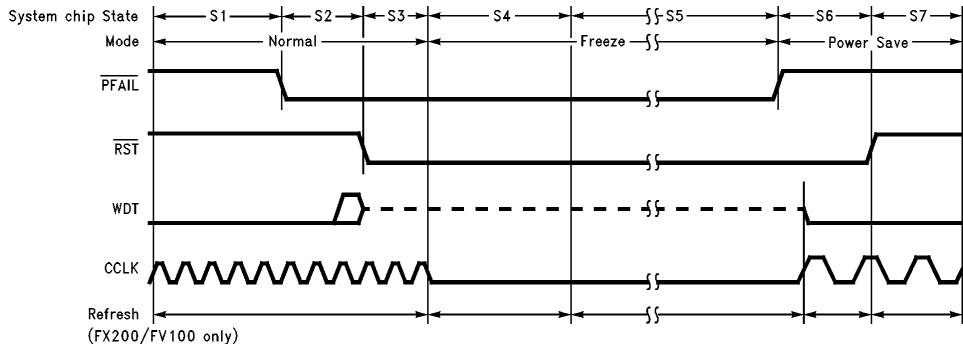

| FIGURE 1-5  | System Chip States and Operation Modes                       | 9  |

| FIGURE 2-1  | Clocks and Traps Connectivity                                | 10 |

| FIGURE 2-2  | High Speed Oscillator Clocks                                 | 11 |

| FIGURE 2-3  | Low Speed Oscillator Clocks                                  | 11 |

| FIGURE 2-4  | Sigma-Delta Block Diagram                                    | 14 |

| FIGURE 2-5  | SDC Off-Chip Analog Circuit                                  | 16 |

| FIGURE 2-6  | Block Diagram of Scanner's Signals Generator Block           | 19 |

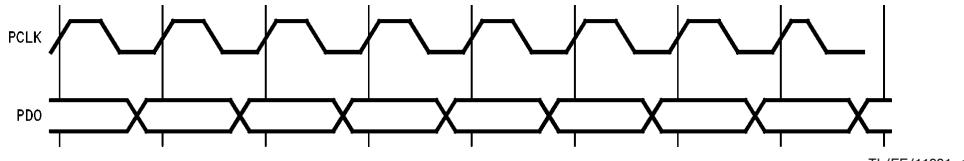

| FIGURE 2-7  | Scanner Pixel Control Signals                                | 20 |

| FIGURE 2-8  | Scanner Period Control Signals                               | 21 |

| FIGURE 2-9  | Block Diagram of Scanner's Video Handling Block              | 21 |

| FIGURE 2-10 | Dither Cyclic Buffer                                         | 22 |

| FIGURE 2-11 | Bitmap Shifter Signals                                       | 25 |

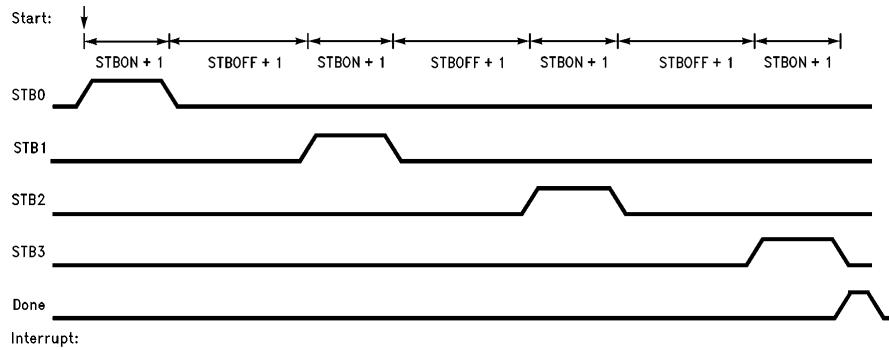

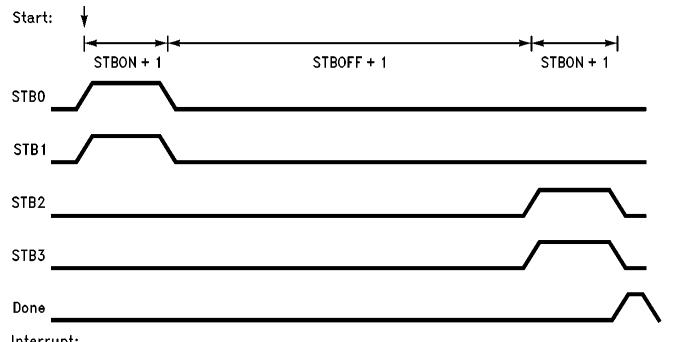

| FIGURE 2-12 | Four Strobes Mode (STBM = 00)                                | 26 |

| FIGURE 2-13 | Two Strobes Mode (STBM = 01)                                 | 26 |

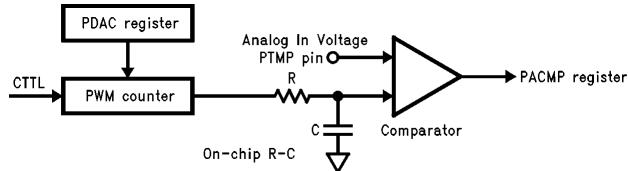

| FIGURE 2-14 | Temperature ADC                                              | 27 |

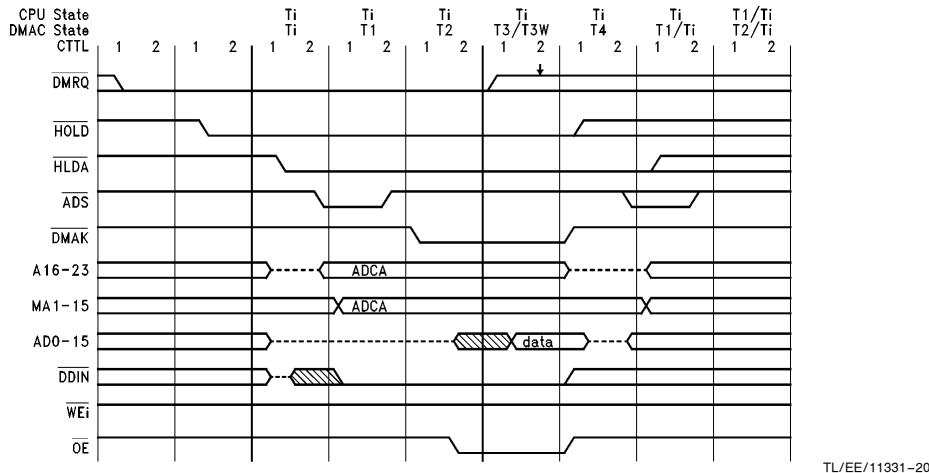

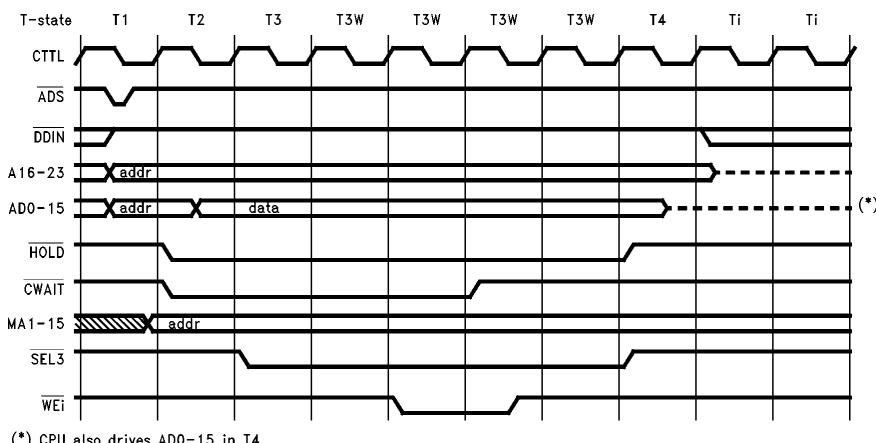

| FIGURE 2-15 | DMA Fly-By Read Transaction (DIR=0, FBY= 0)                  | 32 |

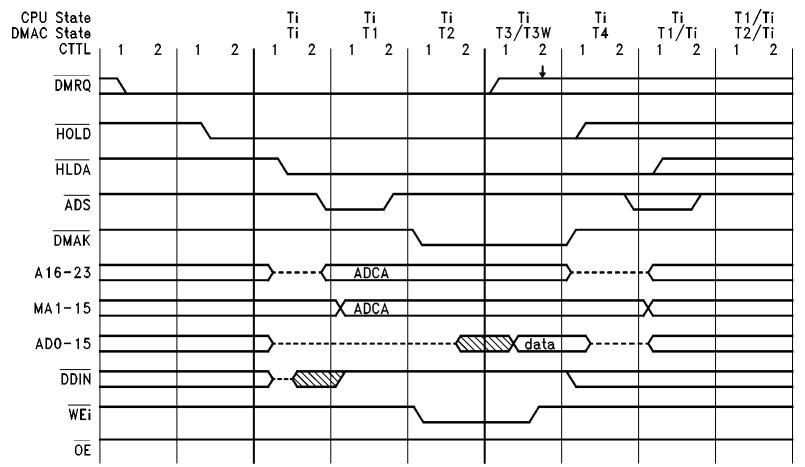

| FIGURE 2-16 | DMA Fly-By Write Transaction (DIR=1, FBY=0)                  | 33 |

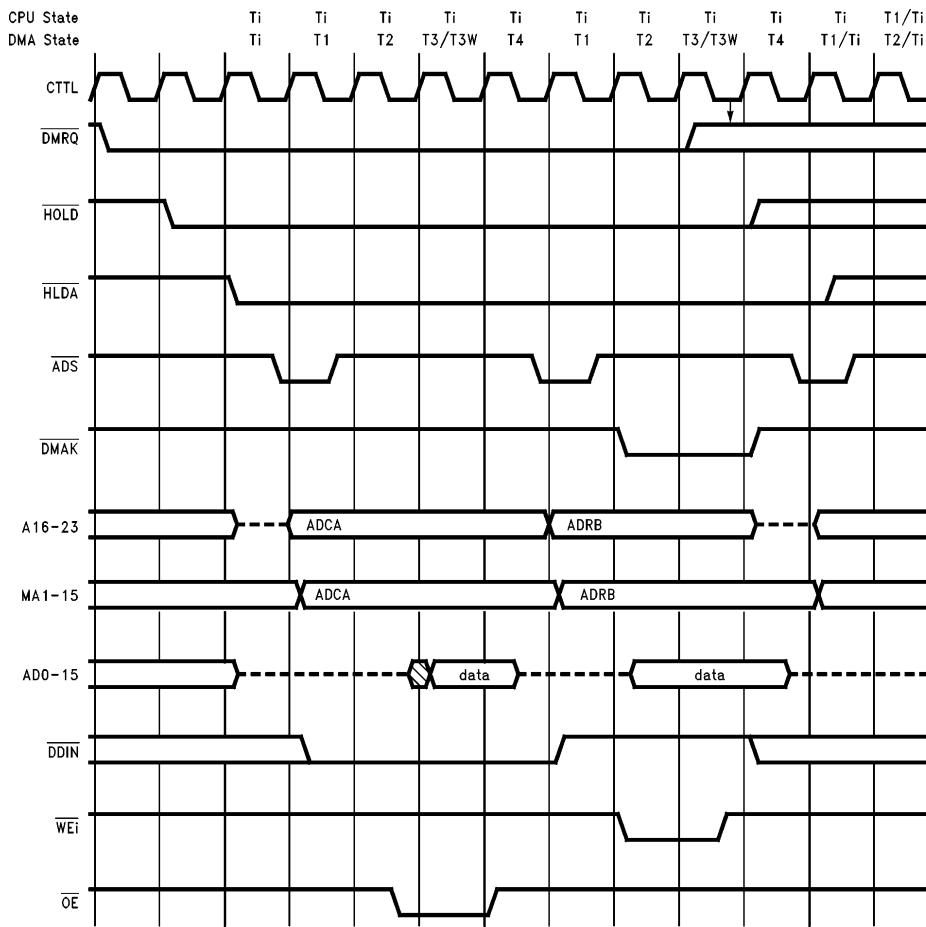

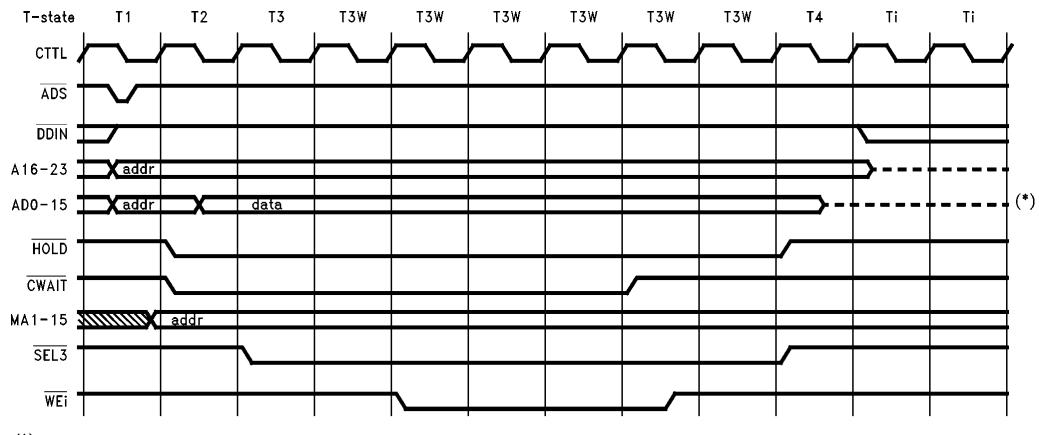

| FIGURE 2-17 | DMA Memory to I/O Read Transaction (DIR=0, NFBY=1)           | 34 |

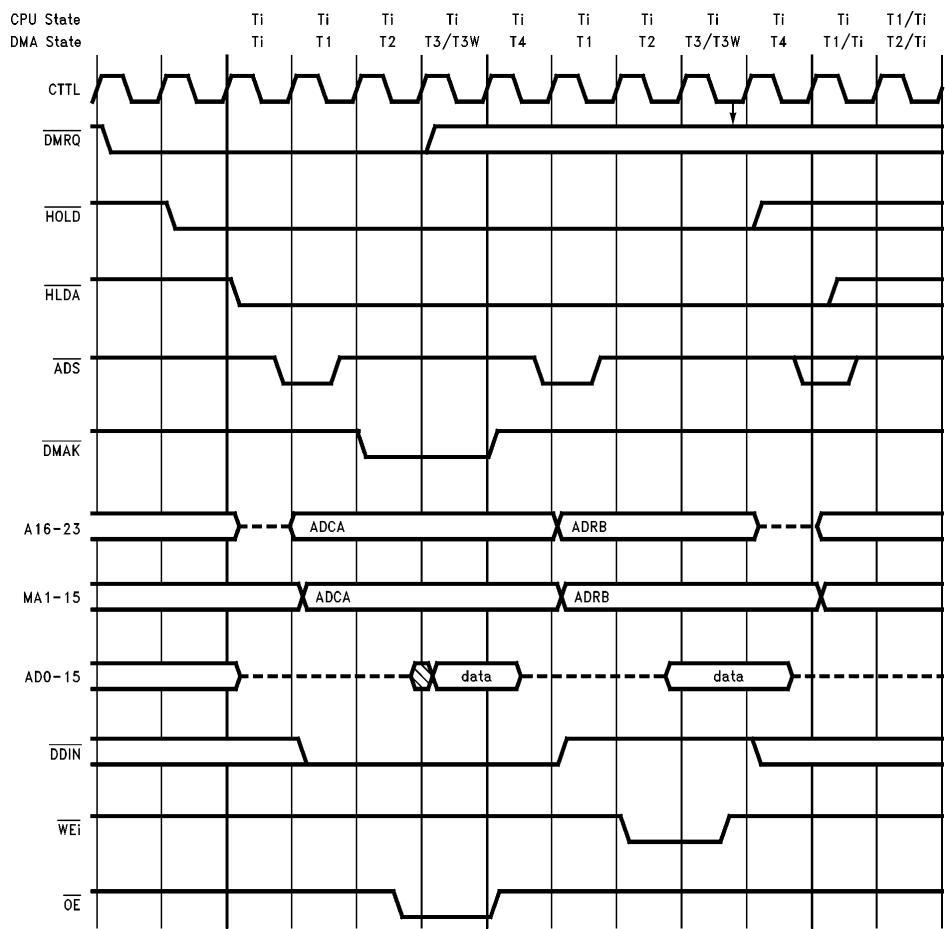

| FIGURE 2-18 | DMA I/O to Memory Write Transaction (DIR=1, NFBY=1)          | 35 |

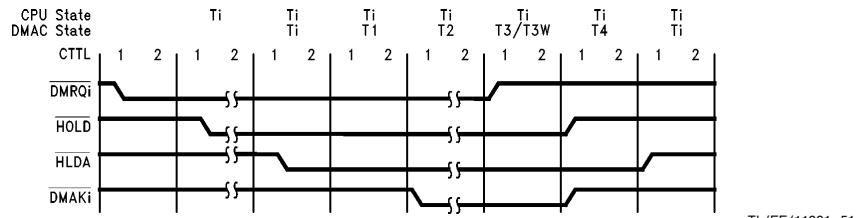

| FIGURE 2-19 | Two Adjacent Fly-By DMA Transactions                         | 36 |

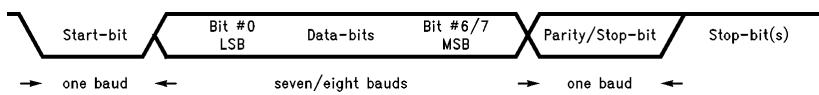

| FIGURE 2-20 | Character Format                                             | 37 |

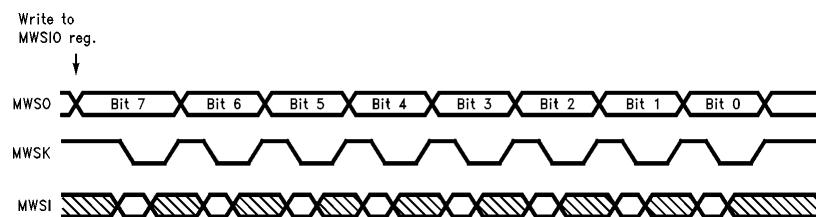

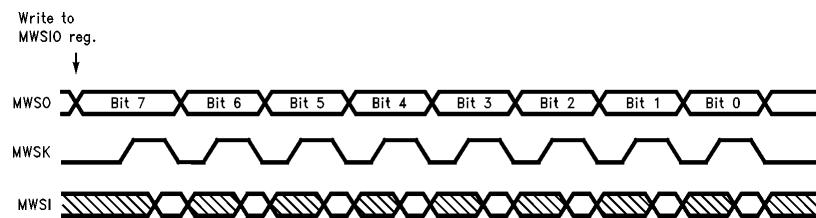

| FIGURE 2-21 | MICROWIRE Transaction (CLKM=0)                               | 39 |

| FIGURE 2-22 | MICROWIRE Transaction (CLKM = 1)                             | 39 |

| FIGURE 2-23 | Port A                                                       | 42 |

| FIGURE 2-24 | Port B                                                       | 42 |

| FIGURE 2-25 | Port C                                                       | 42 |

| FIGURE 2-26 | External Output Port Extension                               | 43 |

| FIGURE 3-1  | Power and Ground Connections                                 | 53 |

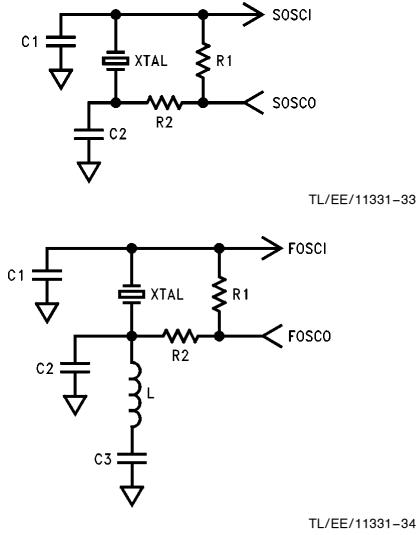

| FIGURE 3-2  | Oscillator Circuits                                          | 53 |

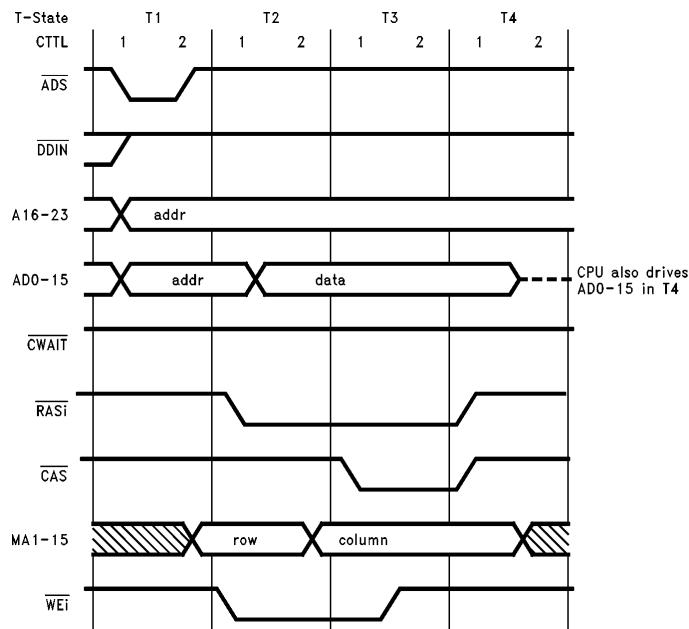

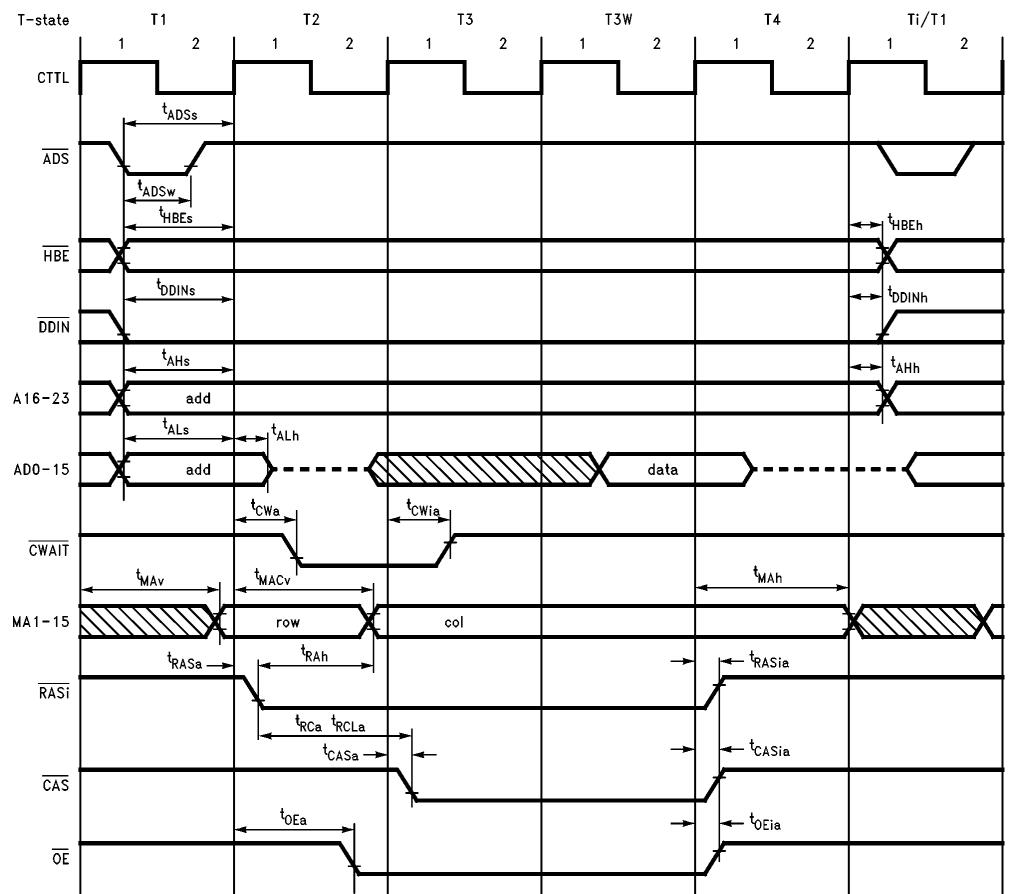

| FIGURE 3-3  | Zones 0, 1 (ROM/SRAM) Read Transaction, Zero Wait State      | 54 |

| FIGURE 3-4  | Zones 0, 1 (ROM/SRAM) Read Transaction, One Wait State       | 54 |

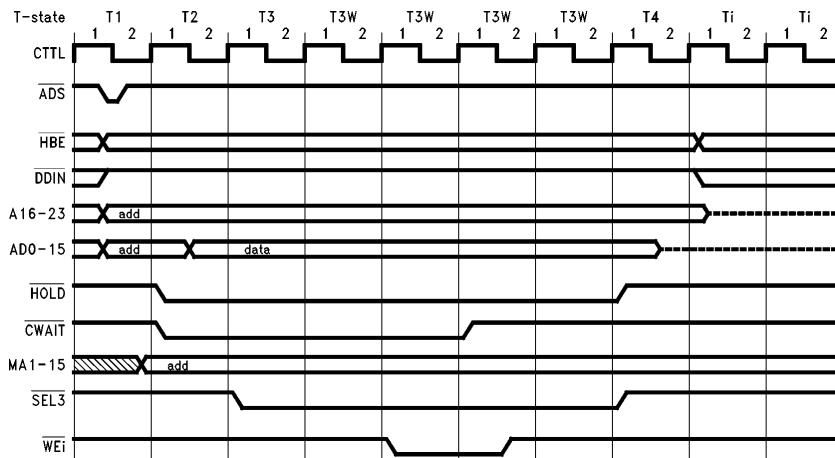

| FIGURE 3-5  | Zones 0, 1 (ROM/SRAM) Write Transaction, Zero Wait State     | 55 |

| FIGURE 3-6  | Zones 0, 1 (ROM/SRAM) Write Transaction, One Wait State      | 55 |

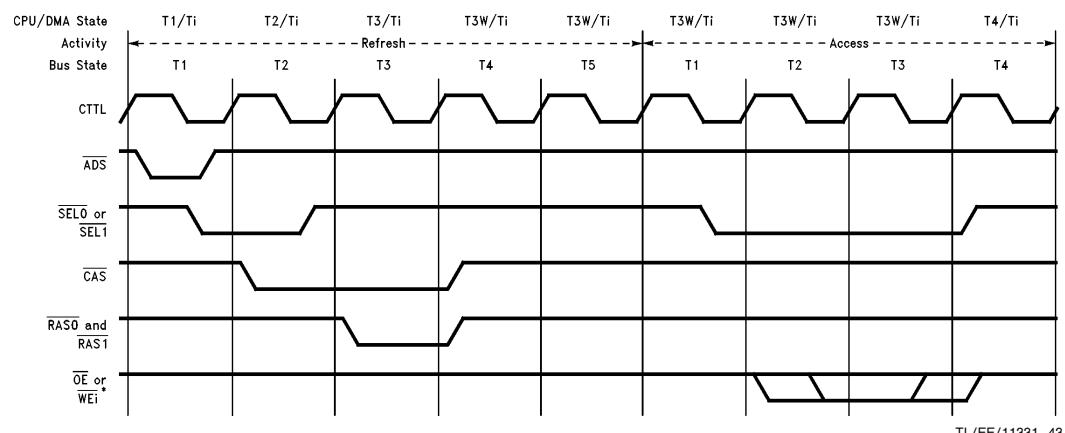

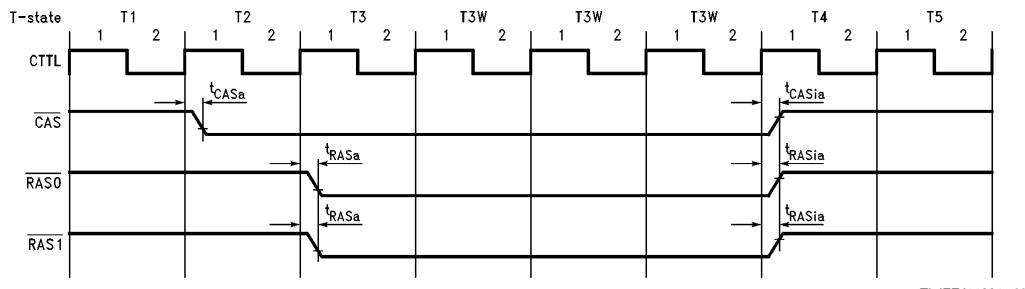

| FIGURE 3-7  | Zone 2 (DRAM) Refresh Transaction, Zero Wait State           | 56 |

| FIGURE 3-8  | Zone 2 (DRAM) Refresh Transaction, Three Wait States         | 56 |

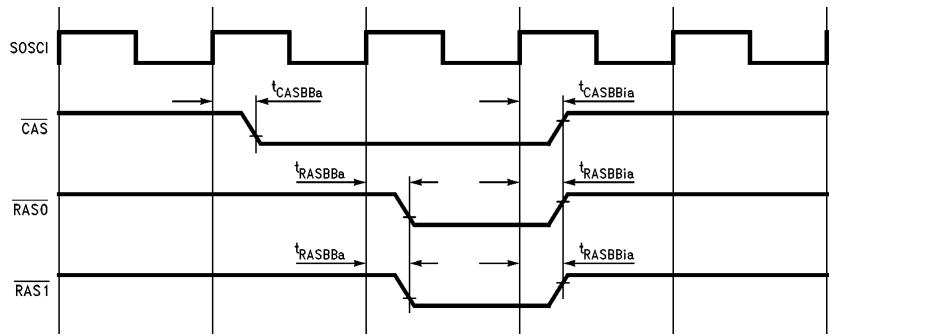

| FIGURE 3-9  | Freeze Mode Refresh Transaction Waveform                     | 56 |

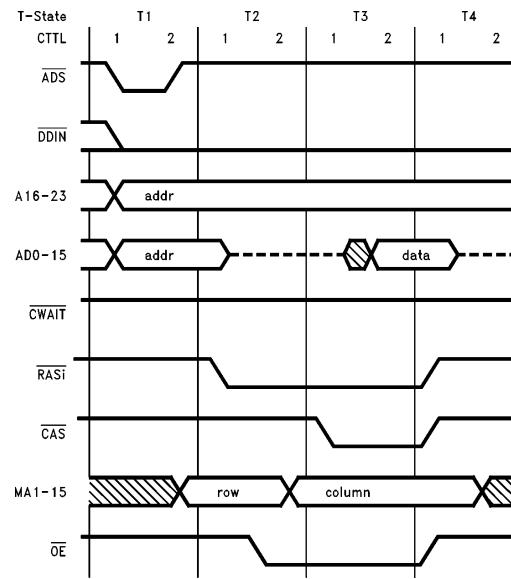

| FIGURE 3-10 | Zone 2 (DRAM) Read Transaction, Zero Wait State              | 57 |

| FIGURE 3-11 | Zones 0, 1 Access Delayed by a Refresh Transaction (No Wait) | 57 |

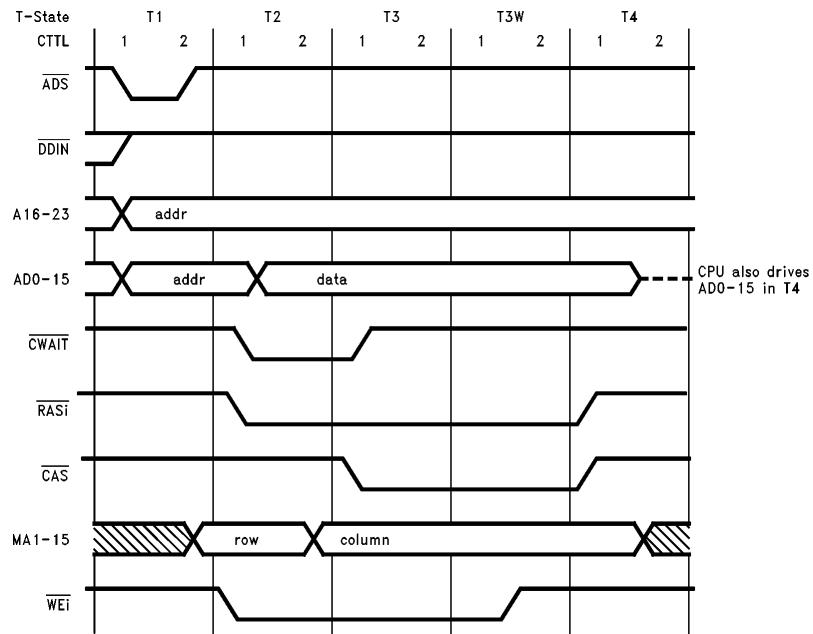

| FIGURE 3-12 | Zone 2 (DRAM) Read Transaction, One Wait State               | 58 |

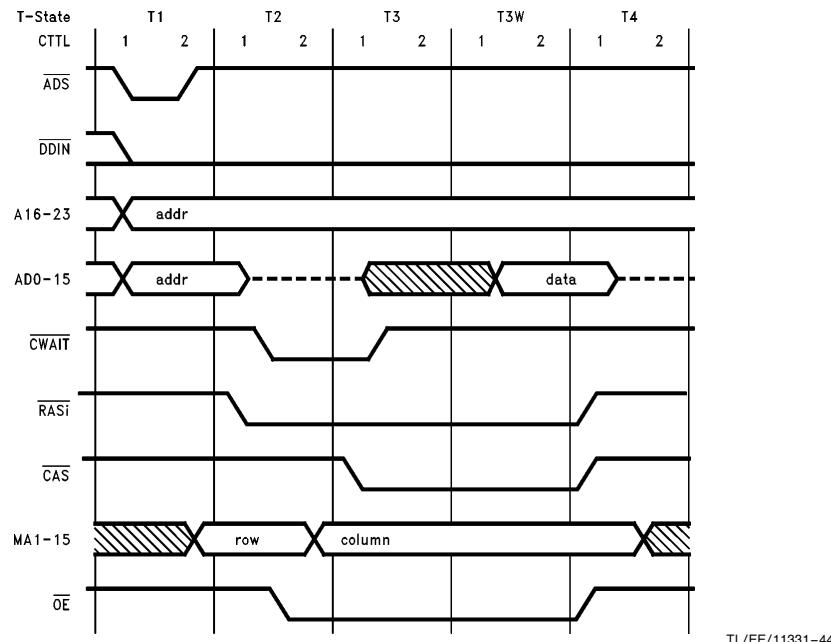

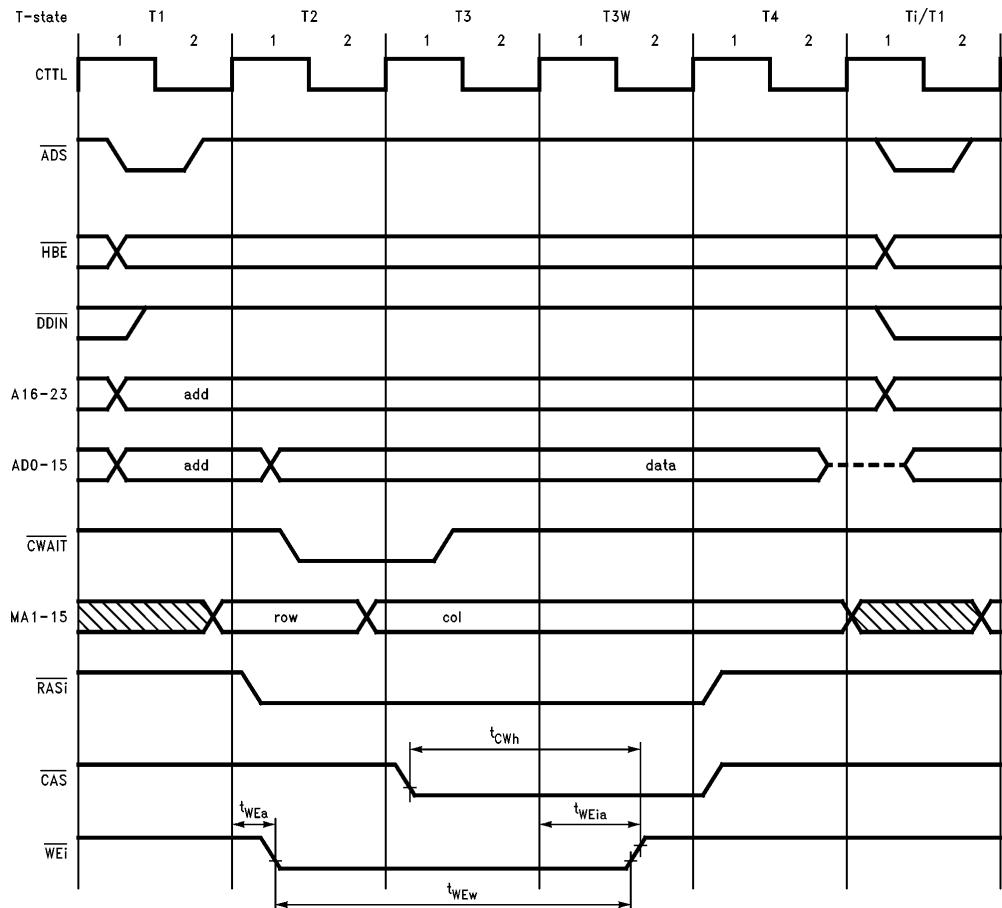

| FIGURE 3-13 | Zone 2 (DRAM) Write Transaction, Zero Wait State             | 58 |

| FIGURE 3-14 | Zone 2 (DRAM) Write Transaction, One Wait State              | 59 |

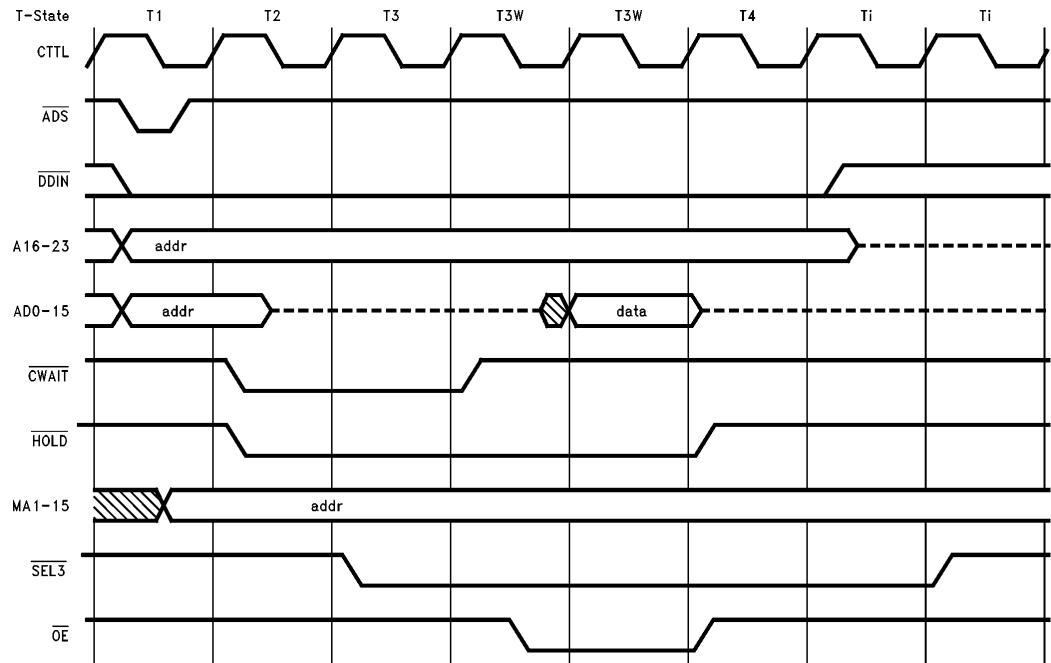

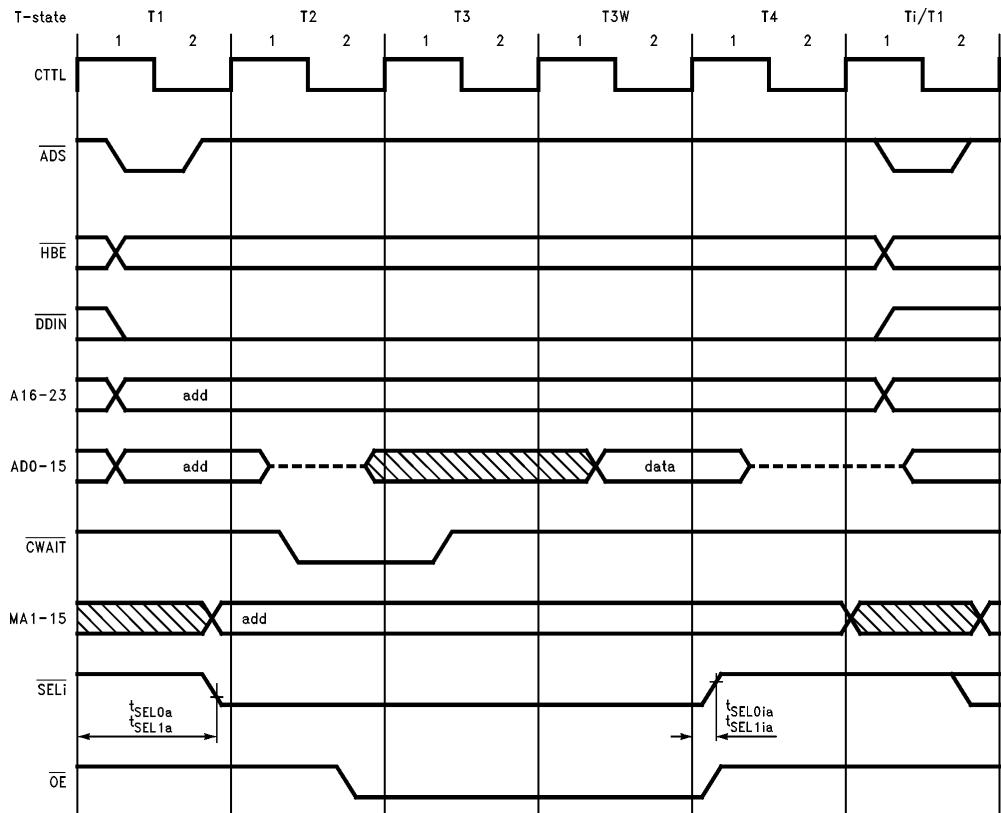

| FIGURE 3-15 | Zone 3 (I/O) Read Transaction, Two Wait States               | 59 |

| FIGURE 3-16 | Zone 3 (I/O) Read Transaction, Four Wait States              | 60 |

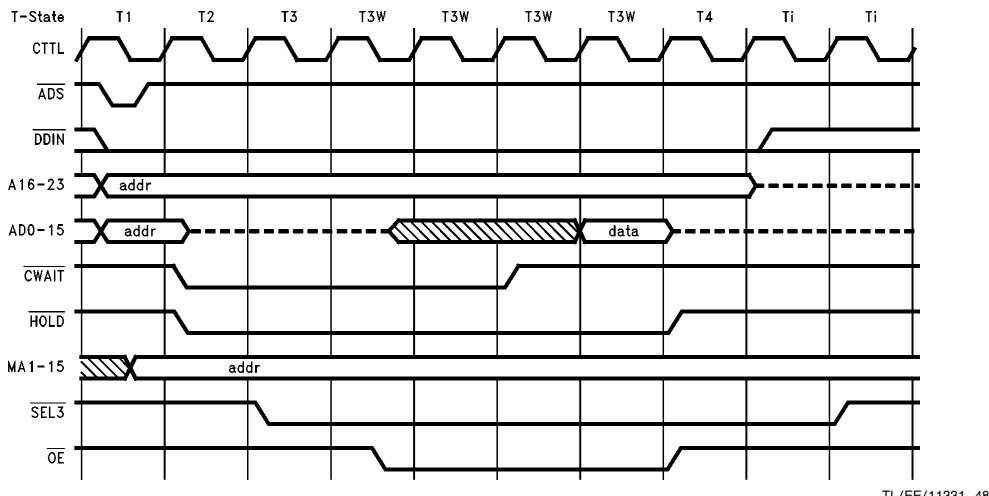

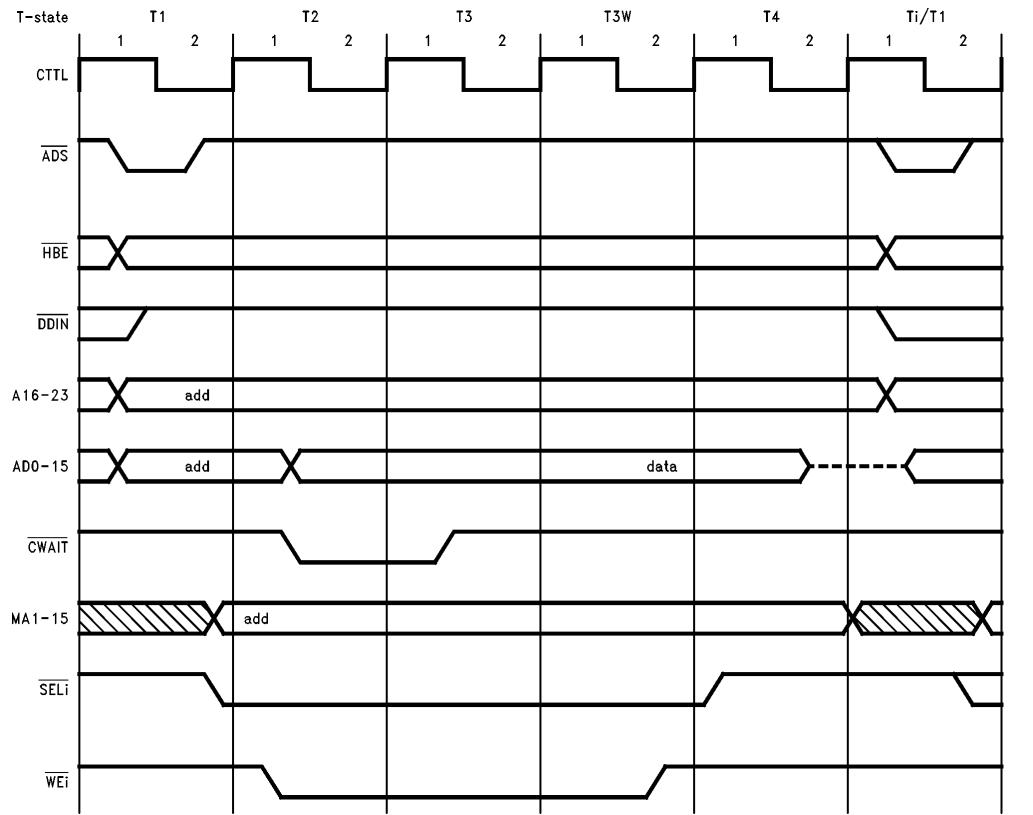

| FIGURE 3-17 | Zone 3 (I/O) Write Transaction, Four Wait States             | 60 |

| FIGURE 3-18 | Zone 3 (I/O) Write Transaction, Six Wait States              | 61 |

| FIGURE 3-19 | CPU/DMA Arbitration                                          | 61 |

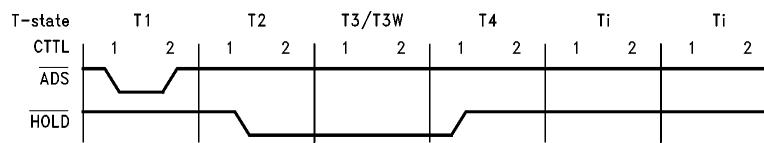

| FIGURE 3-20 | Spaced Memory Transaction, Two Tides after T4                | 61 |

## List of Figures (Continued)

|             |                                            |    |

|-------------|--------------------------------------------|----|

| FIGURE 4-1  | Connection Diagram—Top View                | 66 |

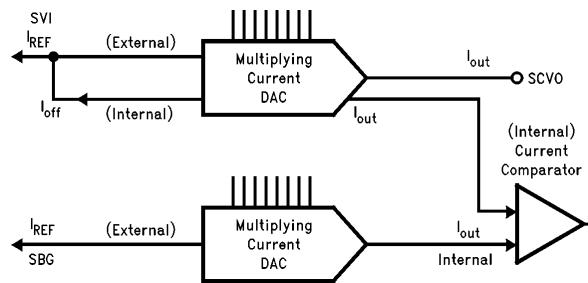

| FIGURE 4-2  | Analog Circuitry Block Diagram             | 69 |

| FIGURE 4-3  | TTL—Output Signals Specification Standard  | 70 |

| FIGURE 4-4  | TTL—Input Signals Specification Standard   | 70 |

| FIGURE 4-5  | CMOS—Output Signals Specification Standard | 70 |

| FIGURE 4-6  | CMOS—Input Signals Specification Standard  | 70 |

| FIGURE 4-7  | Input Hysteresis                           | 70 |

| FIGURE 4-8  | Clock Waveforms                            | 79 |

| FIGURE 4-9  | DRAM Read Bus Cycle                        | 79 |

| FIGURE 4-10 | DRAM Write Bus Cycle                       | 80 |

| FIGURE 4-11 | ROM/SRAM Read Bus Cycle                    | 81 |

| FIGURE 4-12 | ROM/SRAM Write Bus Cycle (One Wait State)  | 82 |

| FIGURE 4-13 | I/O Read Bus Cycle                         | 83 |

| FIGURE 4-14 | I/O Write Bus Cycle                        | 83 |

| FIGURE 4-15 | DRAM Refresh Bus Cycles                    | 84 |

| FIGURE 4-16 | DMA Read Transaction (DIR = 0)             | 85 |

| FIGURE 4-17 | DMA Write Transaction (DIR = 1)            | 86 |

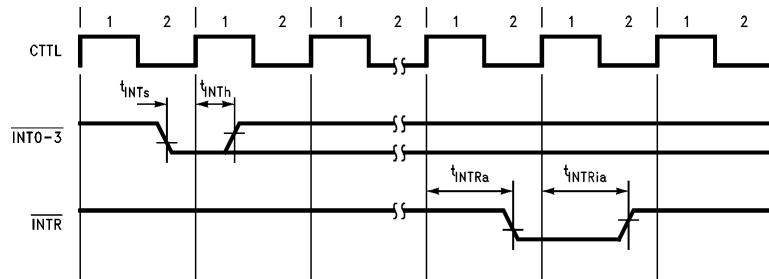

| FIGURE 4-18 | Interrupt Signals Timing                   | 87 |

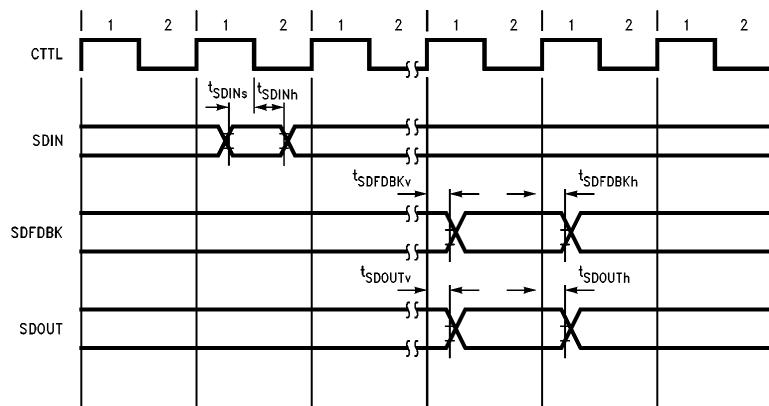

| FIGURE 4-19 | Sigma-Delta Signals Timing                 | 87 |

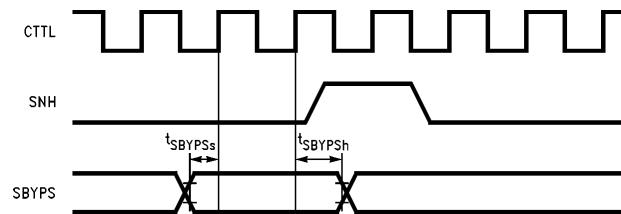

| FIGURE 4-20 | SBYPS Input Signal Timing                  | 87 |

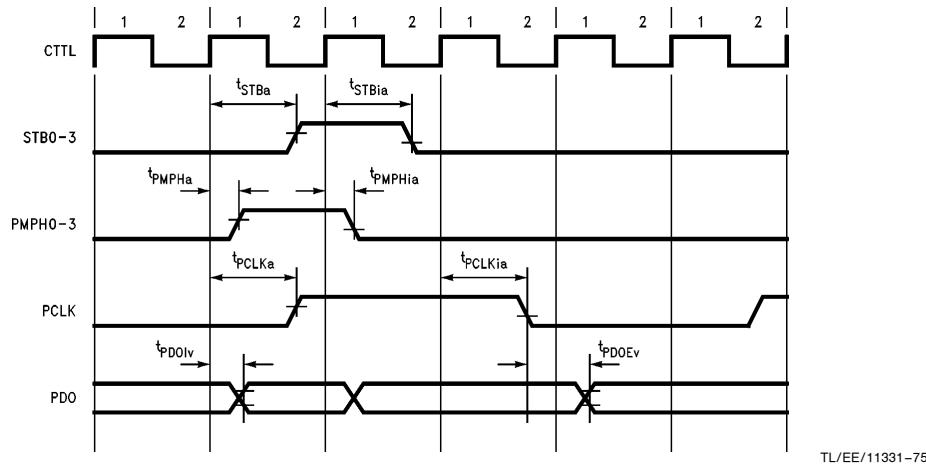

| FIGURE 4-21 | Printer Signals Timing                     | 88 |

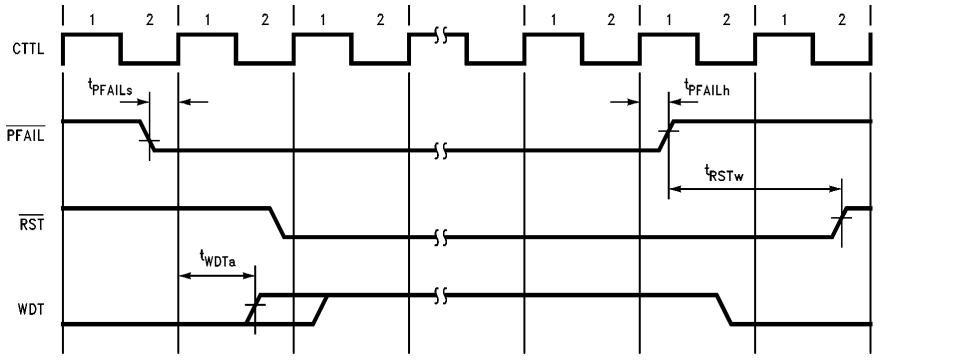

| FIGURE 4-22 | Reset Signals Timing                       | 88 |

| FIGURE 4-23 | Scanner Signals Timing                     | 89 |

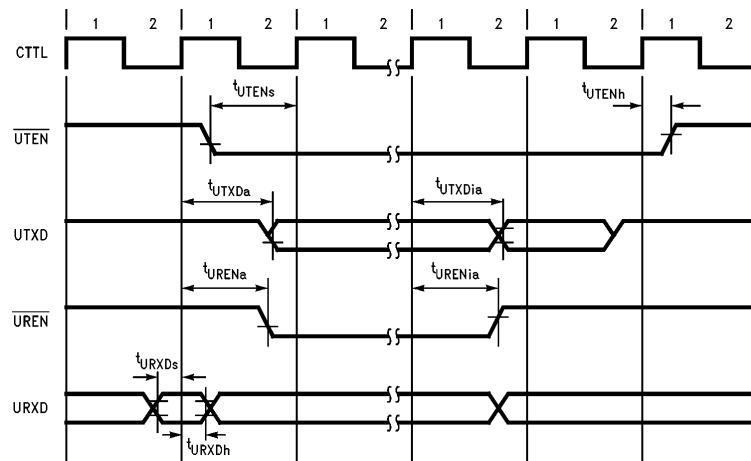

| FIGURE 4-24 | UART Signals Timing                        | 90 |

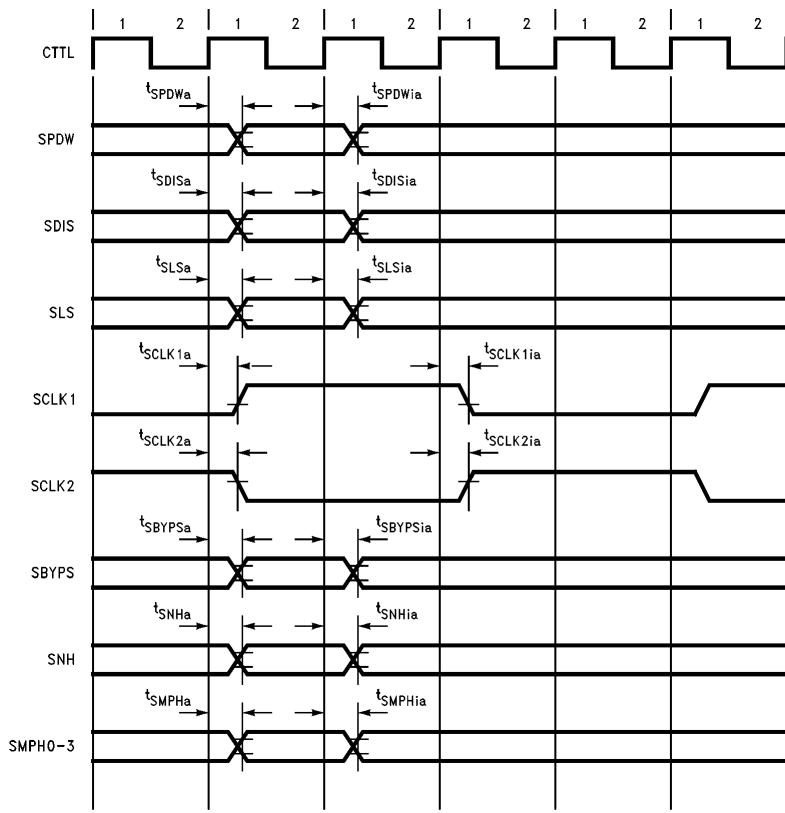

| FIGURE 4-25 | MWIRE Signals Timing                       | 90 |

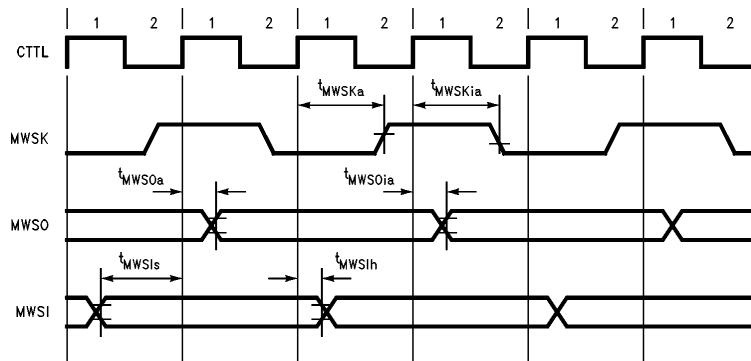

| FIGURE 4-26 | Ports Signals Timing                       | 91 |

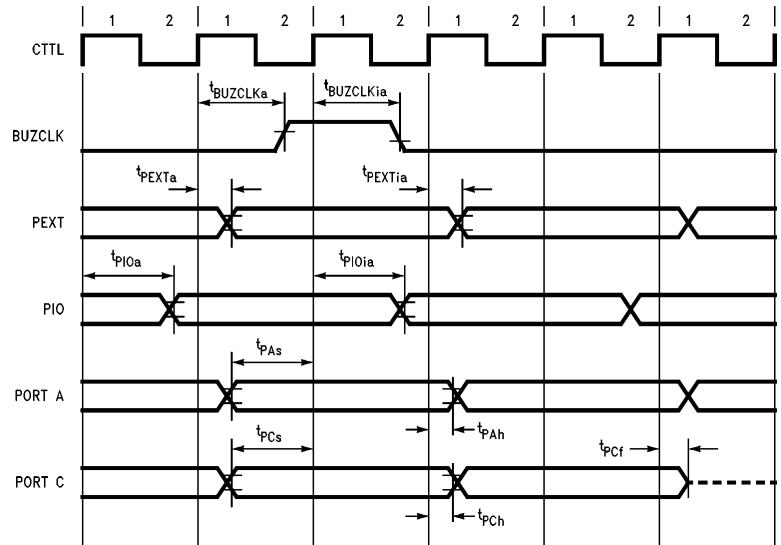

| FIGURE 4-27 | Analog Signals Timing                      | 91 |

## List of Tables

|           |                                                   |    |

|-----------|---------------------------------------------------|----|

| TABLE 2-1 | CTTL, MCLON and MCLOFF Values                     | 12 |

| TABLE 2-2 | Component Values                                  | 15 |

| TABLE 2-3 | Interrupt Sources and Priority Levels             | 40 |

| TABLE 2-4 | DRAM Address Multiplexing                         | 46 |

| TABLE 2-5 | DRAM Address Sizes                                | 46 |

| TABLE 3-1 | R, C and L Values                                 | 53 |

| TABLE 3-2 | System Chip Operation Modes and Power Consumption | 53 |

| TABLE A-1 | Transmitter Performance                           | 92 |

| TABLE A-2 | Receiver Performance                              | 93 |

## 1.0 Fax-System Configuration

A typical FAX system based on the NS32FX100, NS32FX200 or NS32FV100, is shown in *Figure 1-1*.

### 1.1 BLOCK DIAGRAM DESCRIPTION

**CPU.** The typical FAX system shown below is based on a single embedded processor. The choice between the NS32FX161, NS32FV16 and the NS32FX164 depends on the specific application requirements.

**System Chip.** The FAX-system chip interfaces between FAX-system peripheral devices, such as motors, printers and scanners, and the embedded processor. The chip contains FAX-system elements such as CODEC, DMA Controller, Interrupt Control Unit and counters.

**Scanner.** Either a Charge-Coupled Device (CCD) scanner or a Contact Image Sensor (CIS) scanner may be used. The NS32FX100 incorporates most of the video circuits, such as shading compensation, dithering and digitizing, which are required for the scanner interface.

**Printer.** A Thermal Print Head (TPH) can be connected directly to the NS32FX100. Other types of printer engine, such as laser or ink-jet, can easily be interfaced to the NS32FX100 via an additional, small ASIC.

**Motors.** The NS32FX100 controls two stepper motors. The only external components required to operate the motors are buffers/drivers.

**DAA I/F.** The telephone line is accessed via a Data Access Arrangement (DAA). The NS32FX100 contains the digital part of a Sigma-Delta CODEC, which connects to the DAA.

A few external components are required to implement the analog part of the CODEC.

**Memory.** The NS32FX100 directly controls ROM and SRAM. Both the NS32FX200 and the NS32FV100 directly control DRAM, in addition to ROM and SRAM.

Memory access time is also controlled by the NS32FX100, thus allowing the designer to tune memory price and system performance.

**MICROWIRE.** The serial channel, with programmable interface parameters, can be used by advanced FAX systems to interface with other devices (such as EEPROMs).

**IART.** This serial channel, with programmable interface parameters, can be used by advanced fax systems to communicate with other devices (e.g., host machines).

**I/O Pins.** General purpose I/O pins are used both to monitor (e.g., ring detector read) and control (e.g. scanner light control) the FAX-system peripheral devices.

#### DMA Channels:

**NS32FX100 and NS32FV100.** The NS32FX100 and NS32FV100 have three DMA channels which are used to interface the scanner and the printer. All three channels may be allocated for external usage (e.g., Centronics parallel interface, Ethernet).

**NS32FX200.** The NS32FX200 has four DMA channels. Three channels are used by the NS32FX200 to interface to the scanner and the printer, and one channel is for external usage. All four channels may be allocated for external usage (e.g., Centronics parallel interface, Ethernet).

## 1.0 Fax-System Configuration (Continued)

### 1.2 MODULE DIAGRAM

The various functions of the NS32FX100, NS32FV100 and NS32FX200 are performed by on-chip modules as shown below.

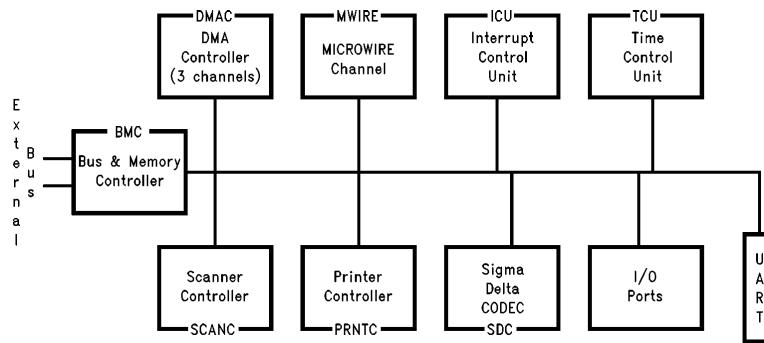

The NS32FX100 module diagram is shown in *Figure 1-2*.

FIGURE 1-2. NS32FX100 Module Diagram

TL/EE/11331-3

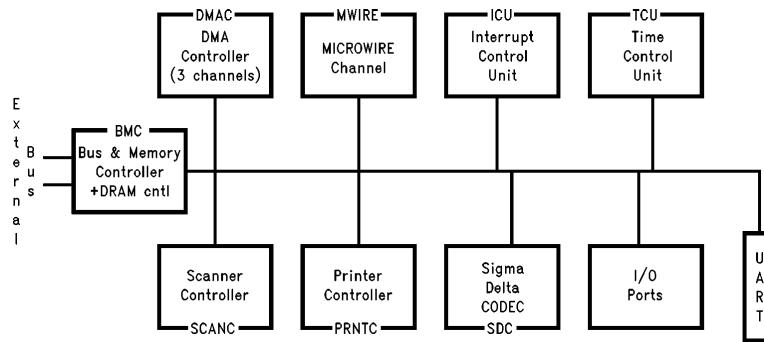

The NS32FV100 module diagram is shown in *Figure 1-3*.

FIGURE 1-3. NS32FV100 Module Diagram

TL/EE/11331-4

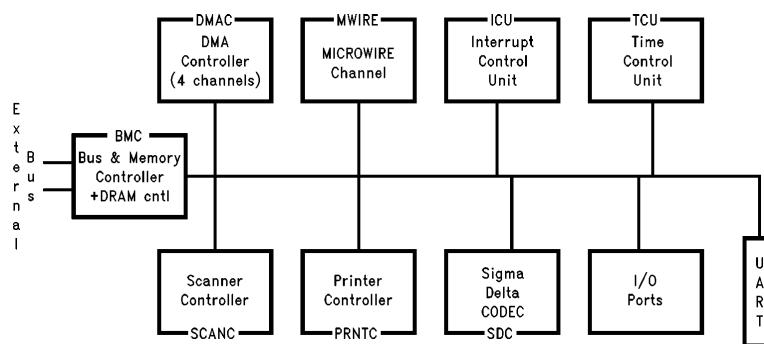

The NS32FX200 module diagram is shown in *Figure 1-4*.

FIGURE 1-4. NS32FX200 Module Diagram

TL/EE/11331-2

## 1.0 Fax-System Configuration (Continued)

The NS32FX100 modules, and their functions, are summarized below: For a more detailed description of each module, see the relevant section.

### 1.2.1 Bus and Memory Controller (BMC)

The Bus and Memory Controller (BMC) interfaces directly to the NS32FX161, the NS32FV16 or the NS32FX164. It enables the NS32FX100 to respond to both read and write transactions, and to generate DMA transactions. It divides the address space into four external zones and generates wait states, and idle cycles, according to the addressed zone, type of transaction and the programmed wait value. The memory controller directly interfaces to ROMs and SRAMs. The memory controllers of the NS32FX200 and the NS32FV100, in addition, directly interface to DRAMs.

### 1.2.2 Timing Control Unit (TCU)

The Timing Control Unit (TCU) contains three blocks. An oscillators block generates the CPU high-speed clock and the time-keeper clock. The TCU module keeps trace of elapsed time during all operation modes. A counters block contains timers/counters for the various FAX-system controller operations.

### 1.2.3 Sigma-Delta CODEC (SDC)

The Sigma-Delta CODEC (SDC) interfaces with the telephone line via an external Data Access Arrangement (DAA), performing analog-to-digital and digital-to-analog conversions, data sampling and buffering. Off-hook control and ring-detect monitoring are performed by the Ports module.

### 1.2.4 Scanner Controller (SCANC)

The Scanner Controller (SCANC) contains the video handling block, the scanner signals generator and the stepper motor control block. The block includes both analog and digital circuits. It uses DMA channel 0 to fetch a reference line from memory and DMA channel 2 to store the digitized video data to memory.

### 1.2.5 Printer Controller (PRNTC)

The Printer Controller (PRNTC) contains the printer bitmap shifter, the stepper motor control block, the temperature-sensing block and the thermal print head control block. It uses DMA channel 1 to fetch the bitmap from memory.

### 1.2.6 DMA Controller (DMAC)

**NS32FX200.** The DMA Controller (DMAC) provides four independent channels for transferring blocks of data between memory and I/O devices, with minimal CPU intervention. Two channels are used for scanner control, one for printer control and one is available for external usage.

**NS32FX100, NS32FV100.** The DMA Controller (DMAC) provides three independent channels for transferring blocks of data between memory and I/O devices, with minimal CPU intervention. Two channels are used for scanner control, one for printer control.

### 1.2.7 Universal Asynchronous Receiver-Transmitter (UART)

The Universal Asynchronous Receiver-Transmitter (UART) supports 7-bit or 8-bit data formats, with or without parity, with or without hardware flow control, and with one or two stop bits. The baud rate is generated on-chip, under software control.

### 1.2.8 MICROWIRE (MWIRE)

The MWIRE is a serial synchronous communication interface. It enables the CPU to interface with any of National Semiconductor's chips which support MWIRE, such as COP400, COP800 and EEPROMs. The MWIRE interface consists of three signals—serial data in, serial data out, and shift clock. Several devices can share the MWIRE channel using selection signals provided by the Ports module.

### 1.2.9 Interrupt Control Unit (ICU)

The Interrupt Control Unit (ICU) receives internal and external interrupt sources and generates an interrupt to the CPU when required. Priority is allocated according to a predetermined scheme. The ICU supports programmable triggering mode and polarity. Each interrupt source can be individually enabled or disabled. Pending interrupts can be polled, regardless of whether they are enabled or disabled.

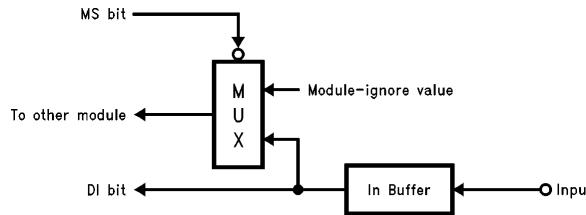

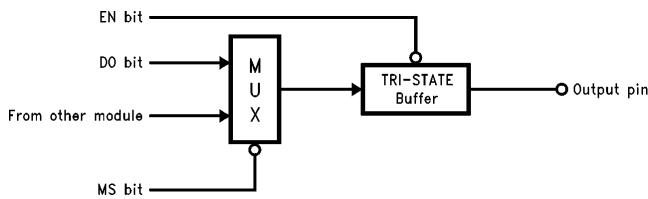

### 1.2.10 Ports

The Ports module controls the usage of general-purpose input and output pins. The pins are shared with other modules, and can be configured either as general-purpose I/O pins or as pins that belong to other modules. An input port always holds the current value/state of its associated pins. Output pins can be enabled or disabled (TRI-STATE®).

The number of general-purpose output pins can easily be increased using an external latch (e.g., DM74LS373).

## 1.3 OPERATION MODES

The NS32FX100 operates in one of three modes:

- **Normal Mode:** The CPU operates at the full clock frequency. Maximum current consumption is 200 mA.

- **Power Save Mode:** The CPU runs at 1/16 of the Normal mode frequency. DMA channels must be disabled, output ports must be TRI-STATE, and MCFG, except for bit 0, must be cleared. Maximum current consumption is 17 mA.

- **Freeze Mode:** The CPU is frozen by active reset and frozen clock; it is not connected to the backup battery. The NS32FX100 chip keeps track of elapsed time. The NS32FX200 and NS32FV100 can, if required, refresh the memories. Maximum current consumption is 1 mA with refresh, and 0.1 mA without refresh.

In normal operation, (see *Figure 1-5*) when reset is asserted, the NS32FX100 enters S6 of the Power Save mode. Switching from Power Save to Normal mode is carried out by software.

An RC circuit may be used to generate the CPU's input reset signal. The WATCHDOG trap signal (WDT), generated by the NS32FX100, may also force active CPU's input reset. The NS32FX100 receives its reset from the CPU output reset signal. This line should be pulled down by a resistor to force reset in case the CPU is not powered.

Failure of the main power source is detected externally (see *Figure 1-6*). The CPU is notified by a non-maskable interrupt. The NS32FX100 is also notified that power has failed, through the PFAIL input pin. The NS32FX100 power source should be externally switched to the backup battery. The

## 1.0 Fax-System Configuration (Continued)

power-fail input is asynchronous. It is recognized by the NS32FX100 during cycles in which the input setup-time requirement is satisfied.

Switching from Normal mode to Power Save mode, and vice versa, must always be carried out using the NS32FX100 explicitly. The clock scaling option of the CPU should not be used for this purpose.

### 1.3.1 Functionality

**State S1: Normal Mode.** The system operates at the full clock frequency. The NS32FX100 is powered by the main power supply. Software can switch the system to state S7, Power Save Mode.

The NS32FX100 switches to state S2, Power Fail, when  $\overline{\text{PFAIL}}$  is asserted.

**State S2: Power Fail.** In this state, the CPU enters an NMI handler, in which the software performs all the bookkeeping required for recovery and switches to full clock frequency. The software should write H'80 to MCFG. Once finished, the software activates the WATCHDOG trap output signal, which asserts the  $\overline{\text{RST}}$  input of the CPU by writing three times to the WATCHDOG.

When both  $\overline{\text{PFAIL}}$  and  $\overline{\text{RST}}$  are active, the NS32FX100 and the RAM must be powered from a battery. The CPU can be powered down.

When  $\overline{\text{RST}}$  is detected, the system chip goes from S2 to one of the following states:

State S3, if DRAM refresh is enabled (only in NS32FV100 and NS32FX200).

State S5, if no DRAM refresh is needed (NS32FX100—always).

**State S3: Complete Refresh Transaction.** If  $\overline{\text{RST}}$  is detected, while refresh is enabled, in state S2, a refresh transaction is performed. The system chip then switches to state S4.

**State S4: Freeze and Refresh.** In this state, the system chip de-activates the fast crystal oscillator and freezes the CCLK clock. Only the Elapsed Time Counter and the DRAM refresh generator are functional.

When the ETC count reaches zero, the state machine switches to state S5, and refresh transactions are stopped. Thus, the contents of the DRAM can be kept for a predefined period (software programmable). If the power failure lasts longer than this period, the system should disconnect the DRAM and leave only the ETC, and possibly an SRAM device, connected to the battery.

If  $\overline{\text{PFAIL}}$  goes high, the state machine switches to state S6, Power Restore.

**State S5: Freeze—No Refresh.** In this state only the ETC counter is active—counting the duration of the power failure. In this state the NS32FX100 functions with a supply voltage as low as 3V.

If  $\overline{\text{PFAIL}}$  goes high, the state machine switches to state S6, Power Restore.

**State S6: Power Restore.** This state can be entered either from Freeze Mode or during normal operation when reset is asserted. When entering from Freeze Mode ( $\overline{\text{PFAIL}}$  goes high),  $\overline{\text{RST}}$  is kept low for a few milliseconds by an external circuit. During this time, the fast crystal oscillator is activated and the CPU and NS32FX100 clocks are synchronized.

If refresh is enabled, the system chip will initiate refresh transactions during this time—the refresh rate is forced to a default value.

When  $\overline{\text{RST}}$  goes high, the NS32FX100 switches to state S7, Power Save Mode.

**State S7: Power Save Mode.** The CPU runs at a slow frequency—1/16 of the Normal Mode frequency.

The system can switch to S1, Normal Mode, under software control.

If  $\overline{\text{PFAIL}}$  input is asserted, the NS32FX100 switches to state S2, Power Fail.

FIGURE 1-5. System Chip States and Operation Modes

## 2.0 Architecture

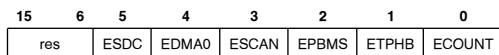

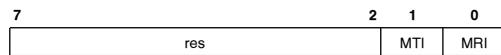

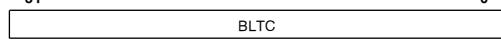

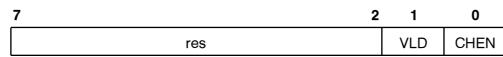

## 2.1 MCFG—MODULE CONFIGURATION REGISTER

The software can configure some of the NS32FX100 major operation modes by programming the Module Configuration Register (MCFG). Some of the bits in this register are also used to initialize the TPH block in the PRNTC, the bitmap shifter block in the PRNTC and the scanner module. When a bit in the MCFG is "0", the associated module is idle. Setting a bit to "1" enables the operation of the associated module. Prior to activating a module, its appropriate registers must be initialized by software.

**ECOUNT:** Enable internal counters of the TCU module. Once set, this bit can not be cleared by software. The TCU counters, except TIMER and WDC, must be initialized prior to setting this bit since they start working when the ECOUNT bit is set.

**ETPHB:** Enable Thermal Print-Head Block of the PRNTC module. The strobe-on and strobe-off counters of this block must be initialized prior to setting this bit to “1”.

**EPBMS:** Enable Bitmap Shifter Block of the PRNTC module. Clearing this bit is treated, by the Bitmap Shifter, as a hardware reset. The block starts operating when this bit is set. When disabled, DMA channel 1 uses the printer PCLK/DMRQ1 pin.

**ESCAN:** Enable Scanner module. Clearing this bit is treated, by the Scanner Controller, as a hardware reset. The module starts operating when this bit is set. When cleared to "0", DMA channel 2 uses the scanner pins and interrupt.

EDMA0: Enable scanner usage of DMA channel 0. When cleared to “0”, DMA channel 0 uses the scanner pins and interrupt.

ESDC: Enable Sigma-Delta CODEC module. When this bit is set the SDC operation takes place as described in Section 2.3.

Upon reset the non reserved bits of the MCFG are cleared to “0”, thus disabling the above modules and options.

## 2.2 TIMING CONTROL UNIT (TCU)

## 2.2.1 Features

- Generation and control of clock running frequency

- CPU and NS32FX100 synchronization by Phase Lock Loop (PLL)

- Fixed System-Tick interrupt of 100 Hz

- WATCHDOG

- Timer

- Buzzer

- Freeze mode

## 2.2.2 Operation

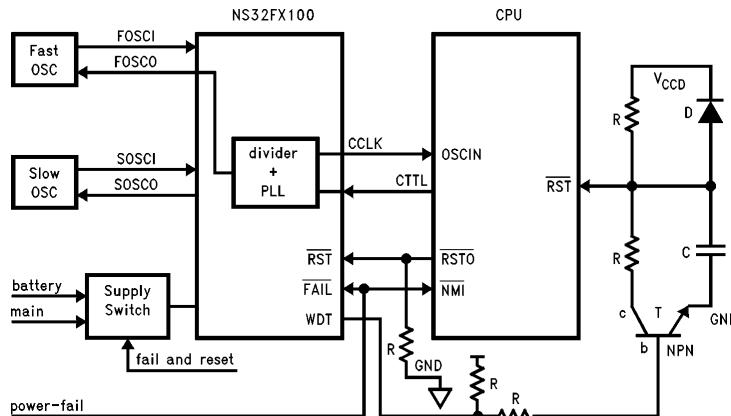

The Timing Control Unit (TCU) is responsible for generating the clocks, used for the various timing and counting functions in the system, and for freeze mode operation. *Figure 2-1* shows how the clocks are connected in an NS32FX100-based FAX system.

FIGURE 2-1 Clocks and Traps Connectivity

TL/EE/11331-6

## 2.0 Architecture (Continued)

### 2.2.2.1 External Clocks

The TCU contains two oscillators, the high-speed oscillator and the low-speed oscillator. The high-speed oscillator is the FAX system clocking source. It generates the CPU clock and, after division, clocks for the Sigma-Delta CODEC, scanner, printer and serial communications channels. A high-speed clock signal is input to the NS32FX100, from an external crystal, through the FOSCI pin. The NS32FX100 uses this signal to generate the CCLK clock, which serves as the input clock to the CPU. The CPU then divides CCLK by two, and generates CTTL which serves as the bus clock. The NS32FX100 includes a PLL to ensure synchronization between the NS32FX100 clocks and the CPU. CTTL is used to close the PLL loop and enable tracking of the CPU internal clocks.

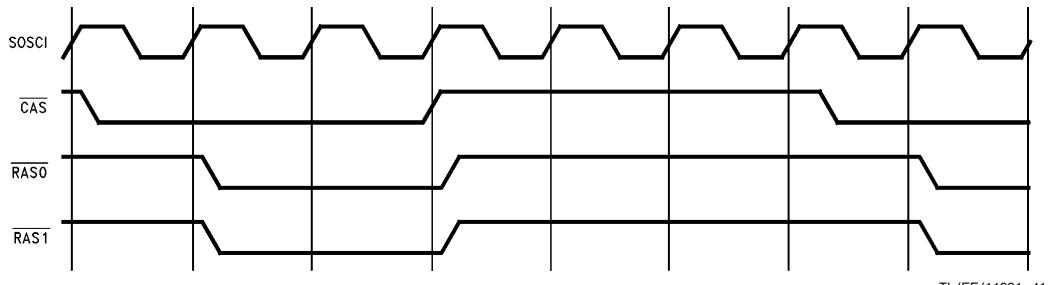

The low-speed oscillator, which gets its input through the SOSCI pin, is used to keep track of elapsed time and to operate the refresh requester. This oscillator operates in Normal mode, as well as in Power Save and Freeze modes.

The NS32FX100 controls the CPU running frequency. It may reduce the frequency by dividing CCLK by 16. To ensure accurate tracking of the CTTL phase by the NS32FX100, clock division should be carried out via the NS32FX100, and the power save mode of the CPU should not be used.

The slow oscillator, which operates during Normal, Power Save and Freeze modes, can be a 32.768 kHz oscillator for systems with memory refresh rate of up to 8 kHz. Systems with memory refresh rate higher than 8 kHz should use a slow oscillator of 455 kHz.

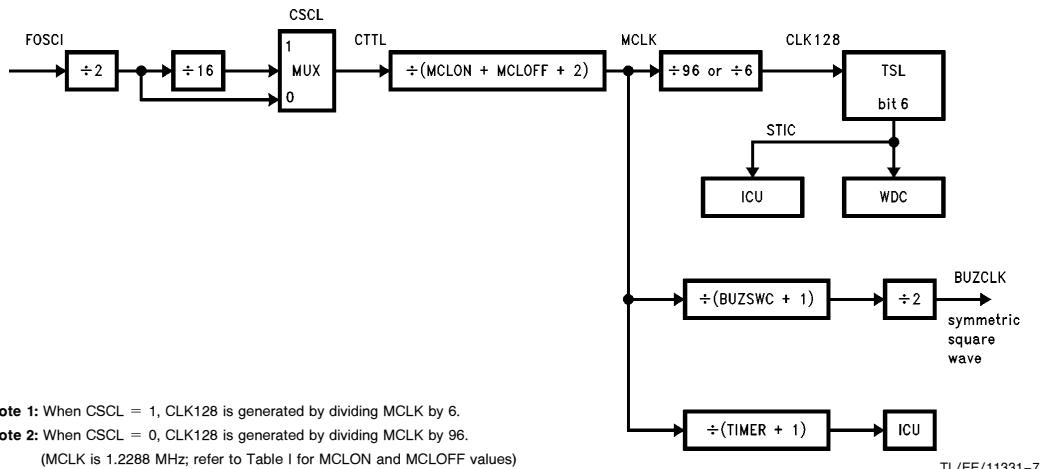

### 2.2.2.2 Internal Clocks

The TCU module generates a 1.2288 MHz Master Clock (MCLK). MCLK is generated by a programmable divider, which divides the CTTL input clock. The MCLK clock is used for synchronization throughout the NSFX100-based FAX system. In particular, the following are derived from MCLK:

- CLK128—A 12.8 kHz clock

- Time-Slots generator (TSL)—An 8-bit down counter fed by CLK128

The Time-Slots generator performs two functions:

- Division of each 20 ms period into 256 time slots

- Generation of a 100 Hz System Tick (STIC)

The time slots are used to synchronize the various components of the FAX system, e.g., the printer and scanner with their respective motors.

The System Tick is used by both the Interrupt Control Unit (ICU), for generating an interrupt, and by the WATCHDOG counter, as described in Section 2.2.3.

Several registers are provided, to control and use the TCU and I/O signals. These registers are described in Section 2.2.3.

FIGURE 2-2. High Speed Oscillator Clocks

FIGURE 2-3. Low Speed Oscillator Clocks

## 2.0 Architecture (Continued)

### 2.2.3 Registers

CSCL: CCLK (CPU Input Clock) Scale register.

| 7   | 5 | 4 | 3 | 0   |

|-----|---|---|---|-----|

| res |   | F |   | res |

F: Controls the CCLK frequency.

- 1: The CCLK frequency is the FOSCI input frequency divided by 16.

- 0: The CCLK frequency is the FOSCI input frequency.

Upon reset F is set to "1".

res: Reserved

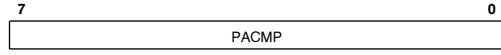

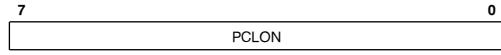

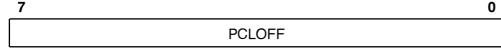

MCLOFF: MCLK Off Time. 8-bit register.

MCLOFF should be set to a fixed value, as shown in Table I, as a function of CTTL in normal operation mode, to generate a 1.2288 MHz clock, thus controlling the CTTL duty cycle.

MCLON: MCLK On Time. 8-bit register.

MCLON should be set to a fixed value, as shown in Table I, as a function of CTTL in normal operation mode, to generate a 1.2288 MHz clock, thus controlling the CTTL duty cycle.

TABLE 2-1. CTTL, MCLON and MCLOFF Values

| CTTL (MHz) | MCLON | MCLOFF |

|------------|-------|--------|

| 14.7456    | 5     | 5      |

| 15.9744    | 6     | 5      |

| 17.2032    | 6     | 6      |

| 18.4320    | 7     | 6      |

| 19.6608    | 7     | 7      |

| 20.8896    | 8     | 7      |

| 22.1184    | 8     | 8      |

| 23.3472    | 9     | 8      |

| 24.5760    | 9     | 9      |

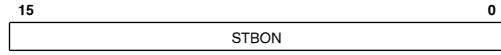

TIMER: Programmable Timer.

| 15    | 0 |

|-------|---|

| TIMER |   |

TIMER: The actual counter bits.

TIMER is a programmable, retriggerable, down counter which generates an interrupt pulse after a programmable number of MCLK cycles. When it goes below zero it stops counting and holds the value 0x0fff. If a new value is written to the TIMER before it reaches zero, it starts counting down from this new value. Reading TIMER gives its current contents.

Each bit in the TIMER register stands for 0.8  $\mu$ s (1/1.2288 MHz), thus the counter may represent the maximum value of  $0.8 \times 2^{16} \mu$ s.

Writing "0" to the timer is not allowed.

BUZCFG: Buzzer Configuration register.

| 7     | 6 | 5   | 0 |

|-------|---|-----|---|

| BCTRL |   | res |   |

BCTRL: Used to control the BUZCLK pin.

- 00 : BUZCLK pin = 0.

- 01 : BUZCLK pin = 1.

- 10 : BUZCLK pin = symmetric square wave, according to BUZSWC register.

- 11 : Reserved.

BUZSWC: Buzzer Square Wave Counter. 16-bit register.

Used for dividing MCLK to generate a symmetric square wave on the BUZCLK pin, as follows:

$$\text{BUZCLK frequency} = \text{MCLK}/(2^* \text{BUZSWC} + 2).$$

WDC: WATCHDOG Counter. 8-bit register.

The WATCHDOG Counter (WDC) is a down counter that counts STIC pulses. The counter generates a trap signal, on the WATCHDOG Trap (WDT) pin, if the counter reaches zero, or if WDC is written into more than once per STIC cycle. After reset WDC is idle (not counting). It starts counting after it is first written, starting from the value that is written into it. Once started, WDC can be stopped only by a hardware reset.

The WATCHDOG counts STIC pulses which are generated by the TCU. Therefore the WATCHDOG is functional only when the TCU's counters are enabled by the MCFG.ECOUNT bit.

Writing "0" to the timer is not allowed.

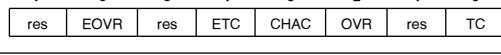

TSL: Time Slot down counter. 8-bit, read only.

Holds the current time slot. Upon reset the TSL bits are set to "1".

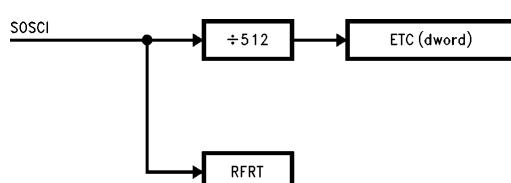

ETC: Elapsed Time Counter. A 32-bit down counter that counts at a rate of the slow clock (SOSCI) divided by 512.

Accessed as double-word only.

Not affected by reset.

At least four slow-clock cycles are required, between a write and any accesses to ETC, to avoid unpredictable results.

Successive reads from the ETC may differ from each other by two.

Example:

Read ETC, value = n (correct value should be n + 1)

Read ETC, value = n + 2 (correct value).

RFRT: Refresh Rate Control. 8-bit register.

The refresh is set to occur once every (RFRT + 1) cycles of the slow clock. RFRT must be set to a minimum value of 3.

The actual refresh transaction may be postponed due to synchronization with the fast clock and with other memory transactions.

## 2.0 Architecture (Continued)

After reset, RFRT is initialized to 6.

Writing to RFRT must be followed by read back to ensure that the RFRT has, in fact, been updated. This procedure must be repeated until RFRT is updated (value read = value written). RFRT exists only in the NS32FV100 and the NS32FX200.

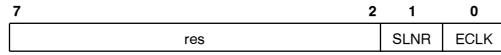

RFEN: Refresh enable

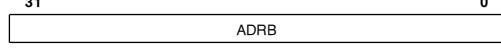

| 7   | 6  | 5 | 0   |

|-----|----|---|-----|

| res | EN |   | res |

EN 0: No refresh transactions.

1: Refresh transactions are issued by the chip according to the refresh rate, selected by RFRT.

After reset EN is set to "1".

RFEN exists only in the NS32FV100 and the NS32FX200.

### 2.2.3.1 Usage Recommendations

The ECOUNT bit, in MCFG, must be set to enable TCU counters operation.

## 2.3 SIGMA-DELTA CODEC (SDC)

### 2.3.1 Features

- 16-bit format Analog-to-Digital converter and Digital-to-Analog converter

- Full and Half Duplex operation

- Optimized for FAX and DATA Modems

- Various sampling rates for voice and data applications

- Total harmonic distortion better than  $-70$  dB

- Programmable IIR filters

- Programmable transmit filters

- Programmable receive filters

- Programmable echo canceling filter

- Programmable gain control

- Programmable fine timing tuning

- Digital loop-back mode

- Reduced CPU load by 12-level transmission FIFO and 12-level reception FIFO

### 2.3.2 Operation

The Sigma Delta CODEC performs high resolution analog-to-digital (A/D) and digital-to-analog (D/A) conversions using an over sampling technique. This module is optimized for use as the analog front end for Digital Signal Processing (DSP) applications such as modems or voice processing.

The SDC's main advantage, compared to other A/D and D/A convertors, is the use of digital circuitry resulting in high reliability and reduced cost. The SDC solution incorporates a second-order, digital Sigma-Delta modulator and a noise shaping technique to improve performance.

The digital parts of the converters are implemented on-chip and a few external components implement the analog parts. NSFAX Software package fully supports the SDC. Software drivers handle both the SDC initialization and data transfers. National Semiconductor's modem software is usually provided in binary form, and hence the internal structure of the SDC is transparent to the user. A detailed description of the SDC is available only for source-level customers.

### 2.3.2.1 Block Diagram

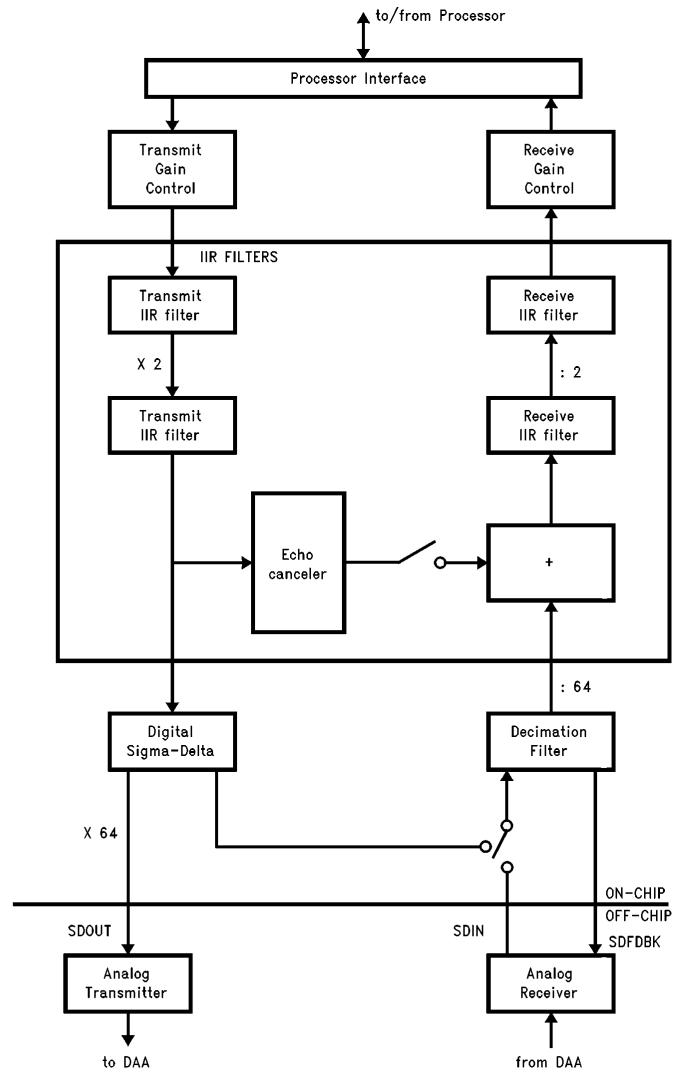

The Sigma-Delta CODEC block diagram is shown in *Figure 2-4*.

## 2.0 Architecture (Continued)

FIGURE 2-4. Sigma-Delta Block Diagram

TL/EE/11331-9

## 2.0 Architecture (Continued)

A full Sigma-Delta CODEC includes a digital part and an analog part. The NS32FX100 includes the digital part, and the analog part should be implemented externally.

### 2.3.2.2 On-Chip Digital Blocks

Sigma-Delta Over Sampling Rate (OSR) is 128 times the Sampling Rate (SR). Some Sigma-Delta blocks use also Double Sampling Rate (DSR).

For communication applications the SR is 9.6 kHz, DSR is 19.2 kHz and the OSR is 1.2288 MHz. For voice applications the SR is 8 kHz, DSR is 16 kHz and the OSR is 1.024 MHz.

**DF (Decimation Filter)**—Receives 1-bit stream at OSR and decimates it to 16-bit at DSR.

**IIR Filters**—The IIR filters include Transmission, Reception and Echo-canceler programmable filters. The Echo-canceling filter can be bypassed.

The Transmission IIR includes two filters. The first filter operates at SR. The second filter interpolates the data rate by two. Thus the filter operates at DSR.

The Reception IIR includes two filters. The first filter operates at DSR and decimates the data rate by two. Thus the second filter operates at SR.

The Echo-canceler filter works at DSR. This filter is used to cancel the echo path.

**Receive Gain Control (RGC)**—Amplifies or attenuates the received data, to achieve the required signal level, controlled by software Automatic Gain Control (AGC).

**Transmit Gain Control (TGC)**—Attenuates the transmitted data, to achieve the required signal level, controlled by software Automatic Gain Control (AGC).

**Digital Sigma-Delta (DSDM)**—Transforms the 16-bit transmitted data at DSR into a 1-bit stream at OSR. A second-order digital Sigma-Delta circuit performs this function.

**Processor Interface (PI)**—Contains the SDC control and data registers, a 12-level transmission FIFO, a 12-level reception FIFO and a clock divider unit.

### 2.3.3 Programmable Functions

The Sigma-Delta programming model consists of the following elements:

- IIR coefficients memory

- Data registers

- Control registers

#### 2.3.3.1 Sigma-Delta ON/OFF

The SDC module is enabled by MCFG.ESDC control bit. When MCFG.ESDC is “0” the SDC module is disabled.

The user can access all SDC memory-mapped addresses (IIR coefficients and SDC registers) only while MCFG.ESDC is active. Any attempt to access SDC memory-mapped addresses while MCFG.ESDC is “0” will cause an unpredictable result.

To turn off SDC, turn off receive mode (SDCCTL.RE=0) and transmit mode (SDCCTL.TE=0) and only then clear MCFG.ESDC to “0”.

### 2.3.4 Off-Chip Analog Circuits

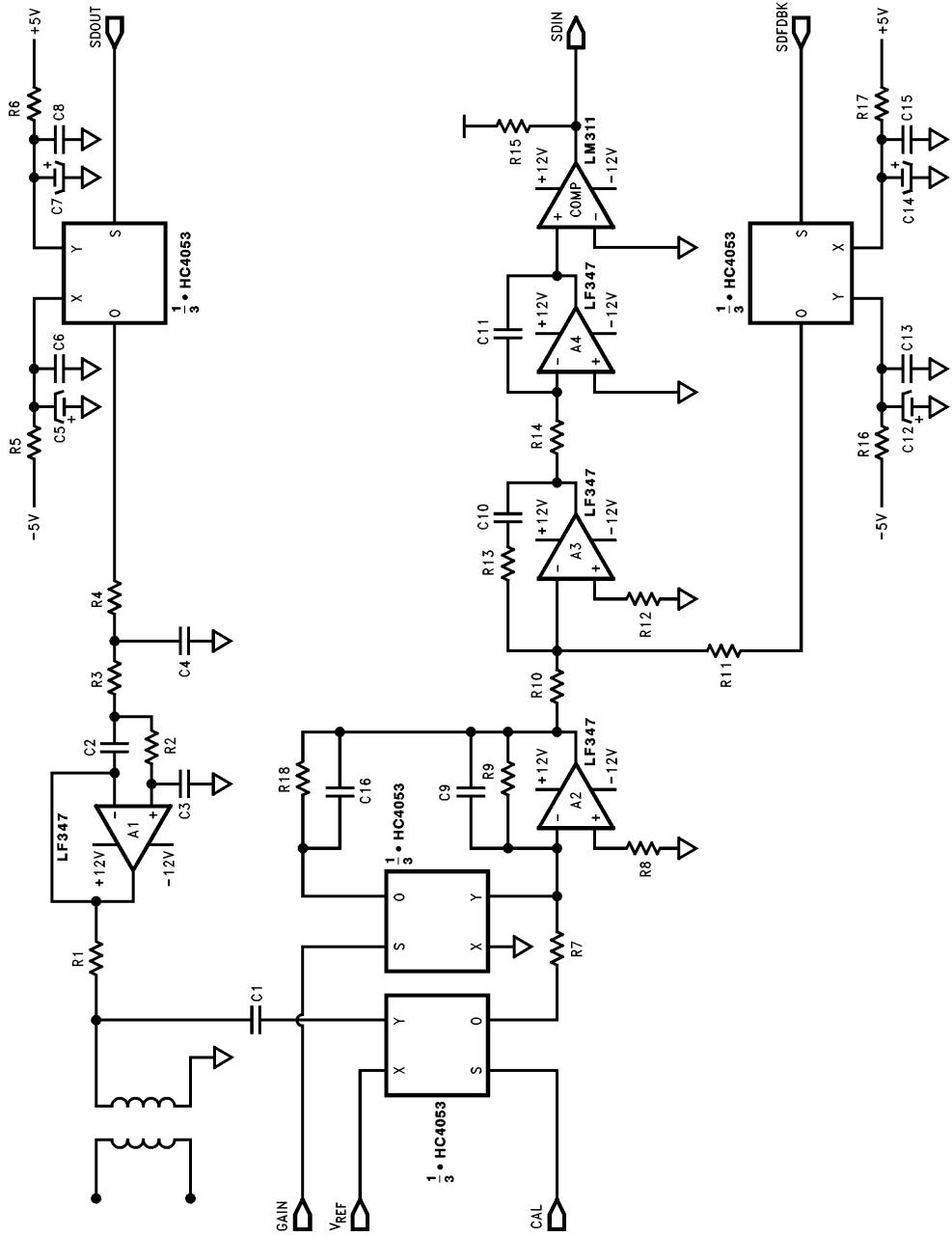

The circuit required to connect the SDC on-chip module to a 2-wire line is shown in *Figure 2-5*. The components are detailed in the following table:

TABLE 2-2. Component Values

| Component | Value           | Tolerance |

|-----------|-----------------|-----------|

| R1        | 600 $\Omega$    | 1%        |

| R2        | 47 k $\Omega$   | 5%        |

| R3        | 47 k $\Omega$   | 5%        |

| R4        | 47 k $\Omega$   | 5%        |

| R5        | 330 $\Omega$    | 5%        |

| R6        | 330 $\Omega$    | 5%        |

| R7        | 15.4 k $\Omega$ | 1%        |

| R8        | 56 k $\Omega$   | 5%        |

| R9        | 100 k $\Omega$  | 5%        |

| R10       | 22 k $\Omega$   | 5%        |

| R11       | 22 k $\Omega$   | 5%        |

| R12       | 56 k $\Omega$   | 5%        |

| R13       | 5.1 k $\Omega$  | 5%        |

| R14       | 5.6 k $\Omega$  | 5%        |

| R15       | 1.0 k $\Omega$  | 5%        |

| R16       | 330 $\Omega$    | 5%        |

| R17       | 330 $\Omega$    | 5%        |

| R18       | 56 k $\Omega$   | 5%        |

| C1        | 0.1 $\mu$ F     | 10%       |

| C2        | 3.3 nF          | 10%       |

| C3        | 100 pF          | 10%       |

| C4        | 1 nF            | 10%       |

| C5        | 22 $\mu$ F      | 10%       |

| C6        | 0.1 $\mu$ F     | 10%       |

| C7        | 22 $\mu$ F      | 10%       |

| C8        | 0.1 $\mu$ F     | 10%       |

| C9        | 47 pF           | 10%       |

| C10       | 330 pF          | 10%       |

| C11       | 200 pF          | 10%       |

| C12       | 22 $\mu$ F      | 10%       |

| C13       | 0.1 $\mu$ F     | 10%       |

| C14       | 22 $\mu$ F      | 10%       |

| C15       | 0.1 $\mu$ F     | 10%       |

| C16       | 100 pF          | 10%       |

## 2.0 Architecture (Continued)

FIGURE 2-5. SDC Off-Chip Analog Circuit

TL/EE/11331-10

## 2.0 Architecture (Continued)

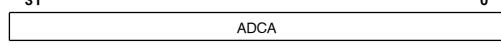

### 2.3.4.1 Analog Transmitter

The input to the transmit analog circuit is the serial bit stream at OSR, which is generated by DSDM. This serial bit stream is fed to a 1-bit D/A converter. This D/A converter is implemented by an analog switch, which selects either +5V or -5V inputs. These voltages are filtered by an RC, low-frequency, Low Pass Filter (LPF), to filter supply noise, and to avoid crosstalk between the transmit and receive circuits. The D/A output is filtered, by a three pole LPF with unity gain, to attenuate the out-of-band quantization noise. The output of the LPF passes through a 600Ω resistor.

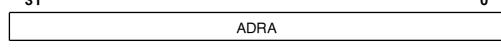

### 2.3.4.2 Analog Receiver

The reception analog circuit obtains its analog input signal from an isolation transformer. The signal passes through a buffer amplifier, and then enters the Sigma Delta second order loop. The amplifier has two gain levels. One gain level provides a total gain of 0 dB and the second level provides a total gain of 9 dB. The two gain level are controlled by the GAIN signal.

The Sigma Delta second order loop contains two integrators and a comparator to zero. The comparator output is the SDIN input to the on-chip Sigma Delta part. SDIN is sampled on-chip at OSR, is passed to the digital filters and returns as feedback (SDFDBK pin) to the analog part. This feedback enters a 1-bit D/A converter. This D/A converter is implemented by an analog switch, which selects either +5V or -5V inputs. These voltages are filtered by an RC low frequency LPF, to reduce supply noise, and to avoid crosstalk between the transmit and receive circuits. The feedback is an input to the first integrator unit.

The receiver analog circuit can be calibrated by receiving a known reference voltage. When the circuit is calibrated, the receiver input signal is a known reference voltage ( $V_{REF}$ ), otherwise the receiver input is the input signal from the isolation transformer.

### 2.3.5 Registers

The following is a partial list of registers. For a full list see the detailed SD documentation, available to source-level customers.

**SDTX** Sigma-Delta Transmit Data. This register is the transmit FIFO port. Any attempt to read from this register will cause an unpredictable result.

**SDRX** Sigma-Delta Transmit Data. This register is the receive FIFO port. Any attempt to write to this register will cause an unpredictable result.

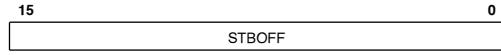

**SDCNTL** Control register

| 15  | 13  | 12   | 11  | 7  | 6   | 5  | 4   | 3 | 2 | 1 | 0 |

|-----|-----|------|-----|----|-----|----|-----|---|---|---|---|

| N/A | N/A | PRES | N/A | TE | N/A | RE | N/A |   |   |   |   |

Upon reset SDCNTL.PRES is loaded at the minimum pre-scale value in Full-duplex mode, "01001". All other implemented bits of SDCNTL are cleared to "0".

NOTE: Bits marked N/A are available only for source-level customers. For other customers, they must not be modified.

**RE** Enables or disables receive mode.

0 : Receive mode is disabled.

1 : Receive mode is enabled.

**TE** Enables or disables transmit mode.

0 : Transmit mode is disabled.

1 : Transmit mode is enabled.

**PRES** CTTL prescale. The SDC over-sampling rate is generated by dividing the CTTL clock by a pre-scale divider. The PRES value is calculated as follows:

$$\text{PRES} = \lceil (\text{CTTL}/\text{OSR}) - 1 \rceil.$$

Some examples for sample rate 9.6 kHz and 8 kHz are given below:

| SDCNTL.PRES | CTTL Frequency (Sample Rate 9.6 kHz) | CTTL Frequency (Sample Rate 8.0 kHz) |

|-------------|--------------------------------------|--------------------------------------|

| 01011       | 14.7456 MHz                          | 12.2880 MHz                          |

| 01110       | 18.4320 MHz                          | 15.3600 MHz                          |

| 01111       | 19.6608 MHz                          | 16.3840 MHz                          |

| 10000       | 20.8896 MHz                          | 17.4080 MHz                          |

| 10001       | 22.1184 MHz                          | 18.4320 MHz                          |

| 10010       | 23.3472 MHz                          | 19.4560 MHz                          |

| 10011       | 24.5760 MHz                          | 20.4800 MHz                          |

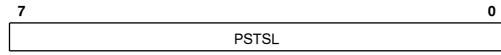

**SDFTM** Fine Timing register.

| 7   | 4 | 3   | 2 | 0    |

|-----|---|-----|---|------|

| res |   | ADV |   | STEP |

**STEP** Advance or delay steps amount (0–7)

**ADV** Advance direction

0: Delay mode is enabled

1: Advance mode is enabled

Writing to this register, while SDCNTL.RE is active, is allowed only if SDFTM.STEP is equal to a "0".

Writing to this register, while both SDCNTL.RE is active and SDFTM.STEP is not "0", will cause an unpredictable result.

While SDCNTL.RE is active, this register holds the number of advance or delay steps yet to be executed.

**SDRGC** Receive Gain Control register. Used to amplify or attenuate the receive IIR output samples. The value to be written in SDRGC register is  $128 \times 10(\text{Gain}/20)$ , rounded to the nearest integer number.

Some examples are given in the following table:

| Gain (dB) | SDRGC  |

|-----------|--------|

| -18       | 0x0010 |

| -17.5     | 0x0011 |

| .         | .      |

| .         | .      |

| 0         | 0x0080 |

| 0.1       | 0x0081 |

| .         | .      |

| .         | .      |

| 48.0      | 0x7D98 |

## 2.0 Architecture (Continued)

**SDTGC** Transmit Gain Control register. Used to attenuate the transmit IIR input samples. The value to be written in SDTGC register is  $16384 \times 10$ (Gain/20), rounded to the nearest integer number.

Some examples are given in the following table:

| Gain (dB) | SDTGC  |

|-----------|--------|

| -42       | 0x0082 |

| -41.9     | 0x0084 |

| .         | .      |

| .         | .      |

| 0         | 0x4000 |

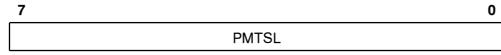

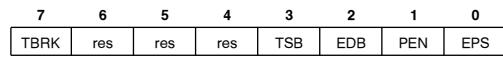

**SDSTAT** Status Register. Provides information about the status of the Sigma-Delta operation.

| 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|------|------|------|------|------|------|------|------|

| TSAT | RSAT | TFNE | RFNE | TERR | RERR | TIRQ | RIRQ |

**RIRQ** When "1" during receive enable (SDCNTL.RE=1), it indicates that N or more samples are ready in the receive FIFO. This bit will remain high as long as the number of samples is greater than, or equal to, N. If this bit is not masked by SDMASK.RIRQ it will cause an interrupt.

**TIRQ** When "1" during transmit enable (SDCNTL.TE=1), it indicates that less than N samples are ready in the transmit FIFO. This bit will remain high as long as the number of samples is less than N. If this bit is not masked by SDMASK.TIRQ it will cause an interrupt.

**RERR** When "1" during receive enable (SDCNTL.RE=1) it indicates an attempt to read an empty receive FIFO, or incoming sample when the receive FIFO is full. If this bit is not masked by SDMASK.RERR it will cause an interrupt.

**TERR** When "1" during transmit enable (SDCNTL.TE=1) it indicates an attempt to read from an empty transmit FIFO, or writing to a full transmit FIFO. If this bit is not masked by SDMASK.TERR it will cause an interrupt.

**TFNE** Transmit FIFO Not Empty, when "0" indicates that the transmit FIFO is empty.

**RFNE** Receive FIFO Not Empty, when "0" indicates that the receive FIFO empty.

**RSAT** Reception Saturation. This bit is set to "1", whenever a saturation value is created in the receive IIR (including the echo-canceling filter, when enabled) or in the receive gain control logic.

**TSAT** Transmit Saturation. This bit is set to "1", whenever a saturation value is created in the transmission IIR or in DSDM.

Upon reset all implemented bits in the SDSTAT register are cleared to "0".

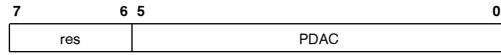

**SDMASK** Mask Register. Enables masking of SDC interrupts.

| 7   | 4    | 3    | 2    | 1    | 0 |

|-----|------|------|------|------|---|

| res | TERR | RERR | TIRQ | RIRQ |   |

**RIRQ** Mask Receive Interrupt Request.

0 : SDSTAT.RIRQ will not cause an interrupt.

1 : SDSTAT.RIRQ will cause an interrupt.

**TIRQ** Mask Transmit Interrupt Request.

0 : SDSTAT.TIRQ will not cause an interrupt.

1 : SDSTAT.TIRQ will cause an interrupt.

**RERR** Mask Receive Error.

0 : SDSTAT.RER will not cause an interrupt.

1 : SDSTAT.RER will cause an interrupt.

**TERR** Mask Transmit Error.

0 : SDSTAT.TER will not cause an interrupt.

1 : SDSTAT.TER will cause an interrupt.

### 2.3.6 Usage Recommendations

The SDC should be enabled (by setting the SDC bit in the MCFG register to "1") before programming SDMASK and SDCNTL.

## 2.4 SCANNER CONTROLLER (SCANC)

### 2.4.1 Features

- Programmable generation of control signals which support a wide range of Charge Coupled Device (CCD) and Contact Image Sensor (CIS) scanners

- Supports line scan times of 2.5 ms, 5 ms, 10 ms and 20 ms

- On-Chip shading-correction circuitry, using reference line values stored in the system RAM, via DMA channel 0

- On-Chip dithering and Gamma correction circuit of 16 grey levels. (64 grey levels in NS32FX200)

- Support for Automatic Background Control (ABC) and edge enhancement with external circuitry

- On-Chip multiplying Digital-to-Analog Converter (DAC) for compensation of scanner offset

- Automatic writing of scanned bitmap to memory via DMA channel 2

- Optional bypass of on-chip video-data generation to support external image enhancement

### 2.4.2 Operation

The Scanner Controller Module (SCANC) consists of a scanner signals generator block, a video handling block (shading compensation, dithering and bitmap accumulation) and a stepper motor control block. The module includes analog and digital circuits. It uses two DMA channels—one for fetching a reference line and one for storing the digitized video data. The module is synchronized with the TCU module. The operation of SCANC, and the allocation of DMA channels 0 and 2 to the Scanner Controller or for external usage, are controlled by the Module Configuration Register (MCFG). The module's minimum operation frequency is 14.7456 MHz (i.e., it can not operate in Power Save mode). Some of the Scanner signals can be assigned to an I/O port when the Scanner is not used (e.g., after reset).

## 2.0 Architecture (Continued)

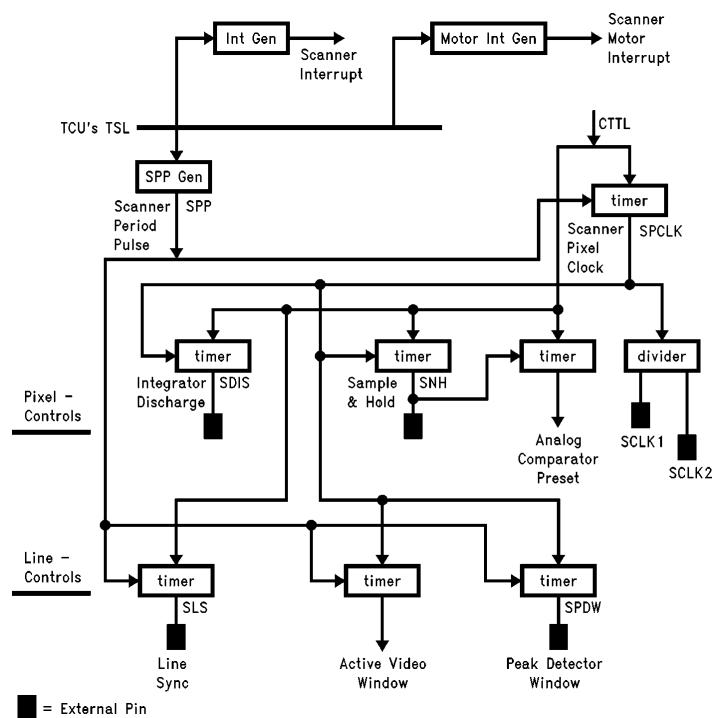

### 2.4.2.1 Scanner Signals Generator Block

This block generates the timing control signals required by CIS and CCD scanners. Scanners with line scan time of 2.5 ms, 5 ms, 10 ms or 20 ms are supported. This period is derived from the TCU module's time-slots (generated by the TCU dividing each 20 ms into 256 time-slots).

The block generates the following signals:

- Scanner Period Pulse (SPP), an internal synchronization pulse.

- Scanner Pixel Clock (SPCLK), an internal pixel clock (its frequency is twice the scanner clock).

- Pixel clocks (two phases—SCLK1 and SCLK2).

- Integrator Discharge Pulse (SDIS).

- Sample and Hold control clock (SNH). Used to sample the scanner analog video signal.

- Scan Line Synchronization Pulse (SLS). Indicates the beginning of a scan line.

- Scanner Comparator Preset, an internal initialization signal for the on-chip analog comparator.

- Active window, an internal time frame that controls the operation of the bitmap generator.

- Peak Detector Window (SPDW). One of the Automatic Background Control (ABC) control signals.

- Scanner interrupt pulse.

- Scanner motor interrupt pulse.

Each signal is generated by an independently programmed waveform generator. The flexible waveform definition facilitates the support of different scanner models.

TL/EE/11331-11

FIGURE 2-6. Block Diagram of Scanner's Signals Generator Block

## 2.0 Architecture (Continued)

### 2.4.2.2 Scanner Period Pulse (SPP) Generation

The Scanner Period Pulse (SPP) is used to synchronize all the scanner control signals. It is derived from the time slots generated by the TCU module (which divides each 20 ms into 256 time slots).

#### SPCLK Generation

The internal Scanner Pixel Clock (SPCLK) is generated by dividing CTTL by a programmable prescale value. The result is a video clock which is twice the frequency of the scanner clocks. SPCLK is used for generation of other scanner signals. The value of SPCLK should be determined according to the scanner specification.

The SPCLK pre-scale divider is reset by each SPP leading edge. As a result, the first SPCLK cycle after the SPP may be distorted. Software should program the control registers SAVWD, SLSD and SPDWD so that the first pixel after the SPP is ignored.

#### SCLK1 and SCLK2 Generation

The two scanner clocks, SCLK1 and SCLK2, are generated by dividing SPCLK by two. SCLK1 is high and SCLK2 is low after SPP leading edge.

#### SDIS and SNH Generation

The Integrator Discharge Pulse (SDIS) and the Sample-and-Hold Control Clock (SNH) are generated by timers which are clocked by CTTL and triggered by SPCLK. For each of these signals, the polarity, the delay (between SPCLK and its leading edge) and the width are software programmable. The total number of delay and width cycles must not exceed the number of CTTL cycles in one SPCLK period.

#### Analog Comparator Preset Generation

The Analog Comparator Preset is an internal signal used to initialize the on-chip analog comparator. It is generated by a timer, clocked by CTTL and triggered by SNH leading edge.

TL/EE/11331-12

**Note:** In this figure SDIS has inverted polarity (DISP = 0).

FIGURE 2-7. Scanner Pixel Control Signals

## 2.0 Architecture (Continued)

### SLS Pulse Generation

Scan Line Sync (SLS) is generated by a timer according to a calculated delay (in CTTL cycles) from the beginning of the SPP pulse. The delay between the beginning of SPP and the leading edge of SLS, SLS pulse width, and SLS polarity are software programmable.

The first pixel clock after SPP may be distorted. SLS must be programmed so that this pixel is ignored.

### Active Video Window and Peak Detector Window Generation

The active Video Window, signaling the valid data window, and the Peak Detector Window, signaling the programmable window for Automatic Background Control, are generated

by timers which are triggered by SPP and clocked by SPCLK.

### Scanner Interrupt Generation

The scanner interrupt is a rising-edge interrupt, generated at the beginning of a time slot which is defined by the Scanner Interrupt Time-Slot register (SITSL).

### 2.4.2.3 Video Handling Block

The Video Handling Block is an Analog-to-Digital convertor for the analog video signal. It enables shading, half-toning and bi-level support with Automatic Background Control (ABC). It also allows pixel generation control, using external circuitry.

TL/EE/11331-13

**Note 1:** The delay is controlled by the respective register (SLSD, SAVWD or SPDWD).

**Note 2:** Measured in CTTL cycles.

**Note 3:** Measured in SPCLK cycles.

FIGURE 2-8. Scanner Period Control Signals

TL/EE/11331-14

FIGURE 2-9. Block Diagram of Scanner's Video Handling Block

## 2.0 Architecture (Continued)

### Video DAC (Shading-Compensation)

The shading-compensation circuit includes an 8-bit multiplying Digital-to-Analog Converter (DAC) that multiplies SVI, the analog input from an external video sample and hold circuit, with a digital reference value (white line) fetched by DMA channel 0. The Video DAC compensates for the input offset, according to the compensation value in the SVDB register, and the control bits in the SVHC register. By writing to the SVDB register, it is possible to control the Video DAC directly by software. In this case, the same 8-bit value replica should be written to both bytes of the register. When the compensation value is greater than the input video signal, the compensated video data signal is "0". The compensated video data, at the output of the video DAC, feeds the video comparator. It also goes to an external pin (SCVO) to enable external implementation of an Automatic Background Control (ABC) circuit.

To enable a longer latency for DMA channel 0 operations, a double buffer is used. DMA cycles are synchronized to the leading edge of SNH during active video window.

When DMA channel 0 is disabled, the same value should be written to both bytes of the Scanner Video DAC Buffer (SVDB) register.

### 2.4.2.4 Threshold DAC (Dithering and Automatic Background Control)

The dithering circuit includes an 8-bit multiplying DAC that multiplies SBG, the input from an external Automatic Background Control (ABC) circuit, with the digital dither value from one of the eight dither bytes. The threshold DAC has no output pin and no  $I_{OFF}$ , internal offset current, but is otherwise similar to the video DAC.

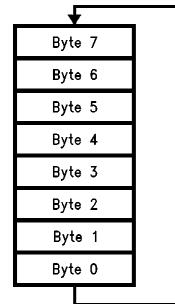

The block includes a cyclic buffer for 64 grey levels. The cyclic buffer contains eight bytes, only one of which is accessible at any given time. Any buffer access (software read, software write or hardware read) causes a cyclic shift in the buffer after the access is completed. A hardware ac-

cess, on SNH leading edge, loads the value of the accessed byte to the DAC's input. Hardware access can take place only during active video window. Software access is carried out via the SDITH register. Software may not access the buffer during active video window. The dither cyclic buffer is shown in *Figure 2-10*. For a gray-level image, ABC should be disabled by externally clamping the SBG input to a constant source. For this purpose, an external analog switch, controlled by any of the Ports module, may be used.

**Note:** Eight dither registers are available on all system chips. The difference between the number of supported gray levels lies in the different characteristics of the associated analog circuits.

TL/EE/11331-15

**FIGURE 2-10. Dither Cyclic Buffer**

### Video Comparator

The output of the shading-compensation (video) DAC is compared by the video comparator with the output of the dithering (threshold) DAC. The comparator feeds the pixel generator.

### Bitmap Accumulator

The bitmap accumulator includes a pixel generator and a bitmap shift register. It uses DMA channel 2 to store the bitmap into memory.

## 2.0 Architecture (Continued)

### Pixel Generator

Pixels may be treated in one of three ways:

No bypass The output of the video comparator is an image pixel. It may be inverted by the pixel generator before the pixel is shifted into the bitmap shifter.

Input bypass (Available in the NS32FX200 only.) The video comparator output is bypassed, (the video DAC output is taken through the SCVO output pin to an external circuit), and an externally generated pixel is taken as the input to the pixel generator through the SBYPS pin.

Output bypass (Available in the NS32FX200 only.) As in the No bypass case, the comparator feeds the bitmap shifter. In addition, the last sampled pixel, sampled on the last SNH leading edge and inverted, is driven onto the SBYPS pin for optional use by an external circuit (e.g., for edge emphasis).

The operation mode of the pixel generator, in the NS32FX200, is controlled by the Scanner Video Handling Control register (SVHC) and Port C control registers (PCMS, PCEN). It must be configured as "No bypass" in the NS32FX100 and NS32FV100.

No bypass — SVHC.BYPASS = 0 and

PCMS.MS4 = 0.

Input bypass — SVHC.BYPASS = 1 and

PCMS.MS4 = 1 and

PCEN.EN4 = 0.

Output bypass — SVHC.BYPASS = 0 and

PCMS.MS4 = 1 and

PCEN.EN4 = 1.

Note that the pin output value is unpredictable if the scanner module is disabled (MCFG.ESCAN = 0) while both PCMS.MS4 and PCEN.EN4 are set.

The pixel generator can be configured to invert a pixel before it is shifted.

### Bitmap Shifter

The pixel generator output is accumulated and stored into memory via DMA channel 2. Pixels are shifted from left to right i.e. The first pixel in each word is the Least Significant Bit (LSB). The bitmap is double buffered by the Scanner Bitmap Shifter (SBMS) and a word buffer between the scanner module and the DMA channel. The shifter operation is enabled during active window only, and clocked by SNH leading edge. In order to allow software intervention in collecting the scanner's bitmap, the shifter is readable by software.

### 2.4.2.5 Stepper Motor Control Block

The stepper motor is controlled by four phases. The motor direction and speed is controlled by setting, or clearing, each phase as scanning progresses. The motor is controlled by setting the time-slots in which the phases should be changed (in the SMTSL register). When the set time-slot is reached, an interrupt is generated and the phase values are updated to the values in the phase register (SMPH) in the Ports module.

### 2.4.3 Registers

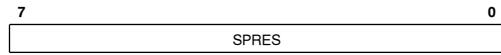

SPRES: Scanner SPCLK Prescale. 8-bit register.

One SPCLK cycle time equals (SPRES + 1) CTTL cycles.

SDISD: Scanner Discharge Delay. Write only. 8-bit register.

Controls the delay between the edge of SCLK1 and the leading edge of the SDIS signal. The delay is (SDISD + 1) CTTL cycles.

SDISW: Scanner Integrator Discharge Pulse Width. Write only. 8-bit register.

The width is (SDISW + 1) CTTL cycles.

SNHD: Scanner Sample and Hold Delay. Write only. 8-bit register.

Controls the delay between the edge of SCLK1 and the leading edge of SNH signal. The delay is (SNHD + 1) CTTL cycles.

SNHW: Scanner Sample and Hold Pulse Width. Write only. 8-bit register.

The width is (SNHW + 1) CTTL cycles.

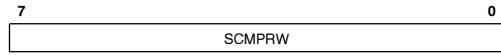

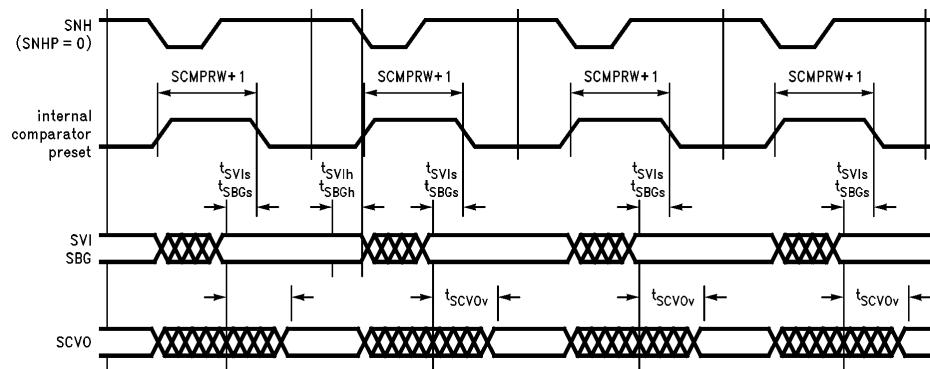

SCMPRW: Scanner Comparator Preset Pulse Width. Write only. 8-bit register.

The width is (SCMPRW + 1) CTTL cycles.

SLSD: Scanner Line Sync Delay. Write only. 8-bit register.

Controls the delay between the Scanner's Period Pulse (SPP) and the leading edge of the SLS signal.

SLSW: Line Sync Pulse Width. Write only. 8-bit register.

The width is (SLSW + 1) CTTL cycles.

SAVWD: Active Video Window Delay. Write only. 16-bit register.

Controls the delay between the leading edge of the Scanner's Period Pulse (SPP) and the beginning of the active video window (number of ignored pixels).

SAVWW: Active Video Window Width. Write only. 16-bit register.

The width is (SAVWW + 1) SPCLK cycles.

SPDWD: Peak Detector Window Delay. Write only. 16-bit register.

The delay between leading edge of Scanner's Period Pulse (SPP) and the beginning of peak detector window.

SPDWW: Peak Detector Window Width. Write only. 16-bit register. The width is (SPDWW + 1) SPCLK cycles.

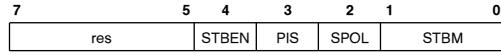

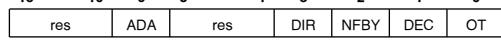

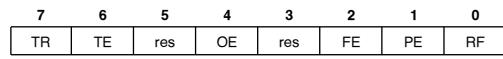

SGC: Scanner Signals Generator Control register.

## 2.0 Architecture (Continued)

|     |      |      |      |      |   |

|-----|------|------|------|------|---|

| 7   | 4    | 3    | 2    | 1    | 0 |

| res | LSPP | PDWP | SNHP | DISP |   |

DISP: Scanner Discharge Pulse Polarity.

0 : Active low

1 : Active high

SNHP: Sample and Hold Pulse Polarity.

0 : Active low

1 : Active high

PDWP: Peak Detector Window Polarity.

0 : Active low

1 : Active high

LSPP: Line Sync Pulse Polarity.

0 : Active low

1 : Active high

SPP: Scanner period pulse. 8-bit register.

7F : Period pulse each 20 ms (TSL=255).

BF : Period pulse each 10 ms (TSL=255 and 127).

DF : Period pulse each 5 ms (TSL=255, 63, 127 and 191).

EF : Period pulse each 2.5 ms (TSL=255, 31, 63, 95, 127, 159, 191, 223).

SPP must be programmed with one of these four values, otherwise the period pulse frequency is undefined.

(TSL indicates the appropriate TCU time slot.)

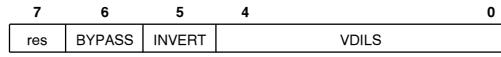

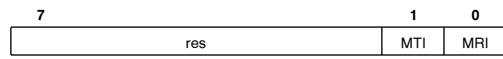

SVHC: Scanner Video handling Control Register.

|     |        |        |   |       |

|-----|--------|--------|---|-------|

| 7   | 6      | 5      | 4 | 0     |

| res | BYPASS | INVERT |   | VDILS |

VDILS: Video DAC Input Level Shift.

Number of current steps to be added-to/subtracted-from the input of the Video DAC. This field is encoded as: Sign bit + four magnitude bits. When the input of the video DAC is to be incremented, the sign bit, bit 4, should be set to "1". When it is to be decremented, the sign bit should be "0". Legal values for VDILS are in the range

1F . . . 10

0 . . . 0F

INVERT: 0 : Pixel not inverted by the pixel generator

1 : Pixel inverted by the pixel generator

BYPASS: (NS32FX200 only.)

0 : No bypass. The comparator output is received by the pixel generator.

1 : Bypass enabled. The SBYPS input is selected by the pixel generator and the comparator output is ignored.

**Note:** Only the NS32FX200 enables bypassing the video comparator output through the SBYPS pin. BYPASS must always be cleared to "0" in the NS32FX100 and NS32FV100.

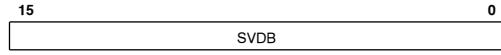

SVDB: Scanner Video DAC Buffer. 16-bit register.

Holds two bytes of compensation values. The lower byte is used first and the upper byte is used for the next pixel.

Normally written by DMA channel 0.

Accessible by software when the DMA channel is either disabled or not allocated to the scanner (i.e., MCFG.EDMA0 = 0).

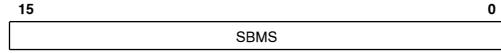

SBMS: Scanner Bitmap Shifter. Read Only. 16-bit register.

Pixels are shifted from left to right, i.e., the first pixel in each word is the LSB.

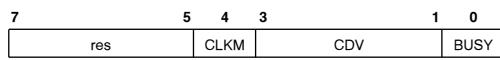

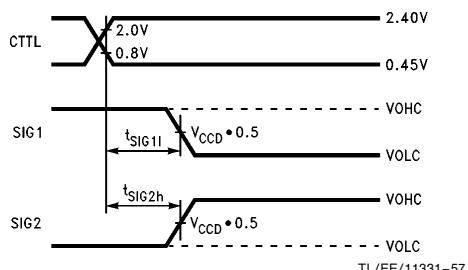

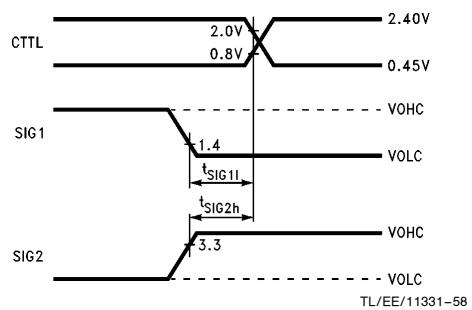

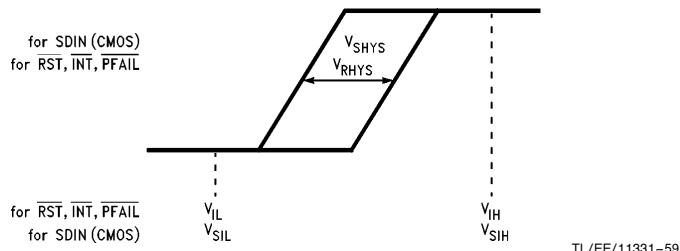

SITSL: Scanner Interrupt Time Slot. 8-bit register.