D3501, APRIL 1990

- Independent Asychronous Inputs and Outputs

- Bidirectional

- 32 Words by 9 Bit. Each

- Programmable Depth

- Data Rates from 0 to 40 MHz

- Fall-Through Time . . . 22 ns Typ

- 3-State Outputs

#### description

This 576-bit memory uses Advanced Low-Power Schottky IMPACT-X™ technology and features high speed and fast fall-through times. It consists of two FIFOs organized as 32 words by 9 bits each.

A FIFO memory is a storage device that allows data to be written into and read from its array at independent data rates. These FIFOs are designed to process data at rates from 0 to 40 MHz in a bit-parallel format, word by word.

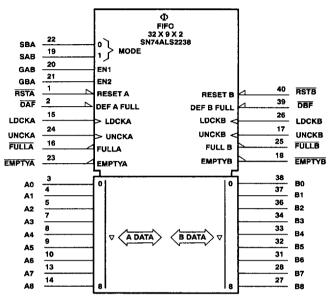

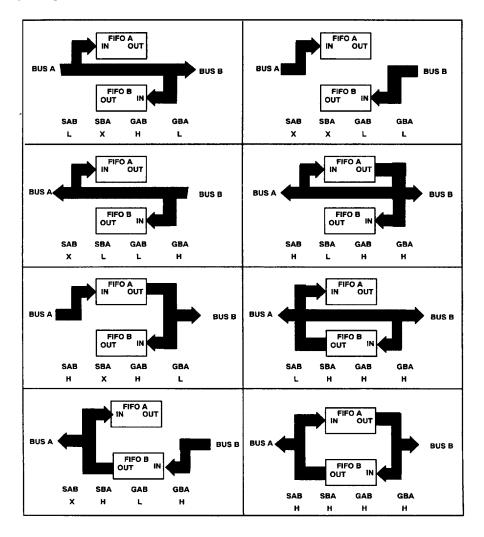

The 'ALS2238 consists of bus transceiver circuits, two 32 X 9 FIFOs, and control circuitry arranged for multiplexed transmission of data directly from the data bus or from the internal FIFO memories. Enable GAB and GBA are provided to control the transceiver functions. The SAB and SBA control pins are provided to select whether real-time or stored data is transferred. The circuitry used for select control will eliminate the typical decoding glitch that occurs in a multiplexer during the transition between stored and real-time data. A low level selects real-time data and a high selects stored data. Eight fundamental bus-management functions can be performed as shown on the Operating Modes page.

Data on the A or B data bus, or both, is written into the FIFOs on a low-to-high transition at the load clock input (LDCKA or LDCKB) and is read out on a low-to-high transition at the unload clock input (UNCKA or UNCKB). The memory is full when the number of words clocked in exceeds, by the defined depth, the number of words clocked out.

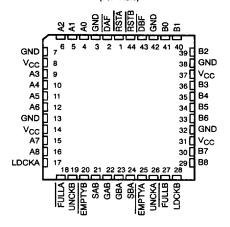

# FN PACKAGE

IMPACT-X is a trademark of Texas Instruments Incorporated.

PRODUCTION DATA documents contain information current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty Production processing does not necessarily include testing of all perameters.

Copyright © 1990, Texas Instruments Incorporated

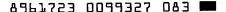

# SN74ALS2238 32 x 9 x 2 ASYNCHRONOUS BIDIRECTIONAL FIRST-IN FIRST-OUT MEMORY

When the memory is full, LDCK signals have no effect on the data residing in memory. When the memory is empty, UNCK signals have no effect.

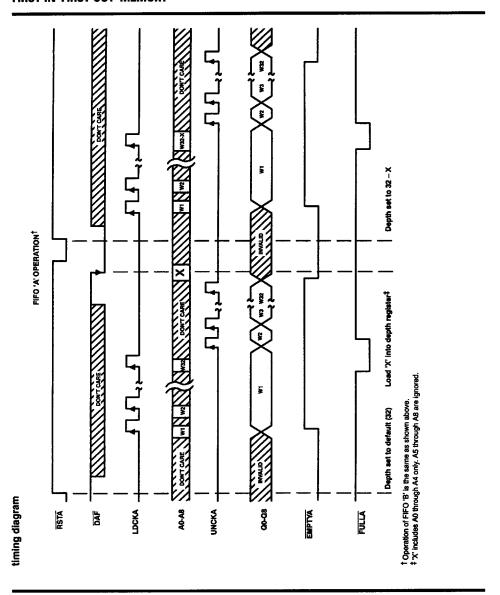

Status of the FIFO memories is monitored by the FULLA, FULLB, EMPTYA, and EMPTYB output flags. The FULLA and FULLB are definable full flags. A high-to-low transition on DAF stores the binary value of A0 through A4 into a register for use as the value of X. A high-to-low transition on DBF stores the binary value of B0 through B4 into a register for use as the value of Y. In this way, the depth of either FIFO can be defined to be one to thirty-two words deep. The value of X and Y must be defined after power-up or the stored value of X and Y will be ambiguous. The FULLA and FULLB outputs will be low when their corresponding memories are full and high when the memories are not full.

The EMPTYA and EMPTYB outputs will be low when their corresponding memories are empty and high when they are not empty. The status flag outputs are always active.

A low-level pulse on the RSTA or RSTB inputs resets the control pointers on FIFO A or FIFO B and also sets EMPTYA low and FULLA high, or EMPTYB low and FULLB high. The outputs are not reset to any specific logic levels. With DAF at a low level, a low-level pulse on RSTA sets FIFO A to a depth of 32 minus X, where X is the value stored above. With DAF at a high level, a low level pulse on RSTA sets FIFO A to a depth of 32 words. The depth of FIFO B is set in a similar manner. The first low-to-high transition on LDCKA or LDCKB, either after a reset pulse or from an empty condition, will cause EMPTYA or EMPTYB to go high and the data to appear on the Q outputs. It is important to note that the first word does not have to be unloaded. Cascading is easily accomplished in the word-width direction, but is not possible in the word-depth direction.

2-670

8961723 0099328T1T 📟

### logic symbol<sup>†</sup>

<sup>†</sup> This symbol is in accordance with ANSI/IEEE Std 91-1984. Pin numbers shown are for the N package.

# SN74ALS2238 32 x 9 x 2 ASYNCHRONOUS BIDIRECTIONAL FIRST-IN FIRST-OUT MEMORY

2-672

**--** 8961723 0099330 678 **--**

### operating modes

2-674

■ 8961723 0099332 440 **■**

#### **FUNCTION TABLES**

#### SELECT MODE CONTROL TABLE

| CONTROL |     | OPERATION                       |                      |  |

|---------|-----|---------------------------------|----------------------|--|

| SBA     | SAB | SAB A Bus B Bus                 |                      |  |

| L       | L   | Real Time B to A Bus            | Real Time A to B Bus |  |

| н       | L.  | FIFO B to A Bus                 | Real Time A to B Bus |  |

| L       | н   | Real Time B to A Bus            | FIFO A to B Bus      |  |

| Н       | н   | FIFO B to A Bus FIFO A to B Bus |                      |  |

#### **OUTPUT ENABLE CONTROL TABLE**

| CONTROL |   | OPERATION                                       |                          |  |

|---------|---|-------------------------------------------------|--------------------------|--|

| GBA GAB |   | A Bus                                           | 8 Bus                    |  |

| н       | I | A Bus Enabled                                   | B Bus Enabled            |  |

| н       | L | A Bus Enabled                                   | Isolation/Input to B Bus |  |

| L       | н | Isolation/Input to A Bus                        | B Bus Enabled            |  |

| L       | L | Isolation/Input to A Bus   Isolation/Input to B |                          |  |

### programming procedure for depth of FIFO A<sup>†</sup>

#### PROGRAM:

- Step 1. With RSTA at a high level, take DAF from a high level to a low level. The high-to-low transition on DAF stores the binary value of A0-A4 for use as the value of 'X' in defining the depth of FIFO A.

- Step 2. With DAF held low, pulse the RSTA signal low. On the low-to-high transition of RSTA, FIFO A is set to a depth of 32 minus 'X', where X is the value of A0-A4 stored above.

- Step 3. To redefine the depth of FIFO A to 32 words, hold DAF at a high level and pulse the RSTA signal low.

## absolute maximum ratings over operating free-air temperature range (unless otherwise noted)‡

| Supply voltage, V <sub>CC</sub>             | 0.5 V to 7 V |

|---------------------------------------------|--------------|

| Input voltage: Control inputs               |              |

| I/O ports                                   | 5.5 V        |

| Voltage applied to a diabled 3-state output | 5.5 V        |

| Operating free-air temperature range        | 0°C to 70°C  |

| Storage temperature range                   |              |

| Maximum junction temperature                | 150°C        |

<sup>\$</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device retiability.

2-675

■ 8961723 DD99333 387 **■**

<sup>&</sup>lt;sup>†</sup> The programming procedures used to define the depth of FIFO B are the same as the procedure above.

# SN74ALS2238 32 x 9 x 2 ASYNCHRONOUS BIDIRECTIONAL FIRST-IN FIRST-OUT MEMORY

### recommended operating conditions (see Note 1)

|        | · · · · · · · · · · · · · · · · · · · |                                                         | MIN  | NOM | MAX   | UNIT |

|--------|---------------------------------------|---------------------------------------------------------|------|-----|-------|------|

| VCC    | Supply voltage                        |                                                         | 4.5  | 5   | 5.5   | ٧    |

| VIH    | High-level input voltage              |                                                         | 2    |     |       | >    |

| VIL    | Low-level input voltage               |                                                         |      |     | 0.8   | >    |

|        |                                       | A or B Ports                                            |      |     | - 15  | mA   |

| ЮН     | High-level output current             | Status flags                                            |      |     | - 0.4 |      |

|        |                                       | A or B Ports                                            |      |     | 24    | mA   |

| IOL    | Low-level output current              | Status flags                                            |      |     | 8     | 1105 |

|        |                                       | LDCKA or LDCKB                                          | 0    |     | 40    | MHz  |

| fclock | Clock frequency                       | UNCKA or UNCKB                                          | 0    |     | 40    | MITZ |

|        | Pulse duration                        | RSTA or RSTB low                                        | 17   |     |       | ns   |

|        |                                       | LDCKA or LDCKB low                                      | 12.5 |     |       |      |

| _      |                                       | LDCKA or LDCKB high                                     | 10   |     |       |      |

| tw     |                                       | UNCKA or UNCKB low                                      | 12.5 |     |       |      |

|        |                                       | UNCKA or UNCKB high                                     | 10   |     |       |      |

|        |                                       | DAF or DBF high                                         | 10   |     |       |      |

|        |                                       | Data before LDCKA or LDCKB†                             | 7    |     |       |      |

|        | Setup time                            | Define Depth: D4-D0 before DAF or DBF‡                  | 6    |     |       |      |

| tsu    |                                       | Define Depth: DAF or DBF   before RSTA or RSTB†         | 45   |     |       | กร   |

|        |                                       | Define Depth (32): DAF or DBF high before RSTA or RSTB† | 32   |     |       |      |

|        |                                       | LDCKA or LDCKB (inactive) before RSTA or RSTB†          | 5    |     |       |      |

| th     | Hold time                             | Data after LDCKA or LDCKB†                              | 3    |     |       |      |

|        |                                       | Define Depth: D4-D0 after DAF or DBF.                   | 4    |     |       |      |

|        |                                       | Define Depth: DAF or DBF low after RSTA or RSTB†        | 0    |     |       | ns   |

|        |                                       | Define Depth (32): DAF or DBF high after RSTA or RSTB†  | 0    |     |       |      |

|        |                                       | LDCKA or LDCKB (inactive) after RSTA or RSTB†           | 5    |     |       | L    |

| TΔ     | Operating free-air temperat           | ture                                                    | 0    |     | 70    | °C   |

NOTE 1: To ensure proper operation of this high-speed FIFO device, it is necessary to provide a clean signal to the LDCKA or LDCKB and UNCKA or UNCKB clock inputs. Any excessive noise or glitching on the clock inputs (which violates the V<sub>1</sub>L, V<sub>I</sub>H, or minimum pulse duration limits) can cause a false clock or improper operation of the internal read and write pointers.

2-676

8961723 0099334 213 📟

### **SN74ALS2238** 32 x 9 x 2 ASYNCHRONOUS BIDIRECTIONAL FIRST-IN FIRST-OUT MEMORY

#### electrical characteristics over recommended operating free-air temperature range (unless otherwise noted)

| PARAMETER      |                                                                         | TEST CONDITIONS                                   |                          | MIN                    | TYP  | MAX   | UNIT  |    |

|----------------|-------------------------------------------------------------------------|---------------------------------------------------|--------------------------|------------------------|------|-------|-------|----|

| VIK            |                                                                         | V <sub>CC</sub> = 4.5 V, I <sub>I</sub> = - 18 mA |                          | T                      |      | - 1.2 | V     |    |

| Voн            | Status flags                                                            | V <sub>CC</sub> = 4.5 V to 5.5 V,                 | IOH = - 0.4 mA           | VCC-2                  |      |       |       |    |

|                |                                                                         | V <sub>CC</sub> = 4.5 V <sub>i</sub>              | IOH = - 2 mA             | VCC-2                  |      |       | v     |    |

|                | A or B ports                                                            | VCC = 4.5 V,                                      | IOH = - 3 mA             | 2.4                    | 3.2  |       | •     |    |

|                |                                                                         | V <sub>CC</sub> = 4.5 V <sub>1</sub>              | IOH = - 15 mA            | 2                      |      |       |       |    |

|                | A or B ports                                                            | V <sub>CC</sub> = 4.5 V,                          | I <sub>OL</sub> = 12 mA  |                        | 0.25 | 0.4   | v     |    |

| V              |                                                                         | V <sub>CC</sub> = 4.5 V,                          | IOL = 24 mA              |                        | 0.35 | 0.5   |       |    |

| VOL            | 0                                                                       | V <sub>CC</sub> = 4.5 V,                          | IOL = 4 mA               |                        | 0.25 | 0.4   |       |    |

|                | Status flags                                                            | V <sub>CC</sub> = 4.5 V,                          | IOL = 8 mA               |                        | 0.35 | 0.5   |       |    |

| l <sub>l</sub> | DAF, DBF, RSTA, RSTB, GAB, GBA, SAB,<br>SBA, LDCKA, LDCKB, UNCKA, UNCKB | V <sub>CC</sub> = 5.5 V,                          | V <sub>I</sub> = 7 V     |                        | -    | 0.1   | mA    |    |

|                | A or B ports                                                            | 1                                                 |                          |                        |      | 0.2   |       |    |

| liH            | DAF, DBF, RSTA, RSTB, GAB, GBA, SAB,<br>SBA, LDCKA, LDCKB, UNCKA, UNCKB | V <sub>CC</sub> = 5.5 V,                          | V <sub>j</sub> = 2.7 V   |                        |      | 20    | μΑ    |    |

|                | A or B ports‡                                                           | 1                                                 |                          |                        |      | 40    | ĺ     |    |

| lur.           | DAF, DBF, RSTA, RSTB, GAB, GBA, SAB,<br>SBA, LCKA, LDCKB, UNCKA, UNCKB  | V <sub>CC</sub> = 5.5 V,                          | V <sub>CC</sub> = 5.5 V, | V <sub>I</sub> = 0.4 V |      | ·     | - 0.2 | mA |

|                | A or B ports‡                                                           |                                                   |                          |                        |      | - 0.4 |       |    |

| 1.8            | A or B ports‡                                                           | V 55V                                             | \/- 0.0E\/               | - 20                   |      | - 130 |       |    |

| IO§            | Status flags                                                            | V <sub>CC</sub> = 5.5 V,                          | V <sub>O</sub> = 2.25 V  | - 15                   |      | - 100 | mA    |    |

| Icc            |                                                                         | V <sub>CC</sub> = 5.5 V                           |                          | 1                      | 190  | 350   | mA    |    |

$<sup>^{\</sup>dagger}$  All typical values are at V<sub>CC</sub> = 5 V, T<sub>A</sub> = 25°C.  $^{\dagger}$  For I/O ports, the parameters I<sub>IH</sub> and I<sub>IL</sub> include the offstate output current.

The output conditions have been chosen to produce a current that closely approximates one half of the true short-circuit output courrent, IOS.

# SN74ALS2238 32 x 9 x 2 ASYNCHRONOUS BIDIRECTIONAL FIRST-IN FIRST-OUT MEMORY

### switching characteristics (see Note 2)

| PARAMETER        | FROM<br>(INPUT) | 1              |     |      | UNIT |     |

|------------------|-----------------|----------------|-----|------|------|-----|

|                  |                 |                | MIN | TYP† | MAX  | ĺ   |

| fmax             | LDCK            |                | 40  |      |      | MHz |

| max              | UNCK            |                | 40  |      |      |     |

| <sup>t</sup> pd  | LDCKA†, LDCKB†  | B/A            | 7   | 22   | 33   | ns  |

| <sup>t</sup> pd  | UNCKA†, UNCKB†  | B/A            | 7   | 20   | 29   | ns  |

| t <sub>PLH</sub> | LDCKA†, LDCKB†  | EMPTYA, EMPTYB | 5   | 12   | 22   | ns  |

| <sup>t</sup> PHL | UNCKA†, UNCKB†  | EMPTYA, EMPTYB | 5   | 12   | 22   | ns  |

| <sup>t</sup> PHL | ASTAĻ, ASTBĻ    | EMPTYA, EMPTYB | 5   | 12   | 22   | ns  |

| <sup>t</sup> PHL | LDCKA†, LDCKB†  | FULLA, FULLB   | 5   | 12   | 22   | ns  |

| †PLH             | UNCKA†, UNCKB†  | FULLA, FULLB   | 5   | 12   | 23   | ns  |

| t <sub>LH</sub>  | RSTAĻ, RSTBĻ    | FULLA, FULLB   | 6   | 15   | 28   | ns  |

| <sup>1</sup> pd  | SAB/SBA‡        | B/A            | 2   | 11   | 18   | ns  |

| <sup>†</sup> pd  | A/B             | B/A            | 2   | 8    | 15   | ns  |

| t <sub>en</sub>  | GBA/GAB         | A/B            | 2   | 6    | 15   | ns  |

| t <sub>dis</sub> | GBA/GAB         | A/B            | 1   | 5    | 12   | กร  |

<sup>†</sup> All typical values are at V<sub>CC</sub> = 5 V, T<sub>A</sub> = 25°C.

<sup>&</sup>lt;sup>‡</sup> These parameters are measured with the internal output state of the storage register opposite to that of the bus input. NOTE 2: Load circuit and voltage waveforms are shown in Section 1.