**ISO518**

For most current data sheet and other product information, visit [www.burr-brown.com](http://www.burr-brown.com)

## Bidirectional ISOLATED DIGITAL COUPLERS

### FEATURES

- **LOW POWER CONSUMPTION:**

< 12mW per Channel

- **1500Vrms ISOLATION:**

100% Tested by Partial Discharge

- **DOUBLE BUFFERED DESIGN FOR EASY INTEGRATION INTO BUS-BASED SYSTEMS**

- **TRI-STATE OUTPUTS**

- **24-PIN PDIP OR GULL WING PACKAGES**

- **2MWORDS/S TRANSFER RATE**

### APPLICATIONS

- **PARALLEL ADCs/DACs**

- **DIGITAL INTERFACES**

- **DIGITAL TRANSMISSION**

- **GROUND-LOOP ISOLATION**

### DESCRIPTION

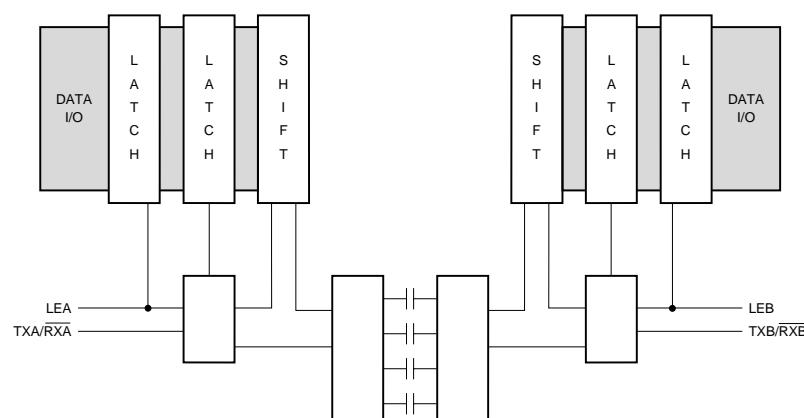

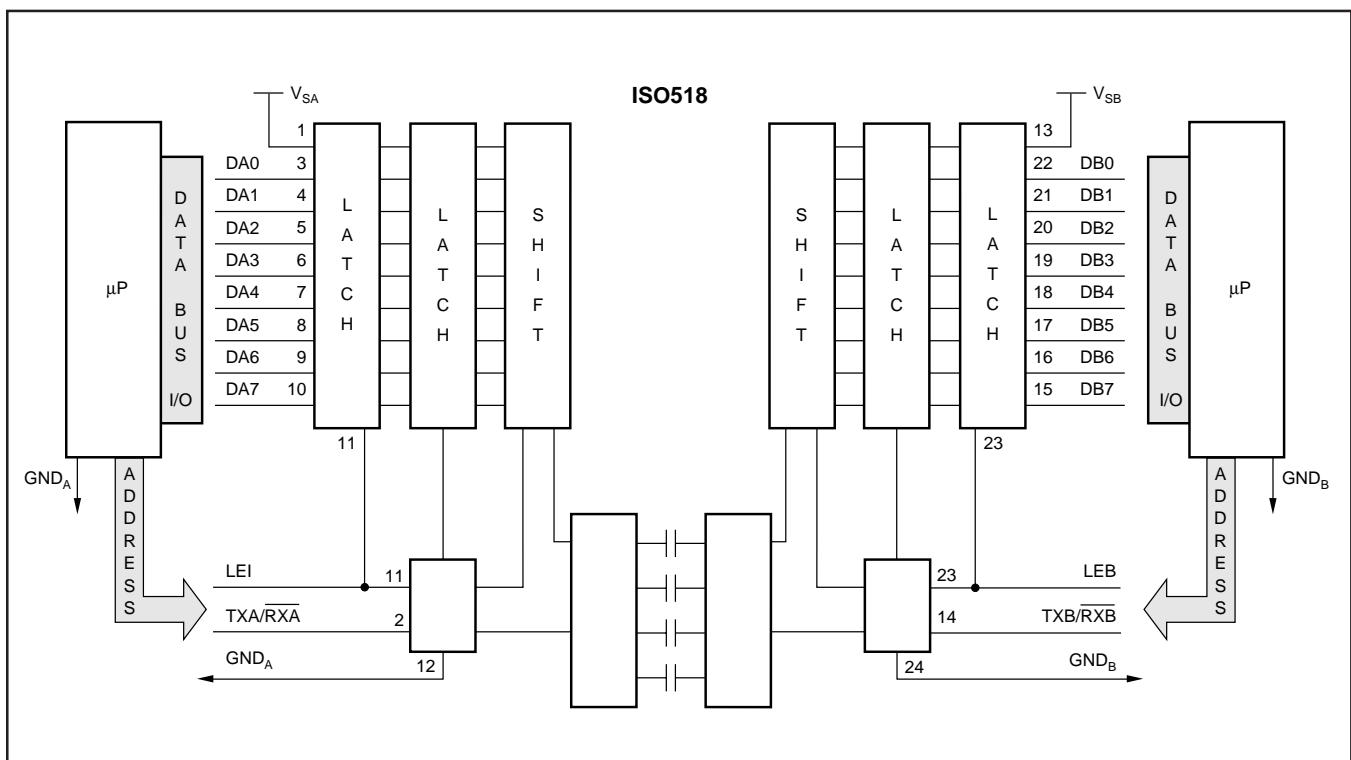

The ISO518 is an 8-channel, isolated, bidirectional digital coupler based on the Burr-Brown capacitive barrier technology.

The ISO518 is designed with input and output buffers for ease of integration into a  $\mu$ P bus system. All data pins are I/O under the control of the TX pins. Input and output buffers are controlled by the latch enable pins. This feature of the ISO518, which allows multiple access to a data bus, requires extra circuitry when using an alternative solution.

The ISO518 will transfer an 8-bit word at rates up to 2Mwords/s without the skew problems associated in implementing this function with optocouplers. The ISO518 is available in 24-pin PDIP or 24-pin Gull Wing packages. Both are specified for operation from  $-40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$ .

ISO518 Functional Block Diagram

International Airport Industrial Park • Mailing Address: PO Box 11400, Tucson, AZ 85734 • Street Address: 6730 S. Tucson Blvd., Tucson, AZ 85706 • Tel: (520) 746-1111

Twx: 910-952-1111 • Internet: <http://www.burr-brown.com/> • Cable: BBRCORP • Telex: 066-6491 • FAX: (520) 889-1510 • Immediate Product Info: (800) 548-6132

# SPECIFICATIONS

At  $T_A = +25^\circ\text{C}$ , and  $V_S = +5\text{V}$ , unless otherwise noted.

| PARAMETER                         | CONDITIONS       | ISO518P, P-U                                   |              |                              | UNITS              |

|-----------------------------------|------------------|------------------------------------------------|--------------|------------------------------|--------------------|

|                                   |                  | MIN                                            | TYP          | MAX                          |                    |

| <b>ISOLATION</b>                  |                  |                                                |              |                              |                    |

| Rated Voltage, Continuous         | $V_{ISO}$        | 50Hz, 60Hz<br>1s, 5 x 5pC/cycle <sup>(1)</sup> | 1500<br>2500 | $>10^{14} \parallel 10$<br>1 | Vrms               |

| Partial Discharge Voltage         |                  |                                                |              |                              | Vrms               |

| Barrier Impedance                 |                  | 240V, 60Hz                                     |              |                              | $\Omega/\text{pF}$ |

| Leakage Current                   |                  | 2500V, 50Hz                                    |              |                              | $\mu\text{A}$      |

| Creepage Distance                 |                  | PDIP = "P" and "U" Package                     |              |                              | mm                 |

| Internal Isolation Distance       |                  | PDIP = "P" and "U" Package                     |              |                              | mm                 |

| Transient Recovery Time           |                  | 5kV/ $\mu\text{s}$ Edge                        |              | 1                            | $\mu\text{s}$      |

| <b>DC CHARACTERISTICS</b>         |                  |                                                |              |                              |                    |

| High Level Input Voltage          | $V_{IH}$         | See Note 2                                     | 2            |                              | V                  |

| Low Level Input Voltage           | $V_{IL}$         | See Note 2                                     |              | 0.8                          | V                  |

| Input Leakage Current             | $I_L$            |                                                | 5            |                              | nA                 |

| Input Capacitance                 | $C_{IN}$         |                                                | 5            |                              | pF                 |

| High Level Output Voltage         | $V_{OH}$         | $I_{OH} = 6\text{mA}$                          | $V_S - 1$    |                              | V                  |

| Low Level Output Voltage          | $V_{OL}$         | $I_{OL} = 6\text{mA}$                          |              | 0.4                          | V                  |

| Output Short-Circuit Current      | $I_{OS}$         | $I_S, \text{max}$                              | 30           |                              | mA                 |

| <b>TIMING</b>                     |                  |                                                |              |                              |                    |

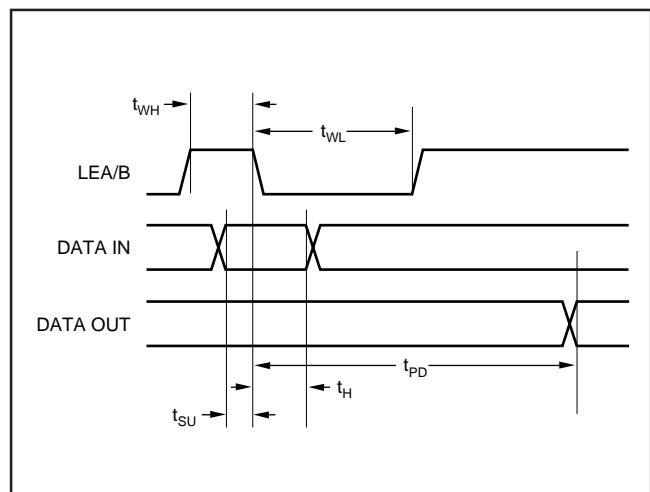

| LE Width (LOW)                    | $t_{WL}$         |                                                | 100          |                              | ns                 |

| LE Width (HIGH)                   | $t_{WH}$         |                                                | 15           |                              | ns                 |

| Data Set-Up to LEA/B              | $t_{SU}$         | LEA/B HIGH to LOW                              | 0            |                              | ns                 |

| Data Hold from LEA/B              | $t_H$            | LEA/B HIGH to LOW                              | 20           |                              | ns                 |

| Propagation Delay                 | $t_{PD}$         | LEA/B LOW to Data Out                          |              | 520                          | ns                 |

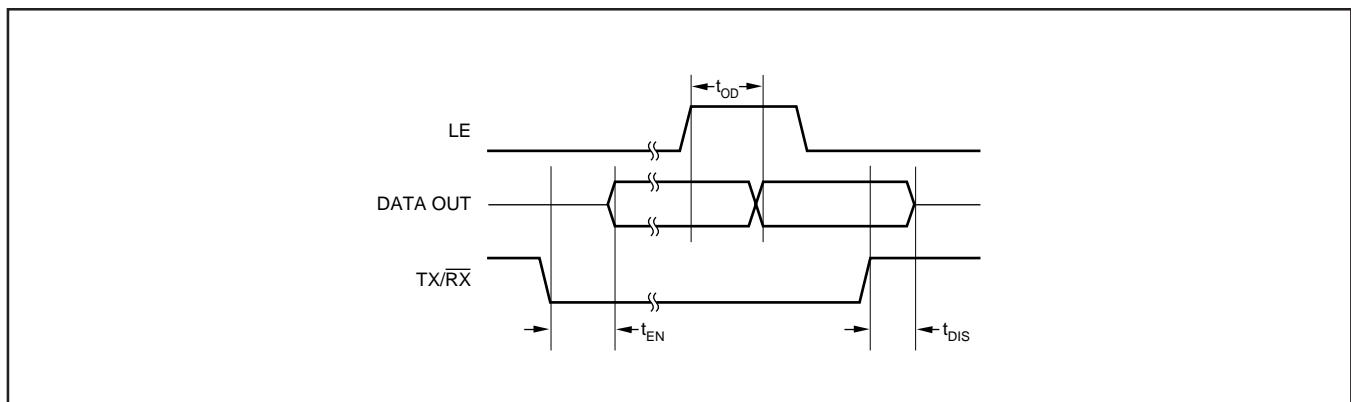

| Data Output Delay                 | $t_{OD}$         | LEO HIGH to Data Out Channels                  |              | 35                           | ns                 |

| Output Rise and Fall Time         | $t_{RF}$         | 10% to 90% Load = 50pF                         | 9            | 14                           | ns                 |

| Output Enable                     | $t_{EN}$         | $\overline{OE}$ to Data Valid HIGH or LOW      |              | 35                           | ns                 |

| Output Disable                    | $t_{DIS}$        | $\overline{OE}$ to Data HI-Z                   |              | 35                           | ns                 |

| Max Data Transfer Rate            |                  |                                                | 2            |                              | Mw/s               |

| Skew                              |                  | Between Any Two Channels                       | 5            |                              | ns                 |

| <b>POWER</b>                      |                  |                                                |              |                              |                    |

| Supply Voltage                    | $V_{SA}, V_{SB}$ | Either Side                                    | 4.5          | 5.5                          | V                  |

| Supply Current                    | $I_{SA/B}$       | Transmit Side DC                               | 5            | 10                           | mA                 |

|                                   |                  | Transmit Side DC Max Rate                      | 7            | 15                           | mA                 |

| Supply Current                    | $I_{SB/A}$       | Receive Side DC                                | 8            | 12                           | mA                 |

|                                   |                  | Receive Side Max Rate                          | 12           | 20                           | mA                 |

| <b>TEMPERATURE RANGE</b>          |                  |                                                |              |                              |                    |

| Operating                         |                  |                                                | -40          |                              | $^\circ\text{C}$   |

| Storage                           |                  |                                                | -40          | +85                          | $^\circ\text{C}$   |

| Thermal Resistance, $\theta_{JA}$ |                  |                                                |              | +125                         | $^\circ\text{C/W}$ |

NOTES: (1) All devices receive a 1s test. Failure criterion is  $> 5\text{pC}$  pulses of  $\geq 5\text{pC}$  per cycle. (2) Logic inputs are HCT-type and thresholds are a function of power supply voltage with approximately 400mV hysteresis.

The information provided herein is believed to be reliable; however, BURR-BROWN assumes no responsibility for inaccuracies or omissions. BURR-BROWN assumes no responsibility for the use of this information, and all use of such information shall be entirely at the user's own risk. Prices and specifications are subject to change without notice. No patent rights or licenses to any of the circuits described herein are implied or granted to any third party. BURR-BROWN does not authorize or warrant any BURR-BROWN product for use in life support devices and/or systems.

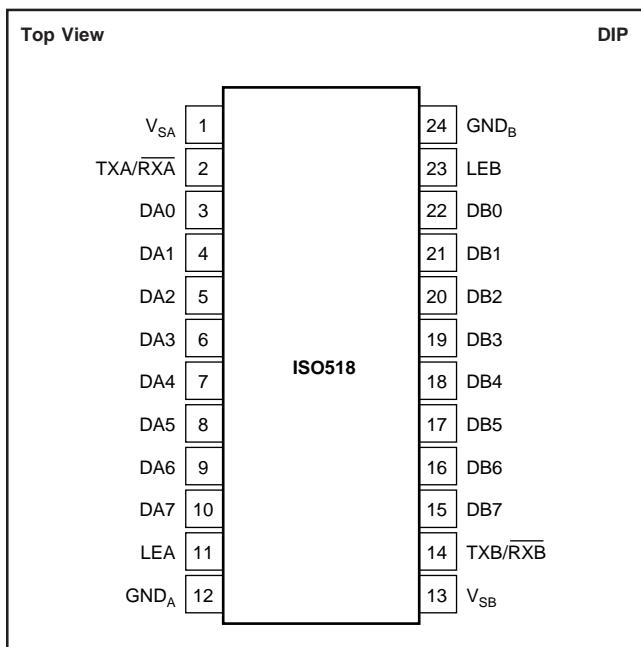

## PIN CONFIGURATION

## FUNCTIONAL DESCRIPTION

| NAME                  | FUNCTION                                                                                                              |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------|

| DA (0 - 7)            | Data Bus A. The logic levels on these pins are transmitted to, or received from the corresponding pins on data bus B. |

| DB (0 - 7)            | Data Bus B. The logic levels on these pins are transmitted to, or received from the corresponding pins on data bus A. |

| LEA <sup>(1)</sup>    | Latch Enable A. Latch enable signal for the A data buffer.                                                            |

| LEB <sup>(1)</sup>    | Latch Enable B. Latch enable signal for the B data buffer.                                                            |

| TX/RXA <sup>(2)</sup> | Transmit/Receive Control for Side A.                                                                                  |

| TX/RXB <sup>(2)</sup> | Transmit/Receive Control for Side B.                                                                                  |

NOTES: (1) In transmit mode (TX/RX = 1), a logic 0 (LOW) will latch the input buffer data into the input register and initialize the transmission. A logic 0 (LOW) will latch the internal buffer data into the output register and prevent any further changes in the output data. A logic 1 (HIGH) will pass the internal buffer data to the output register and permit each new set of data to appear as soon as available after transmission. (2) A logic 1 (HIGH) will set that side to transmit mode and the same side's data bus to input mode. A logic 0 (LOW) will set that side to receive mode and the same side's data bus to output mode.

## ELECTROSTATIC DISCHARGE SENSITIVITY

Electrostatic discharge can cause damage ranging from performance degradation to complete device failure. Burr-Brown Corporation recommends that all integrated circuits be handled and stored using appropriate ESD protection methods.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet published specifications.

## ABSOLUTE MAXIMUM RATINGS

|                                         |                 |

|-----------------------------------------|-----------------|

| Supply Voltage: V <sub>SA</sub> .....   | -0.5V to +6V    |

| V <sub>SB</sub> .....                   | -0.5V to +6V    |

| Maximum Input Current, Any Input .....  | 20mA            |

| Continuous Isolation Voltage .....      | 1500VRMS        |

| Storage Temperature .....               | -40°C to +125°C |

| Lead Temperature (soldering, 10s) ..... | 300°C           |

## PACKAGE INFORMATION

| PRODUCT   | PACKAGE                        | PACKAGE DRAWING NUMBER <sup>(1)</sup> |

|-----------|--------------------------------|---------------------------------------|

| ISO518P   | 24-Pin Plastic DIP             | 167                                   |

| ISO518P-U | 24-Pin Gull Wing Surface Mount | 167-4                                 |

NOTE: (1) For detailed drawing and dimension table, please see end of data sheet, or Appendix C of Burr-Brown IC Data Book.

# OPERATION

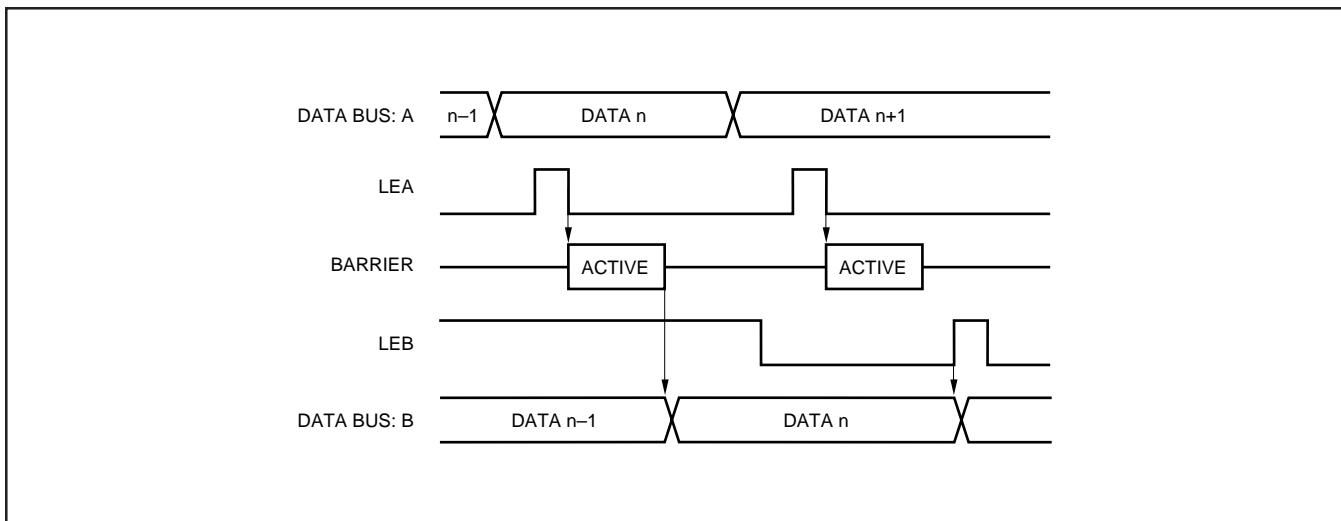

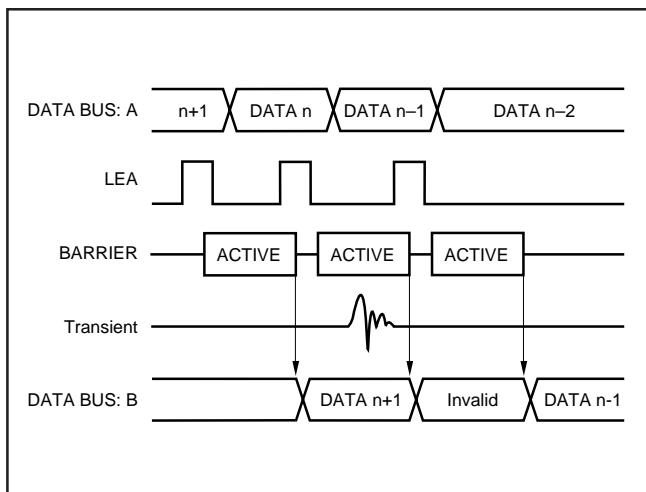

Data is transmitted across the barrier under the control of LEA or LEB; the direction being decided by TXA/RXA and TXB/RXB.

Assume side A is set to transmit and side B is set to receive. With LEA LOW, no data is passed to the input buffer and no barrier transmission takes place. When LEA is HIGH, the input data is passed to the input buffer ready for transmission across the barrier on the falling edge of LEA. On the falling edge of LEA, the data is latched to prevent any subsequent input data changes interfering with the single barrier transmission. Should LEA go HIGH again before the transmission is complete, the data in the input pins will be loaded into

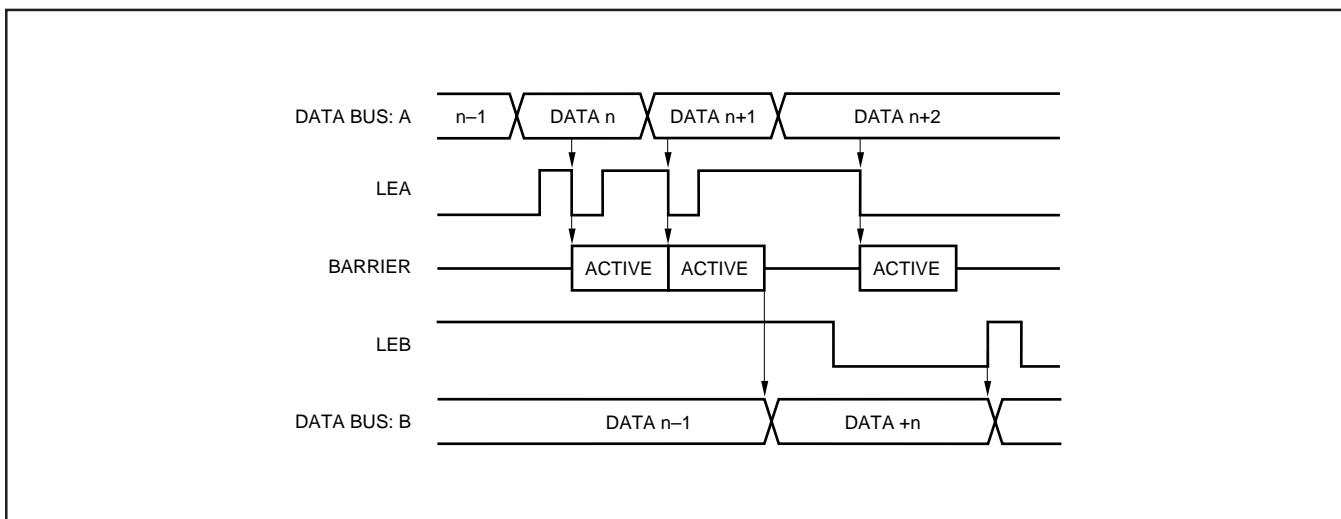

the input buffer without affecting the transmission. However, should LEA go LOW again before the barrier transmission is complete, the barrier transmission will terminate and restart with the new data (see Figure 2). This will not affect the output data which only changes at the end of a transmission or under control of LEB.

If LEB is HIGH, the output data will change at the end of transmission. If LEB is LOW the output data will change when LEB next goes HIGH. In both cases, all data bits will change together, guaranteeing the specified skew performance. It should also be noted that LEB may be used to ignore transmitted data if required.

FIGURE 1. Data Transfer.

FIGURE 2. Data Transfer—Restart.

FIGURE 3. Data Corruption.

FIGURE 4. Transmission Timing Diagram.

FIGURE 5. Output Data Timing.

FIGURE 6. Burr-Brown I/O System using ISO518.

**PACKAGING INFORMATION**

| ORDERABLE DEVICE | STATUS(1) | PACKAGE TYPE | PACKAGE DRAWING | PINS | PACKAGE QTY |

|------------------|-----------|--------------|-----------------|------|-------------|

| ISO518P          | OBsolete  | PDIP         | NTA             | 24   |             |

| ISO518P-U        | OBsolete  | SOP          | DTA             | 24   |             |

(1) The marketing status values are defined as follows:

**ACTIVE:** Product device recommended for new designs.

**LIFEBUY:** TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

**NRND:** Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available.

**OBsolete:** TI has discontinued the production of the device.

## IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| <b>Products</b>  |                        | <b>Applications</b> |                                                                          |

|------------------|------------------------|---------------------|--------------------------------------------------------------------------|

| Amplifiers       | amplifier.ti.com       | Audio               | <a href="http://www.ti.com/audio">www.ti.com/audio</a>                   |

| Data Converters  | dataconverter.ti.com   | Automotive          | <a href="http://www.ti.com/automotive">www.ti.com/automotive</a>         |

| DSP              | dsp.ti.com             | Broadband           | <a href="http://www.ti.com/broadband">www.ti.com/broadband</a>           |

| Interface        | interface.ti.com       | Digital Control     | <a href="http://www.ti.com/digitalcontrol">www.ti.com/digitalcontrol</a> |

| Logic            | logic.ti.com           | Military            | <a href="http://www.ti.com/military">www.ti.com/military</a>             |

| Power Mgmt       | power.ti.com           | Optical Networking  | <a href="http://www.ti.com/opticalnetwork">www.ti.com/opticalnetwork</a> |

| Microcontrollers | microcontroller.ti.com | Security            | <a href="http://www.ti.com/security">www.ti.com/security</a>             |

|                  |                        | Telephony           | <a href="http://www.ti.com/telephony">www.ti.com/telephony</a>           |

|                  |                        | Video & Imaging     | <a href="http://www.ti.com/video">www.ti.com/video</a>                   |

|                  |                        | Wireless            | <a href="http://www.ti.com/wireless">www.ti.com/wireless</a>             |

Mailing Address: Texas Instruments

Post Office Box 655303 Dallas, Texas 75265

Copyright © 2003, Texas Instruments Incorporated