**MAXIM****Quad Bus LVDS Driver with Flow-Through Pinout****General Description**

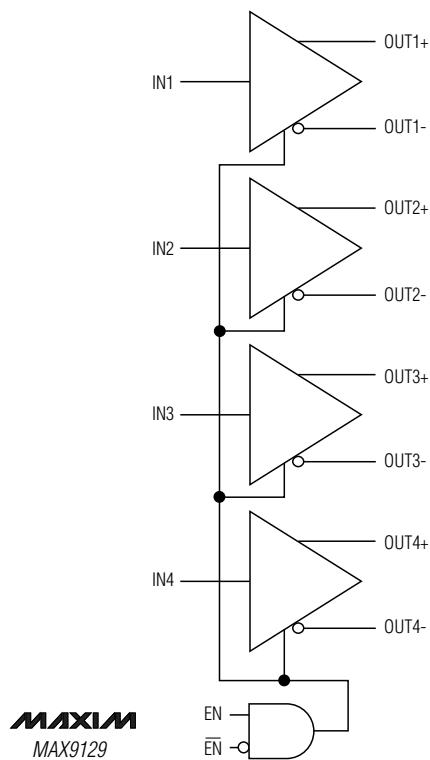

The MAX9129 is a quad bus low-voltage differential signaling (BLVDS) driver with flow-through pinout. This device is designed to drive a heavily loaded multipoint bus with controlled transition times (1ns 0% to 100% minimum) for reduced reflections. The MAX9129 accepts four LVTT/LVCMOS input levels and translates them to output levels of 250mV to 450mV (standard LVDS levels) into a  $27\Omega$  load at speeds up to 200Mbps (100MHz).

The power-on reset ensures that all four outputs are disabled and high impedance during power up and power down. The outputs can be set to high impedance by two enable inputs, EN and  $\bar{EN}$ , thus dropping the device to a low-power state of 11mW. The enables are common to all four drivers. The flow-through pinout simplifies PC board layout and reduces crosstalk by keeping the LVTT/LVCMOS inputs and BLVDS outputs separated.

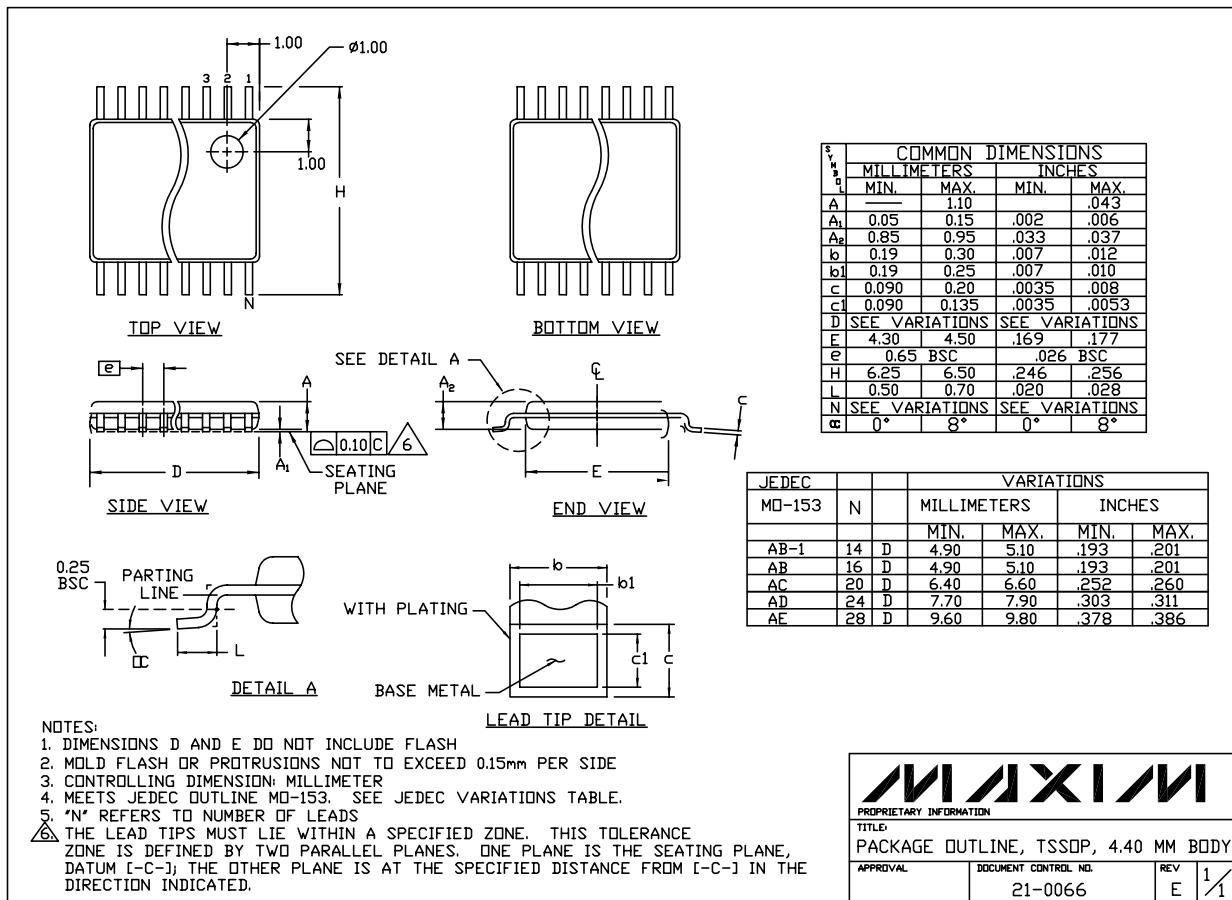

The MAX9129 operates from a single +3.3V supply and is specified for operation from  $-40^{\circ}\text{C}$  to  $+85^{\circ}\text{C}$ . It is available in 16-pin QFN and TSSOP packages. Refer to the MAX9121 data sheet for a quad LVDS line receiver with flow-through pinout.

**Applications**

Cell Phone Base Stations

Add/Drop Muxes

Digital Cross-Connects

DSLAMs

Network Switches/Routers

Backplane Interconnect

Clock Distribution

**Features**

- ◆ Drive LVDS Levels into a  $27\Omega$  Load

- ◆ 1ns (0% to 100%) Minimum Transition Time Reduces Reflections

- ◆ Guaranteed 200Mbps (100MHz) Data Rate

- ◆ Enable Pins for High-Impedance Output

- ◆ High-Impedance Outputs when Powered Off

- ◆ Glitch-Free Power-Up and Power-Down

- ◆ Hot Swappable

- ◆ Flow-Through Pinout

- ◆ Available in Tiny QFN Package (50% Smaller than TSSOP)

- ◆ Single +3.3V Supply

**MAX9129****Ordering Information**

| PART       | TEMP. RANGE                                    | PIN-PACKAGE |

|------------|------------------------------------------------|-------------|

| MAX9129EGE | $-40^{\circ}\text{C}$ to $+85^{\circ}\text{C}$ | 16 QFN      |

| MAX9129EUE | $-40^{\circ}\text{C}$ to $+85^{\circ}\text{C}$ | 16 TSSOP    |

*Functional Diagram appears at end of data sheet.*

*Pin Configurations appear at end of data sheet.*

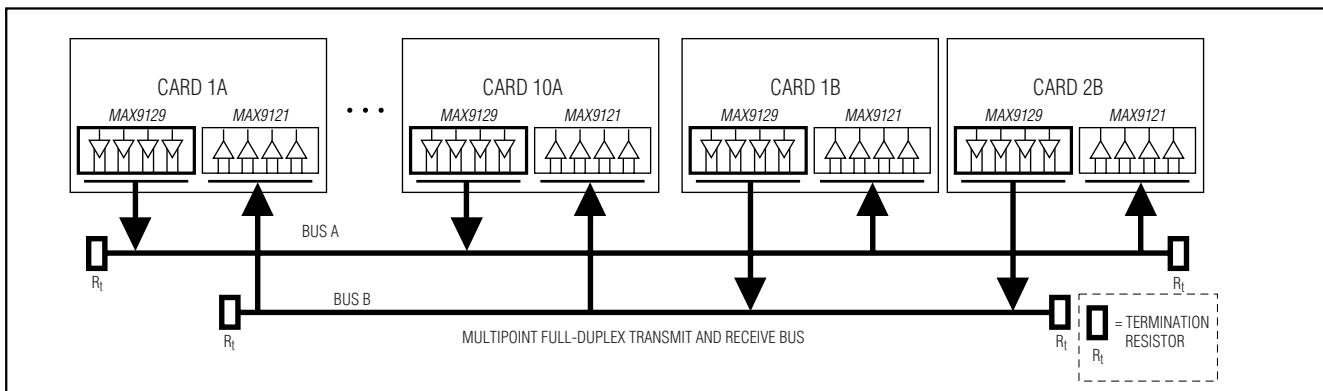

**Typical Applications Circuit****MAXIM**

Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at 1-888-629-4642, or visit Maxim's website at [www.maxim-ic.com](http://www.maxim-ic.com).

# Quad Bus LVDS Driver with Flow-Through Pinout

## ABSOLUTE MAXIMUM RATINGS

|                                                               |                                   |

|---------------------------------------------------------------|-----------------------------------|

| V <sub>CC</sub> to GND                                        | -0.3V to +4.0V                    |

| IN <sub>+</sub> , EN, $\overline{EN}$ to GND                  | -0.3V to (V <sub>CC</sub> + 0.3V) |

| OUT <sub>+</sub> , OUT <sub>-</sub> to GND                    | -0.3V to +4.0V                    |

| Short-Circuit Duration (OUT <sub>+</sub> , OUT <sub>-</sub> ) | Continuous                        |

| Continuous Power Dissipation (T <sub>A</sub> = +70°C)         |                                   |

| 16-Pin QFN (derate 18.5mW/°C above +70°C)                     | 1481mW                            |

| 16-Pin TSSOP (derate 9.4mW/°C above +70°C)                    | 755mW                             |

|                                                       |                 |

|-------------------------------------------------------|-----------------|

| Storage Temperature Range                             | -65°C to +150°C |

| Maximum Junction Temperature                          | +150°C          |

| Operating Temperature Range                           | -40°C to +85°C  |

| ESD Protection                                        |                 |

| Human Body Model, OUT <sub>+</sub> , OUT <sub>-</sub> | ±8kV            |

| Lead Temperature (soldering, 10s)                     | +300°C          |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## DC ELECTRICAL CHARACTERISTICS

(V<sub>CC</sub> = +3.0V to +3.6V, R<sub>L</sub> = 27Ω ±1%, EN = high,  $\overline{EN}$  = low, T<sub>A</sub> = -40°C to +85°C, unless otherwise noted. Typical values are at V<sub>CC</sub> = +3.3V, T<sub>A</sub> = +25°C.) (Notes 1, 2)

| PARAMETER                                                                  | SYMBOL           | CONDITIONS                                                                                                                          | MIN   | TYP             | MAX   | UNITS |

|----------------------------------------------------------------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------|-------|-----------------|-------|-------|

| <b>BLVDS OUTPUTS (OUT<sub>+</sub>, OUT<sub>-</sub>)</b>                    |                  |                                                                                                                                     |       |                 |       |       |

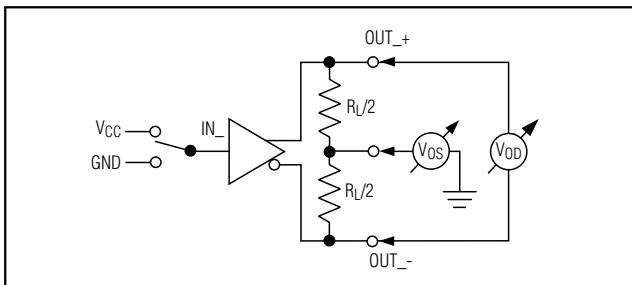

| Differential Output Voltage                                                | V <sub>OD</sub>  | Figure 1                                                                                                                            | 250   | 371             | 450   | mV    |

| Change in Magnitude of V <sub>OD</sub> Between Complementary Output States | ΔV <sub>OD</sub> | Figure 1                                                                                                                            |       | 1               | 25    | mV    |

| Offset Voltage                                                             | V <sub>OS</sub>  | Figure 1                                                                                                                            | 1.125 | 1.29            | 1.375 | V     |

| Change in Magnitude of V <sub>OS</sub> Between Complementary Output States | ΔV <sub>OS</sub> | Figure 1                                                                                                                            |       | 5               | 25    | mV    |

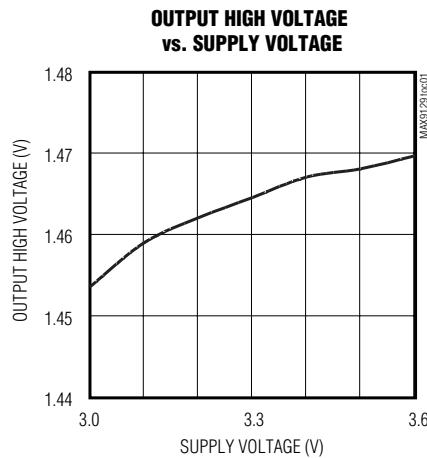

| Output High Voltage                                                        | V <sub>OH</sub>  |                                                                                                                                     |       | 1.465           | 1.6   | V     |

| Output Low Voltage                                                         | V <sub>OL</sub>  |                                                                                                                                     | 0.90  | 1.085           |       | V     |

| Differential Output Short-Circuit Current                                  | I <sub>OSD</sub> | V <sub>OD</sub> = 0                                                                                                                 |       | 20              |       | mA    |

| Output Short-Circuit Current                                               | I <sub>OS</sub>  | OUT <sub>+</sub> = 0 at IN <sub>-</sub> = V <sub>CC</sub> or OUT <sub>-</sub> = 0 at IN <sub>-</sub> = 0                            |       | -20             |       | mA    |

| Output High-Impedance Current                                              | I <sub>OZ</sub>  | Disabled, OUT <sub>+</sub> = 0 or V <sub>CC</sub> , OUT <sub>-</sub> = 0 or V <sub>CC</sub>                                         | -1    | 1               |       | µA    |

| Power-Off Output Current                                                   | I <sub>OFF</sub> | V <sub>CC</sub> = 0 or open, EN = $\overline{EN}$ = IN <sub>-</sub> = 0, OUT <sub>+</sub> = 0 or 3.6V, OUT <sub>-</sub> = 0 or 3.6V | -1    | 1               |       | µA    |

| Output Capacitance                                                         | C <sub>OUT</sub> | Capacitance from OUT <sub>+</sub> or OUT <sub>-</sub> to GND                                                                        |       | 4.3             |       | pF    |

| <b>INPUTS (IN<sub>-</sub>, EN, <math>\overline{EN}</math>)</b>             |                  |                                                                                                                                     |       |                 |       |       |

| High-Level Input Voltage                                                   | V <sub>IH</sub>  |                                                                                                                                     | 2.0   | V <sub>CC</sub> |       | V     |

| Low-Level Input Voltage                                                    | V <sub>IL</sub>  |                                                                                                                                     | GND   | 0.8             |       | V     |

| Input Current                                                              | I <sub>IN</sub>  | IN <sub>-</sub> , EN, $\overline{EN}$ = 0 or V <sub>CC</sub>                                                                        | -15   | 15              |       | µA    |

| <b>SUPPLY CURRENT</b>                                                      |                  |                                                                                                                                     |       |                 |       |       |

| Supply Current                                                             | I <sub>CC</sub>  | R <sub>L</sub> = 27Ω, IN <sub>-</sub> = V <sub>CC</sub> or 0 for all channels                                                       | 58    | 70              |       | mA    |

| Disabled Supply Current                                                    | I <sub>CCZ</sub> | Disabled                                                                                                                            | 3.2   | 5               |       | mA    |

# Quad Bus LVDS Driver with Flow-Through Pinout

## AC ELECTRICAL CHARACTERISTICS

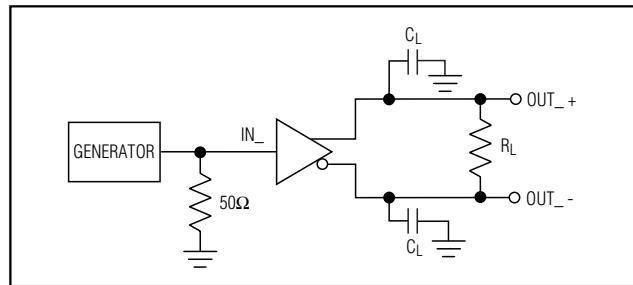

( $V_{CC} = +3.0V$  to  $+3.6V$ ,  $R_L = 27\Omega \pm 1\%$ ,  $C_L = 15pF$ ,  $EN = \text{high}$ ,  $\overline{EN} = \text{low}$ ,  $T_A = -40^\circ\text{C}$  to  $+85^\circ\text{C}$ , unless otherwise noted. Typical values are at  $V_{CC} = +3.3V$ ,  $T_A = +25^\circ\text{C}$ .) (Notes 3, 4, 5)

| PARAMETER                                     | SYMBOL     | CONDITIONS      |            | MIN  | TYP  | MAX  | UNITS |

|-----------------------------------------------|------------|-----------------|------------|------|------|------|-------|

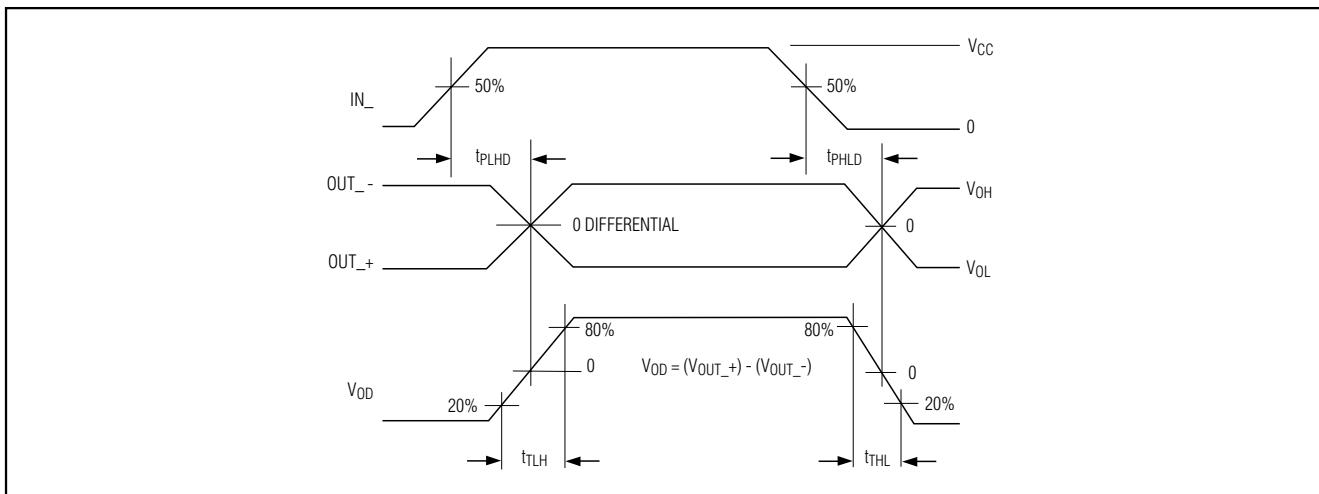

| Differential Propagation Delay High to Low    | $t_{PHLD}$ | Figures 2 and 3 |            | 1.0  | 1.98 | 3.0  | ns    |

| Differential Propagation Delay Low to High    | $t_{PLHD}$ | Figures 2 and 3 |            | 1.0  | 1.92 | 3.0  | ns    |

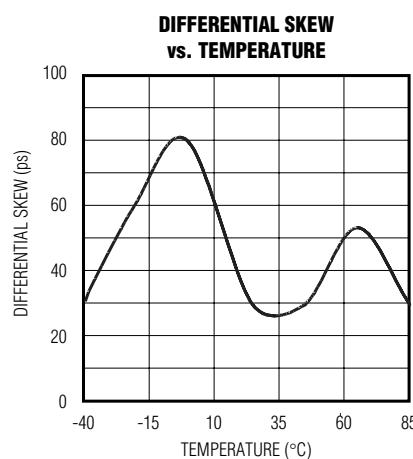

| Differential Pulse Skew (Note 6)              | $t_{SKD1}$ | Figures 2 and 3 |            |      | 300  |      | ps    |

| Differential Channel-to-Channel Skew (Note 7) | $t_{SKD2}$ | Figures 2 and 3 |            |      | 450  |      | ps    |

| Differential Part-to-Part Skew (Note 8)       | $t_{SKD3}$ | Figures 2 and 3 |            |      | 1.2  |      | ns    |

| Differential Part-to-Part Skew (Note 9)       | $t_{SKD4}$ | Figures 2 and 3 |            |      | 2.0  |      | ns    |

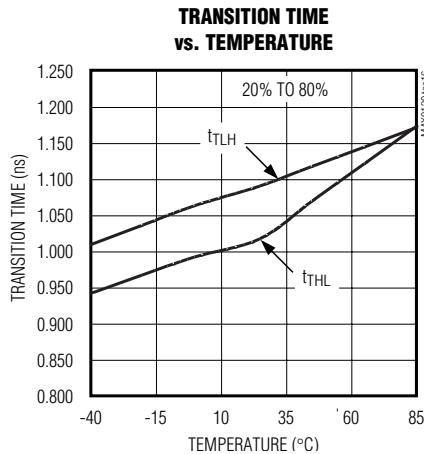

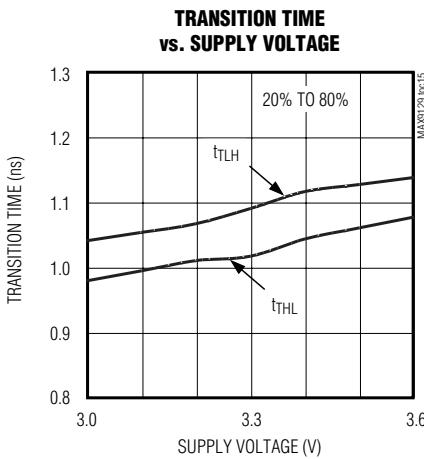

| Rise Time                                     | $t_{TLH}$  | Figures 2 and 3 | MAX9129EGE | 0.60 | 1.19 | 1.55 | ns    |

|                                               |            |                 | MAX9129EUE | 0.60 | 1.09 | 1.40 |       |

| Fall Time                                     | $t_{THL}$  | Figures 2 and 3 | MAX9129EGE | 0.60 | 1.12 | 1.55 | ns    |

|                                               |            |                 | MAX9129EUE | 0.60 | 1.02 | 1.40 |       |

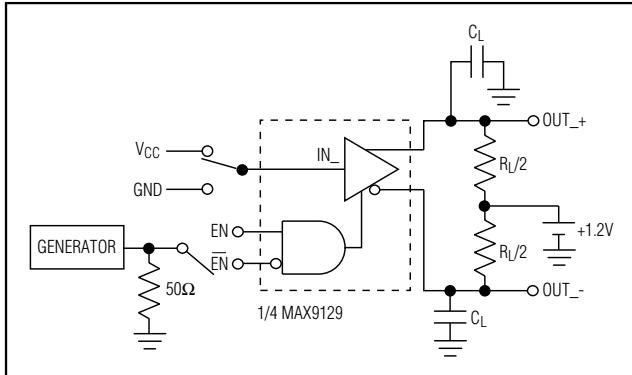

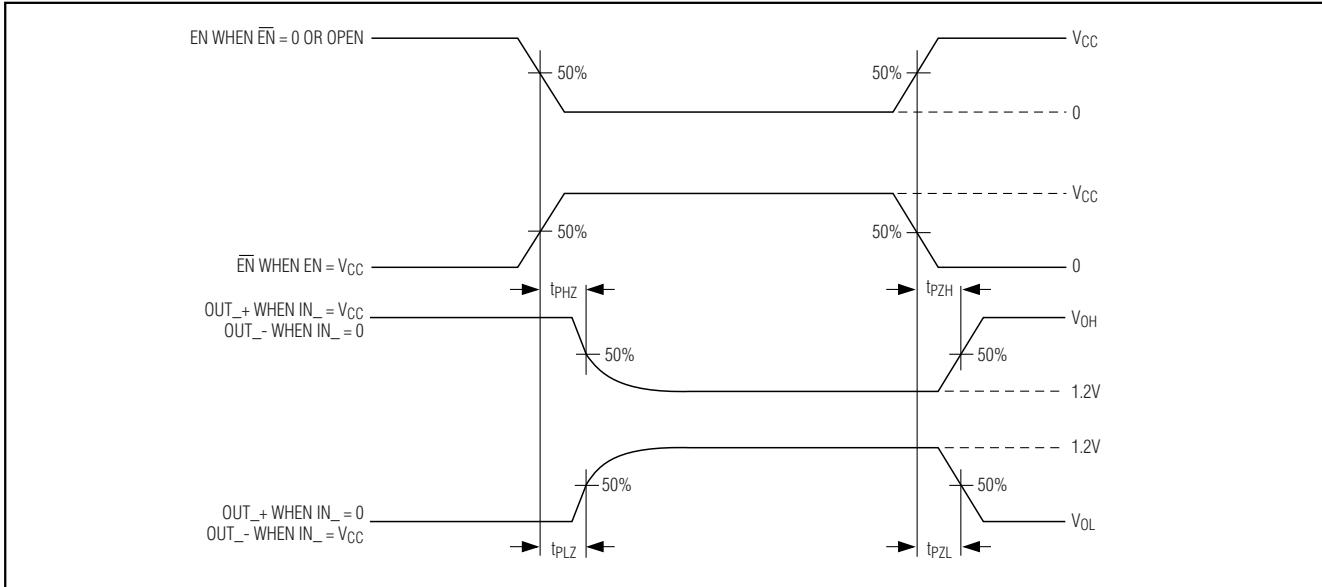

| Disable Time High to Z                        | $t_{PHZ}$  | Figures 4 and 5 |            |      | 8    |      | ns    |

| Disable Time Low to Z                         | $t_{PLZ}$  | Figures 4 and 5 |            |      | 8    |      | ns    |

| Enable Time Z to High                         | $t_{PZH}$  | Figures 4 and 5 |            |      | 10   |      | ns    |

| Enable Time Z to Low                          | $t_{PZL}$  | Figures 4 and 5 |            |      | 10   |      | ns    |

| Maximum Operating Frequency (Note 10)         | $f_{MAX}$  | Figure 2        |            | 100  |      |      | MHz   |

**Note 1:** Maximum and minimum limits over temperature are guaranteed by design and characterization. Devices are 100% tested at  $T_A = +25^\circ\text{C}$ .

**Note 2:** Current into the device is defined as positive, and current out of the device is defined as negative. All voltages are referenced to ground except  $V_{OD}$  and  $\Delta V_{OD}$ .

**Note 3:** AC parameters are guaranteed by design and characterization.

**Note 4:**  $C_L$  includes probe and jig capacitance.

**Note 5:** Signal generator conditions:  $V_{OL} = 0$ ,  $V_{OH} = V_{CC}$ ,  $f = 100\text{MHz}$ , 50% duty cycle,  $R_O = 50\Omega$ ,  $t_R = t_F = 1\text{ns}$  (10% to 90%).

**Note 6:**  $t_{SKD1}$  is the magnitude difference of differential propagation delays.  $t_{SKD1} = |t_{PHLD} - t_{PLHD}|$ .

**Note 7:**  $t_{SKD2}$  is the magnitude difference of  $t_{PHLD}$  or  $t_{PLHD}$  of one channel to the  $t_{PHLD}$  or  $t_{PLHD}$  of another channel on the same device.

**Note 8:**  $t_{SKD3}$  is the magnitude difference of any differential propagation delays between devices at the same  $V_{CC}$  and within  $5^\circ\text{C}$  of each other.

**Note 9:**  $t_{SKD4}$  is the magnitude difference of any differential propagation delays between devices operating over the rated supply and temperature ranges.

**Note 10:** Signal generator conditions:  $V_{OL} = 0$ ,  $V_{OH} = V_{CC}$ ,  $f = 100\text{MHz}$ , 50% duty cycle,  $R_O = 50\Omega$ ,  $t_R = t_F = 1\text{ns}$  (10% to 90%). MAX9129 output criteria: duty cycle = 45% to 55%,  $V_{OD} \geq 250\text{mV}$ , all channels switching.

MAX9129

# Quad Bus LVDS Driver with Flow-Through Pinout

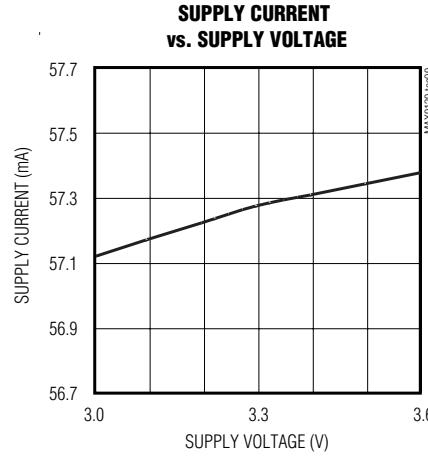

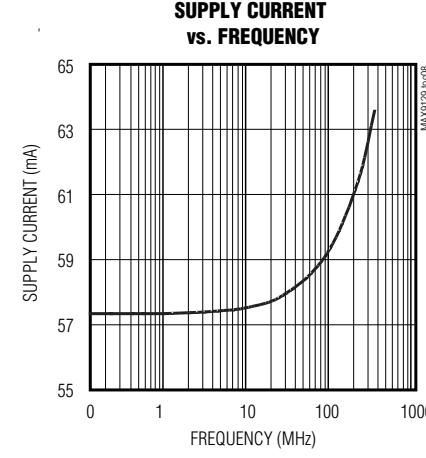

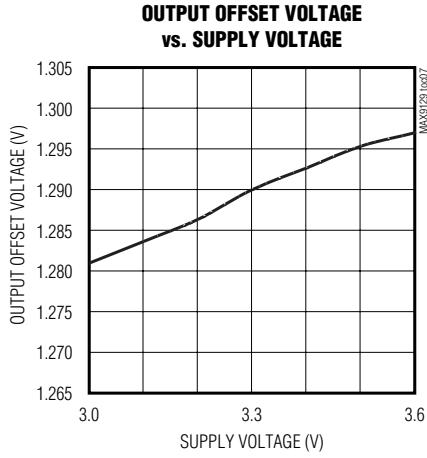

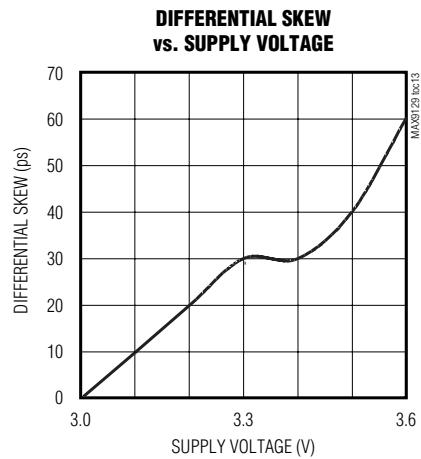

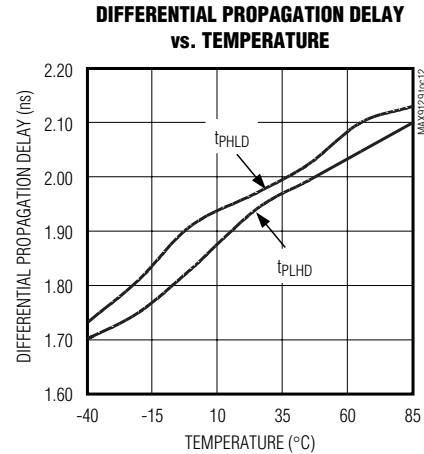

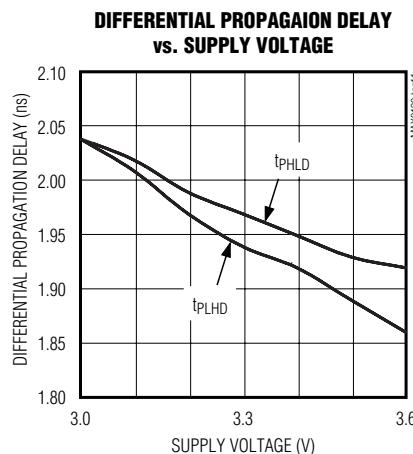

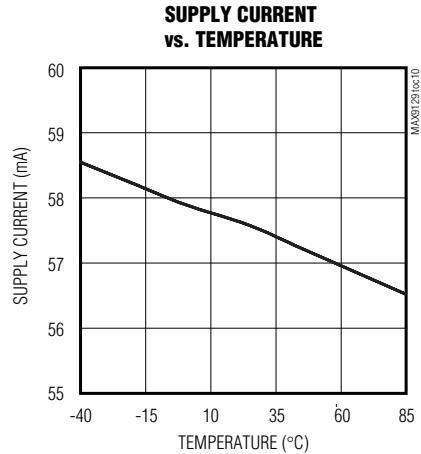

## Typical Operating Characteristics

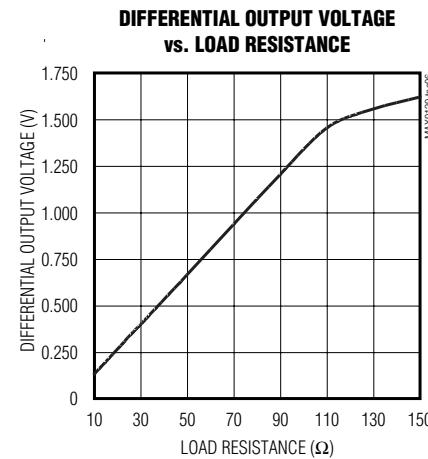

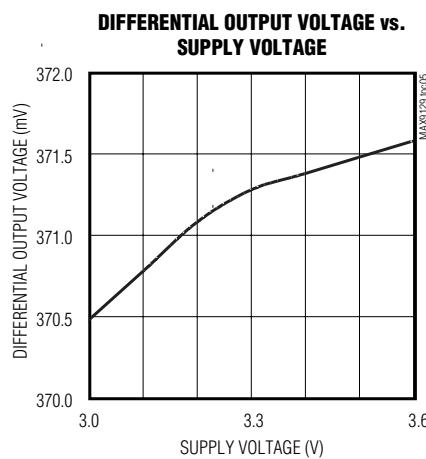

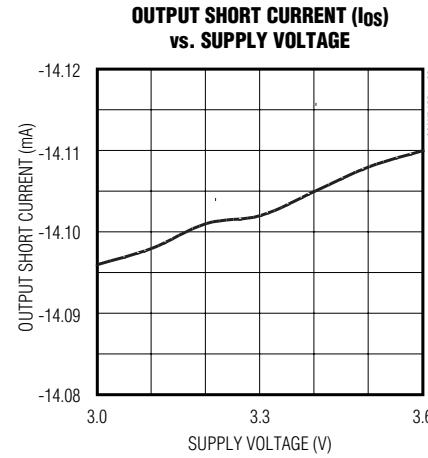

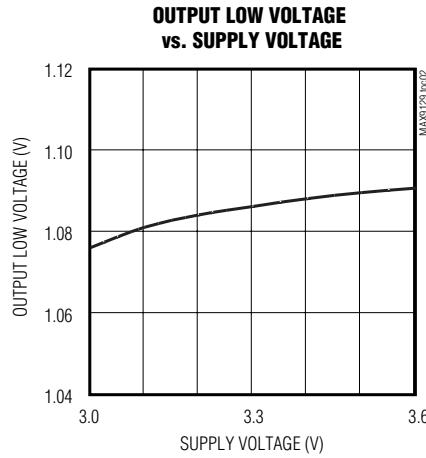

(MAX9129EUE (TSSOP package),  $V_{CC} = +3.3V$ ,  $R_L = 27\Omega$ ,  $C_L = 15pF$ ,  $T_A = +25^\circ C$ , unless otherwise noted.) (Note 5)

# Quad Bus LVDS Driver with Flow-Through Pinout

## Typical Operating Characteristics (continued)

(MAX9129EUE (TSSOP package),  $V_{CC} = +3.3V$ ,  $R_L = 27\Omega$ ,  $C_L = 15pF$ ,  $T_A = +25^\circ C$ , unless otherwise noted.) (Note 5)

MAX9129

# Quad Bus LVDS Driver with Flow-Through Pinout

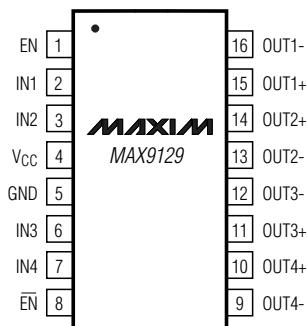

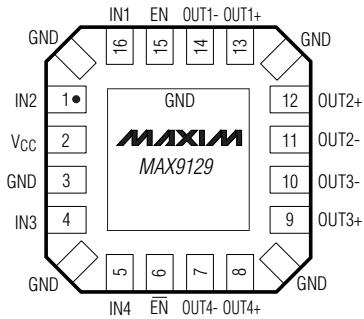

## Pin Description

| PIN           |                | NAME            | FUNCTION                                                                                                                                                                                                                                                                      |

|---------------|----------------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| QFN           | TSSOP          |                 |                                                                                                                                                                                                                                                                               |

| 15            | 1              | EN              | LVTTL/LVCMOS Enable Input. The driver is disabled when EN is low. EN is internally pulled down. When EN = high and $\overline{EN}$ = low or open, the outputs are active. For other combinations of EN and $\overline{EN}$ , the outputs are disabled and are high impedance. |

| 1, 4, 5, 16   | 2, 3, 6, 7     | IN_-            | LVTTL/LVCMOS Driver Inputs                                                                                                                                                                                                                                                    |

| 2             | 4              | VCC             | Power-Supply Input. Bypass VCC to GND with 0.1 $\mu$ F and 0.001 $\mu$ F ceramic capacitors.                                                                                                                                                                                  |

| 3             | 5              | GND             | Ground                                                                                                                                                                                                                                                                        |

| 6             | 8              | $\overline{EN}$ | LVTTL/LVCMOS Enable Input. The driver is disabled when $\overline{EN}$ is high. $\overline{EN}$ is internally pulled down.                                                                                                                                                    |

| 7, 10, 11, 14 | 9, 12, 13, 16  | OUT_-           | Inverting BLVDS Driver Outputs                                                                                                                                                                                                                                                |

| 8, 9, 12, 13  | 10, 11, 14, 15 | OUT_+           | Noninverting BLVDS Driver Outputs                                                                                                                                                                                                                                             |

Figure 1. Driver VOD and VOS Test Circuit

Figure 2. Driver Propagation Delay and Transition Time Test Circuit

Figure 3. Driver Propagation Delay and Transition Time Waveforms

# Quad Bus LVDS Driver with Flow-Through Pinout

MAX9129

Figure 4. Driver High-Impedance Delay Test Circuit

Table 1. Input/Output Function Table

| ENABLES                              |           | INPUTS | OUTPUTS |       |

|--------------------------------------|-----------|--------|---------|-------|

| EN                                   | EN̄       | IN_-   | OUT_+   | OUT_- |

| H                                    | L or open | L      | L       | H     |

|                                      |           | H      | H       | L     |

| All other combinations of EN and EN̄ |           | X      | Z       | Z     |

Figure 5. Driver High-Impedance Delay Waveform

## Detailed Description

The MAX9129 is a 200Mbps quad differential BLVDS driver designed for multipoint, heavily loaded backplane applications. This device accepts LVTT/LVCMOS input levels and translates them to output levels of 250mV to 450mV into a  $27\Omega$  load. The flow-through pinout simplifies board layout and reduces the potential for crosstalk between single-ended inputs and differential outputs. Transition times are designed to reduce reflections, yet enable high data rates. The MAX9129 can be used in conjunction with standard quad LVDS receivers, such

as the MAX9121, to implement full-duplex multipoint buses more efficiently than with transceivers.

## Effect of Capacitive Loading

The characteristic impedance of a differential PC board trace is uniformly reduced when equal capacitive loads are attached at equal intervals (provided the transition time of the signal being driven on the trace is longer than the delay between loads). This kind of loading is typical of multipoint buses where cards are attached at 1in or 0.8in intervals along the length of a backplane.

# Quad Bus LVDS Driver with Flow-Through Pinout

The reduction in characteristic impedance is approximated by the following formula:

$$Z_{\text{DIFF-loaded}} = Z_{\text{DIFF-unloaded}} \times \text{SQRT} [C_0 / (C_0 + N \times C_L / L)]$$

where:

$Z_{\text{DIFF-unloaded}}$  = unloaded differential characteristic impedance

$C_0$  = unloaded trace capacitance (pF/unit length)

$C_L$  = value of each capacitive load (pF)

$N$  = number of capacitive loads

$L$  = trace length

For example, if  $C_0 = 2.5\text{pF/in}$ ,  $C_L = 10\text{pF}$ ,  $N = 18$ ,  $L = 18\text{in}$ , and  $Z_{\text{DIFF-unloaded}} = 120\Omega$ , the loaded differential impedance is:

$$Z_{\text{DIFF-loaded}} = 120\Omega \times \text{SQRT} [2.5\text{pF} / (2.5\text{pF} + 18 \times 10\text{pF}/18\text{in})]$$

$$Z_{\text{DIFF-loaded}} = 54\Omega$$

In this example, capacitive loading reduces the characteristic impedance from  $120\Omega$  to  $54\Omega$ . The load seen by a driver located on a card in the middle of the bus is  $27\Omega$  because the driver sees two  $54\Omega$  loads in parallel. A typical LVDS driver (rated for a  $100\Omega$  load) would not develop a large enough differential signal to be reliably detected by an LVDS receiver. Maxim's BLVDS driver is designed and specified to drive a  $27\Omega$  load to differential voltage levels of  $250\text{mV}$  to  $450\text{mV}$  (which are standard LVDS driver levels). A standard LVDS receiver is able to detect this level of differential signal.

Short extensions off the bus, called stubs, contribute to capacitive loading. Keep stubs less than  $1\text{in}$  for a good balance between ease of component placement and good signal integrity.

The MAX9129 is a current source driver and drives larger differential signal levels into loads higher than  $27\Omega$  and smaller levels into loads less than  $27\Omega$  (see typical operating curves). To keep loading from reducing bus impedance below the rated  $27\Omega$  load, PC board traces can be designed for higher unloaded characteristic impedance.

## Effect of Transition Time

For transition times (measured from 0% to 100%) shorter than the delay between capacitive loads, the loads are seen as low-impedance discontinuities from which the driven signal is reflected. Reflections add and subtract from the signal being driven and cause decreased noise margin and jitter. The MAX9129 is designed for a

minimum transition time of  $1\text{ns}$  (rated  $0.6\text{ns}$  from 20% to 80%, or about  $1\text{ns}$  0% to 100%) to reduce reflections while being fast enough for high-speed backplane data transmission.

## Power-On Reset

The power-on reset voltage of the MAX9129 is typically  $2.25\text{V}$ . When the supply falls below this voltage, the device is disabled and the outputs are in high impedance.

## Applications Information

### Power-Supply Bypassing

Bypass  $V_{\text{CC}}$  with high-frequency, surface-mount ceramic  $0.1\mu\text{F}$  and  $0.001\mu\text{F}$  capacitors in parallel as close to the device as possible, with the smaller valued capacitor closest to  $V_{\text{CC}}$ .

### Termination

In the example above, the loaded differential impedance of the bus is reduced to  $54\Omega$ . Since it can be driven from any card position, the bus must be terminated at each end. A parallel termination of  $54\Omega$  at each end of the bus placed across the traces that make up the differential pair provides a proper termination. The total load seen by the driver is  $27\Omega$ .

The MAX9129 drives higher differential signal levels into lighter loads. A multidrop bus with the driver at one end and receivers connected at regular intervals along the bus has a lowered impedance due to capacitive loading. Assuming the same impedance calculated in the multidrop example above ( $54\Omega$ ), the multidrop bus can be terminated with a single, parallel-connected  $54\Omega$  resistor at the far end from the driver. Only a single resistor is required because the driver sees one  $54\Omega$  differential trace. The signal swing is larger with a  $54\Omega$  load.

In general, parallel terminate each end of the bus with a resistor matching the differential impedance of the bus (taking into account any reduced impedance due to loading).

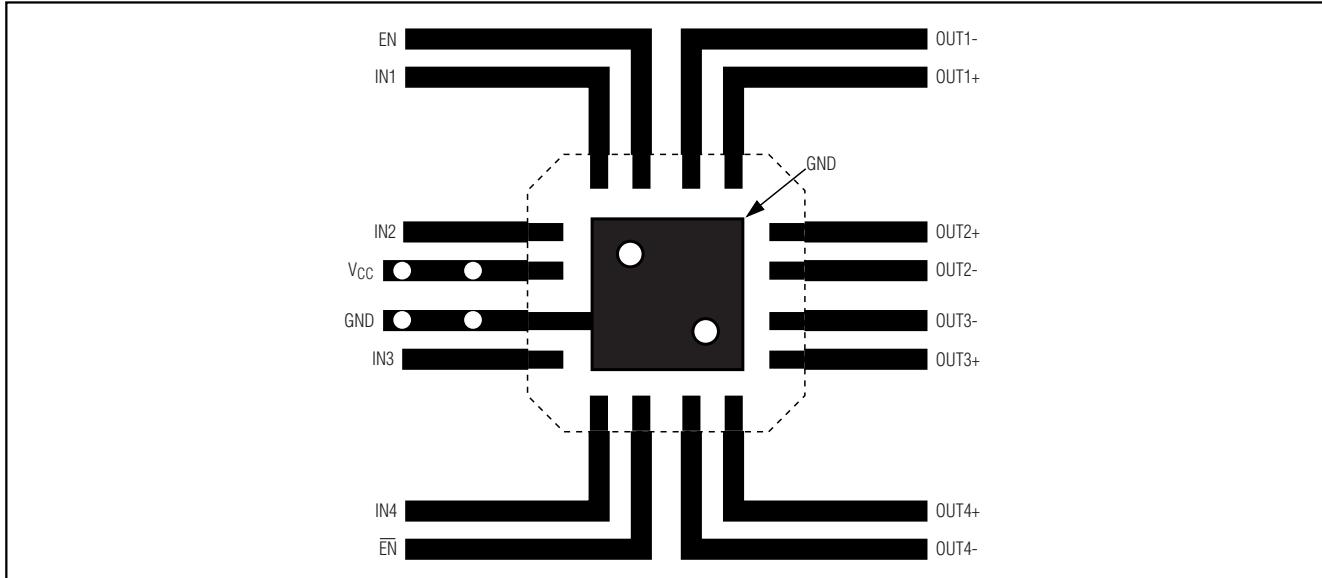

### Board Layout

A four-layer PC board that provides separate power, ground, input, and output signals is recommended. Keep the LVTT/LVCMOS and BLVDS signals separated to prevent coupling as shown in the suggested layout for the QFN package (not drawn to scale) (Figure 6).

# **Quad Bus LVDS Driver with Flow-Through Pinout**

**MAX9129**

Figure 6. Suggested Layout for QFN Package

## **Chip Information**

TRANSISTOR COUNT: 948

PROCESS: CMOS

# Quad Bus LVDS Driver with Flow-Through Pinout

## Pin Configurations

TOP VIEW

TSSOP

QFN

(4mm x 4mm)

(CONTACTS UNDER QFN)

## Functional Diagram

# Quad Bus LVDS Driver with Flow-Through Pinout

## Package Information

MAX9129

TSSOP, NO PADS, ERS

# Quad Bus LVDS Driver with Flow-Through Pinout

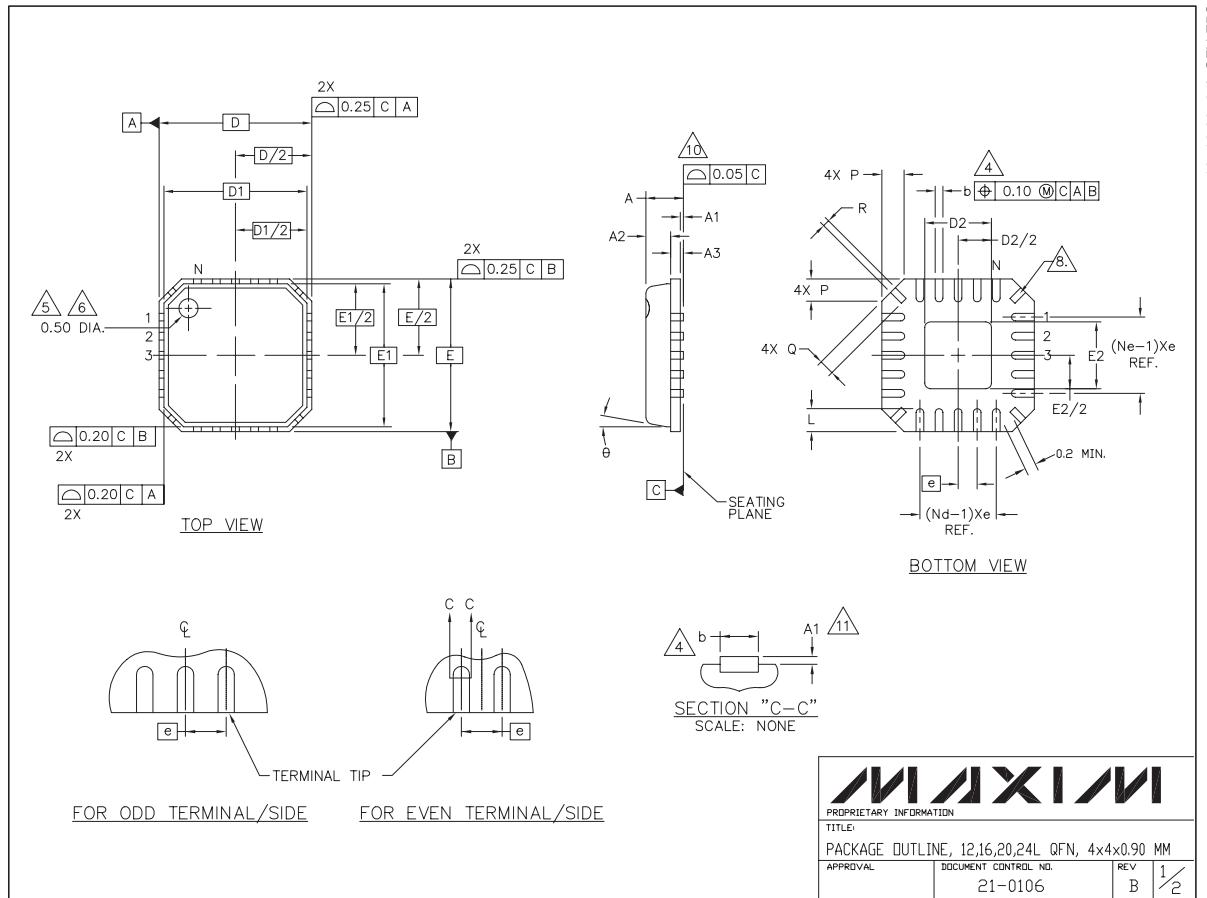

## Package Information (continued)

# Quad Bus LVDS Driver with Flow-Through Pinout

## Package Information (continued)

MAX9129

### NOTES:

1. DIE THICKNESS ALLOWABLE IS 0.305mm MAXIMUM (.012 INCHES MAXIMUM)

2. DIMENSIONING & TOLERANCES CONFORM MUST TO ASME Y14.5M. - 1994.

3.  $N$  IS THE NUMBER OF TERMINALS.

$N_d$  IS THE NUMBER OF TERMINALS IN X-DIRECTION &

$N_e$  IS THE NUMBER OF TERMINALS IN Y-DIRECTION.

4. DIMENSION  $b$  APPLIES TO PLATED TERMINAL AND IS MEASURED BETWEEN 0.20 AND 0.25mm FROM TERMINAL TIP.

5. THE PIN #1 IDENTIFIER MUST BE EXISTED ON THE TOP SURFACE OF THE PACKAGE BY USING INDENTATION MARK OR OTHER FEATURE OF PACKAGE BODY.

6. EXACT SHAPE AND SIZE OF THIS FEATURE IS OPTIONAL.

7. ALL DIMENSIONS ARE IN MILLIMETERS.

8. THE SHAPE SHOWN ON FOUR CORNERS ARE NOT ACTUAL I/O.

9. PACKAGE WARPAGE MAX 0.05mm.

10. APPLIED FOR EXPOSED PAD AND TERMINALS.

EXCLUDE EMBEDDING PART OF EXPOSED PAD FROM MEASURING.

11. APPLIED ONLY FOR TERMINALS.

12. MEETS JEDEC MO220.

| SYMBOL   | COMMON DIMENSIONS |      |      | $N_{O_{TE}}$ |

|----------|-------------------|------|------|--------------|

|          | MIN.              | NOM. | MAX. |              |

| A        | —                 | 0.85 | 1.00 |              |

| A1       | 0.00              | 0.01 | 0.05 | 11           |

| A2       | —                 | 0.65 | 0.80 |              |

| A3       | 0.20              | REF. |      |              |

| D        | 4.00              | BSC  |      |              |

| D1       | 3.75              | BSC  |      |              |

| E        | 4.00              | BSC  |      |              |

| E1       | 3.75              | BSC  |      |              |

| $\theta$ |                   |      | 12°  |              |

| P        | 0.24              | 0.42 | 0.60 |              |

| R        | 0.13              | 0.17 | 0.23 |              |

| SYMBOL | PITCH VARIATION A               |      |                                 | SYMBOL | PITCH VARIATION B               |      |                                 | SYMBOL | PITCH VARIATION C               |      |                                 | SYMBOL | PITCH VARIATION D            |      |                              | $N_{O_{TE}}$ |

|--------|---------------------------------|------|---------------------------------|--------|---------------------------------|------|---------------------------------|--------|---------------------------------|------|---------------------------------|--------|------------------------------|------|------------------------------|--------------|

|        | MIN.                            | NOM. | MAX.                            |        | MIN.                            | NOM. | MAX.                            |        | MIN.                            | NOM. | MAX.                            |        | MIN.                         | NOM. | MAX.                         |              |

| (a)    | 0.80                            | BSC  |                                 | (a)    | 0.65                            | BSC  |                                 | (a)    | 0.50                            | BSC  |                                 | (a)    | 0.50                         | BSC  |                              |              |

| N      | 12                              | 3    | N                               |        | 16                              | 3    | N                               |        | 20                              | 3    | N                               |        | 24                           | 3    |                              | 3            |

| $N_d$  | 3                               | 3    | $N_d$                           |        | 4                               | 3    | $N_d$                           |        | 5                               | 3    | $N_d$                           |        | 6                            | 3    |                              | 3            |

| $N_e$  | 3                               | 3    | $N_e$                           |        | 4                               | 3    | $N_e$                           |        | 5                               | 3    | $N_e$                           |        | 6                            | 3    |                              | 3            |

| L      | 0.50                            | 0.60 | 0.75                            | L      | 0.50                            | 0.60 | 0.75                            | L      | 0.50                            | 0.60 | 0.75                            | L      | 0.30                         | 0.40 | 0.55                         |              |

| b      | 0.28                            | 0.33 | 0.40                            | b      | 0.23                            | 0.28 | 0.35                            | b      | 0.18                            | 0.23 | 0.30                            | b      | 0.18                         | 0.23 | 0.30                         | 4            |

| Q      | 0.30                            | 0.40 | 0.65                            | Q      | 0.30                            | 0.40 | 0.65                            | Q      | 0.30                            | 0.40 | 0.65                            | Q      | 0.00                         | 0.20 | 0.45                         |              |

| D2     | SEE EXPOSED PAD VARIATION: A, B | D2   | SEE EXPOSED PAD VARIATION: A, B | D2     | SEE EXPOSED PAD VARIATION: A, B | D2   | SEE EXPOSED PAD VARIATION: A, B | D2     | SEE EXPOSED PAD VARIATION: A, B | D2   | SEE EXPOSED PAD VARIATION: A, B | D2     | SEE EXPOSED PAD VARIATION: A | D2   | SEE EXPOSED PAD VARIATION: A |              |

| F2     | SEE EXPOSED PAD VARIATION: A, B | E2   | SEE EXPOSED PAD VARIATION: A, B | E2     | SEE EXPOSED PAD VARIATION: A, B | E2   | SEE EXPOSED PAD VARIATION: A, B | E2     | SEE EXPOSED PAD VARIATION: A, B | E2   | SEE EXPOSED PAD VARIATION: A, B | E2     | SEE EXPOSED PAD VARIATION: A | E2   | SEE EXPOSED PAD VARIATION: A |              |

| SYMBOLS                | D2  |      |      | E2   |      |      | NOTE |

|------------------------|-----|------|------|------|------|------|------|

|                        | MIN | NOM  | MAX  | MIN  | NOM  | MAX  |      |

| EXPOSED PAD VARIATIONS | A   | 1.95 | 2.10 | 2.25 | 1.95 | 2.10 | 2.25 |

|                        | B   | 1.55 | 1.70 | 1.85 | 1.55 | 1.70 | 1.85 |

EXAMPLE: WE CAN CALL VARIATION "BB" FOR 16 TERMINAL QFN WITH 1.70x1.70 mm NOMINAL EXPOSED PAD DIMENSION. THE FORMER ONE IN VARIATION IS FOR PITCH VARIATION AND THE LATTER ONE IS FOR EXPOSED PAD VARIATION.

|                                                |

|------------------------------------------------|

| <b>MAXIM</b>                                   |

| PROPRIETARY INFORMATION                        |

| TITLE:                                         |

| PACKAGE OUTLINE, 12,16,20,24L QFN, 4x4x0.90 MM |

| APPROVAL                                       |

| DOCUMENT CONTROL NO.                           |

| 21-0106                                        |

| REV                                            |

| B                                              |

| 2/2                                            |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

**Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600**

13