**ALPHA & OMEGA**

SEMICONDUCTOR

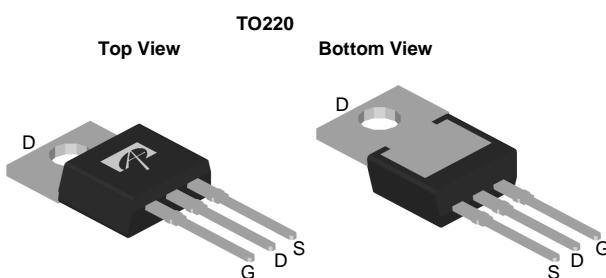

**AOT500L**

**N-Channel Enhancement Mode Field Effect Transistor**

### General Description

AOT500 uses an optimally designed temperature compensated gate-drain zener clamp. Under overvoltage conditions, the clamp activates and turns on the MOSFET, safely dissipating the energy in the MOSFET. The built in resistor guarantees proper clamp operation under all circuit conditions, and the MOSFET never goes into avalanche breakdown. Advanced trench technology provides excellent low  $R_{DS(on)}$ , gate charge and body diode characteristics, making this device ideal for motor and inductive load control applications. Standard Product AOT500 is Pb-free (meets ROHS & Sony 259 specifications)

### Features

$V_{DS}$  (V) = Clamped

$I_D = 80A$  ( $V_{GS} = 10V$ )

$R_{DS(ON)} < 5.3 m\Omega$  ( $V_{GS} = 10V$ )

100% UIS tested

100%  $R_g$  tested

### Absolute Maximum Ratings $T_A=25^\circ C$ unless otherwise noted

| Parameter                                | Symbol         | Maximum    | Units |

|------------------------------------------|----------------|------------|-------|

| Drain-Source Voltage                     | $V_{DS}$       | clamped    | V     |

| Gate-Source Voltage                      | $V_{GS}$       | clamped    | V     |

| Continuous Drain Current <sup>G</sup>    | $I_D$          | 80         | A     |

| $T_C=100^\circ C$                        |                | 57         |       |

| Continuous Drain Gate Current            | $I_{DG}$       | $\pm 50$   | mA    |

| Continuous Gate Source Current           | $I_{GS}$       | $\pm 50$   |       |

| Pulsed Drain Current <sup>C</sup>        | $I_{DM}$       | 250        | A     |

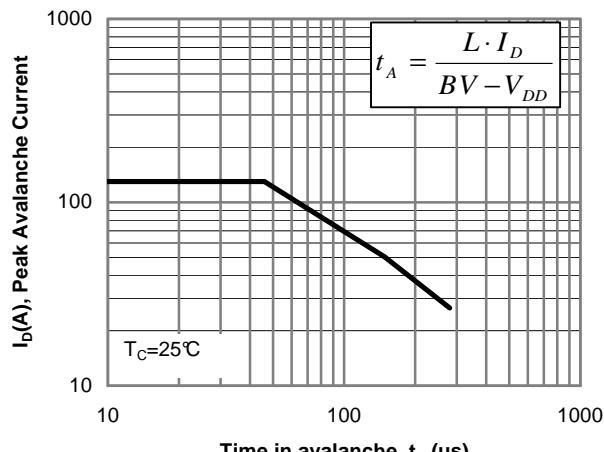

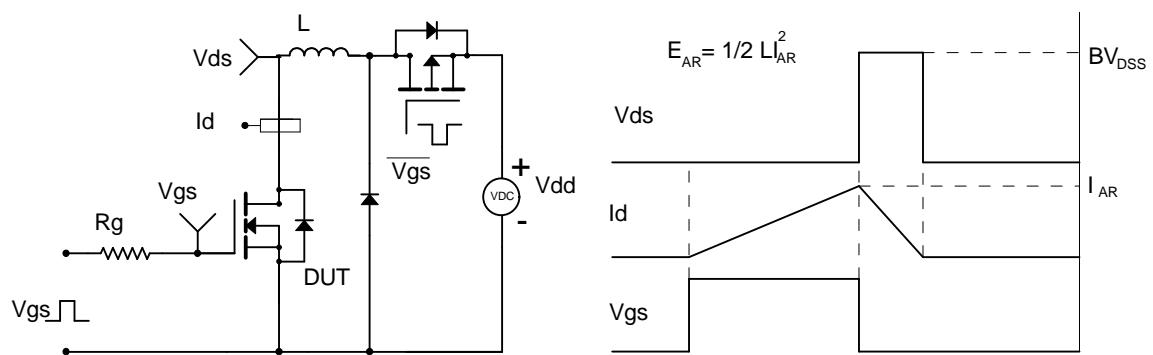

| Avalanche Current $L=100\mu H^H$         | $I_{AR}$       | 50         | A     |

| Repetitive avalanche energy <sup>H</sup> | $E_{AR}$       | 125        | mJ    |

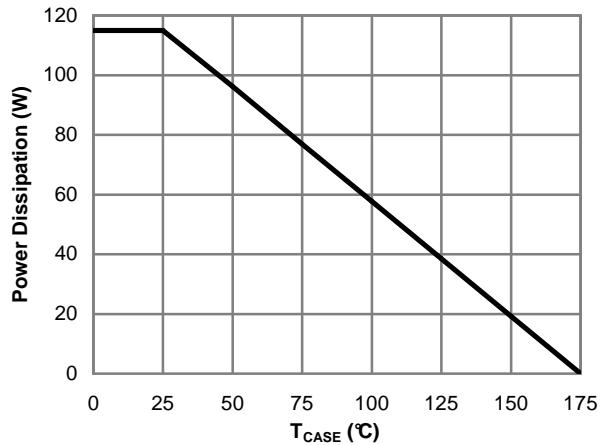

| Power Dissipation <sup>B</sup>           | $P_D$          | 115        | W     |

| $T_C=25^\circ C$                         |                | 58         |       |

| Junction and Storage Temperature Range   | $T_J, T_{STG}$ | -55 to 175 | °C    |

### Thermal Characteristics

| Parameter                                | Symbol          | Typ | Max | Units |

|------------------------------------------|-----------------|-----|-----|-------|

| Maximum Junction-to-Ambient <sup>A</sup> | $R_{\theta JA}$ | 60  | 75  | °C/W  |

| Maximum Junction-to-Case <sup>B</sup>    | $R_{\theta JC}$ | 0.7 | 1.3 | °C/W  |

Electrical Characteristics ( $T_J=25^\circ\text{C}$  unless otherwise noted)

| Symbol                             | Parameter                             | Conditions                                                                                           | Min | Typ  | Max  | Units            |

|------------------------------------|---------------------------------------|------------------------------------------------------------------------------------------------------|-----|------|------|------------------|

| <b>STATIC PARAMETERS</b>           |                                       |                                                                                                      |     |      |      |                  |

| $\text{BV}_{\text{DSS}(\text{z})}$ | Drain-Source Breakdown Voltage        | $I_D=10\text{mA}$ , $V_{\text{GS}}=0\text{V}$                                                        | 33  |      |      | V                |

| $\text{BV}_{\text{CLAMP}}$         | Drain-Source Clamping Voltage         | $I_D=1\text{A}$ , $V_{\text{GS}}=0\text{V}$                                                          | 36  |      | 44   | V                |

| $I_{\text{DSS}(\text{z})}$         | Zero Gate Voltage Drain Current       | $V_{\text{DS}}=16\text{V}$ , $V_{\text{GS}}=0\text{V}$                                               |     |      | 30   | $\mu\text{A}$    |

| $\text{BV}_{\text{GSS}}$           | Gate-Source Voltage                   | $V_{\text{DS}}=0\text{V}$ , $I_D=250\mu\text{A}$                                                     | 20  |      |      | V                |

| $I_{\text{GSS}}$                   | Gate-Body leakage current             | $V_{\text{DS}}=0\text{V}$ , $V_{\text{GS}}=\pm 10\text{V}$                                           |     |      | 10   | $\mu\text{A}$    |

| $V_{\text{GS}(\text{th})}$         | Gate Threshold Voltage                | $V_{\text{DS}}=V_{\text{GS}}$ , $I_D=250\mu\text{A}$                                                 | 1.5 | 2    | 3    | V                |

| $I_{\text{D}(\text{ON})}$          | On state drain current                | $V_{\text{GS}}=10\text{V}$ , $V_{\text{DS}}=5\text{V}$                                               | 250 |      |      | A                |

| $R_{\text{DS}(\text{ON})}$         | Static Drain-Source On-Resistance     | $V_{\text{GS}}=10\text{V}$ , $I_D=30\text{A}$                                                        |     | 4.1  | 5.3  | $\text{m}\Omega$ |

|                                    |                                       |                                                                                                      |     | 6.2  |      |                  |

| $g_{\text{FS}}$                    | Forward Transconductance              | $V_{\text{DS}}=5\text{V}$ , $I_D=30\text{A}$                                                         |     | 95   |      | S                |

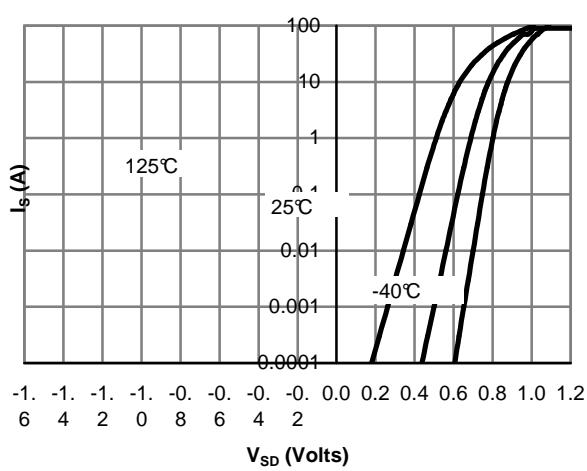

| $V_{\text{SD}}$                    | Diode Forward Voltage                 | $I_S=1\text{A}$ , $V_{\text{GS}}=0\text{V}$                                                          |     | 0.7  | 1    | V                |

| $I_S$                              | Maximum Body-Diode Continuous Current |                                                                                                      |     |      | 80   | A                |

| <b>DYNAMIC PARAMETERS</b>          |                                       |                                                                                                      |     |      |      |                  |

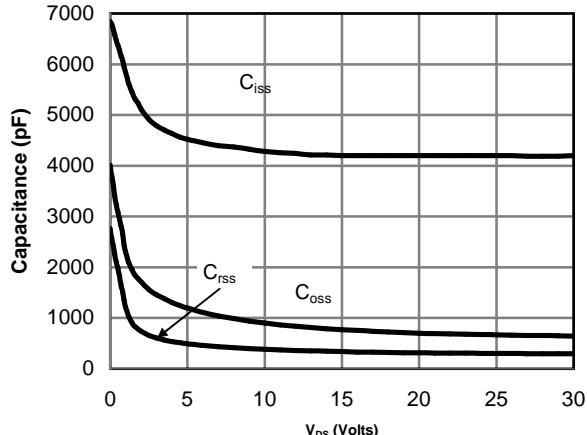

| $C_{\text{iss}}$                   | Input Capacitance                     | $V_{\text{GS}}=0\text{V}$ , $V_{\text{DS}}=15\text{V}$ , $f=1\text{MHz}$                             |     | 4200 | 5500 | $\text{pF}$      |

| $C_{\text{oss}}$                   | Output Capacitance                    |                                                                                                      |     | 765  |      | $\text{pF}$      |

| $C_{\text{rss}}$                   | Reverse Transfer Capacitance          |                                                                                                      |     | 340  |      | $\text{pF}$      |

| $R_g$                              | Gate resistance                       | $V_{\text{GS}}=0\text{V}$ , $V_{\text{DS}}=0\text{V}$ , $f=1\text{MHz}$                              |     | 13   | 30   | $\Omega$         |

| <b>SWITCHING PARAMETERS</b>        |                                       |                                                                                                      |     |      |      |                  |

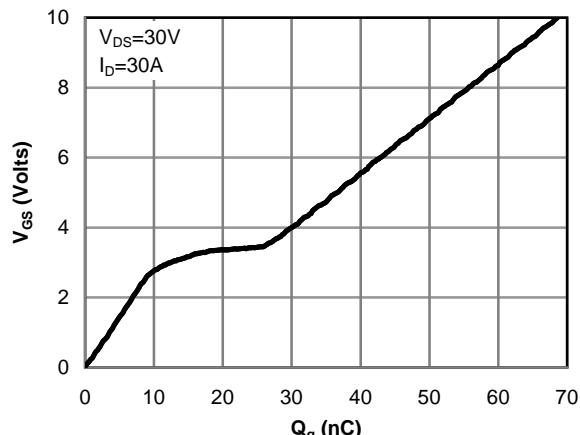

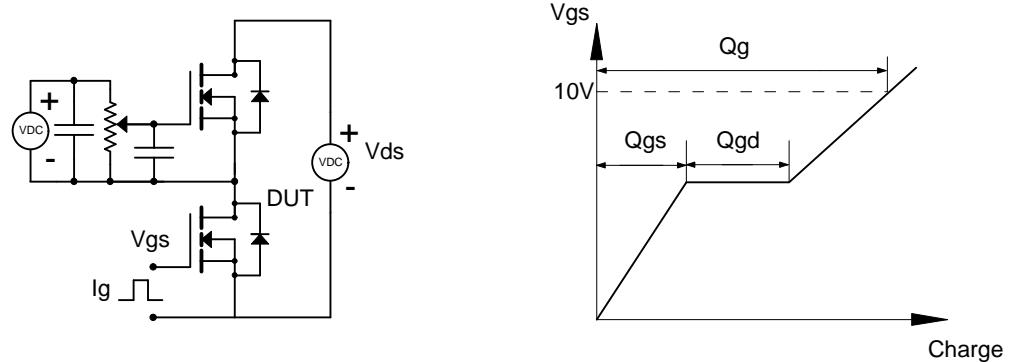

| $Q_g(10\text{V})$                  | Total Gate Charge                     | $V_{\text{GS}}=10\text{V}$ , $V_{\text{DS}}=15\text{V}$ , $I_D=30\text{A}$                           |     | 69   | 89   | $\text{nC}$      |

| $Q_g(4.5\text{V})$                 | Total Gate Charge                     |                                                                                                      |     | 34   |      | $\text{nC}$      |

| $Q_{\text{gs}}$                    | Gate Source Charge                    |                                                                                                      |     | 12   |      | $\text{nC}$      |

| $Q_{\text{gd}}$                    | Gate Drain Charge                     |                                                                                                      |     | 15   |      | $\text{nC}$      |

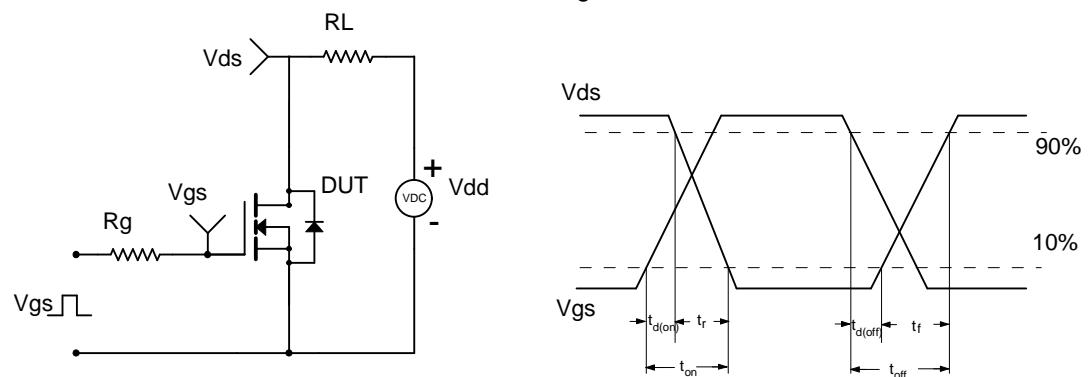

| $t_{\text{D}(\text{on})}$          | Turn-On DelayTime                     | $V_{\text{GS}}=10\text{V}$ , $V_{\text{DS}}=15\text{V}$ , $R_L=0.5\Omega$ , $R_{\text{GEN}}=3\Omega$ |     | 25   |      | ns               |

| $t_r$                              | Turn-On Rise Time                     |                                                                                                      |     | 35   |      | ns               |

| $t_{\text{D}(\text{off})}$         | Turn-Off DelayTime                    |                                                                                                      |     | 150  |      | ns               |

| $t_f$                              | Turn-Off Fall Time                    |                                                                                                      |     | 62   |      | ns               |

| $t_{\text{rr}}$                    | Body Diode Reverse Recovery Time      | $I_F=30\text{A}$ , $dI/dt=100\text{A}/\mu\text{s}$                                                   |     | 60   | 78   | ns               |

| $Q_{\text{rr}}$                    | Body Diode Reverse Recovery Charge    | $I_F=30\text{A}$ , $dI/dt=100\text{A}/\mu\text{s}$                                                   |     | 84   |      | $\text{nC}$      |

A: The value of  $R_{\theta JA}$  is measured with the device in a still air environment with  $T_A=25^\circ\text{C}$ .

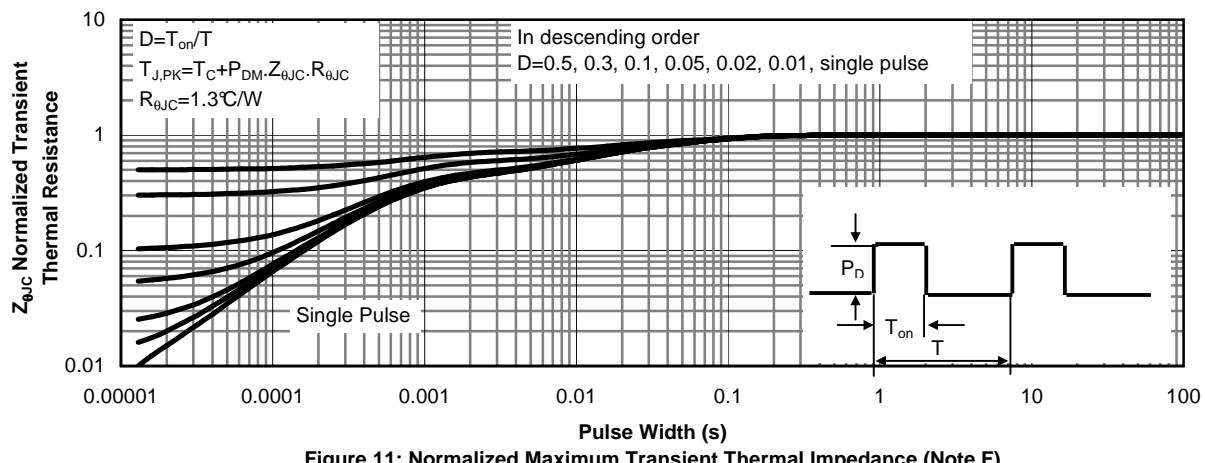

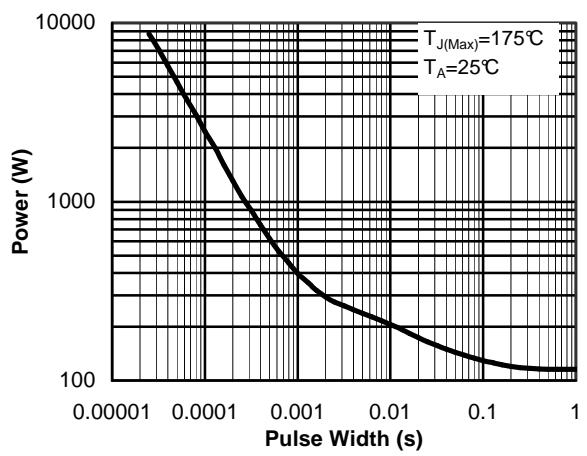

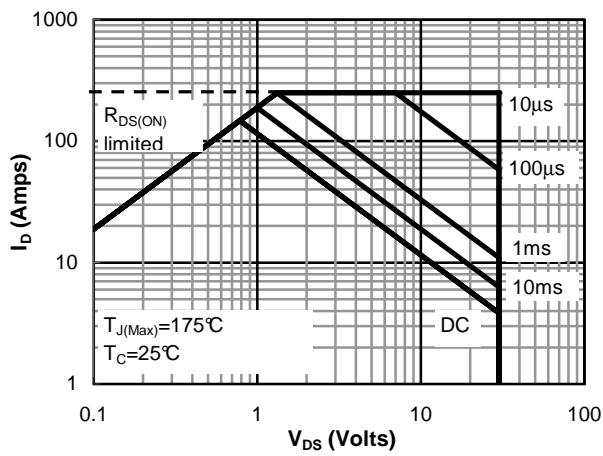

B. The power dissipation  $P_D$  is based on  $T_{J(\text{MAX})}=175^\circ\text{C}$ , using junction-to-case thermal resistance, and is more useful in setting the upper dissipation limit for cases where additional heatsinking is used.

C: Repetitive rating, pulse width limited by junction temperature  $T_{J(\text{MAX})}=175^\circ\text{C}$ .

D. The  $R_{\theta JA}$  is the sum of the thermal impedance from junction to case  $R_{\theta JC}$  and case to ambient.

E. The static characteristics in Figures 1 to 6 are obtained using  $<300\ \mu\text{s}$  pulses, duty cycle 0.5% max.

F. These curves are based on the junction-to-case thermal impedance which is measured with the device mounted to a large heatsink, assuming a maximum junction temperature of  $T_{J(\text{MAX})}=175^\circ\text{C}$ .

G. The maximum current rating is limited by bond-wires.

H.  $E_{\text{AR}}$  and  $I_{\text{AR}}$  are based on a  $100\mu\text{H}$  inductor with  $T_j(\text{start}) = 25^\circ\text{C}$  for each pulse.

Rev 2: Dec 2010

THIS PRODUCT HAS BEEN DESIGNED AND QUALIFIED FOR THE CONSUMER MARKET. APPLICATIONS OR USES AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS ARE NOT AUTHORIZED. AOS DOES NOT ASSUME ANY LIABILITY ARISING OUT OF SUCH APPLICATIONS OR USES OF ITS PRODUCTS. AOS RESERVES THE RIGHT TO IMPROVE PRODUCT DESIGN, FUNCTIONS AND RELIABILITY WITHOUT NOTICE.

## TYPICAL ELECTRICAL AND THERMAL CHARACTERISTICS

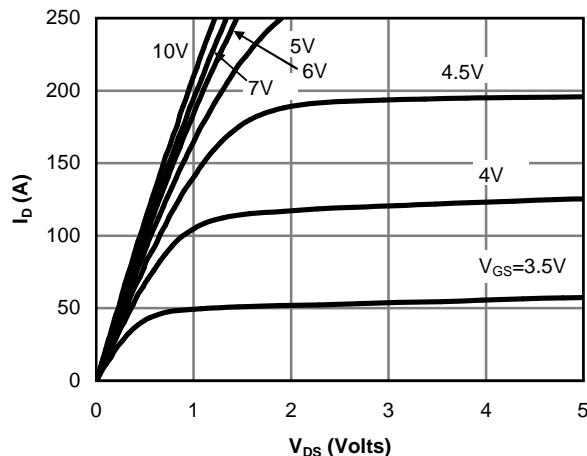

Fig 1: On-Region Characteristics

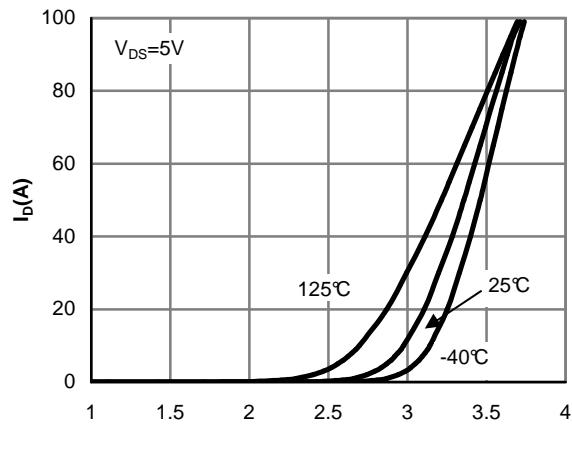

Figure 2: Transfer Characteristics

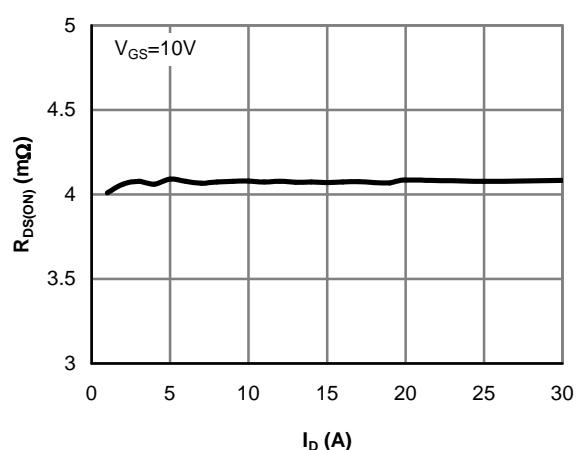

Figure 3: On-Resistance vs. Drain Current and Gate Voltage

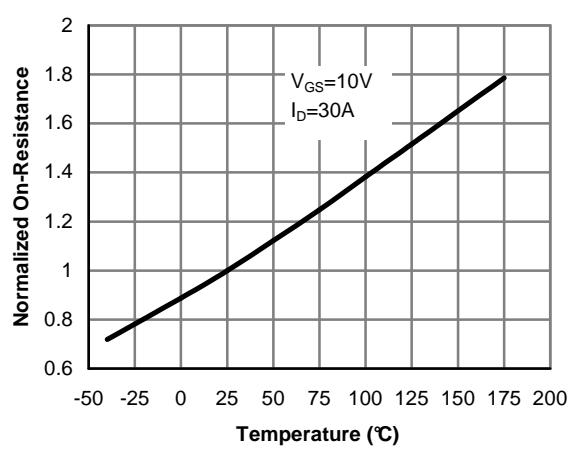

Figure 4: On-Resistance vs. Junction Temperature

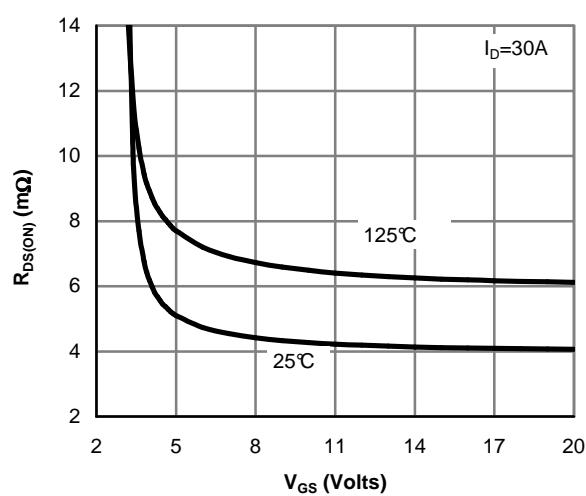

Figure 5: On-Resistance vs. Gate-Source Voltage

Figure 6: Body-Diode Characteristics

## TYPICAL ELECTRICAL AND THERMAL CHARACTERISTICS

## TYPICAL ELECTRICAL AND THERMAL CHARACTERISTICS

Figure 12: Single Pulse Avalanche capability

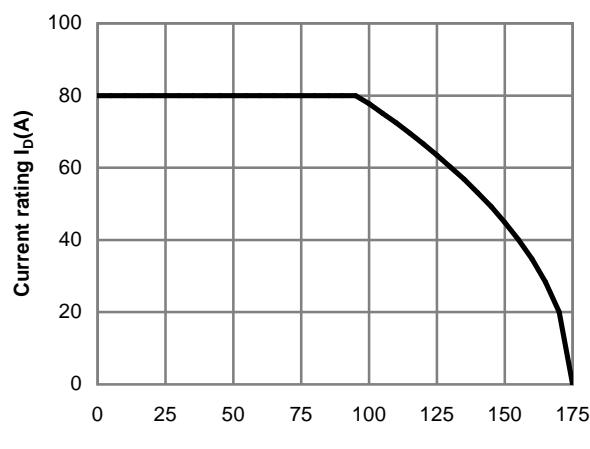

Figure 13: Power De-rating (Note B)

Figure 14: Current De-rating (Note B)

## TYPICAL PROTECTION CHARACTERISTICS

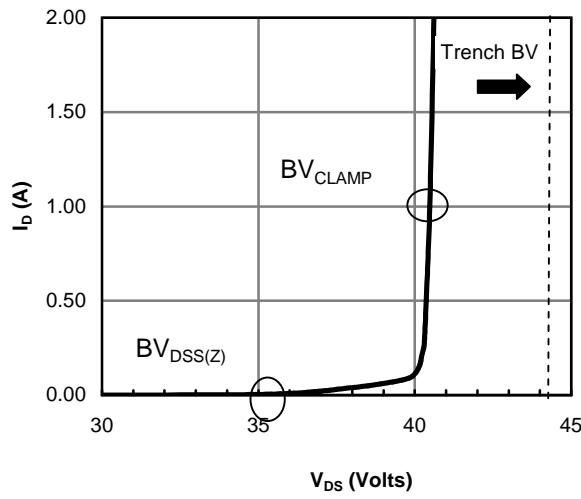

Fig 15:  $BV_{CLAMP}$  Characteristic

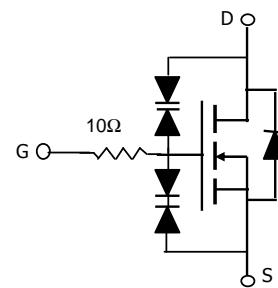

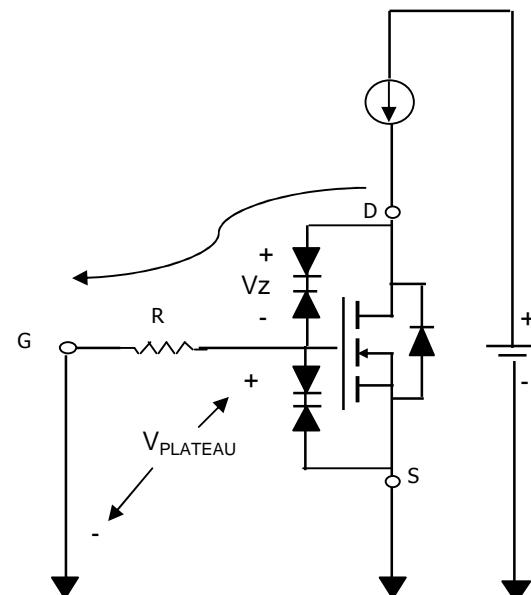

This device uses built-in Gate to Source and Gate to Drain zener protection. While the Gate-Source zener protects against excessive  $V_{GS}$  conditions, the Gate to Drain protection, clamps the VDS well below the device breakdown, preventing an avalanche condition within the MOSFET as a result of voltage over-shoot at the Drain electrode.

It is designed to breakdown well before the device breakdown. During such an event, current flows through the zener clamp, which is situated internally between the Gate to Drain. This current flows at  $BV_{DSS(Z)}$ , building up the  $V_{GS}$  internal to the device. When the current level through the zener reaches approximately 300mA, the  $V_{GS}$  is approximately equal to  $V_{GS(PLATEAU)}$ , allowing significant channel conduction and thus clamping the Drain to Source voltage. The  $V_{GS}$  needed to turn the device on is controlled with an internally lumped gate resistor  $R$  approximately equal to 10Ω.

$$V_{GS(PLATEAU)} = 10\Omega \times 300\text{mA} = 3\text{V}$$

It can also be said that the VDS during clamping is equal to:

$$BV_{DSS} = BV_{CLAMP} + V_{GS(PLATEAU)}$$

Additional power loss associated with the protection circuitry can be considered negligible when compare to the conduction losses of the MOSFET itself;

EX:

$$PL = 30\mu\text{A}_{\text{max}} \times 16\text{V} = 0.48\text{mW} \quad (\text{Zener leakage loss})$$

$$PL(rds) = 102\text{A} \times 6\text{m}\Omega = 300\text{mW} \quad (\text{MOSFET loss})$$

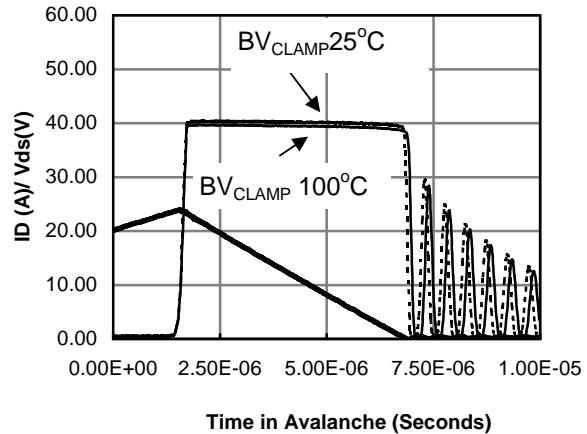

Fig 16: Unclamped Inductive Switching

Fig16: The built-in Gate to Drain clamp prevents the device from going into Avalanche by setting the clamp voltage well below the actual breakdown of the device. When the Drain to Gate voltage approaches the BV clamp, the internal Gate to Source voltage is charged up and channel conduction occurs, sinking the current safely through the device. The  $BV_{CLAMP}$  is virtually temperature independent, providing even greater protection during normal operation.

Gate Charge Test Circuit &amp; Waveform

Resistive Switching Test Circuit &amp; Waveforms

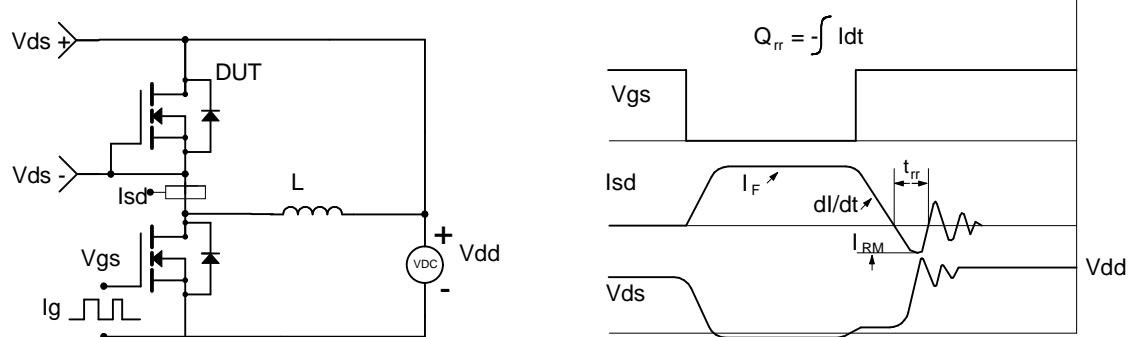

Unclamped Inductive Switching (UIS) Test Circuit &amp; Waveforms

Diode Recovery Test Circuit &amp; Waveforms