### MIC2342/2342R

### Dual-Slot PCI Express® Hot-Plug Controller

#### **General Description**

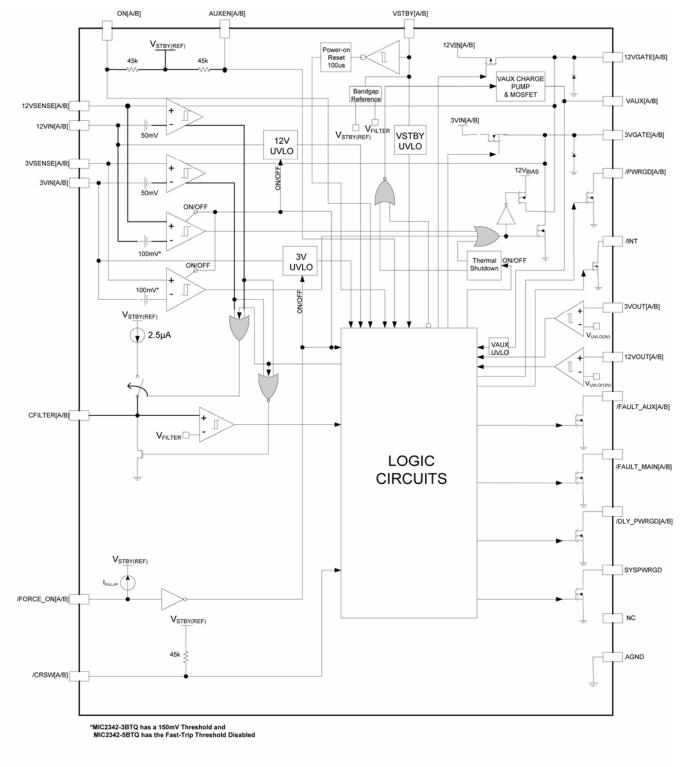

The MIC2342 is a dual-slot power controller supporting the power distribution requirements for Peripheral Component Interconnect Express (PCI Express®) Hot-Plug compliant systems. The MIC2342 provides complete power control support for two PCI Express slots, including the 3.3VAUX defined by the PCI Express standards. Support for the 12V. 3.3V. and 3.3VAUX supplies includes programmable gate voltage slew-rate control, voltage supervision, programmable current limit, and circuit breaker functions. These features provide comprehensive system protection and fault isolation. Additionally, in the event of an overcurrent fault on 3.3VAUX that "trips" the circuit breaker to cause the 3.3VAUX output to shut down, the MAIN outputs (3.3V and 12V) for the affected 3.3VAUX slot, A or B, will also be shut down. The MIC2341 controller provides truly independent output operation for MAIN and AUX.

Data sheets and support documentation can be found on Micrel's web site at: www.micrel.com.

#### **Features**

- Supports two independent PCI Express slots

- MAIN & AUX outputs are inter-dependent during AUX overcurrent conditions

- 12V, 3.3V, and 3.3VAUX supplies supported per PCI Express Specification v1.0a, v.2.0

- Integrated Power MOSFETS for 3.3VAUX rails

- Standby Operation for Wake-on-LAN applications with low backfeed on Main +12V and +3.3V rails

- Electronic circuit breakers for each supply per slot

- Programmable gate voltage slew-rate control

- Active current regulation controls inrush current

- High accuracy Primary and Secondary Circuit Breaker Current-limit Thresholds

- Dual-level, dual-speed fault detection for fast response without nuisance tripping

- User-programmable Primary Overcurrent Detector

- /PWRGD and Delayed /PWRGD (164 ms) Signal Outputs per slot

- Separate /FAULT output signals for MAIN and AUX rails for each slot

- · Global Systems Power-is-Good Output

- · Both slots thermally isolated

- Internally Debounced Plug-in Card Retention Switch Inputs per slot.

### **Applications**

PCI Express v1.0a, v2.0 hot-plug power control

## **Ordering Information**

| Part                        | Number                       | 12V and 3V              | 3.3VAUX Nominal |             |

|-----------------------------|------------------------------|-------------------------|-----------------|-------------|

| Latch Off                   | Auto-Retry                   | Fast-Trip<br>Thresholds | Current Limit   | Package     |

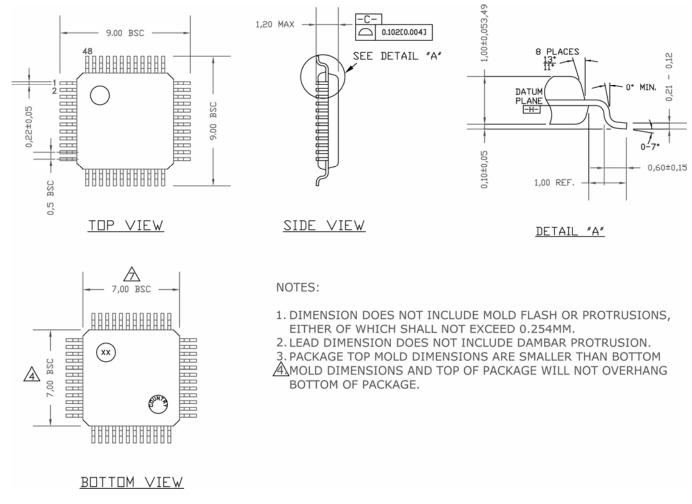

| MIC2342-2YTQ                | MIC2342R-2YTQ                | 100mV                   | 0.375A          | 48 Pin TQFP |

| MIC2342-3YTQ <sup>(1)</sup> | MIC2342R-3YTQ <sup>(1)</sup> | 150mV                   | 0.375A          | 48 Pin TQFP |

| MIC2342-5YTQ <sup>(1)</sup> | MIC2342R-5YTQ <sup>(1)</sup> | Disabled                | 0.375A          | 48 Pin TQFP |

#### Note:

<sup>1.</sup> Contact factory for availability

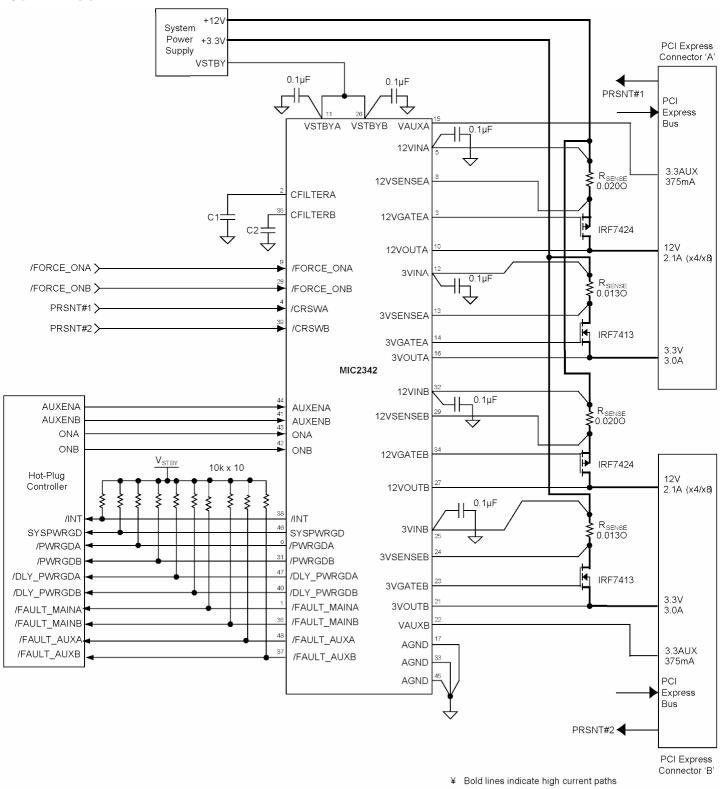

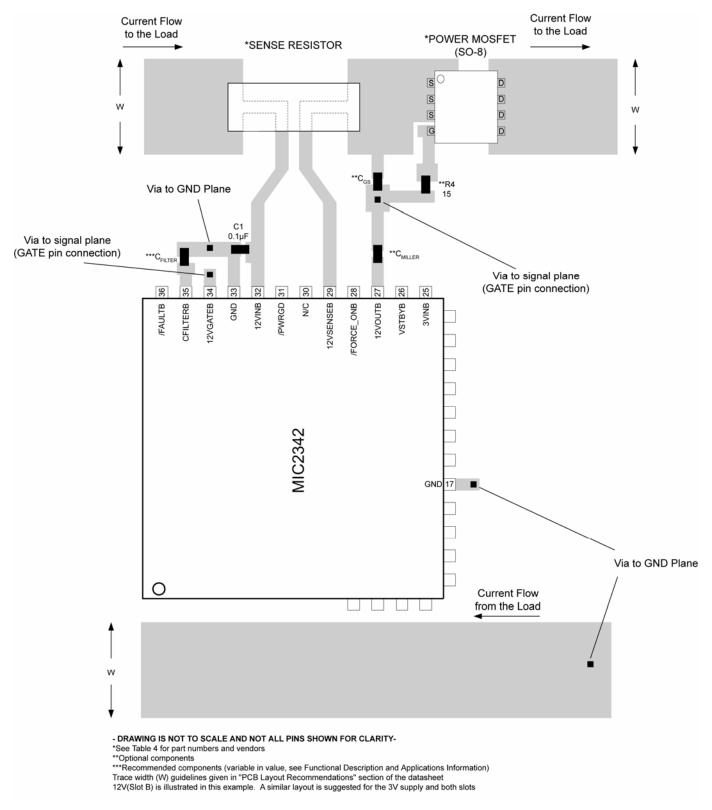

## **Typical Application**

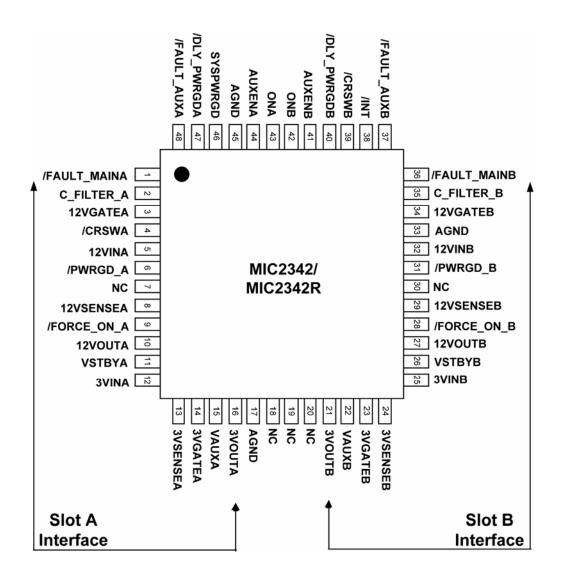

### **Pin Configuration**

## **Pin Description**

| Pin Number | Pin Name               | Pin Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|------------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

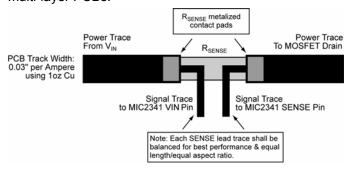

| 5<br>32    | 12VINA<br>12VINB       | 12V Supply Power and Sense Inputs [A/B]: Two pins are provided for Kelvin connection (one for each slot). Pin 5 is the (+) Kelvin-sense connection to the supply side of the sense resistor for 12V Slot A. Pin 32 is the (+) Kelvin-sense connection to the supply side of the sense resistor for 12V Slot B. These two pins must ultimately connect to each other as close as possible at the MIC2342 controller in order to eliminate any IR drop between these pins. An undervoltage lockout circuit (UVLO) prevents the switches from turning on while this input is lower than its lockout threshold voltage.                                           |

| 12<br>25   | 3VINA<br>3VINB         | 3.3V Supply Power and Sense Inputs [A/B]: Two pins are provided for connection (one for each slot). Pin 12 is the (+) Kelvin-sense connection to the supply side of the sense resistor for 3V Slot A. Pin 25 is the (+) Kelvin-sense connection to the supply side of the sense resistor for 3V Slot B. These two pins must ultimately connect to each other as close as possible at the MIC2342 controller in order to eliminate any IR drop between these pins. An undervoltage lockout circuit (UVLO) prevents the switches from turning on while this input is lower than its lockout threshold voltage.                                                  |

| 16<br>21   | 3VOUTA<br>3VOUTB       | 3.3V Power-Good Sense Inputs: Connect to 3.3V[A/B] outputs. Used to monitor the 3.3V output voltages for 3.3V Output Power-is-Good status.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 10<br>27   | 12VOUTA<br>12VOUTB     | 12V Power-Good Sense Inputs: Connect to 12V[A/B] outputs. Used to monitor the 12V output voltages for 12V Output Power-is-Good status.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

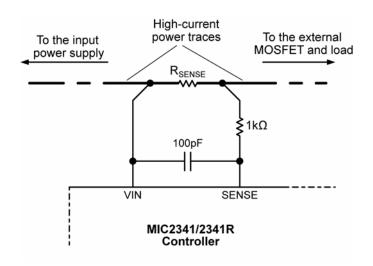

| 8<br>29    | 12VSENSEA<br>12VSENSEB | 12V Circuit Breaker Sense Input [A/B]: The current limit thresholds are set by connecting sense resistors between these pins and 12VIN[A/B]. When the 12V primary overcurrent detector current-limit threshold of 50mV is reached, the 12VGATE[A/B] pin is modulated to maintain a constant voltage across the sense resistor and therefore a constant current into the load. If the 50mV threshold is exceeded for t <sub>FLT</sub> or t <sub>DFLT</sub> (whichever is shorter), the circuit breaker is tripped and the corresponding 12VGATE pin for the affected slot is immediately pulled up to its corresponding 12VIN to turn OFF the external MOSFET. |

| 13<br>24   | 3VSENSEA<br>3VSENSEB   | 3V Circuit Breaker Sense Input [A/B]: The current limit thresholds are set by connecting sense resistors between these pins and 3VIN[A/B]. When the 3V primary overcurrent detector current-limit threshold of 50mV is reached, the 3VGATE[A/B] pin is modulated to maintain a constant voltage across the sense resistor and therefore a constant current into the load. If the 50mV threshold is exceeded for t <sub>FLT</sub> or t <sub>DFLT</sub> (whichever is shorter), the circuit breaker is tripped and the corresponding 3VGATE pin for the affected slot is immediately pulled down to AGND to turn OFF the external MOSFET.                       |

| 3<br>24    | 12VGATEA<br>12VGATEB   | 12V Gate Drive Outputs [A/B]: Each pin connects to the gate of an external P-channel power MOSFET. During power-up, the external $C_{\text{GATE}}$ (if used) and the $C_{\text{GS}}$ of the external MOSFETs are connected to a 25µA current sink. This controls the value of dv/dt seen at the source of the MOSFETs, and hence the current flowing into the 12V load capacitance.                                                                                                                                                                                                                                                                           |

|            |                        | During current limit events, the voltage at this pin is adjusted to maintain constant current through the FET for a period of $t_{\text{FLT}}$ or $t_{\text{DFLT}}$ (whichever is shorter). Whenever an overcurrent, thermal shutdown, or input undervoltage fault condition occurs, the corresponding 12VGATE pin for the affected slot is pulled up to its corresponding 12VIN pin to turn OFF the external MOSFET.                                                                                                                                                                                                                                         |

## Pin Description (cont.)

| Pin Number | Pin Name             | Pin Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

|------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 14<br>23   | 3VGATEA<br>3VGATEB   | 3V Gate Drive Outputs [A/B]: Each pin connects to the gate of an external N-channel power MOSFET. During power-up, the $C_{GATE}$ (if used) and the $C_{GS}$ of the external MOSFETs are connected to a 25 $\mu$ A current source. This controls the value of dv/dt seen at the source of the MOSFETs, and hence the current flowing into the 3V load capacitance.                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

|            |                      | During current limit events, the voltage at this pin is adjusted to maintain constant current through the FET for a period of $t_{\text{FLT}}$ or $t_{\text{DFLT}}$ (whichever is shorter). Whenever an overcurrent, thermal shutdown, or input undervoltage fault condition occurs, the corresponding 3VGATE pin for the affected slot is pulled down to AGND to turn OFF the external MOSFET.                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| 11<br>26   | VSTBYA<br>VSTBYB     | 3.3V Standby Supply Voltage: Required to support the PCI Express VAUX output. Additionally, all internal logic circuitry operates on VSTBY[A/B]. An internal UVLO circuit prevents turn-on of the external 3.3VAUX supply until the voltage at the VSTBY[A/B] pins is higher than the V <sub>UVLO(STBY)</sub> threshold voltage. Both pins must be externally connected together at the MIC2342 controller.                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| 15<br>22   | VAUXA<br>VAUXB       | 3.3VAUX[A/B] Outputs to PCI Express Card Slots: These outputs connect the 3.3AUX pin of the PCI Express connectors to VSTBY[A/B] via internal 0.4- $\Omega$ MOSFETs. These outputs are current limited and protected against short-circuit faults.                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| 44<br>43   | ONA<br>ONB           | Main +12VOUT[A/B] and +3.3VOUT[A/B] Enable Inputs: These level-sensitive digital inputs are each internally connected with pull-up resistors to VSTBY[A] and are used to enable or disable the MAIN[A/B] (+3.3V and +12V) outputs. Applying a high-to-low transition on ON[A/B] for at least 200ns (t <sub>LPW</sub> ) after a fault resets the +12V and/or +3.3V fault latches for the affected slot and de-asserts the /FAULT_MAIN[A/B] output signals. The +12V and/or the +3.3V electronic circuit breakers are reset once the /FAULT_MAIN[A/B] output signals are deasserted.                                                                                                                                |  |  |  |  |  |

| 45<br>42   | AUXENA<br>AUXENB     | VAUX[A/B] Enable Inputs: These level-sensitive digital inputs are each internally connected with pull-up resistors to VSTBY[A] and are used to enable or disable the VAUX[A/B] outputs. Applying a high-to-low transition on AUXEN[A/B] for at least 200ns (t <sub>LPW</sub> ) after a fault resets the VAUX fault latches for the affected slot and de-asserts the /FAULT_AUX[A/B] output signals. The VAUX[A/B] electronic circuit breakers are reset once the /FAULT_AUX[A/B] output signals are deasserted.                                                                                                                                                                                                   |  |  |  |  |  |

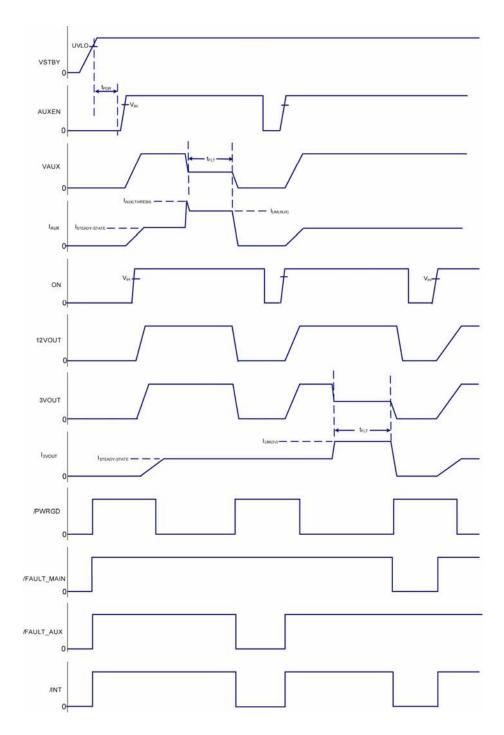

| 2<br>35    | CFILTERA<br>CFILTERB | Overcurrent Filter Capacitor [A/B]: Capacitors connected between these pins and AGND set the duration of $t_{\text{FLT}}$ , the response time of the primary overcurrent (OC) detector circuits. $t_{\text{FLT}}$ is the amount of time for which a slot remains in current limit before its circuit breaker is tripped. To configure the controller to use its internal digital filter delay timer, CFILTER[A/B] pins shall be connected to AGND. If the overcurrent filter times out during an AUX fault condition to shutdown the AUX output, the MAIN outputs of the corresponding slot will also be shutdown (See the "Output Signals' Timing Responses" in Figure 9 in the Functional Description section). |  |  |  |  |  |

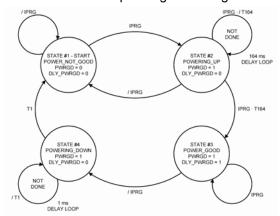

| 6<br>31    | /PWRGDA<br>/PWRGDB   | /PWRGD[A/B] are open-drain, asserted active-LOW digital outputs that are normally connected by an external $10k\Omega$ pull-up resistor (each) to VSTBY. Each output signal is asserted when inputs signals ON[A/B] and AUXEN[A/B] have been enabled, each output voltage has crossed its respective Power-is-Good output threshold (VuVTH(12V), VuVTH(3V), and VuVTH(VAUX) threshold voltages), and no fault conditions exist . Please consult the /PWRGD[A/B] and the /DLY_PWRGD[A/B] state diagrams in the Applications Information section for more detail.                                                                                                                                                   |  |  |  |  |  |

## Pin Description (cont.)

| Pin Number | Pin Name                     | Pin Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------|------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1<br>36    | /FAULT_MAINA<br>/FAULT_MAINB | /FAULT_MAIN[A/B] Outputs are open-drain, asserted active-LOW digital outputs that are normally connected by an external $10 \text{k}\Omega$ resistor to VSTBY. Asserted whenever the primary or secondary circuit breaker trips because of an overcurrent fault condition or an input undervoltage. Applying a high-to-low transition at the ON[A/B] pin resets the /FAULT_MAIN[A/B] outputs if /FAULT_MAIN[A/B] was asserted in response to a fault condition on one of the slot's MAIN outputs (+12V or +3.3V). If an overcurrent event asserted /FAULT_MAIN[A/B], the respective output's circuit breaker is reset when /FAULT_MAIN[A/B] output signal is de-asserted. A 200ns minimum pulse width ( $t_{\text{LPW}}$ ) for ON[A/B] will reset the MAIN outputs in the event of an overcurrent fault once the fault is removed.                     |

|            |                              | If a fault condition occurred on both the MAIN and VAUX outputs of the same slot, then a high-to-low transition on both ON[A/B] and AUXEN[A/B] must be applied to de-assert the /FAULT_MAIN[A/B] and /FAULT_AUX[A/B] outputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|            |                              | To simplify system fault reporting, the /FAULT_MAIN[A/B] output pins may be connected together with the /FAULT_AUX[A/B] output pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 4<br>39    | /CRSWA<br>/CRSWB             | Card Retention Switch Inputs [A/B]. These are level sensitive, asserted active- LOW digital inputs with internal pull-up resistors to VSTBY[A]. These inputs can be connected to the PRNST#1 or PRNST#2 pins on a PCle connector to indicate to the MIC2342 that a PCle plug-in card is present and firmly mated. Internally, the MIC2342's +12VGATE[A/B], +3VGATE[A/B], and 3VAUX[A/B] gate drive circuits are gated with the MIC2342's ON[A/B] and the AUXEN[A/B] inputs to deliver power to the connector only when a PCle plug-in card is present. During operation, if the /CRSW[A/B] inputs are disconnected or if there is a pc board trace failure, all outputs on the respective slot are turned OFF without delay. Each of these inputs exhibit an internal switch debounce delay of approximately 10ms.                                     |

| 48<br>37   | /FAULT_AUXA<br>/FAULT_AUXB   | /FAULT_AUX[A/B] Outputs are open-drain, asserted active-LOW digital outputs that are normally connected by an external $10k\Omega$ resistor to VSTBY. Asserted whenever the VAUX[A/B] circuit breaker trips because of an overcurrent fault condition or a slot/die overtemperature condition. Applying a high-to-low transition at the AUXEN[A/B] pin for at least 0.5μs resets the /FAULT_AUX[A/B] outputs if the /FAULT_AUX[A/B] output signal was asserted in response to a fault condition on the respective slot's VAUX output. If an overcurrent event asserted /FAULT_AUX[A/B], the respective output's VAUX circuit breaker is reset when /FAULT_AUX[A/B] output signal is de-asserted. A 200ns minimum pulse width ( $t_{LPW}$ ) for AUX_EN[A/B] will reset the MAIN outputs in the event of an overcurrent fault once the fault is removed. |

|            |                              | If a fault condition occurred on both the MAIN and VAUX outputs of the same slot, then a high-to-low transition on both ON[A/B] and AUXEN[A/B] must be applied to de-assert the /FAULT_MAIN[A/B] and /FAULT_AUX[A/B] outputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|            |                              | To simplify system fault reporting, the /FAULT_AUX[A/B] output pins may be connected together with the /FAULT_MAIN[A/B] output pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 9<br>28    | /FORCE_ONA<br>/FORCE_ONB     | Force On Enable Inputs [A/B]: These active-LOW, level-sensitive inputs with internal pull-up current ( $\mu$ A) to VSTBY[A] will turn on all three of the respective slot's outputs (+12V, +3.3V, and VAUX), while specifically defeating all protections on those supplies when asserted. This explicitly includes all overcurrent and short circuit protections and on-chip thermal protection for the VAUX[A/B] supplies. Additionally included are the UVLO protections for the +3.3V and +12V main supplies. The /FORCE_ON[A/B] pins do not disable UVLO protection for the VAUX[A/B] supplies.                                                                                                                                                                                                                                                   |

|            |                              | These input pins are intended for diagnostic purposes only.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|            |                              | Asserting /FORCE_ON[A/B] will cause the respective slot's /PWRGD[A/B] and /DLY_PWRGD[A/B] output signals to be asserted LOW and cause the /FAULT_MAIN[A/B], the /FAULT_AUX[A/B], the /INT, and the SYSPWRGD output signals to their open-drain state.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

## Pin Description (cont.)

| Pin Number     | Pin Name                   | Pin Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------------|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 47<br>40       | /DLY_PWRGDA<br>/DLY_PWRGDB | /DLY_PWRGD[A/B] are open-drain, asserted active-LOW digital outputs that are normally connected by an external $10k\Omega$ pull-up resistor (each) to VSTBY or to a local logic supply. Each output signal is asserted approximately 164 ms after their respective /PWRGD[A/B] output signals are asserted. The /DLY_PWRGD[A/B] output signals are de-asserted when the /PWRGD[A/B] outputs are de-asserted or upon a high-to-low transition on the ON[A/B] or AUXEN[A/B] inputs. There is approximately a 1-ms delay between the de-assertion of /DLY_PWRGD[A/B] and its corresponding /PWRGD[A/B] digital outputs. Please consult the /PWRGD[A/B] and /DLY_PWRGD[A/B] state diagrams within the Applications Information section for more detail. |

| 46             | SYSPWRGD                   | System Power is Good. SYSPWRGD is an open-drain, active-HIGH digital output that is normally connected by an external $10k\Omega$ pull-up resistor to VSTBY or to a local logic supply. The SYSPWRGD output signal is asserted LOW when: (1) /CRSW[A] is asserted, ON[A] is asserted, /FORCE_ON_A is HIGH, and either MAIN 12V[A] or MAIN 3V[B] output is below its output Power-Good threshold;                                                                                                                                                                                                                                                                                                                                                    |

|                |                            | (2) /CRSW[B] is asserted, ON[B] is asserted, /FOCRE_ON_B is HIGH, and either MAIN 12V[B] or MAIN 3V[B] output is below its output Power-Good threshold;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                |                            | (3) /CRSW[A] is asserted, AUXEN[A] is asserted, /FORCE_ON_A is HIGH, and the VAUXA output is below its output Power-Good threshold; or                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                |                            | (4) /CRSW[B] is asserted, AUXEN[B] is asserted, /FORCE_ON_B is HIGH, and VAUXB output is below its Power-Good threshold.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                |                            | For all other conditions, the SYSPWRGD output is open-drain. For more information with respect to the SYSPWRGD output signal, please consult the "Functional Description" section.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 38             | /INT                       | Interrupt Output: This open-drain, asserted active-LOW digital output is normally connected by an external $10k\Omega$ resistor to VSTBY or a local logic supply. This signal is asserted whenever a power fault is detected. Checking the status of /FAULT_MAIN[A/B] or /FAULT_AUX[A/B] output will determine which slot and which rail caused the interrupt. To de-assert this signal output, please follow instructions provided on /FAULT_MAIN[A/B] and /FAULT_AUX[A/B] output pin descriptions.                                                                                                                                                                                                                                                |

| 17<br>33<br>45 | AGND                       | 3 Pins, IC Ground Connections: Tie directly to the system's analog GND plane directly at the device.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 7<br>18<br>19  | NC                         | Reserved: Make no external connections to these pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 20<br>30       |                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

## Absolute Maximum Ratings<sup>(1)</sup>

| 12VIN[A/B], 12VSENSE[A/B], 12VGATE[A/B], |

|------------------------------------------|

| 12VOUT[A/B]14V                           |

| 3VIN[A/B], 3VSENSE[A/B], 3VGATE[A/B],    |

| 3VOUT[A/B], VSTBY[A/B], VAUX[A/B]7V      |

|                                          |

| Digital Inputs                           |

| ON[A/B], AUXEN[A/B], /CRSW[A/B],         |

| /FORCE_ON[A/B]0.5V (min) to 3.6V (max)   |

| CFILTER[A/B], RFILTER[A&B]7V             |

| Output Current                           |

| /PWRGD[A/B], /DLY_PWRGD[A/B]             |

| /FAULT MAIN[A/B], SYSPWRGD, /INT,        |

| /FAULT_AUX[A/B] 10mA                     |

| Power DissipationInternally Limited      |

| Lead Temperature (Soldering)             |

| Lead-Free Package (-xYTQ)                |

| IR Reflow, Peak260°C +0°C/-5°C           |

| Storage Temperature–65°C to +150°C       |

| ESD Rating <sup>(3)</sup>                |

| Human Body Model2kV                      |

| Machine Model                            |

| IVIACIIII IC IVIOUCI2007                 |

## Operating Ratings<sup>(2)</sup>

| Supply Voltages                        |                |

|----------------------------------------|----------------|

| 12VIN[A/B]                             | 11.0V to 13.0V |

| 3VIN[A/B]                              | 3.0V to 3.6V   |

| VSTBY[A/B]                             | 3.0V to 3.6V   |

| Ambient Temperature (T <sub>A</sub> )  | 0°C to + 70°C  |

| Junction Temperature (T <sub>J</sub> ) | 125°C          |

| Package Thermal Resistance             |                |

| TQFP $(\theta_{JA})$                   | 76.8°C/W       |

## **Electrical Characteristics**(4)

$12V_{IN[A/B]}$  = 12V,  $3V_{IN[A/B]}$  = 3.3V,  $V_{STBY[A/B]}$  = 3.3V,  $T_A$  = 25°C, unless otherwise noted. **Bold** values specifications applies over the full operating temperature range from 0 °C  $\leq$   $T_A \leq$  +70 °C.

| Symbol                                          | Parameter                                                                | Condition                                                                                                  | Min             | Тур               | Max               | Units          |

|-------------------------------------------------|--------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|-----------------|-------------------|-------------------|----------------|

| Power Control                                   | and Logic Sections                                                       |                                                                                                            | 1               | •                 | •                 | •              |

| ICC12<br>ICC3.3<br>ICCSTBY                      | Supply Current                                                           | /CRSW[A/B] = LOW<br>/FORCE_ON[A/B] = HIGH<br>AUX_EN[A/B], ON[A/B] = [L,H], [L,L]                           |                 | 1.8<br>0.6<br>2.8 | 3<br>2.5<br>5     | mA<br>mA<br>mA |

| Vuvlo(12V)<br>Vuvlo(3V)<br>Vuvlo(STBY)          | Undervoltage Lockout Thresholds<br>12VIN[A/B]<br>3VIN[A/B]<br>VSTBY[A/B] | 12V <sub>IN[A/B]</sub> increasing<br>3V <sub>IN[A/B]</sub> increasing<br>V <sub>STBY[A/B]</sub> increasing | 8<br>2.2<br>2.8 | 9<br>2.5<br>2.9   | 10<br>2.75<br>3.0 | V<br>V<br>V    |

| V <sub>HYSSTBY</sub>                            | Undervoltage Lockout Hysteresis VSTBY[A/B]                               |                                                                                                            |                 | 50                |                   | mV             |

| V <sub>HYSUV</sub>                              | Undervoltage Lockout Hysteresis 12VIN[A/B], 3VIN[A/B]                    |                                                                                                            |                 | 180               |                   | mV             |

| V <sub>UVTH(12V)</sub><br>V <sub>UVTH(3V)</sub> | Power-Good Undervoltage<br>Thresholds<br>12VOUT[A/B]<br>3VOUT[A/B]       | 12VOUT[A/B] decreasing<br>3VOUT[A/B] decreasing                                                            | 10.2<br>2.7     | 10.5<br>2.8       | 10.8<br>2.9       | V              |

| V <sub>UVTH(VAUX)</sub>                         | Power-Good Undervoltage<br>Threshold<br>VAUX[A/B]                        | VAUX[A/B] decreasing I <sub>AUX</sub> = 600mA                                                              | 2.7             | 2.8               | 2.9               | V              |

| V <sub>HYSPG</sub>                              | Power-Good Detect Hysteresis                                             |                                                                                                            |                 | 30                |                   | mV             |

| V <sub>GATE(12V)</sub>                          | 12VGATE[A/B] Voltage                                                     |                                                                                                            | 0               |                   | 1.5               | V              |

| I <sub>GATE(12VSINK)</sub>                      | 12VGATE[A/B] Pull-down Current                                           | Start Cycle                                                                                                | 15              | 25                | 35                | μA             |

| I <sub>GATE(12</sub> VPULLUP)                   | 12VGATE[A/B] Pull-up Current<br>(Fault Off)                              | Any fault condition<br>(VDD –VGATE) = 2.5V                                                                 | 20              |                   |                   | mA             |

## DC Electrical Characteristics<sup>(4)</sup>

$12V_{IN[A/B]}$  = 12V,  $3V_{IN[A/B]}$  = 3.3V,  $V_{STBY[A/B]}$  = 3.3V,  $T_A$  = 25°C, unless otherwise noted. **Bold** values specifications applies over the full operating temperature range from  $0^{\circ}C \le T_A \le +70^{\circ}C$ .

| Symbol                          | Parameter                                                                                                   | Condition                                                                                                                        | Min           | Тур                         | Max        | Units    |

|---------------------------------|-------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|---------------|-----------------------------|------------|----------|

| V <sub>GATE(3V)</sub>           | 3VGATE[A/B] Voltage                                                                                         |                                                                                                                                  | 12VIN<br>-1.5 |                             | 12VIN      | V        |

| I <sub>GATE(3VCHARGE)</sub>     | 3VGATE[A/B] Charge Current                                                                                  | Start Cycle                                                                                                                      | 15            | 25                          | 35         | μA       |

| I <sub>GATE</sub> (3VSINK)      | 3VGATE[A/B] Pull-down Current (Fault Off)                                                                   | Any fault condition V <sub>3VGATE</sub> = 2.5V                                                                                   | 65            |                             |            | mA       |

| $V_{FILTER}$                    | CFILTER[A/B] Threshold Voltage                                                                              |                                                                                                                                  | 1.20          | 1.25                        | 1.30       | V        |

| I <sub>FILTER</sub>             | CFILTER[A/B] Charging Current                                                                               | $V_{12VIN} - V_{12VSENSE} > V_{THILIMIT}$<br>and/or<br>$V_{3VIN} - V_{3VSENSE} > V_{THILIMIT}$                                   | 1.80          | 2.5                         | 5.0        | μA       |

| V <sub>THLIMIT</sub>            | Current Limit Threshold Voltages<br>12VIN[A/B] Supplies<br>3VIN[A/B] Supplies                               | V <sub>12VIN</sub> – V <sub>12VSENSE</sub><br>V <sub>3VIN</sub> – V <sub>3VSENSE</sub>                                           | 45<br>45      | 50<br>50                    | 57<br>57   | mV<br>mV |

| V <sub>THFAST</sub>             | 12VOUT[A/B] & 3VOUT[A/B] Fast-Trip Threshold Voltages                                                       | V <sub>12VIN</sub> – V <sub>12VSENSE</sub><br>V <sub>3VIN</sub> – V <sub>3VSENSE</sub><br>MIC2342-2YTQ Only                      | 90            | 100                         | 110        | mV       |

| V <sub>THFAST</sub>             | 12VOUT[A/B] & 3VOUT[A/B] Fast-Trip Threshold Voltages                                                       | V <sub>12VIN</sub> - V <sub>12VSENSE</sub> MIC2342-2YTQ<br>V <sub>3VIN</sub> - V <sub>3VSENSE</sub> MIC2342-3YTQ<br>MIC2342-5YTQ | 135           | 100<br>150<br>Dis-<br>abled | 110<br>165 | mV<br>mV |

| I <sub>12VSENSE[A/B]</sub>      | 12VSENSE[A/B] Input Current                                                                                 |                                                                                                                                  |               | 0.35                        | 1          | μA       |

| I <sub>3VSENSE[A/B]</sub>       | 3VSENSE[A/B] Input Current                                                                                  |                                                                                                                                  |               | 0.35                        | 1          | μA       |

| I <sub>LKG,OFF(12VIN[A/B]</sub> | 12VIN[A/B] Input Leakage Current                                                                            | VSTBY = VSTBY[A/B] = +3.3V;<br>12VIN[A/B] = OFF; 3VIN[A/B] = OFF                                                                 |               |                             | 1          | μA       |

| I <sub>LKG,OFF(3VIN[A/B]</sub>  | 3VIN[A/B] Input Leakage Current                                                                             | VSTBY = VSTBY[A/B] = +3.3V;<br>12VIN[A/B] = OFF; 3VIN[A/B] = OFF                                                                 |               |                             | 1          | μA       |

| V <sub>IL</sub>                 | LOW-Level Digital Input Voltage<br>ON[A/B], AUXEN[A/B],<br>/CRSW[A/B],<br>/FORCE_ON[A/B]                    |                                                                                                                                  |               |                             | 0.8        | V        |

| V <sub>IH</sub>                 | HIGH-Level Digital Input Voltage<br>ON[A/B], AUXEN[A/B],<br>/CRSW[A/B],<br>/FORCE_ON[A/B]                   |                                                                                                                                  | 2.1           |                             | 3.6        | V        |

| V <sub>OL</sub>                 | LOW-Level Digital Output Voltage /FAULT_AUX[A/B], /INT, /FAULT_MAIN[A/B], /PWRGD[A/B] ,SYSPWRGD, /DLY_PWRGD | I <sub>OL</sub> = 3 mA                                                                                                           |               |                             | 0.4        | V        |

| Symbol                                                                                                  | Parameter                                                                                                                              | Condition                                                                                          | Min                                           | Тур                    | Max   | Units       |

|---------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|-----------------------------------------------|------------------------|-------|-------------|

| I <sub>LKG(OFF)</sub>                                                                                   | Digital Output Off-State Leakage<br>Current<br>/FAULT_AUX[A/B], /INT,<br>/FAULT_MAIN[A/B],<br>/PWRGD[A/B], SYSPWRGD<br>/DLY_PWRGD[A/B] |                                                                                                    |                                               |                        | 5     | μА          |

| R <sub>PULLUP</sub>                                                                                     | Internal Pull-up Resistors to VSTBY[A] /CRSW[A/B],ON[A/B], AUXEN[A/B]                                                                  | VSTBY[A/B] = +3.3V                                                                                 |                                               | 45                     |       | kΩ          |

| I <sub>PULLUP</sub>                                                                                     | Internal Pull-up Current to VSTBY[A] /FORCE_ON[A/B]                                                                                    | VSTBY[A/B] = +3.3V                                                                                 |                                               | 60                     |       | μА          |

| R <sub>DS(AUX)</sub>                                                                                    | Internal VAUX[A/B] Power<br>MOSFET Channel Resistance                                                                                  | I <sub>DS</sub> = 375 mA; T <sub>J</sub> = 100 °C                                                  |                                               |                        | 0.4   | Ω           |

| V <sub>OFF(12VOUT[A/B]</sub>                                                                            | 12VOUT[A/B] Off-state Output<br>Offset Voltage                                                                                         | ON[A/B] = LOW,<br>12VOUT[A/B] = OFF, T <sub>J</sub> = 100 °C                                       |                                               |                        | 50    | mV          |

| V <sub>OFF(3VOUT[A/B]</sub>                                                                             | 3VOUT[A/B] Off-state Output<br>Offset Voltage                                                                                          | ON[A/B] = LOW,<br>3VOUT[A/B] = OFF, T <sub>J</sub> = 100 °C                                        |                                               |                        | 50    | mV          |

| V <sub>OFF(VAUX[A/B]</sub>                                                                              | VAUX[A/B] Off-state Output<br>Offset Voltage                                                                                           | AUXEN[A/B] = LOW,<br>VAUX[A/B] = OFF, T <sub>J</sub> = 100 °C                                      |                                               |                        | 50    | mV          |

| T <sub>OV</sub>                                                                                         | Overtemperature Shutdown and Reset Thresholds with Overcurrent on Slot <sup>(5)</sup>                                                  | T <sub>J</sub> increasing, each slot<br>T <sub>J</sub> decreasing, each slot                       |                                               | 140<br>130             |       | °C          |

|                                                                                                         | Overtemperature Shutdown and<br>Reset Thresholds, All Other<br>Conditions (All Outputs will Latch<br>OFF) <sup>(5)</sup>               | T <sub>J</sub> increasing, both slots T <sub>J</sub> decreasing, both slots                        |                                               | 160<br>150             |       | °C<br>°C    |

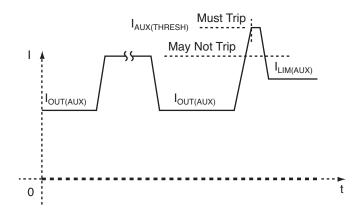

| I <sub>AUX(THRESH)</sub>                                                                                | Auxiliary Output Current Limit<br>Threshold (Figure 4)                                                                                 | Current which must be drawn from VAUX to register as a fault                                       |                                               | 0.84                   |       | Α           |

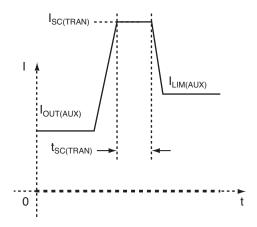

| I <sub>SC(TRAN)</sub>                                                                                   | Maximum Transient Short Circuit Current                                                                                                | VAUX[A/B] Enabled, then Grounded                                                                   | $I_{MAX} = \frac{V_{STBY[A/B]}}{R_{DS(AUX)}}$ |                        | A     |             |

| I <sub>LIM(AUX)</sub>                                                                                   | Regulated Current after Transient                                                                                                      | From end of I <sub>SC(TRAN)</sub> to CFILTER time-out                                              | 0.375                                         | 0.7                    | 0.975 | Α           |

|                                                                                                         | Output Discharge Resistance                                                                                                            |                                                                                                    |                                               |                        |       |             |

| $\begin{array}{c} R_{\text{DIS}(12V)} \\ R_{\text{DIS}(3V)} \\ R_{\text{DIS}(V\text{AUX})} \end{array}$ | 12VOUT[A/B]<br>3VOUT[A/B]<br>3VAUX[A/B]                                                                                                | 12V <sub>OUT[A/B]</sub> = 6.0V<br>3V <sub>OUT[A/B]</sub> = 1.65V<br>3V <sub>AUX[A/B]</sub> = 1.65V |                                               | 160<br>0<br>150<br>430 |       | Ω<br>Ω<br>Ω |

## AC Electrical Characteristics<sup>(4)</sup>

$12V_{IN[A/B]}$  = 12V,  $3V_{IN[A/B]}$  = 3.3V,  $V_{STBY[A/B]}$  = 3.3V,  $T_A$  = 25°C, unless otherwise noted. **Bold** values specifications applies over the full operating temperature range from  $0^{\circ}C \le T_A \le +70^{\circ}C$ .

| Symbol                      | Parameter                                                                                                                          | Condition                                                                                                  | Min  | Тур | Max   | Units |

|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|------|-----|-------|-------|

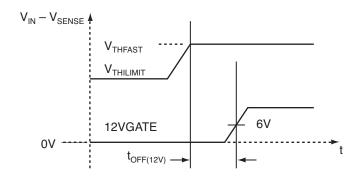

| t <sub>OFF(12V)</sub>       | 12V Current Limit Response Time (5) (Figure 2)                                                                                     | MIC2342-2YTQ<br>CGATE[A/B] = 25pF<br>V <sub>IN</sub> -V <sub>SENSE</sub> = 140mV                           |      | 1   | 2.0   | μs    |

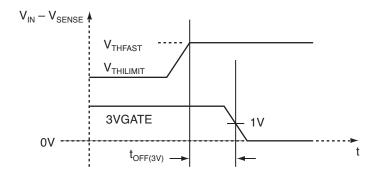

| t <sub>OFF(3V)</sub>        | 3.3V Current Limit Response<br>Time <sup>(5)</sup><br>(Figure 3)                                                                   | MIC2342-2YTQ<br>CGATE[A/B] = 25pF<br>V <sub>IN</sub> -V <sub>SENSE</sub> = 140mV                           |      | 1   | 2.0   | μs    |

| t <sub>SC(TRAN)</sub>       | VAUX[A/B] Current Limit<br>Response Time (Figure 5)                                                                                | VAUX[A/B] = 0V, VSTBY[A/B] = +3.3V                                                                         |      | 2.5 | 5     | μs    |

| t <sub>PROP(12VFAULT)</sub> | Delay from 12VOUT[A/B] Overcurrent Limit to /FAULT_MAIN[A/B] = LOW (5)                                                             | MIC2342-2YTQ<br>CFILTER[A/B] = OPEN<br>V <sub>IN</sub> -V <sub>SENSE</sub> = 140mV                         |      |     | 1     | μs    |

| t <sub>PROP(3VFAULT)</sub>  | Delay from 3VOUTA/B] Overcurrent Limit to /FAULT_MAIN[A/B] = LOW (5)                                                               | MIC2342-2YTQ<br>CFILTER[A/B] = OPEN<br>V <sub>IN</sub> -V <sub>SENSE</sub> = 140mV                         |      |     | 2     | μs    |

| tprop(vauxfault)            | Delay on VAUX[A/B] Overcurrent from CFILTER "time out" (V <sub>CFILTER</sub> = V <sub>FILTER</sub> ) to  /FAULT_AUX[A/B] = LOW (5) | MIC2342-2YTQ<br>limit to /FAULT_AUX[A/B] output<br>CFILTER[A/B] = 50pF<br>V <sub>AUX</sub> Output Grounded |      | 10  |       | μs    |

| t <sub>LPW</sub>            | ON[A/B], AUXEN[A/B] Low Pulse<br>Width to Reset Output Upon Fault<br>Removal <sup>(5)</sup>                                        | ON[A/B], AUXEN[A/B]<br>= HIGH-to-LOW-HIGH                                                                  | 200  |     |       | ns    |

| tintclk                     | Digital Filter (Internal Clock)<br>Period                                                                                          |                                                                                                            | 5    |     | 15    | μs    |

| t <sub>POR</sub>            | MIC2342 Power-On Reset Time<br>after VSTBY[A/B] becomes valid                                                                      |                                                                                                            | 80   |     | 255   | μs    |

| t/crsw[A/B]                 | /CRSW[A/B] Debounce Delay<br>Time                                                                                                  |                                                                                                            | 5.10 |     | 15.85 | ms    |

| t/PWRGD                     | /PWRGD[A/B] De-assertion Delay Time                                                                                                | ON[A/B] or AUXEN[A/B] High-to-Low<br>Transition                                                            | 640  |     | 2040  | μs    |

| t <sub>/DLY_PWRGD</sub>     | /DLY_PWRGD[A/B] Assertion<br>Delay after /PWRGD[A/B]<br>Assertion                                                                  | ON[A/B], AUXEN[A/B] = HIGH,<br>12VOUT[A/B], 3VOUT[A/B], VAUX[A/B] =<br>VALID;                              | 80   |     | 241   | ms    |

| t <sub>DFLT</sub>           | Internal Primary OC Detector<br>Response Time<br>(MIC2342 and MIC2342R)                                                            | CFILTER[A/B] = GND                                                                                         | 20.5 | 41  | 63.5  | ms    |

| t <sub>AUTO RETRY</sub>     | Auto Retry Period<br>(MIC2342R only)                                                                                               |                                                                                                            | 410  |     | 1236  | ms    |

#### Notes:

- 1. Exceeding measurements given within the "Absolute Maximum Ratings" section may damage the device.

- 2. The device is not guaranteed to function outside of the measurements given in the "Operating Ratings" section.

- 3. These devices are ESD sensitive. Employ proper handling precautions. The HBM is 1.5kΩ in series with 100pF.

- 4. Specifications apply to packaged product only.

- 5. Parameters guaranteed by design, not subject to test.

## **Timing Diagrams**

Figure 1. 12V Current Limit Response Timing

Figure 2. 3V Current Limit Response Timing

Figure 3. VAUX Current Limit Threshold

Figure 4. VAUX Current Limit Response Timing

## **Functional Diagram**

MIC2342/MIC2342R Block Diagram

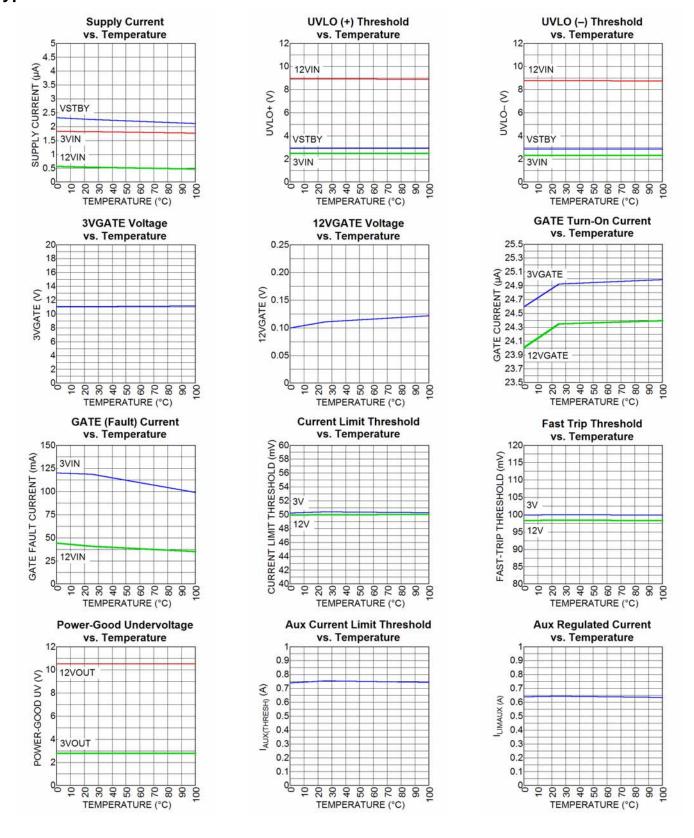

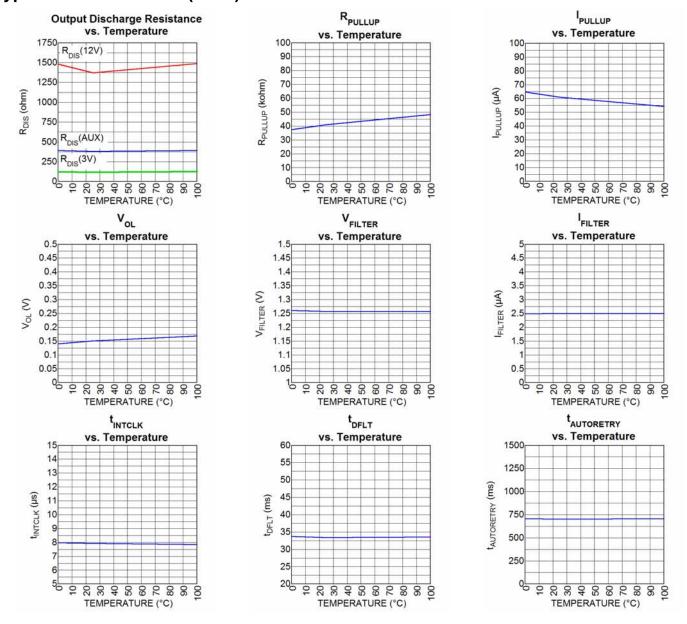

### **Typical Characteristics**

### **Typical Characteristics (cont.)**

### **Functional Description**

#### **Hot Swap Insertion**

When circuit boards are inserted into systems carrying live supply voltages ("hot-plugged"), high inrush currents often result due to the charging of bulk capacitance that resides across the circuit board's supply pins. This transient inrush current can cause the system's supply voltages to temporarily go out of regulation, causing data loss or system lock—up. In more extreme cases, the transients occurring during a hot-plug event may cause permanent damage to connectors or on-board components.

The MIC2342 addresses these issues by limiting the inrush currents to the load (PCI Express Board), and thereby controlling the rate at which the load's circuits turn-on. In addition to this inrush current control, the MIC2342 offers input and output voltage supervisory functions and current limiting to provide robust protection for both the system and circuit board.

#### **System Interface**

The MIC2342 employs a hardware system interface that includes: ON[A/B], AUXEN[A/B], /CRSW[A/B], /FAULT\_MAIN[A/B], /FAULT\_AUX[A/B], /PWRGD[A/B], /INT, and SYSPWRGD.

#### **Power-On Reset**

VSTBY[A/B] are the main power supply for the MIC2342's internal logic circuits and state machines . VSTBY[A/B] is required for proper operation of the MIC2342's internal logic circuitry and must be applied at all times. A Power-On Reset (POR) cycle is initiated after VSTBY[A/B] is higher than its V<sub>UVLO(STBY)</sub> threshold voltage and remains valid at that voltage for at least 80µs. All internal logic flags are cleared after POR. If the VSTBY[A/B] pin voltages are cycled ON-OFF-ON, a new power-on-reset cycle is initiated.  $V_{\text{STBY}}$  must be the first supply input applied followed by the MAIN supply inputs of  $12V_{IN}$  and  $3V_{IN}$ . During  $t_{POR}$ , all outputs remain off. In most applications, the total POR interval will consist of the time required to charge the V<sub>STBY</sub> input (bypass) capacitance to the UVLO threshold plus the internal t<sub>POR</sub> delay time. The following equation is used to approximate the total POR interval:

$$t_{POR\_TOTAL(\mu s)} = \left\{ \left[ \frac{\left( C_{STBY(\mu F)} \times V_{ULVO(STBY)} \right)}{I_{CHARGE(STBY)}(A)} \right] \times 10^{-6} \right\} + t_{POR}(\mu s)$$

where  $C_{\text{STBY}}$  is the  $V_{\text{STBY}}$  input bulk bypass capacitance and  $I_{\text{CHARGE}(\text{STBY})}$  is the current supplied by the  $V_{\text{STBY}}$  source to charge the capacitance.

#### +12VOUT[A/B] and +3VOUT[A/B] Start-Up Cycles

All four of the MIC2342's +12V and +3V gate drive circuits have been designed to drive the gates of external power MOSFETs. The +12V gate drive circuits have been designed to drive P-channel MOSFETs and the +3V gate drive circuits are intended to drive N-channel MOSFETs. A list of recommended N- and P-channel power MOSFETs suited for use with the MIC2342 and PCI Express applications can be found in Table 2

These gate drive circuits have also been designed to limit inrush current in one of two modes: (1) by controlling the 12VGATE[A/B] or the 3VGATE[A/B] voltage slew rates ( $dV_{12GATE[A/B]}/dt$  or  $dV_{3GATE[A/B]}/dt$ ) or (2) by actively limiting the inrush current, thereby charging the corresponding load capacitance in current limit. The mode that the MIC2342 automatically enters is dependent upon the magnitude of the inrush current and the magnitude of the load capacitance at 12VOUT[A/B] and 3VOUT[A/B].

#### Mode 1: [12V/3V]GATE[A/B] Slew Rate Control

When a slot's MAIN supply voltages (12VOUT[A/B] and 3VOUT[A/B]) are OFF, each of the 12VGATE[A/B] pins is held at 12VIN[A/B] by an internal pull-up transistor. Similarly, each 3VGATE[A/B] pin is internally held at AGND. When the MAIN supply voltages are enabled by a low-to-high transition on the ON[A/B] input pins (recall that the /CRSW[A/B] inputs must also be asserted), the 12VGATE[A/B] and the 3VGATE[A/B] pins are each connected to an internal constant current supply, typically 25 µA each. At each 12VGATE[A/B] pin, this constant current supply is a current sink; at each 3VGATE[A/B] pin, the supply is a current source. For applications where the inrush current is controlled by the 12VGATE[A/B] voltage rate of change, an expression for the circuit's behavior is given by the following equation:

$$\frac{\text{dV}_{12\text{VGATE[A/B]}}}{\text{dt}} = \frac{I_{\text{GATE}(12\text{VGATE})}}{C_{\text{ISSP}}} = \frac{25\mu A}{C_{\text{ISSP}}}$$

where  $C_{\text{ISSP}}$  = P-channel power MOSFET gate input capacitance.

For example, a Si4435BDY (a 30-V P-channel power MOSFET) exhibits an approximate  $C_{ISSP}$  of 1700pF at  $V_{DS}$  = 12V. The 12VGATE[A/B] pin voltage rate-of-change (slew rate) would be:

$$\frac{dV_{12VGATE[A/B]}}{dt} = \frac{I_{GATE(12VSNK)}}{C_{ISSP}} = \frac{25\mu A}{1700pF} = 14.7 \frac{V}{ms}$$

The 12VOUT[A/B] inrush current to the load while the 12VGATE[A/B] voltage is ramping is dependent on  $C_{\text{LOAD}(12\text{VOUT}[A/B])}$  and  $C_{\text{ISSP}}$ . An expression for the 12VOUT[A/B] inrush current is given by:

$$\begin{split} I_{INRUSH(12VOUT[A/B])} &= \frac{dV_{12VGATE[A/B]}}{dt} \times C_{LOAD(12VOUT[A/B])} \\ &= I_{GATE(12VSNK)} \times \frac{C_{LOAD(12VOUT[A/B])}}{C_{ISSP}} \end{split}$$

For the same p-channel power MOSFET in the previous example, if  $C_{\rm ISSP}$  = 1700pF and  $C_{\rm LOAD(12VOUT[A/B])}$  = 100µF, the 12VOUT[A/B] inrush current charging this load capacitance is:

$$I_{INRUSH(12VOUT[A/B])} = 25 \mu A \times \frac{100 \mu F}{1700 \rho F} = 1.47 A$$

Calculating the 12VOUT[A/B] voltage rate-of-change for a given capacitive load can be determined by the following expression:

$$\frac{dV_{12VOUT[A/B]}}{dt} = \frac{I_{INRUSH(12VOUT[A/B])}}{C_{LOAD(12VOUT[A/B])}}$$

and, using the same quantities in the current example, is given by:

$$\frac{\text{dV}_{12VOUT[A/B\ ]}}{\text{dt}} = \frac{1.47\ A}{100\ \mu\text{F}} = 14.7\ \frac{\text{V}}{\text{ms}}$$

To determine (to first-order) the time point at which the 12VOUT[A/B] voltage crosses its corresponding output "Power Good" threshold, the following equation can be used:

$$t_{PWRGD(12VOUT[A/B])} = \frac{\left(V_{UVTH(12V)} + V_{HYSPG}\right)}{\frac{dV_{12VOUT[A/B]}}{dt}} = \frac{10.53V}{14.7\frac{V}{ms}} \approx 0.72ms$$

To determine 3VGATE[A/B] pin voltage slew rates, inrush currents, 3VOUT[A/B] output voltage slew rates, and time to assert its corresponding internal "Power Good" flag into capacitive loads connected to 3VOUT[A/B], simple computations can be made using the same equations by substituting  $I_{\text{GATE}(3V\text{CHARGE})}$  for  $I_{\text{GATE}(12V\text{SINK})}$ ,  $C_{\text{ISSN}}$  (the input gate capacitance of an N-channel power MOSFET) for  $C_{\text{ISSP}}$ ,  $C_{\text{LOAD}(3V\text{OUT}[A/B])}$  for  $C_{\text{LOAD}(12V\text{OUT}[A/B])}$ ,  $I_{\text{INRUSH}(3V\text{OUT}[A/B])}$  for  $I_{\text{INRUSH}(12V\text{OUT}[A/B])}$ , and  $V_{\text{UVTH}(3V)}$  for  $V_{\text{UVTH}(12V)}$ .

For example, if a Si4420BDY n-channel power MOSFET is used with the MIC2342 to control inrush currents at 3VOUT[A/B], its  $C_{ISSN}$  is approximately 4100pF at  $V_{DS}$  = 3V. The 3VGATE[A/B] pin voltage rate of change is given by:

$$\frac{\text{dV}_{3\text{VGATE[A/B]}}}{\text{dt}} = \frac{I_{GATE(3\text{VCHARGE})}}{C_{ISSN}} = \frac{25 \mu A}{4100 \text{pF}} = 6.1 \frac{V}{\text{ms}}$$

Assuming a 300- $\mu$ F capacitive load, the 3VOUT[A/B] inrush current charging this load capacitance is given by:

$$I_{INRUSH(3VOUT[A/B])} = 25 \mu A \times \frac{300 \mu F}{4100 pF} = 1.82 A$$

The 3VOUT[A/B] output voltage slew rate is given by:

$$\frac{\text{dV}_{3VOUT[A/B]}}{\text{dt}} = \frac{1.82 \text{ A}}{300 \text{ } \mu\text{F}} \approx 6.1 \frac{\text{V}}{\text{ms}}$$

and the time to assert the internal 3VOUT[A/B] "Power Good" flag is given by:

$$t_{PWRGD(3VOU\,T[A/B])} = \frac{\left(V_{UVTH(3V)} + V_{HYSPG}\right)}{\frac{dV_{3VOUT[A/B]}}{dt}} = \frac{2.77V}{6.1\frac{V}{ms}} \approx 0.45 \; ms$$

# Mode 2: Charging 12VOUT and 3VOUT Capacitive Loads in Current Limit

In x4 and x8 PCI Express applications, capacitive loads at 12VOUT[A/B] and 3VOUT[A/B] can be as large as 1000µF. As a result, the inrush load charging currents at start-up can be large enough to cause a voltage drop across the external sense resistor larger than 50mV. In these applications, internal servo circuits at 12VGATE[A/B] and 3VGATE[A/B] modulate the drive to the gates of their corresponding power MOSFETs to regulate the load current to:

$$I_{LIMIT(12VOUT[A/B])} = \frac{V_{THLIMIT}}{R_{12VSENSE[A/B]}} = \frac{50 \text{ mV}}{R_{12VSENSE[A/B]}}$$

In the typical application circuit, the external sense resistor connected between 12VIN[A/B] and 12VSENSE[A/B] pins was selected to be  $20m\Omega$ . The regulated current charging the load capacitance at 12VOUT[A/B] is given by:

$$I_{LIMIT(12VOUT[A/B])} = \frac{50 \text{ mV}}{20 \text{ m}\Omega} = 2.5 \text{ A}$$

Once current-regulation control is activated, the circuit breaker's  $t_{\text{FLT}}$  timer is also activated to protect the external power MOSFET against potentially excessive power dissipation. For additional information on this timer and the MIC2342's circuit breaker operation, please consult the section labeled "Circuit Breaker Function." The output voltage rate of change at 12VOUT[A/B] during current limit charging into a 1000µF capacitive load is given by:

$$\frac{\text{dV}_{12\text{VOUT[A/B]}}}{\text{dt}} = \frac{I_{\text{LIMIT}(12\text{VOUT[A/B]})}}{C_{\text{LOAD}(12\text{VOUT[A/B]})}} = \frac{2.5 \text{ A}}{1000 \text{ \muF}} = 2.5 \frac{\text{V}}{\text{ms}}$$

In this fashion, the inrush current is controlled and the load capacitance is charged up slowly during the start-up cycle. The gate drive circuits will maintain control of the inrush current until the 12VOUT[A/B] or 3VOUT[A/B] voltages have reached their corresponding "Power Good" thresholds ( $V_{UVTH(12V)[A/B]}$  or  $V_{UVTH(3V)[A/B]}$ , respectively) at which time the inrush current approaches its nominal steady-state level, the voltage across the external sense resistor drops below the circuit breaker's  $V_{THLIMIT}$  threshold, and the corresponding internal "Power-is-Good" flag is asserted. For the 12VOUT[A/B] example, its internal "Power-is-Good" flag is asserted at:

$$t_{PWRGD(12VOUT[A/B])} = \frac{\left(V_{UVTH(12V)} + V_{HYSPG}\right)}{\frac{dV_{12VOUT[A/B]}}{dt}} = \frac{10.53V}{2.5\frac{V}{ms}} \approx 4.2\,\text{ms}$$

Calculating the current limit for charging the 3VOUT[A/B] load capacitance, the output voltage slew rate at

3VOUT[A/B], and when the internal 3VOUT[A/B] "Power Good" flag is asserted is a simple matter of substituting  $R_{3VSENSE[A/B]}$  for  $R_{12VSENSE[A/B]}$ ,  $C_{LOAD(3VOUT[A/B])}$  for  $C_{LOAD(12VOUT[A/B])}$ , and  $V_{UVTH(3V)}$  for  $V_{UVTH(12V)}$ .

Even though individual internal "Power Good" flags may be asserted, the conditions under which the MIC2342's external /PWRGD[A/B] and /DLY\_PWRGD[A/B] digital outputs are asserted is described in the section labeled "/PWRGD[A/B] and /DLY\_PWRGD[A/B] Digital Outputs."

#### **Power-Down Cycle**

When a slot is turned off, resistors internal to the MIC2342/MIC2342R are connected to each of the outputs to provide a discharge path for capacitors connected to the part's outputs. The nominal output discharge resistance values for each rail are found in the "Electrical Characteristics" table.

# Use of an External Gate Capacitor to Control Inrush Current Profile

In PCI Express applications where the 12VOUT[A/B] and the 3VOUT[A/B] maximum load capacitance is 1000  $\mu F$  (2000uF on the 12V rail for x16 modules), the PCI

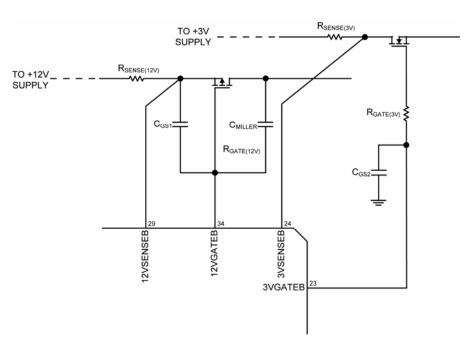

Express power control specification clearly states that any inrush current rate-of-change shall not exceed 0.1A/µs. This situation is most likely to happen when the controller is charging these large load capacitances in current limit. Under these circumstances, it may be preferable to modify the gate drive by using GATE voltage control instead of active current regulation to charge the load. As shown in Figure 5, an external capacitor connected from each 3VGATE[A/B] to AGND can be used. For the 12VGATE[A/B], an optional Miller capacitor (Gate-Drain) can be used in conjunction with a Gate-Source capacitor to form a Miller integrator to control the output slew rate. The optimal capacitor value is best determined empirically as the magnitude of the inrush current slew rate is a function of the power MOSFET's input capacitance  $(C_{ISS}),$ capacitance (C<sub>LOAD(3VOUT[A/B])</sub> and C<sub>LOAD(12VOUT[A/B])</sub>), and the current-limit sense resistor (R<sub>3VSENSE[A/B]</sub> R<sub>12VSENSE[A/B</sub>). Using an external capacitor to control the gate voltage slew rate for large load capacitance may affect the MIC2342/MIC2342R's specified system turnon and turn-off time performance.

Figure 5. (Optional) External Gate Slew Control Components

#### **Standby Mode**

Standby mode is entered when one or more of the MAIN supply inputs (12VIN and/or 3VIN) are below its respective UVLO threshold or OFF. The MIC2342 also supplies 3.3V auxiliary outputs (VAUX[A/B]), satisfying PCI Express specifications. These outputs are fed via the VSTBY[A/B] input pins and controlled by the AUXEN[A/B] input pins. These outputs are independent of the MAIN outputs (12VIN[A/B] and 3VIN[A/B]). Should the MAIN supply inputs move below their respective UVLO thresholds, VAUX[A/B] will still function as long as VSTBY[A/B] is present. Prior to standby mode, ONA and ONB inputs should be de-asserted or the MIC2342 will assert the /FAULT\_MAIN[A/B] and /INT output signals, if an undervoltage condition on the MAIN supply inputs is detected.

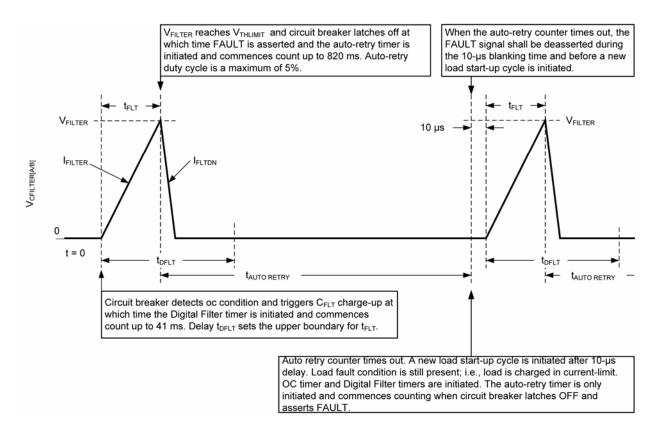

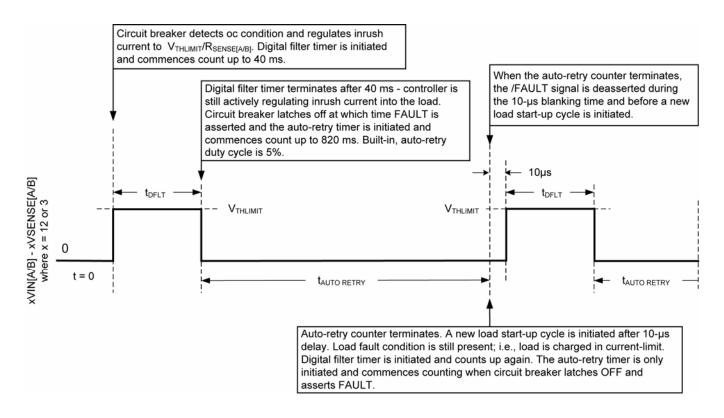

#### **Circuit Breaker Function**

The MIC2342 provides an electronic circuit breaker function that protects against excessive loads, such as short circuits, at each supply. When the current from one or more of a slot's MAIN outputs exceeds the current limit threshold ( $I_{\text{LIM}} = 50 \text{mV/R}_{\text{SENSE}}$ ) for a duration greater than  $t_{\text{FLT}}$ , the circuit breaker is tripped and both MAIN supplies (all outputs except VAUX[A/B]) are shut off. Should the load current cause a MAIN output's  $V_{\text{SENSE}}$  to exceed  $V_{\text{THFAST}}$ , the outputs are immediately shut off with no delay. Undervoltage conditions on the MAIN supply inputs also trip the circuit breaker, but only when the MAIN outputs are enabled (to signal a supply input brown-out condition).

The VAUX[A/B] outputs have a different circuit-breaker function. The VAUX[A/B] circuit breakers do not incorporate a fast-trip detector, instead they regulate the output current into a fault to avoid exceeding their operating current limit. The circuit breaker will trip due to an overcurrent on VAUX[A/B] when the fault timer expires, shutting down the VAUX output and both MAIN outputs of the affected slot. The AUX output dependence for the MAIN supplies during an AUX fault is inherent in the MIC2342/MIC2342R but does not apply for the MIC2341/MIC2341R. This use of the t<sub>FLT</sub> timer prevents the circuit breaker from tripping prematurely due to brief current transients.

Following a fault condition, the outputs can be turned on again by toggling the ON[A/B] input high-low-high (if the fault occurred on one of the MAIN outputs), or similarly toggling the AUXEN[A/B] input (if the fault occurred on the AUX outputs), or by cycling both ON[A/B] and AUXEN[A/B] (if faults occurred on both the MAIN and AUX outputs). When the circuit breaker trips, the corresponding /FAULT\_MAIN[A/B] or /FAULT\_AUX[A/B]

will be asserted. At the same time, /INT will be asserted. Note that /INT is only de-asserted by applying a high-to-low transition on the corresponding slot's ON[A/B] or AUXEN[A/B] input.

The response time ( $t_{FLT}$ ) of the MIC2342's primary overcurrent detector is set by external capacitors at the CFILTER[A/B] pins to GND. For Slot A, CFILTER[A] is located at Pin 2; for Slot B, CFILTER[B] is located at Pin 35. For a given response time, the value for  $C_{FILTER[A/B]}$  is given by:

$$C_{FILTER[A/B]}(\mu F) = \frac{t_{FLT[A/B]}(ms) \times l_{FILTER}(\mu A)}{V_{FILTER}(V) \times 10^3}$$