#### **FEATURES AND BENEFITS**

- Automotive AEC-Q100 qualified

- 5.25 to 40 V<sub>IN</sub> operating range, 50 V load dump rating

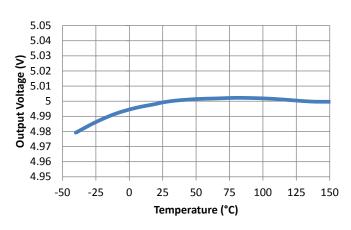

- 5 V  $\pm$ 1% internal LDO regulator

- Foldback short-circuit protection

- Short-to-battery protection (to 32 V, independent of  $V_{\rm IN}$ ) for harness faults

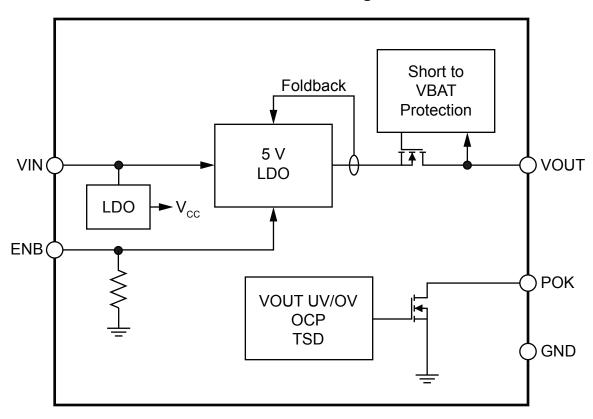

- Power OK (POK) flag

- High-voltage logic level enable input (ENB) for microprocessor control or connection directly to battery

- · Pin-to-pin and pin-to-ground tolerant at every pin

### Package:

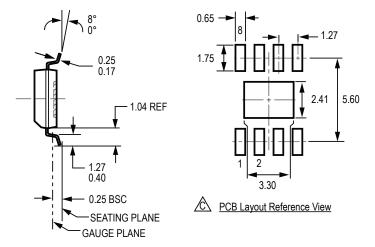

8-pin SOIC with exposed thermal pad (suffix LJ)

Not to scale

#### DESCRIPTION

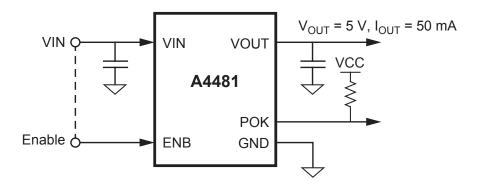

The A4481 is a single low-dropout linear regulator with complete control, diagnostics, and protection features that address many requirements of automotive applications. It regulates input voltages from 5.25 to 40 V, down to 5 V  $\pm 1\%$  output voltage and is able to supply up to 50 mA of load current.

Diagnostic output from the A4481 includes Power OK (POK) output to alert the microprocessor that a fault has occurred.

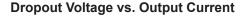

Protection features include input undervoltage lockout (UVLO), foldback overcurrent protection, output undervoltage and overvoltage protections (UV/OVP), and thermal shutdown (TSD). In addition, the output is protected from a short-to-battery event up to 32 V.

The A4481 device is available in an 8-pin SOIC package with exposed pad for enhanced thermal dissipation. It is lead (Pb) free, with 100% matte-tin leadframe plating.

#### **APPLICATIONS**

Power supplies for:

- Microcontrollers

- Transceivers (CAN, LIN, etc.)

- Sensors

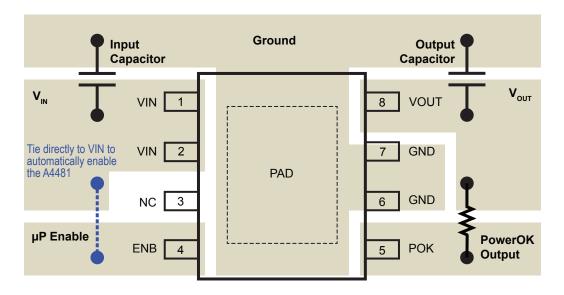

### **Typical Application Circuit**

### A4481

### 5 $V_{OUT}$ , 50 mA Automotive Linear Regulator with 50 V Load Dump and Short-to-Battery Protection

#### **SELECTION GUIDE**

| Part Number  | Temperature Range (°C) | Package                              | Packing*                   |

|--------------|------------------------|--------------------------------------|----------------------------|

| A4481KLJTR-T | -40 to 150             | 8-pin eSOIC with exposed thermal pad | 3000 pieces per 7-in. reel |

<sup>\*</sup>Contact Allegro for additional packing options.

#### ABSOLUTE MAXIMUM RATINGS\*

| Characteristic             | Symbol               | Notes              | Rating     | Unit |

|----------------------------|----------------------|--------------------|------------|------|

| VIN, ENB Pins              | $V_{IN}, V_{ENB}$    |                    | -0.3 to 50 | V    |

| VOUT Pin                   | V <sub>OUT</sub>     | Independent of VIN | -0.3 to 32 | V    |

| All other pins             |                      |                    | -0.3 to 7  | V    |

| Junction Temperature Range | T <sub>J</sub> (max) |                    | -40 to 165 | °C   |

| Storage Temperature Range  | T <sub>stg</sub>     |                    | -40 to 150 | °C   |

<sup>\*</sup>Stresses beyond those listed in this table may cause permanent damage to the device. The absolute maximum ratings are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the Electrical Characteristics table is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability

#### THERMAL CHARACTERISTICS:\* May require derating at maximum conditions; see application section for optimization

| Characteristic                                   | Symbol           | Test Conditions*     | Value | Unit |

|--------------------------------------------------|------------------|----------------------|-------|------|

| Package Thermal Resistance (Junction to Ambient) | R <sub>eJA</sub> | eSOIC-8 (LJ) package | 35    | °C/W |

<sup>\*</sup>Additional thermal information available on the Allegro website.

### **Functional Block Diagram**

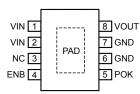

#### **Pinout Diagram**

#### **Terminal List Table**

| Number | Name | Function                                         |

|--------|------|--------------------------------------------------|

| 1      | VIN  | Input voltage pin                                |

| 2      | VIN  | Input voltage pin                                |

| 3      | NC   | No connect                                       |

| 4      | ENB  | Logic enable input from a microcontroller or DSP |

| 5      | POK  | Open-drain regulator fault detection output      |

| 6      | GND  | Ground                                           |

| 7      | GND  | Ground                                           |

| 8      | VOUT | 5 V regulator output                             |

### A4481

### 5 $V_{OUT}$ , 50 mA Automotive Linear Regulator with 50 V Load Dump and Short-to-Battery Protection

#### ELECTRICAL CHARACTERISTICS<sup>1</sup>: Valid at 5.25 V $\leq$ V<sub>INx</sub> $\leq$ 40 V, $-40^{\circ}$ C $\leq$ T<sub>A</sub> = T<sub>J</sub> $\leq$ 150°C, unless otherwise specified

| Characteristics                              | Symbol                  | Test Conditions                                                                 | Min. | Тур. | Max. | Units |

|----------------------------------------------|-------------------------|---------------------------------------------------------------------------------|------|------|------|-------|

| INPUT VOLTAGE                                |                         |                                                                                 | ·    |      |      |       |

| Operating Input Voltage                      | V <sub>IN</sub>         | ENB high                                                                        | 5.25 | 5.35 | 40   | V     |

| VIN UVLO Start Voltage                       | V <sub>IN(START)</sub>  | V <sub>IN</sub> rising, ENB high                                                | 4.75 | _    | 5.2  | V     |

| VIN UVLO Stop Voltage                        | V <sub>IN(STOP)</sub>   | V <sub>IN</sub> falling, ENB high                                               | 4.55 | _    | 5    | V     |

| VIN UVLO Hysteresis                          | V <sub>IN(HYS)</sub>    | V <sub>IN(START)</sub> - V <sub>IN(STOP)</sub>                                  | _    | 0.2  | _    | V     |

| INPUT CURRENT                                |                         |                                                                                 | '    |      |      |       |

| Input Quiescent Current <sup>1</sup>         | IQ                      | V <sub>IN</sub> = 5.25 V, ENB high                                              | _    | 3.4  | _    | mA    |

| Input Sleep Supply Current <sup>1</sup>      | I <sub>Q(SLEEP)</sub>   | V <sub>IN</sub> = 5.25 V, ENB low                                               | _    | 1    | 10   | μA    |

| 5 V LINEAR REGULATOR                         |                         |                                                                                 |      |      |      |       |

| Accuracy                                     |                         | I <sub>OUT</sub> = 25 mA, V <sub>IN</sub> = 5.25 V                              | 4.95 | 5    | 5.05 | V     |

| Load Regulation                              | - V <sub>OUT</sub>      | 5 mA < I <sub>OUT</sub> < 50 mA, V <sub>IN</sub> = 5.25 V                       | -1   | _    | +1   | %     |

| Output Capacitance Range <sup>2</sup>        | C <sub>OUT</sub>        |                                                                                 | 3    | 4.7  | 10   | μF    |

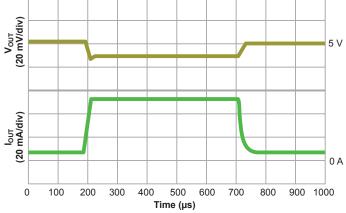

| Startup Time <sup>2</sup>                    | t <sub>START</sub>      | $C_{OUT} \le 4.7 \ \mu\text{F, Load} = 100 \ \Omega \pm 5\% \ (50 \ \text{mA})$ | 0.7  | 1.5  | 2.3  | ms    |

| LOGIN ENABLE (ENB) INPUT                     |                         |                                                                                 | · ·  |      | *    |       |

| CAID Threehold                               | V <sub>ENB(H)</sub>     | V <sub>ENB</sub> rising                                                         | _    | _    | 2    | V     |

| ENB Threshold                                | V <sub>ENB(L)</sub>     | V <sub>ENB</sub> falling                                                        | 0.8  | _    | _    | V     |

| ENB Resistance                               | R <sub>ENB</sub>        |                                                                                 | _    | 100  | _    | kΩ    |

| ENB Filter/Deglitch Time                     | t <sub>d(EN,FILT)</sub> |                                                                                 | 10   | 15   | 25   | μs    |

| OVERCURRENT PROTECTION (OCP                  | ")                      |                                                                                 | *    |      |      |       |

| Current Limit <sup>1</sup>                   | I <sub>LIM</sub>        | V <sub>OUT</sub> = 5 V                                                          | -55  | -80  | -140 | mA    |

| Foldback Current <sup>1</sup>                | I <sub>FBK</sub>        | V <sub>OUT</sub> = 0 V                                                          | -13  | -23  | -35  | mA    |

| THERMAL PROTECTION (TSD)                     |                         |                                                                                 | ,    |      |      |       |

| Thermal Shutdown Threshold <sup>2</sup>      | T <sub>TSD</sub>        | T <sub>J</sub> rising                                                           | 165  | _    | _    | °C    |

| Thermal Shutdown Hysteresis <sup>2</sup>     | T <sub>HYS</sub>        |                                                                                 | -    | 15   | -    | °C    |

| VOUT OV/UV PROTECTIONS                       |                         |                                                                                 | ·    |      | *    |       |

| VOLIT OV Threeholds                          | V <sub>OV(H)</sub>      | V <sub>OUT</sub> rising                                                         | 5.15 | 5.33 | 5.5  | V     |

| VOUT OV Thresholds                           | V <sub>OV(L)</sub>      | V <sub>OUT</sub> falling                                                        | _    | 5.3  | _    | V     |

| VOUT OV Hysteresis                           | V <sub>OV(HYS)</sub>    | $V_{OV(H)} - V_{OV(L)}$                                                         | 15   | 30   | 50   | mV    |

| VOUT UV Thresholds                           | V <sub>UV(H)</sub>      | V <sub>OUT</sub> rising                                                         | _    | 4.71 | _    | V     |

| VOOT OV Tillesholds                          | V <sub>UV(L)</sub>      | V <sub>OUT</sub> falling                                                        | 4.5  | 4.68 | 4.85 | V     |

| VOUT UV Hysteresis                           | V <sub>UV(HYS)</sub>    | $V_{UV(H)} - V_{UV(L)}$                                                         | 15   | 30   | 50   | mV    |

| VOUT Output Disconnect Threshold             | V <sub>DISC</sub>       | V <sub>OUT</sub> rising                                                         | _    | 7.2  | _    | V     |

| POK OUTPUTS                                  |                         |                                                                                 |      |      |      |       |

| POK Output Low Voltage                       | V <sub>POK(L)</sub>     | ENB high, V <sub>IN</sub> ≥ 5.25 V, I <sub>POK</sub> = 4 mA                     | _    | 150  | 400  | mV    |

| POK Leakage Current <sup>1</sup>             | I <sub>POK(LKG)</sub>   | V <sub>POK</sub> = 3.3 V                                                        | _    | _    | 2    | μA    |

| OV and UV Filter/Deglitch Times <sup>2</sup> | t <sub>d(FILT)</sub>    | Applies to undervoltage of the VOUT voltages                                    | 10   | 15   | 20   | μs    |

<sup>1</sup> For input and output current specifications, negative current is defined as coming out of the node or pin (sourcing), positive current is defined as going into the node or pin

<sup>&</sup>lt;sup>2</sup> Ensured by design and characterization, not production tested.

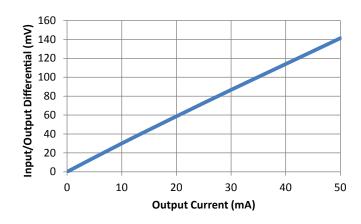

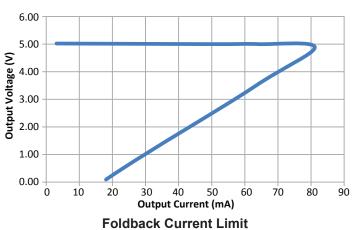

#### TYPICAL PERFORMANCE CHARACTERISTICS

**Output Voltage vs. Temperature**

Tappie Rejectio

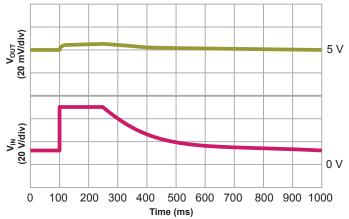

Load Dump Characteristics (V<sub>IN</sub> = 12 to 50 V, I<sub>OUT</sub> = 50 mA, C<sub>OUT</sub> = 4.7  $\mu$ F)

#### **FUNCTIONAL DESCRIPTION**

#### **Enable (ENB) Input**

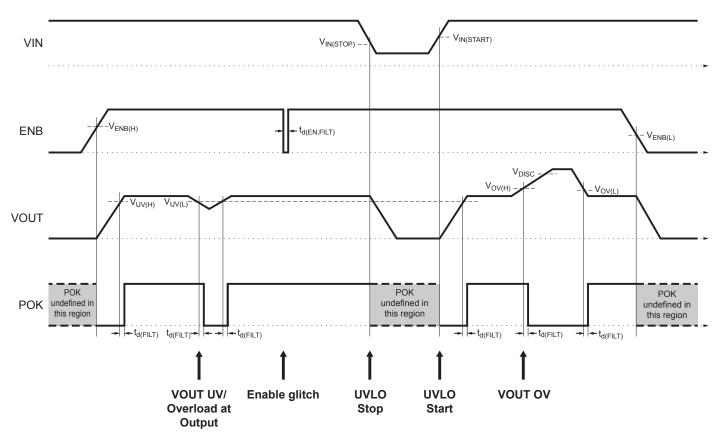

The A4481 has an enable (ENB) logic level input pin. To get the A4481 to operate, the ENB pin must be a logic high (>2 V). The ENB pin is rated to 50 V, allowing the ENB pin to be connected directly to VIN if there is no suitable logic signal available to wake up the A4481. When ENB transitions low, the A4481 waits approximately 15  $\mu$ s before shutting down. This delay provides plenty of filtering to prevent the A4481 from prematurely shutting down because of any small glitch coupling onto the PCB trace or ENB pin.

#### Power OK (POK) Output

The Power OK (POK) output is an open-drain output, so an external pull-up resistor must be connected. An internal comparator monitors the voltage at the VOUT pin and controls the open-drain device at the POK pin. POK is high when the voltage at the VOUT pin is within 10% of the final regulation voltage. The POK output is pulled low if: (1) the ENB pin transitions low, (2) UVLO occurs, (3) TSD occurs, or (4) UV/OVP occurs.

The following timing diagram shows the basic operation and fault handling of the A4481:

Figure 1: Timing Diagram (not to scale)

#### APPLICATION INFORMATION

#### **Capacitor Selection**

Output Capacitor ( $C_{OUT}$ ): The A4481 is designed to be stable with all types of output capacitors, but it must meet the minimum and maximum capacitance requirement of 3  $\mu$ F and 10  $\mu$ F at the intended operating temperature and working voltage. For a ceramic capacitor, X5R or X7R dielectrics with 10 V or higher voltage rating are recommended. However, if the part needs to survive short-to-battery events (e.g. to supply off-board sensors), then 50 to 100 V voltage-rated capacitors are recommended.

Input Capacitor ( $C_{IN}$ ): A 2.2  $\mu F$  or larger capacitor is recommended for an input bypass capacitor. Similarly, choose a capacitor that offers plenty of safety margins for known input voltage applications.

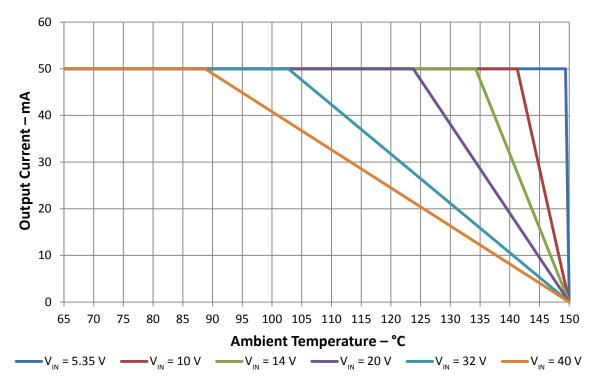

#### **Thermal Considerations**

The A4481 remains fully operational to 40 V. However, owing to power dissipation characteristics of the package, full output cur-

rent cannot be ensured for all combinations of ambient temperature and input voltage. The maximum allowable power dissipation in the IC is as follows:

$$P_{MAX} = \frac{(T_{J(MAX)} - T_A)}{R_{\theta JA}}$$

where  $T_{J(MAX)}$  = maximum junction temperature,  $T_A$  = ambient air temperature, and  $R_{\theta JA}$  thermal = resistance from junction to ambient. (35°C/W for the 8-pin eSOIC).

The power dissipated by the IC can be calculated according to the following equation:

$$P_{DISS} = (V_{IN} - V_{OUT}) \times I_{OUT} + V_{IN} \times I_{Q}$$

where  $V_{IN}$  = input voltage,  $V_{OUT}$  = output voltage,  $I_{OUT}$  = output current, and  $I_{O}$  = input quiescent current (3.4 mA typical).

Figure 2 shows current de-rating plot at selected input voltages based on the above calculations.

Figure 2: Output Current De-Rating vs. Input Voltage

1.508.853.5000; www.allegromicro.com

#### **PCB LAYOUT GUIDELINES**

Place the input and output capacitors as close as possible and on the same side of the PCB and IC.

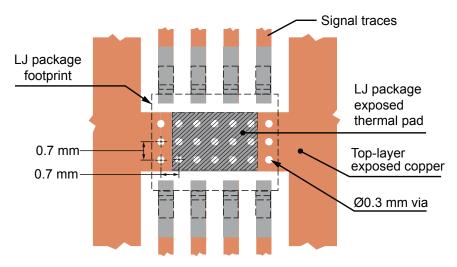

Place thermal vias directly under the device in a tight pattern, as shown in Figure 4, to improve dissipation.

Figure 3: A4481 Layout Example

Figure 4: Suggested PCB layout for thermal optimization (maximum available bottom-layer copper recommended)

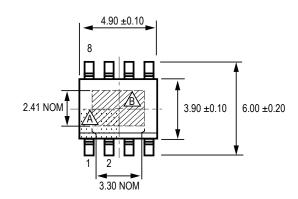

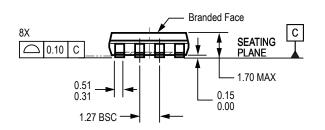

#### PACKAGE OUTLINE DRAWING

For Reference Only; not for tooling use (reference MS-012BA) Dimensions in millimeters

Dimensions exclusive of mold flash, gate burrs, and dambar protrusions Exact case and lead configuration at supplier discretion within limits shown

Terminal #1 mark area

Exposed thermal pad (bottom surface); dimensions may vary with device

Reference land pattern layout (reference IPC7351 SOIC127P600X175-9AM); all pads a minimum of 0.20 mm from all adjacent pads; adjust as necessary to meet application process requirements and PCB layout tolerances; when mounting on a multilayer PCB, thermal vias at the exposed thermal pad land can improve thermal dissipation (reference EIA/JEDEC Standard JESD51-5)

Figure 5: Package LJ, 8-Pin eSOIC

### A4481

# $5~V_{OUT}$ , 50~mA Automotive Linear Regulator with 50~V Load Dump and Short-to-Battery Protection

#### **Revision History**

| Number | Date            | Description                                                                          |  |

|--------|-----------------|--------------------------------------------------------------------------------------|--|

| _      | October 9, 2015 | Initial Release                                                                      |  |

| 1      | August 31, 2016 | Updated Foldback Current values (page 4) and Power OK (POK) Output section (page 6). |  |

Copyright ©2016, Allegro MicroSystems, LLC

Allegro MicroSystems, LLC reserves the right to make, from time to time, such departures from the detail specifications as may be required to permit improvements in the performance, reliability, or manufacturability of its products. Before placing an order, the user is cautioned to verify that the information being relied upon is current.

Allegro's products are not to be used in any devices or systems, including but not limited to life support devices or systems, in which a failure of Allegro's product can reasonably be expected to cause bodily harm.

The information included herein is believed to be accurate and reliable. However, Allegro MicroSystems, LLC assumes no responsibility for its use; nor for any infringement of patents or other rights of third parties which may result from its use.

For the latest version of this document, visit our website: www.allegromicro.com