## **Ultra Low Power 10/100 Ethernet Transceiver with Auto-MDIX**

#### DESCRIPTION

The AC101L is a single channel, low power, 10/100BASE-TX/FX transceiver. The AC101L transceiver has an integrated voltage regulator to allow operation from a single 3.3 V or 2.5 V supply source. The device contains a full-duplex 10BASE-T/100BASE-TX/100BASE-FX Fast Ethernet transceiver, which performs all of the physical layer interface functions.

The AC101L is a highly integrated solution combining an encoder/decoder, link monitor, auto-negotiation selection, parallel detection, adaptive equalization, clock/data recovery, baseline wander correction, multimode transmitter, scrambler/descrambler, far-end fault (FEF), and auto-MDI/MDIX circuitry. It is fully compliant with the IEEE802.3 and 802.3u standards.

#### **FEATURES**

- 3.3 V tolerant and 2.5 V capable

- Integrated voltage regulator to allow operation from a single 3.3 V or 2.5 V supply source

- 10/100 TX/FX

- Full-duplex or half-duplex

- FEFI on 100FX

- 48-pin TQFP

- Industrial temperature (-40°C to +85°C)

- 0.25 μm CMOS

- Fully compliant with IEEE 802.3/802.3u

- MII/RMII interface

- · Baseline wander correction

- Multifunction LED outputs

- Cable length indicator

- HP auto-MDI/MDIX

- Eight programmable interrupts

- · Diagnostic registers

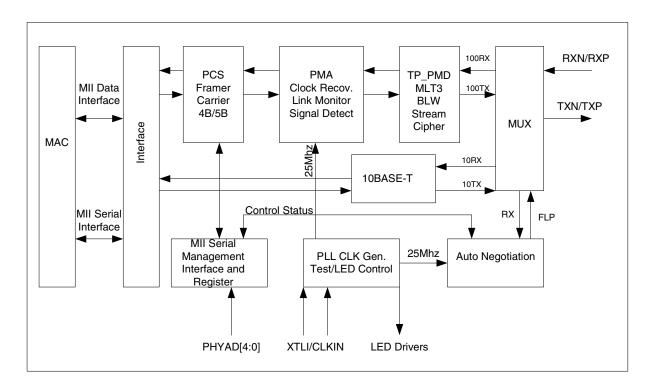

Figure 1: AC101L functional block diagram

#### **REVISION HISTORY**

| Revision #    | Date     | Change Description                                                                                         |

|---------------|----------|------------------------------------------------------------------------------------------------------------|

| AC101L-DS02-R | 06/06/02 | <ul> <li>Added table showing current requirements at 2.5 V operation with<br/>LED disabled.</li> </ul>     |

|               |          | <ul> <li>Added table showing current requirements at 3.3 V operation with<br/>LED disabled.</li> </ul>     |

|               |          | <ul> <li>Added output voltage high values and output voltage low values (all<br/>digital pins).</li> </ul> |

|               |          | Added input voltage high and low values (all digital input pins).                                          |

| AC101L-DS01-R | 02/20/02 | Updated FX application figure and Power and ground filtering figure.                                       |

| AC101L-DS00-R | 01/02/02 | Initial release.                                                                                           |

Broadcom Corporation

P.O. Box 57013

16215 Alton Parkway

Irvine, California 92619-7013

© Copyright 2001 by Broadcom Corporation

All rights reserved

Printed in the U.S.A.

Broadcom<sup>®</sup> and the pulse logo<sup>®</sup> are trademarks of Broadcom Corporation and/or its subsidiaries in the United States and certain other countries. All other trademarks are the property of their respective owners.

## **C**ONTENTS

| Section 1: Functional Description   | 1   |

|-------------------------------------|-----|

| Encoder/Decoder                     |     |

| Link monitor                        |     |

| Carrier sense (CRS)/RXDV            |     |

| Collision detection                 |     |

| Auto-Negotiation                    |     |

| Parallel detection                  |     |

| Analog adaptive equalizer           |     |

| Clock recovery                      |     |

| Baseline wander correction          |     |

| Multimode transmitter               |     |

| Stream cipher scrambler/descrambler |     |

| FEF (far-end fault)                 |     |

| Transmit driver                     |     |

| HP auto-MDI/MDIX                    |     |

| MAC interface                       |     |

| MII                                 |     |

| RMII                                |     |

| SMI                                 | 6   |

| Physical layer interfaces           |     |

|                                     |     |

| Section 2: Pin Descriptions         | 7   |

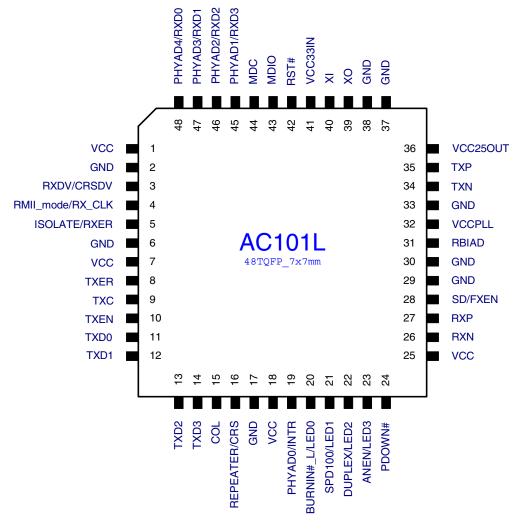

| Section 3: Pinout Diagram           | 11  |

| Ocation 4: One wational December    | 4.0 |

| Section 4: Operational Description  |     |

| Reset                               |     |

| Power source                        |     |

| Power saving mode                   | 13  |

| Clock source                        | 13  |

| Isolate mode                        | 14  |

| Loopback mode                       | 14  |

| Interrupt mode                      | 14  |

| LED operation                       | 14  |

| LED interface                                                                             | 14 |

|-------------------------------------------------------------------------------------------|----|

| LED configuration                                                                         | 15 |

| LED [3:0] event table                                                                     | 15 |

| Section 5: Register Description                                                           | 17 |

| TP PHY register summary                                                                   | 17 |

| Register 0: Control register                                                              | 18 |

| Register 1: Status register                                                               | 18 |

| Register 2: PHY Identifier 1 register                                                     | 19 |

| Register 3: PHY Identifier 2 register                                                     | 20 |

| Register 4: Auto-Negotiation Advertisement register                                       | 20 |

| Register 5: Auto-Negotiation Link Partner Ability register/Link Partner Next Page message | 21 |

| Register 6: Auto-Negotiation Expansion register                                           | 21 |

| Register 7: Auto-Negotiation Next Page Transmit register                                  | 22 |

| Register 16: BT and Interrupt Level Control register                                      | 22 |

| Register 17: Interrupt Control/Status register                                            | 23 |

| Register 18: Diagnostic register                                                          | 23 |

| Register 19: Power/Loopback register                                                      | 24 |

| Register 20: Cable Measurement Capability register                                        | 24 |

| Register 21: Receive Error Counter                                                        | 24 |

| Register 22: Power Management register                                                    | 25 |

| Register 23: Operation Mode register                                                      | 25 |

| Register 24: CRC for Recent Received Packet                                               | 26 |

| Common registers                                                                          | 26 |

| Common Register 0 (Map to Reg. 28) Mode Control register                                  | 26 |

| Common Register 1: (Map to Reg. 29, Page 0 a28.[15:12]=0000) Test Mode register           | 27 |

| Common Register 4: (Map to Reg. 29, Page 1 a28.[15:12]=0001) LED Blink Rate               | 27 |

| Common Register 5: (Map to Reg. 30, Page 1 a.28.[15:12]=0001) LED0 Setting1 register      | 27 |

| Common Register 6: (Map to Reg. 31, Page 1 a.28.[15:12]=0001) LED0 Setting2 register      | 28 |

| Common Register 7: (Map to Reg. 29, Page 2 a.28.[15:12]=0010) LED1 Setting1 register      | 28 |

| Common Register 8: (Map to Reg. 30, Page 2 a.28.[15:12]=0010) LED1 Setting2 register      | 28 |

| Common Register 9: (Map to Reg. 31, Page 2 a.28.[15:12]=0010) LED2 Setting1 register      | 29 |

| Common Register 10: (Map to Reg. 29, Page 3 a.28.[15:12]=0011) LED2 Setting2 register     | 29 |

| Common Register 11: (Map to Reg. 30, Page 3 a.28[.15:12]=0011) LED3 Setting1 register     | 29 |

| Common Register 12: (Map to Reg. 31, Page 3 a.28.[15:12]=0011) LED3 Setting2 register     | 30 |

| Section 6: 4B/5B Code Group               | 31 |

|-------------------------------------------|----|

| Section 7: SMI Read/Write Sequence        | 33 |

| Section 8: Timing and AC Characteristics  | 35 |

| Clock timing                              | 35 |

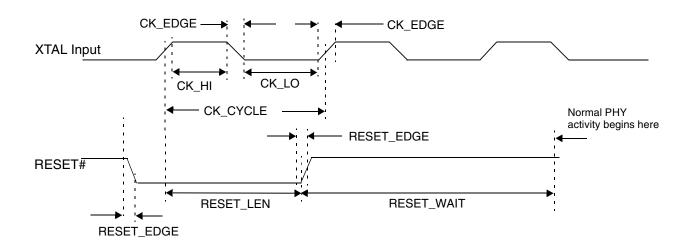

| Reset timing                              | 35 |

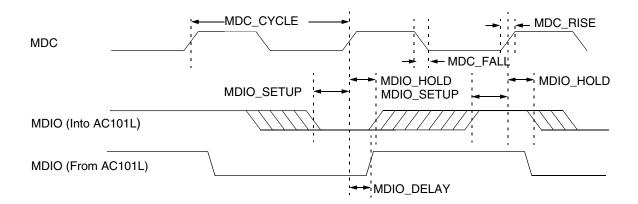

| Management Data Interface timing          | 36 |

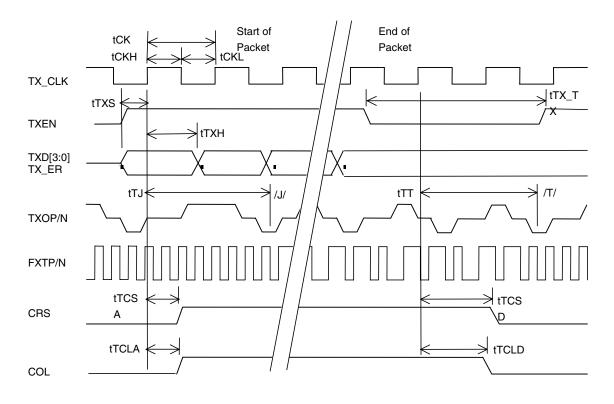

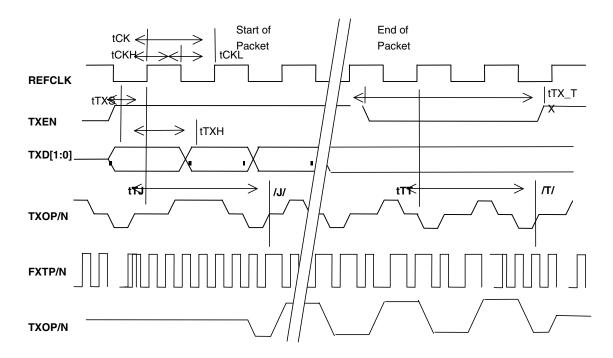

| 100BASE-TX/FX MII transmit system timing  | 37 |

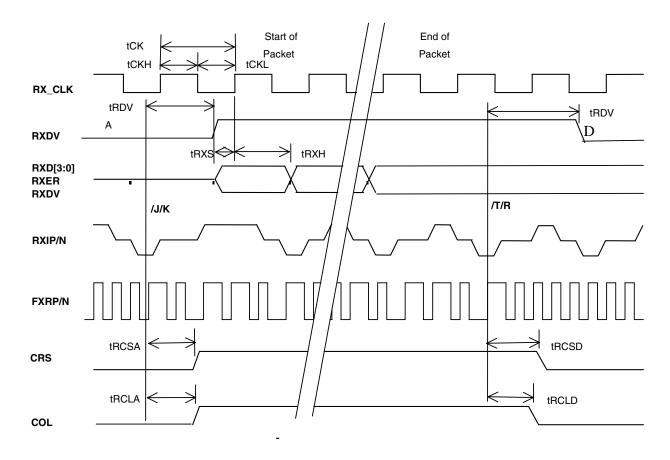

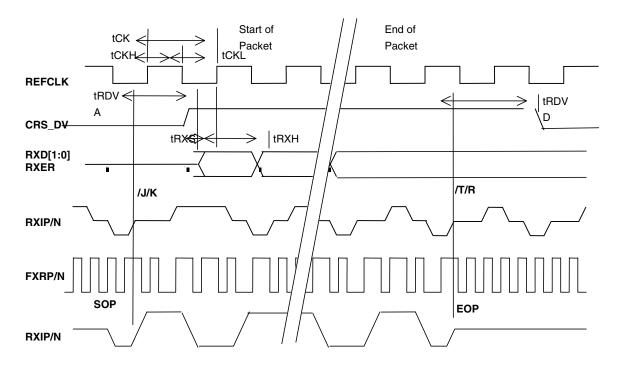

| 100BASE-TX/FX MII receive system timing   | 38 |

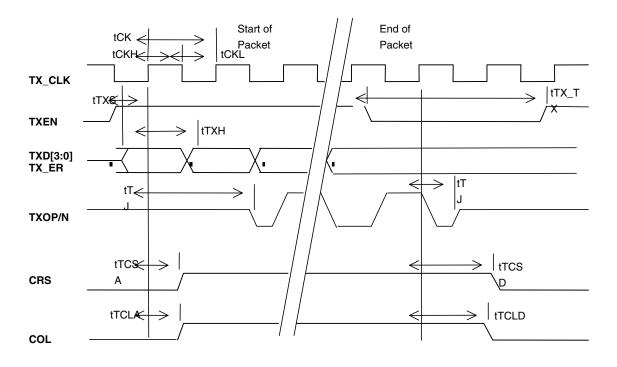

| 10BASE-T MII transmit system timing       | 39 |

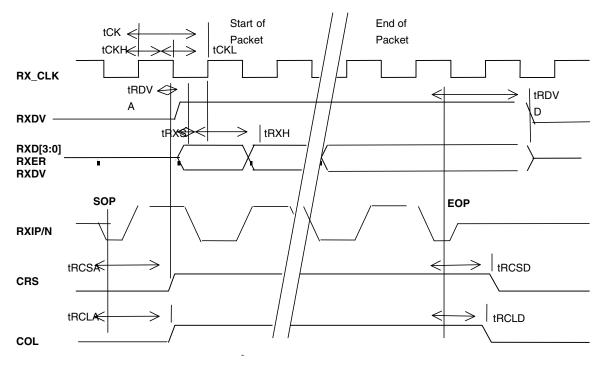

| 10BASE-T MII receive system timing        | 40 |

| RMII transmit timing                      | 41 |

| RMII receive timing                       | 42 |

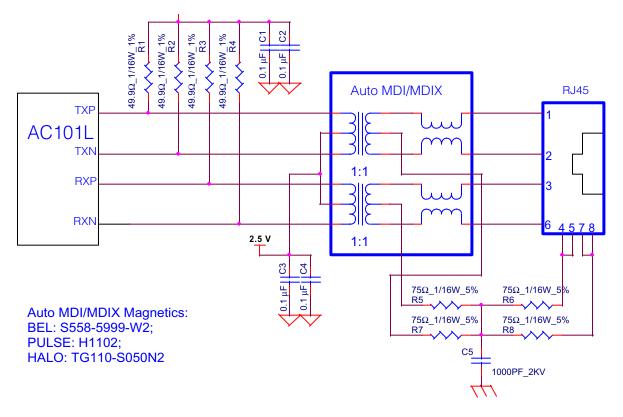

| Copper application termination            | 43 |

| Section 9: Electrical Characteristics     | 45 |

| Absolute maximum ratings                  | 45 |

| Recommended operating conditions          | 46 |

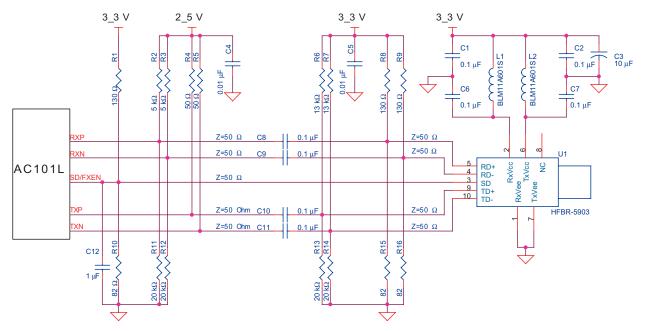

| Section 10: Fiber Application Termination | 47 |

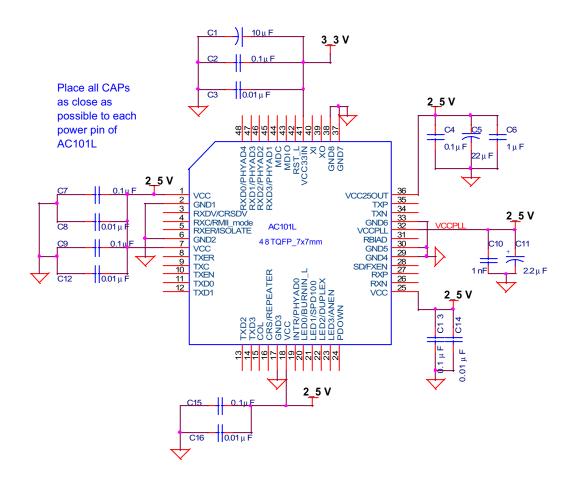

| Section 11: Power and Ground Filtering    | 49 |

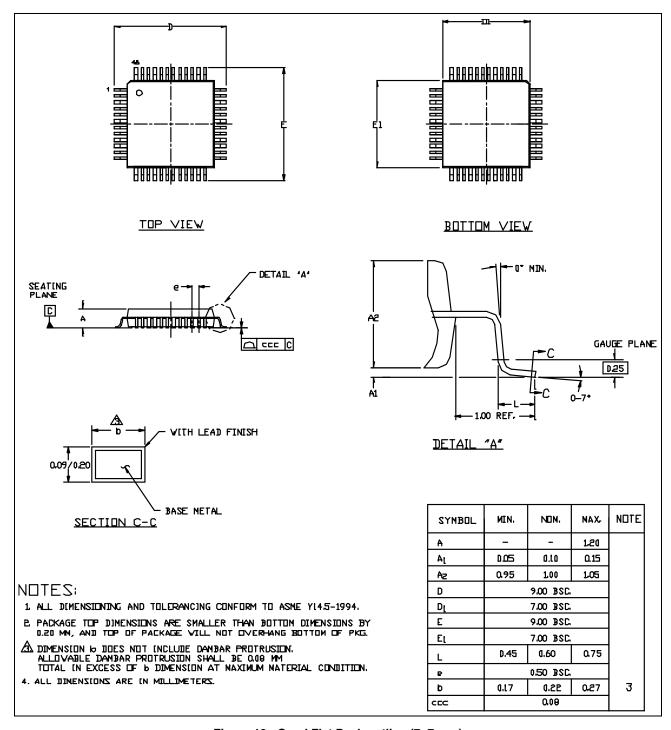

| Section 12: Mechanical Information        | 51 |

| Section 13: Thermal Parameters            | 53 |

| Section 14: Ordering Information          | 55 |

06/06/02

## **FIGURES**

| Figure 1: AC101L functional block diagram   | i  |

|---------------------------------------------|----|

| Figure 1: AC101L pinout diagram             | 11 |

| Figure 2: Reset timing                      | 35 |

| Figure 3: Management interface timing       | 36 |

| Figure 4: 100BASE-TX/FX MII transmit timing | 37 |

| Figure 5: 100BASE-T MII receive timing      | 38 |

| Figure 6: 10BASE-T transmit timing          | 39 |

| Figure 7: 10BASE-T Receive Timing           | 40 |

| Figure 8: RMII transmit timing              | 41 |

| Figure 9: RMII receive timing               | 42 |

| Figure 10: TX application                   | 43 |

| Figure 11: FX application                   | 47 |

| Figure 12: Power and ground filtering       | 49 |

| Figure 13: Quad Flat Pack outline (7×7 mm)  | 51 |

06/06/02

## **TABLES**

| Table 2: Pinout and signal definitions                                                              | 7    |

|-----------------------------------------------------------------------------------------------------|------|

| Table 3: LED [3:0] event table                                                                      | . 15 |

| Table 4: TP PHY register summary                                                                    | . 17 |

| Table 5: Register 0: Control register                                                               | 18   |

| Table 6: Register 1: Status register                                                                | . 18 |

| Table 7: Register 2: PHY Identifier 1 register                                                      | .19  |

| Table 8: Register 3: PHY Identifier 2 register                                                      | 20   |

| Table 9: Register 4: Auto-Negotiation Advertisement register                                        | 20   |

| Table 10: Register 5: Auto-Negotiation Link Partner Ability register/Link partner Next Page message | . 21 |

| Table 11: Register 6: Auto-Negotiation Expansion register                                           | . 21 |

| Table 12: Register 7: Auto-Negotiation Next Page Transmit register                                  | . 22 |

| Table 13: Register 16: BT and Interrupt Level Control register                                      | 22   |

| Table 14: Register 17: Interrupt Control/Status register                                            | 23   |

| Table 15: Register 18: Diagnostic register                                                          | 23   |

| Table 16: Register 19: Power/Loopback register                                                      | 24   |

| Table 17: Register 20: Cable Measurement Capability register                                        | 24   |

| Table 18: Register 21: Receive Error Counter                                                        | 24   |

| Table 19: Register 22: Power Management register                                                    | . 25 |

| Table 20: Register 23: Operation Mode register                                                      | 25   |

| Table 21: Register 24: CRC for Recent Received Packet                                               | 26   |

| Table 22: Common Register 0 (Map to Reg. 28) Mode Control register                                  | 26   |

| Table 23: Common Register 1: (Map to Reg. 29, Page 0 a28.[15:12]=0000) Test Mode register           | 27   |

| Table 24: Common Register 4: (Map to Reg. 29, Page 1 a28.[15:12]=0001) LED Blink Rate               | . 27 |

| Table 25: Common Register 5: (Map to Reg. 30, Page 1 a.28.[15:12]=0001) LED0 Setting1 Register      | . 27 |

| Table 26: Common Register 6: (Map to Reg. 31, Page 1 a.28.[15:12]=0001) LED0 Setting2 register      | 28   |

| Table 27: Common Register 7: (Map to Reg. 29, Page 2 a.28.[15:12]=0010) LED1 Setting1 register      | 28   |

| Table 28: Common Register 8: (Map to Reg. 30, Page 2 a.28.[15:12]=0010) LED1 Setting2 register      | 28   |

| Table 29: Common Register 9: (Map to Reg. 31, Page 2 a.28.[15:12]=0010) LED2 Setting1 register      | 29   |

| Table 30: Common Register 10: (Map to Reg. 29, Page 3 a.28.[15:12]=0011) LED2 Setting2 register     | 29   |

| Table 31: Common Register 11: (Map to Reg. 30, Page 3 a.28[.15:12]=0011) LED3 Setting1 register     | 29   |

| Table 32: Common Register 12: (Map to Reg. 31, Page 3 a.28.[15:12]=0011) LED3 Setting2 register     | 30   |

| Table 33: 4B/5B code group                                                                          | 31   |

| Table 34: SMI read/write sequence                                  | 33 |

|--------------------------------------------------------------------|----|

| Table 35: Clock timing                                             | 35 |

| Table 36: Reset Timing                                             | 35 |

| Table 37: Management Interface Timing                              | 36 |

| Table 38: 100BASE-X MII transmit system timing                     | 37 |

| Table 39: 100BASE-TX/FX MII receive system timing                  | 38 |

| Table 40: 10BASE-T MII transmit system timing                      | 39 |

| Table 41: 10BASE-T MII receive system timing                       | 40 |

| Table 42: RMII transmit timing                                     | 41 |

| Table 43: RMII receive timing                                      | 42 |

| Table 44: Absolute maximum ratings                                 | 45 |

| Table 45: Current requirement at 2.5 V operation with LED disabled | 45 |

| Table 46: Current requirement at 3.3 V operation with LED disabled | 45 |

| Table 47: Recommended operating conditions                         | 46 |

| Table 48: Thermal parameters                                       | 53 |

Page 1

06/06/02 Functional Description

## **Section 1: Functional Description**

The AC101L is a single-chip, Fast Ethernet transceiver. It performs all of the physical layer interface functions for 100BASE-TX full-duplex or half-duplex on Category 5 twisted-pair cable, and 10BASE-T full-duplex or half-duplex on Category 3 cable. It can be configure for 100BASE-FX full- or half-duplex transmission over fiber optic cable when pair with an external fiber optic line driver and receiver.

The chip performs 4B5B, MLT3, NRZI, encoder/decoder, link monitor, auto-negotiation selection, adaptive equalization, clock/data recovery, baseline wander correction, multimode transmitter, scrambler/descrambler, far-end fault (FEF), and auto-MDI/MDIX. It can be connected to a MAC switch controller through the MII on one side, and connects directly to the media on the other side through a transformer for twisted-pair (TP) mode, or fiber-optic module for FX mode. It is fully compliant with the IEEE 802.3 and 803.3u standards.

#### **ENCODER/DECODER**

In 100BASE-TX and 100BASE-FX modes, the AC101L transmits and receives data stream on twisted-pair or fiber-optic cable. When the MII transmit enable is asserted, nibble wide (4 bit) data from transmit data pins is encoded into 5-bit code groups and inserted into transmit data stream. The 4B5B encoding is shown in Section 6: "4B/5B Code Group" on page 31. The transmit packet is encapsulated by replacing the first 2 nibbles of preamble with a start of stream delimiter (J/K codes) and appending an end of stream delimiter (T/R codes) to the end of packet. When the MII transmit error input is asserted during a packet, the error code group (H) is sent in place of the corresponding data code group. The transmitter sends repeatedly the idle code group between packets.

In 100BASE-TX mode, the encode data stream is scrambled by a stream cipher block and then serialized and encoded into an MLT3 signal level. A multi mode transmit DAC (digital to analog converter) is used to drive the MLT3 data onto twisted-pair cable. Following are baseline wander correction, adaptive equalization and clock/data recovery in 100BASE-TX mode, the receive data stream is converted from MLT3 to serial NRZ data. The NRZ data is descrambled by the stream cipher block and then deserialized and aligned into 5-bit code groups.

In 100BASE-FX mode, the scrambling function is bypassed and the data is NRZII encoded. The multi mode transmit DAC drives differential Positive ECL (PECL) levels to an external fiber optic transmitter. Baseline wander correction, adaptive equalization, stream cipher descrambling functions are bypass and NRZI decoding is used instead of MLT3.

The 5-bit code groups are decoded into 4 bit data nibbles. The start of stream delimiter is replaced with preamble nibbles and the end of stream delimiter and idle codes are replaced with all zeros. The decoded data is driven onto the MII receive data pins. When an invalid code group or bad SSD is detected in the data stream, the AC101L asserts the MII RXER signal.

In 10BASE-T mode, Manchester encoding and decoding is performed on the data stream. The multi mode transmit DAC performs pre-equalization for 100 meters of Category 3 cable.

#### **LINK MONITOR**

In 100BASE-TX mode, receive signal energy is detected by monitoring the receive pair for transitions in the signal level. The signal levels are qualified using squelch detect circuits. When no signal or certain valid signal is detected on the receive pair for a minimum period of time, the link monitor enter the link pass state and the transmit and receive functions are enabled.

In 100BASE-FX mode, the external fiber-optic receiver performs the signal energy detection function and communicates this information directly to the SD signal (PIN 28).

In 10BASE-T mode, a link pulse detection circuit constantly monitors the RXP/RXN pins for the present of valid link pulses.

## CARRIER SENSE (CRS)/RXDV

Carrier sense is asserted asynchronously on the CRS pins as soon as activity is detected on the receive data stream. RXDV is asserted as soon as a valid SSD (Start-of-Stream Delimiter) is detected. Carrier sense and RXDV are de-asserted synchronously upon detection of a valid end of stream delimiter or two consecutive idle code groups in the receive data stream. However, if the carrier sense is asserted and a valid SSD is not detected immediately, RXER is asserted instead of RXDV.

In 10BASE-T mode, CRS is asserted asynchronously when the valid preamble and data activity is detected on the RXIP and RXIN pins.

In the half-duplex mode, the CRS is activated during data transmit. In the full-duplex mode, the CRS is activated during data receiving only.

#### **COLLISION DETECTION**

In half-duplex mode, collision detect is asserted on the COL pin whenever carrier sense is asserted and transmission is in progress.

#### **AUTO-NEGOTIATION**

Auto-negotiation selection is on 100BASE twisted-pair PHY only; it is not operating in 100BASE fiber PHY.

In 100BASE-TX mode, auto-negotiation can be enabled or disabled by hardware or software control. When auto-negotiation function is enable, the 100BASE-TX PHY automatically chooses its mode of operation by advertising its abilities and comparing them with those received from it's link partner. 100BASE-TX PHY can be configured to advertise 100BASE-TX full-duplex or 100BASE-TX half-duplex.

The default auto-negotiation mode is configured via reset read value of ANEN/LED3 signal (pin 23) and SPD100/LED1.

#### Table 1:

| 0.13     | Speed Select           | The default value is: SPD100                                                         |

|----------|------------------------|--------------------------------------------------------------------------------------|

| 0.12     | ANEN Enable            | <ul><li>1 = Enable Auto-negotiation.</li><li>0 = Disable Auto-negotiation.</li></ul> |

| 0.8      | Duplex                 | The default value is:<br>!ANEN && DUPLEX                                             |

| 4.8/1.14 | 100BASE-TX Full-Duplex | The default value of this bit is: SPD100 && DUPLEX                                   |

| 4.7/1.13 | 100BASE-TX             | The default value is:<br>SPD100 && (ANEN    !DUPLEX)                                 |

| 4.6/1.12 | 10BASE-T Full-Duplex   | The default value of this bit is: DUPLEX && (ANEN    ISPD100)                        |

| 4.5/1.11 | 10BASE-T               | The default value is: ANEN    (ISPD100 && IDUPLEX)                                   |

06/06/02 Functional Description

#### PARALLEL DETECTION

Because there are many devices in the field that do not support the ANEN process, but must still be communicated with, it is necessary to detect and link through the parallel detection process. The parallel detection circuit is enabled in the absence of FLPs. The circuit is able to detect the following:

- Normal link pulse (NLP)

- 10BASE-T receive data

- 100BASE-TX idle

The mode of operation gets configured based on the technology of the incoming signal. If any of the above is detected, the device automatically configures to match the detected operating speed in the half-duplex mode. This ability allows the device to communicate with the legacy 10BASE-T and 100BASE-TX systems, while maintaining the flexibility of auto-negotiation.

### **ANALOG ADAPTIVE EQUALIZER**

The analog adaptive equalizer removes Inter Symbol Interference (ISI) created by the transmission channel media.

The PHY is designed to accommodate a maximum of 140 meters of UTP Category 5 cable. An AT&T 1061 Category 5 cable of this length typically has an attenuation of 31 dB at 100 MHz. A typical attenuation of 100-meter cable is 21 dB. The worst case cable attenuation is around 24–26 dB as defined by TP-PMD specification. The amplitude and phase distortion from the cable causes ISI which makes clock and data recovery difficult. The adaptive equalizer is designed to closely match the inverse transfer function of the twisted-pair cable. The equalizer has the ability to changes its equalizer frequency response according to the cable length. The equalizer will tune itself automatically for any cable, compensating for the amplitude and phase distortion introduced by the cable.

#### **CLOCK RECOVERY**

The equalized MLT3 signal passes through the slicer circuit, and gets converted to NRZI format. The PHY uses a proprietary mixed-signal Phase Locked Loop (PLL) to extract clock information from the incoming NRZI data. The extracted clock is used to re-time the data stream and set the data boundaries. The transmit clock is locked to the 25 MHz clock input while the receive clock is locked to the incoming data streams. When initial lock is achieved, the PLL switches to the data stream, extracts the 125 MHz clock, and uses it for the bit framing for the recovered data. The recovered 125 MHz clock is also used to generate the 25 MHz RX\_CLK signal. The PLL requires no external components for its operation and has high noise immunity and low jitter. It provides fast phase alignment and locks to data in one transition. Its data/clock acquisition time, after power-on, is less than 60 transitions. The PLL can maintain lock on run-lengths of up to 60 data bits in the absence of signal transitions. When no valid data is present (that is, when the SD is deasserted), the PLL switches and locks on to TX\_CLK. This provides a continuously running RX\_CLK. At the PCS interface, the 5-bit data RXD[4:0] is synchronized to the 25 MHz RX\_CLK.

#### **BASELINE WANDER CORRECTION**

A 100BASE-TX data stream is not always DC balanced. Because the receive signal must pass through a transformer, the DC offset of the differential receive input can wander. This effect, known as baseline wander, can greatly reduce the noise immunity of the receiver. The 100BASE-TX PHY automatically compensates for baseline wander by removing the DC offset from the input signal, and thereby significantly reduces the chance of a receive symbol error.

The baseline wander circuit is not required in 100BASE-FX PHY operation.

Document AC101L-DS02-R Page 3

#### **MULTIMODE TRANSMITTER**

The multimode transmitter transmits MLT3 coded symbols in 100BASE-TX mode, and NRZI coded symbols in 100BASE-FX mode. It utilizes a current drive output, which is well balanced and produces very low noise transmit signals. PECL voltage levels are produced with resistive terminations in 100BASE-FX mode.

The serialized data bypasses the scrambler and 4B/5B encoder in FX mode. The output data is NRZI PECL signals. The PECL level signals are used to drive the fiber-optic transmitter.

### STREAM CIPHER SCRAMBLER/DESCRAMBLER

In 100BASE-TX mode, the transmit data stream is scrambled to reduce radiated emissions on the twisted-pair cable. The data is scrambled by exclusive ORing the NRZ signal with the output of an 11-bit wide Linear Feedback Shift register (LFSR), which produces a 2047 bit nonrepeating sequence. The scrambler reduces peak emission by randomly spreading the signal energy over the transmit frequency range and eliminating peaks at certain frequencies.

The receiver descrambles the incoming data stream by exclusive ORing it with the same sequence generated at the transmitter. The descrambler detects the state of the transmit LFSR by looking for a sequence representing consecutive idle codes. The descrambler locks to the scrambler state after detecting a sufficient number of consecutive idle code group.

The receiver does not attempt to decode the data stream unless the descrambler is locked. When locked, the descrambler continuously monitors the data stream to make sure that it has not lost synchronization.

The receive data stream is expected to contain inter-packet idle periods. If the descrambler does not detect enough idle code within 724  $\mu$ s, it becomes unlocked and the receive decoder is disabled. The descrambler is always forced into the unlock state when a link failure condition is detected.

Stream cipher descrambler is not used in the 100BASE-FX mode.

## FEF (FAR-END FAULT)

Auto-negotiation provides the mechanism to inform the link partner that a remote fault has occurred. Auto-negotiation is disabled, however, in the 100BASE-FX applications. An alternative in-band signaling function (FEFI) is used to signal a remote fault condition.

FEFI is a stream of 84 consecutive ones followed by one logic zero. This pattern is repeated three times.

An FEFI signal is given under three conditions:

- When no activity is received from the link partner,

- When the clock recovery circuit detects a signal error or PLL lock error,

- When a management entity sets the Transmit Far-End Fault bit.

The FEFI mechanism is enabled by default in the 100BASE-FX mode, and is disabled in 100BASE-TX or 10BASE-T modes. The register setting can be changed by software after reset.

06/06/02 Functional Description

#### TRANSMIT DRIVER

In 100BASE-TX mode, the PHY transmit function converts synchronous 4-bit data nibbles from the MII to a pair of 125 Mbps differential serial data streams. The serial data is transmitted over network twisted-pair cables via an isolation transformer. Data conversion includes 4B/5B encoding, scrambling, parallel-to-serial, NRZ to NRZI, and MLT3 encoding. The entire operation is synchronous to the 25 MHz and 125 MHz clocks. Both clocks are generated by an on-chip PLL clock synthesizer that is locked on to an external 25 MHz clock source.

In 100BASE-FX, the transmit driver does not perform filtering; it utilizes a current drive output that is well balanced and produces a low noise PECL signal. PECL voltage levels are produced with resistive terminations.

In 10BASE-T mode, if the MII interface is used, parallel-to-serial logic is used to convert the 4-bit data into the serial stream through the output wave shaping driver. The wave shaper reduces any EMI emission by filtering out the harmonics, therefore eliminating the need for an external filter.

#### HP AUTO-MDI/MDIX

This feature is able to detect the required cable connection type (straight through or crossed over) and make correction automatically.

#### **MAC** INTERFACE

#### MII

The Media Independent Interface (MII) is an 18-wire MAC/PHY interface described in IEEE 802.3u. The purpose of the interface is to allow MAC layer devices to attach to a variety of physical layer devices through a common interface. MII operates at either 100 Mbps or 10 Mbps, depending on the speed of the physical layer. With clocks running at either 25 MHz or 2.5 MHz, 4-bit data is clocked between the MAC and PHY, synchronously with Enable and Error signals.

At the time of PLL lock on an incoming signal from the wire interface, the PHY generates RX\_CLK at either 2.5 MHz for 10 Mbps or 25 MHz for 100 Mbps.

On receipt of valid data from the wire interface, RXDV goes active signaling the MAC that valid data will be presented on the RXD[3:0] pins at the speed of the RX\_CLK.

On transmission of data from the MAC, TXEN is presented to the PHY, indicating the presence of valid data on TXD[3:0]. TXD[3:0] are sampled by the PHY( synchronous to TX\_CLK) during the time that TXEN is valid.

#### **RMII**

The Reduced Media Independent Interface (RMII) is used to connect the PHY with the MAC. The PHY and MAC obtain their clock timing from a common 50 MHz source, such as a clock oscillator. This clock is shared by all ports within the PHY for transmitting and receiving data on two individual 2-bit data buses. CRS and RXDV are multiplexed to indicate to the MAC when there is valid data on the receive bus. In 100 Mbps mode, RXD[1:0] is sampled on every cycle of REFCLK. In 10 Mbps mode, RXD[1:0] is sampled on every 10<sup>th</sup> cycle of REFCLK. RXER is generated by the PHY to indicate a receive error to the MAC. TXEN is generated by the MAC to indicate to the PHY when there is valid data on the transmit bus. In 100 Mbps mode the PHY reads 2 bits from TXD[1:0] for each cycle of REFCLK. In 10 Mbps mode, the PHY reads 2 bits of data from TXD[1:0] every 10<sup>th</sup> cycle of REFCLK.

Physical layer interfaces 06/06/02

#### SMI

The PHYs internal registers are accessible only through the MII 2-wire Serial Management Interface (SMI). MDC is a clock input to the PHY, which is used to latch in or out data and instructions for the PHY. The clock can run at any speed from DC to 25 MHz. MDIO is a bidirectional connection used to write instructions to, write data to, or read data from the PHY. Each data bit is latched either in or out on the rising edge of the MDC. The MDC is not required to maintain any speed or duty cycle, provided no half cycle is less than 20 ns, and that data is presented synchronous to the MDC.

MDC/MDIO are a common signal pair to all PHYs on a design. Therefore, each PHY needs to have its own unique physical address. The physical address of the PHY is set using the pins defined as PHYAD[4:0]. These input signals are strapped externally, and are sampled as reset is negated. At idle, the PHY is responsible to pull the MDIO line to a high state. Therefore, a  $1.5 \text{ k}\Omega$  resistor is required to connect the MDIO line to VCC.

## PHYSICAL LAYER INTERFACES

The two supported interfaces are the twisted-pair (TP) interface with auto-MDI/MDIX selection, and the fiber-optic Interface with PECL signaling.

The selection of these two interfaces is performed at reset time by the SD/FXEN signal (pin 28). Pull pin 28 LOW to enable the TP interface, or connect pin 28 to the fiber module to enable FX interface.

06/06/02 Pin Descriptions

## **Section 2: Pin Descriptions**

Many of the pin have multiple functions. The multifunction pins are designated by bold style of the pin number. The separate descriptions of these pins are listed in the proper sections. Designers must assure that they have identified all modes of operation prior to final design.

#### Signal types:

- B = Bidirection pin

- P = Power pin

- G = Ground pin

- AI = Analog Input pin

- AO = Analog output pin

- D = Digital pull-down pin

- U = Digital pull-up pin

- # = Active low

All digital pins are bidirectional pins.

Table 2: Pinout and signal definitions

| PIN # | PIN name             | Type           | Description                                                                                                                                                                                                                                                                                                                                                                       |

|-------|----------------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | VCC                  | Р              | +2.5 V power supply.                                                                                                                                                                                                                                                                                                                                                              |

| 2     | GND                  | G              | Ground                                                                                                                                                                                                                                                                                                                                                                            |

| 2     | GND                  | G              | Ground                                                                                                                                                                                                                                                                                                                                                                            |

| 3     | RXDV/CRSDV           | B <sub>D</sub> | RXDV (active HIGH output): Receive Data Valid is the output signal in the MII mode. RXDV is active HIGH to indicate that the receive frame is in progress, and that the data stream present on the RXD output pins is valid.  CRSDV (active HIGH output): Carrier Sense/Data Valid is the output signal in the RMII mode. The CRSDV pin is asserted high when media are non-idle. |

| 4     | RMII_mode/<br>RX_CLK | B <sub>D</sub> | RMII_mode (resets read input): Pull HIGH to configure the chip into RMII mode. Default is in MII mode. RX_CLK (Out put): Receive clock in MII mode. RX_CLK is 25 MHz out put in 100BASE and 2.5 MHz output in 10BASE. This clock is recovered from the incoming data on the cable inputs.                                                                                         |

| 5     | ISOLATE/RXER         | B <sub>D</sub> | ISOLATE (resets read Input): Pull HIGH to isolate the PHY from the MII. The MII output pins are high impedance. The MII input pins still respond to data. This allows multiple PHY to be attached to the same MII interface.  RXER (active HIGH output): asserted to indicate that an invalid symbol or bad SSD is detected in both the RMII and MII modes.                       |

| 6     | GND                  | G              | Ground                                                                                                                                                                                                                                                                                                                                                                            |

| 7     | VCC                  | Р              | +2.5 V power supply.                                                                                                                                                                                                                                                                                                                                                              |

| 8     | TXER                 | B <sub>D</sub> | TXER (active HIGH input): Transmits an error in the MII interface. When TXER is asserted for one or more TX_CLK periods while TXEN is also asserted, the PHY emits one or more symbols that are not part of the valid data or delimiter set somewhere in the frame being transmitted. The relative position of the error within the frame need not be preserved.                  |

| 9     | TX_CLK               | B <sub>D</sub> | TX_CLK (output): Transmits the clock signal of the MII mode. TX_CLK is 25 MHz output in 100BASE operation and 2.5 MHz in 10BASE operation. This clock is a continuously-driven output, generated from the XI (crystal input) pin.                                                                                                                                                 |

| 10    | TXEN                 | B <sub>D</sub> | TXEN (active HIGH input): Transmits the Enable signal in the RMII and MII interfaces. TXEN is asserted by the MAC to indicate that valid data is present on TXD[3:0].                                                                                                                                                                                                             |

| 11    | TXD0                 | B <sub>D</sub> | TXD0: Transmits data input for the MII and RMII interfaces.                                                                                                                                                                                                                                                                                                                       |

Document AC101L-DS02-R Page 7

## Table 2: Pinout and signal definitions (Cont.)

| PIN# | PIN name      | Туре           | Description                                                                                                                                                                                                                                                                                                                                                      |

|------|---------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12   | TXD1          | B <sub>D</sub> | TXD1: Transmits data input for MII and RMII interfaces.                                                                                                                                                                                                                                                                                                          |

| 13   | TXD2          | B <sub>D</sub> | TXD2: Transmits data input for MII interface.                                                                                                                                                                                                                                                                                                                    |

| 14   | TXD3          | B <sub>D</sub> | TXD3: Transmits data input for MII interface.                                                                                                                                                                                                                                                                                                                    |

| 15   | COL           | B <sub>D</sub> | COL (active HIGH output): Is the collision detect signal in the MII interface. In half-duplex mode, COL active high output indicates that a collision has occurred. In full-duplex mode, COL remains low.                                                                                                                                                        |

| 16   | REPEATER/ CRS | B <sub>D</sub> | REPEATER: Resets read input. Active high puts the chip in repeater mode.  CRS (active HIGH output): Carrier sense signal in the MII interface. CRS is asserted when the twisted-pair media is non-idle and is deasserted when idle or a valid end-of-stream delimiter is detected.                                                                               |

| 17   | GND           | G              | Ground                                                                                                                                                                                                                                                                                                                                                           |

| 18   | VCC           | Р              | +2.5 V power supply.                                                                                                                                                                                                                                                                                                                                             |

| 19   | PHYAD0/INTR   | B <sub>U</sub> | PHYAD0: Resets read Input. Pull high or low to set the PHY Address bit 0 for the MII/RMII management function.  INTR (output): interrupt output enable. The active value is the inverse of its reset read value.                                                                                                                                                 |

| 20   | BURNIN#/ LED0 | B <sub>U</sub> | BURNIN#: Resets read input. Set Active LOW to put the chip in burn-in test mode. LED0 (output): Low active, the default behavior is ON when the chip is in link-up condition and is BLINK when the chip detects transmits or receive activity.                                                                                                                   |

| 21   | SPD100/LED1   | B <sub>U</sub> | SPD100: Resets read input.  If ANEN is Low, SPD100 sets the TP port speed in register 0.  If ANEN is High, SPD100 is used to set 100 Mbps half-duplex and 100 Mbps full-duplex bits in register 4.  LED1 (output): Low active. The default behavior is ON when the chip is operating at 100 Mbps, and is OFF when the chip is operating at 10 Mbps.              |

| 22   | DUPLEX/LED2   | B <sub>U</sub> | DUPLEX: Resets read input.  If ANEN is Low, DUPLEX sets the TP port in full-duplex mode in register 0.  If ANEN is High, DUPLEX is used to set 10 Mbps FDX and 100 Mbps FDX bits in register 4.  LED2 (output): Low active. The default behavior is ON when the chip is operating in full-duplex mode and is OFF when the chip is operating in half-duplex mode. |

| 23   | ANEN/LED3     | B <sub>U</sub> | ANEN (resets read input): Auto-negotiation enable for the twisted-pair port. Pull high to enable auto-negotiation. Pull low to disable auto-negotiation.  LED3 (output): Low active. The default behavior is BLINK when the chip detect collision is in half-duplex mode.                                                                                        |

| 24   | PDOWN#        | B <sub>U</sub> | PDOWN# (input): Power-down input. Pulling this pin low puts both the TP and fiber port into power-down mode. This is a regular input, <i>not</i> a reset read signal.                                                                                                                                                                                            |

| 25   | VCC           | Р              | +2.5 V power supply.                                                                                                                                                                                                                                                                                                                                             |

| 26   | RXN           | Α              | Receive. For TP port in MDI mode. Transmit. For TP port in MDIX mode.                                                                                                                                                                                                                                                                                            |

| 27   | RXP           | Α              | Receive +. For TP port in MDI mode.  Transmit +. For TP port in MDIX mode.                                                                                                                                                                                                                                                                                       |

| 28   | SD/FXEN       | Al             | SD/FXEN (analog input): Pull LOW to enable TP mode.  Connect to fiber module to enable FX mode; also serves as signal detect input.                                                                                                                                                                                                                              |

| 29   | GND           | G              | Ground                                                                                                                                                                                                                                                                                                                                                           |

| 30   | GND           | G              | Ground                                                                                                                                                                                                                                                                                                                                                           |

| 31   | RBIAD         | Α              | Bias resistor connection. Connect to a 10K 1% resistor to GND.                                                                                                                                                                                                                                                                                                   |

| 32   | VCCPLL        | Р              | +2.5 V supply for analog bias, PLL modules.                                                                                                                                                                                                                                                                                                                      |

| 33   | GND           | G              | Ground                                                                                                                                                                                                                                                                                                                                                           |

| 34   | TXN           | A              | Transmit. In MDI mode. Receive. In MDIX mode.                                                                                                                                                                                                                                                                                                                    |

06/06/02 Pin Descriptions

### Table 2: Pinout and signal definitions (Cont.)

| PIN# | PIN name     | Туре           | Description                                                                                                                                                                                                                                                       |

|------|--------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 35   | TXP          | А              | Transmit +. In MDI mode. Receive +. In MDIX mode.                                                                                                                                                                                                                 |

| 36   | VCC25OUT     | Р              | +2.5 VCC out from the on chip regulator.                                                                                                                                                                                                                          |

| 37   | GND          | G              | Ground                                                                                                                                                                                                                                                            |

| 38   | GND          | G              | Ground                                                                                                                                                                                                                                                            |

| 39   | хо           | Α              | XTAL output.                                                                                                                                                                                                                                                      |

| 40   | XI           | A              | XTAL input.  In RMII mode, it is defined as CLK_REF = 50 MHz clock input.  In MII Mode: XI and XO is designed to connect to a 25 MHz., 50 PPM XTAL or 25 MHz OSC.                                                                                                 |

| 41   | VCC33IN      | Р              | 3.3 V Power supply input.                                                                                                                                                                                                                                         |

| 42   | RST#         | Ιυ             | Reset input. Low active.                                                                                                                                                                                                                                          |

| 43   | MDIO         | B <sub>U</sub> | MDIO (input/ output): Management data I/O. This serial input/output pin is used to read from and write to the MII register. The data value on the MDIO pin is valid and latched on the rising edge of the MDC. This pin requires a 1 k $\Omega$ resistor pull-up. |

| 44   | MDC          | I <sub>D</sub> | MDC (input): Management data clock. The MDC clock input must be provided to allow MII management function. This pin has a Schmitt trigger input.                                                                                                                  |

| 45   | PHYAD1/ RXD3 | B <sub>D</sub> | PHYAD1: Resets read input. Pull high or low to set the PHY Address bit 1 for MII/RMII management function.  RXD3: Receives the data output signal in the MII interface.                                                                                           |

| 46   | PHYAD2/ RXD2 | B <sub>D</sub> | PHYAD2: Resets read input. Pull high or low to set the PHY Address bit 2 for MII/RMII management function.  RXD2: Receives the data output signal in the MII interface.                                                                                           |

| 47   | PHYAD3/ RXD1 | B <sub>D</sub> | PHYAD3 (Reset Read Input): Pull High or Low to set the PHY Address bit 3 for MII/RMII management function.  RXD1: Receive data output signal in MII/RMII interface.                                                                                               |

| 48   | PHYAD4/ RXD0 | B <sub>D</sub> | PHYAD4: Resets read input. Pull high or low to set the PHY Address bit 4 for MII/RMII management function.  RXD0: Receives the data output signal in the MII/RMII interface.                                                                                      |

06/06/02

06/06/02 Pinout Diagram

## **Section 3: Pinout Diagram**

Figure 1: AC101L pinout diagram

06/06/02

06/06/02 Operational Description

## **Section 4: Operational Description**

#### RESET

The PHY can be reset in three ways:

- · During initial power on.

- Hardware reset: (See "Pin Descriptions" on page 7).

- Software reset: (See "Register Description" on page 17).

#### **POWER SOURCE**

The AC101L chip provides an onboard 3.3 V  $\pm$ 5% input to 2.5 V  $\pm$ 5% output regulator with the capability to drive 150 mA of current. The 2.5 V output supplies the PHY operation, including the LEDs. It is recommended to limit the LED current below 10 mA per LED.

The 2.5 V power should be decoupled to provide the digital and analog pins on the chip.

#### **POWER SAVING MODE**

The power consumption of the AC101L device is significantly reduced due to its built-in power management features. Separate power supply lines are used to power the 10BASE-T circuitry and the 100BASE-TX circuitry. Therefore, the two circuits can be turned on and turned off independently. When the PHY is set to operate in 100BASE-TX mode, the 10BASE-T circuitry is powered down.

The following power management features are supported:

- **Power-down mode**: (see pin and register descriptions). During power down mode, the device is still able to interface through the management interface.

- Energy detect/power saving mode: Energy detect mode turns off the power to select internal circuitry when there is no live network connected. The energy detect (ED) circuit is always turned on to monitor if there is signal energy present on the media. The management circuitry is also powered on and ready to respond to any management transaction. The transmit circuit still sends out link pulses with minimum power consumption. If a valid signal is received from the media, the device powers up and resumes normal transmit/receive operations.

- Valid data detection mode: This can be achieved by writing to the Receive Clock Register control bit. During this

mode, if there is no data other than incoming idles, the receive clock (RX\_CLK) turns itself off. This could save the

power of the attached media access controller. RX\_CLK resumes operation one clock period prior to the assertion of

RXDV. The receive clock again shuts off 64 clock cycles after RXDV is deasserted.

#### **CLOCK SOURCE**

The clock source for this chip is from the XI pin. In MII mode, it can connect to a 25 MHz 50 ppm (parts per million) OSC or a 25 MHz 50 ppm XTAL (crystal).

When operating in RMII mode, this pin shall be connected to the 50 MHz, 50 ppm clock reference. The internal circuit determines the operating mode upon reset read of the RX\_CLK/RMII\_SEL signal, and decides whether to divide done this clock to provide 25 MHz internal clock reference.

Isolate mode 06/06/02

#### **ISOLATE MODE**

When the AC101L device is put into isolate mode, all MII inputs (TXD[3:0], TXEN, TXER) are ignored, and all MII outputs (TX\_CLK, COL, CRS, RX\_CLK, RXDV, RXER, RXD[3:0] are set to high impedance. Only the MII management pins (MDC, MDIO) operate normally. Pull HIGH pin 4 at reset or write 1 to bit 10 register 0 to put the chip into isolate mode.

#### LOOPBACK MODE

Local loopback is provided for testing purpose. It can be enabled by writing a one to register 0 bit 14.

The local loopback routes transmitted data through the transmit path back to the clock and data recovery module of the receiving path. The loopback data are presented to the PCS in 5 bit symbol format. This loopback is used to check the operation of the 5-bit symbol decoder and the phase lock loop circuitry. In local loopback, the SD output is forced to a logical 1 and TXOP/N outputs are tri-stated.

#### **INTERRUPT MODE**

The INTR pin on the PHY is asserted whenever 1 of 8 selectable interrupt events occurs. The assertion state is high or low and is programmable through the INTR\_LEVL register bit. The selection is made by setting the appropriate bit in the upper half of the Interrupt Control/Status register. When the INTR bit goes active, the MAC interface is required to read the Interrupt Control/Status register to determine which event caused the interrupt. The Status bits are read-only and clear-on-read. When INTR is not asserted, the pin is held in a high impedance state.

#### **LED** OPERATION

#### LED INTERFACE

The LED interface is fully configurable through register setting. The connection of LED (source/sink current) depends on the default setting.

The default LED modes are as shown below:

LED0 LED1 LED2 LED3

Link/Act Speed Duplex COL

06/06/02 Operational Description

#### **LED** CONFIGURATION

The LEDs are fully configurable to other operational modes. Each LED has two 16-bit registers to define its operation. See "Common registers" on page 26 and Table 3 to configure the LEDs to work with operational modes other than default mode.

## LED [3:0] EVENT TABLE

LED [3:0] are configurable. The following events are defined for AC101L operation:

Table 3: LED [3:0] event table

| Bit# | Description               |

|------|---------------------------|

| 7    | Duplex                    |

| 6    | Collision                 |

| 5    | Speed 100                 |

| 4    | Speed 10                  |

| 3    | Transmit activity         |

| 2    | Transmit/Receive activity |

| 1    | Receive activity          |

| 0    | Link                      |

LED operation 06/06/02

06/06/02 Register Description

## **Section 5: Register Description**

The first 7 registers of the MII register set are defined by the MII specification. In addition to these required registers are several registers that are specific to Altima Communications Inc. There are reserved registers and/or bits that are for Altima internal use only. The following standard registers are supported (register numbers are in decimal notation; the values are in hexadecimal notation):

NOTE—When writing to registers, it is recommended that a read/modify/write operation be performed, as unintended bits may get set to unwanted states. This applies to all registers, including those with reserved bits.

#### Legend:

- RW = Read and write access

- SC = Self-clearing

- LL = Latch low until cleared by reading

- RO = Read-only

- RC = Cleared on read

- LH = Latch high until cleared by reading

#### TP PHY REGISTER SUMMARY

Table 4: TP PHY register summary

| Register       | Description                                    | Default value |

|----------------|------------------------------------------------|---------------|

| Registers 0-7  |                                                | ,             |

| 0              | Control register                               | 3000          |

| 1              | Status register                                | 7849          |

| 2              | PHY Identifier 1 register                      | 0022          |

| 3              | PHY Identifier 2 register                      | 5521          |

| 4              | Auto-Negotiation Advertisement register        | 01E1          |

| 5              | Auto-Negotiation Link Partner Ability register | 0001          |

| 6              | Auto-Negotiation Expansion register            | 0004          |

| 7              | Next Page Advertisement register               | 2001          |

| Registers 8-31 |                                                |               |

| 8–15           | Reserved                                       | XXXX          |

| 16             | BT and Interrupt Level Control register        | 03C0          |

| 17             | Interrupt Control/Status register              | 0000          |

| 18,19          | Reserved                                       | xxxx          |

| 20             | Cable measurement capability register          | xxxx          |

| 21             | Receive Error Counter register                 | 0304          |

| 22–31          | Reserved                                       | xxxx          |

### **REGISTER 0: CONTROL REGISTER**

Table 5: Register 0: Control register

| Bit     | Name           | Description                                                                                                                                                                                                                             | Mode  | Default            |

|---------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--------------------|

| 0.15    | Reset          | 1 = PHY reset. This bit is self-clearing.                                                                                                                                                                                               | RW/SC | 0                  |

| D.14    | Loopback       | Enable loopback mode. This loops back TXD to RXD and ignores all of the activity on the cable media.     Normal operation.                                                                                                              | RW    | 0                  |

| 0.13    | Speed Select   | 1 = 100 Mbps<br>0 = 10 Mbps<br>Default value:<br>SPD100                                                                                                                                                                                 | RW    | Set by<br>SPD100   |

| 0.12    | ANEN Enable    | 1 = Enable the auto-negotiate process (overrides 0.13 and 0.8) 0 = Disable the auto-negotiate process. Mode selection is controlled via bit 0.8, 0.13 Default value: ANEN                                                               | RW    | Set by<br>ANEN     |

| D.11    | Power Down     | 1 = Power down. All blocks except for SMI will be turned off.  Setting PDOWN# pin (24) to LOW will achieve the same result.  0 = Normal operation.                                                                                      | RW    | 0                  |

| 0.10    | Isolate        | 1 = Electrically isolate the PHY from the MII. The PHY is still able to respond to the SMI. 0 = Normal operation.                                                                                                                       | RW    | 0                  |

| 0.9     | Restart ANEN   | 1 = Restart auto-negotiation process. 0 = Normal operation.                                                                                                                                                                             | RW/SC | 0                  |

| 0.8     | Duplex Mode    | 1 = Full-duplex operation. 0 = Half-duplex operation. Default value: !ANEN && DUPLEX                                                                                                                                                    | RW    | See<br>description |

| 0.7     | Collision Test | 1 = Enable collision test, which issues the COL signal in response to the assertion of TXEN signal. Collision test is disabled if the PCSBP pin is high. Collision test is enabled regardless of the duplex mode. 0 = Disable COL test. | RW    | 0                  |

| 0.[6:0] | Reserved       | -                                                                                                                                                                                                                                       | RW    | 0000000            |

## **REGISTER 1: STATUS REGISTER**

Table 6: Register 1: Status register

| Bit  | Name                      | Description                                                                                                 | Mode | Default            |

|------|---------------------------|-------------------------------------------------------------------------------------------------------------|------|--------------------|

| 1.15 | 100BASE-T4                | Permanently tied to zero; indicates no 100BASE-T4 capability.                                               | RO   | 0                  |

| 1.14 | 100BASE-TX<br>Full-Duplex | 1 = 100BASE-TX full-duplex capable. 0 = Not 100BASE-TX full-duplex capable. Default value: SPD100 && DUPLEX | RO   | See<br>description |

06/06/02 Register Description

Table 6: Register 1: Status register

| Bit      | Name                       | Description                                                                                                                                                         | Mode  | Default            |

|----------|----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--------------------|

| 1.13     | 100BASE-TX<br>Half-Duplex  | 1 = 100BASE-TX half-duplex capable. 0 = Not TX half-duplex capable. Default value: SPD100 && (ANEN    !DUPLEX).                                                     | RO    | See<br>description |

| 1.12     | 10BASE-T<br>Full-Duplex    | 1 = 10BASE-T full-duplex capable. 0 = Not 10BASE-T full-duplex capable. Default value: DUPLEX && (ANEN    ISPD100)                                                  | RO    | See<br>description |

| 1.11     | 10BASE-T<br>Half-Duplex    | 1 = 10BASE-T half-duplex capable. 0 = Not 10BASE-T half-duplex capable. Default value: ANEN    (ISPD100 && !DUPLEX)                                                 | RO    | See<br>description |

| 1.[10:7] | Reserved                   | -                                                                                                                                                                   | RO    | 0000               |

| 1.6      | MF Preamble<br>Suppression | The PHY is able to perform management transaction without MDIO preamble. The management interface needs a minimum of 32 bits of preamble after reset.               | RO    | 1                  |

| 1.5      | ANEN Complete              | 1 = Auto-negotiation process completed. Registers 4, 5, and 6 are valid after this bit is set. 0 = Auto-negotiation process is not completed.                       | RO    | 0                  |

| 1.4      | Remote Fault               | <ul> <li>1 = Remote fault condition detected.</li> <li>0 = No remote fault.</li> <li>This bit will remain set until it is cleared by reading register 1.</li> </ul> | RO/LH | 0                  |

| 1.3      | ANEN Ability               | 1 = Able to perform the auto-negotiation function; default value is determined by the ANEN pin.     0 = Unable to perform Auto-Negotiation function.                | RO    | Set by<br>ANEN     |

| 1.2      | Link Status                | 1 = Link is established. If the link fails, this bit clears and remains at 0 until the register is read again. 0 = Link is down.                                    | RO/LL | 0                  |

| 1.1      | Jabber Detect              | <ul><li>1 = Jabber condition detected.</li><li>0 = No Jabber condition detected.</li></ul>                                                                          | RO/LH | 0                  |

| 1.0      | Extended Capability        | 1 = Extended register capable. This bit is tied permanently to a value of 1.                                                                                        | RO    | 1                  |

### **REGISTER 2: PHY IDENTIFIER 1 REGISTER**

Table 7: Register 2: PHY Identifier 1 register

| Bit      | Name             | Description                                                                                          | Mode | Default |

|----------|------------------|------------------------------------------------------------------------------------------------------|------|---------|

| 2.[15:0] | OUI <sup>a</sup> | Composed of the 3rd through 18th bits of the Organizationally Unique Identifier (OUI), respectively. | RO   | 0022(H) |

a. Based on an OUI of 0010A9 (hexadecimal)

### **REGISTER 3: PHY IDENTIFIER 2 REGISTER**

Table 8: Register 3: PHY Identifier 2 register

| Bit       | Name             | Description                                        | Mode | Default |

|-----------|------------------|----------------------------------------------------|------|---------|

| 3.[15:10] | OUI <sup>a</sup> | Assigned to the 19th through 24th bits of the OUI. | RO   | 010101  |

| 3.[9:4]   | Model Number     | Six bit manufacturer's model number.               | RO   | 010010  |

| 3.[3:0]   | Revision Number  | Four-bit manufacturer's revision number.           | RO   | 0001    |

a. Based on an OUI of 0010A9 (hexadecimal)

#### **REGISTER 4: AUTO-NEGOTIATION ADVERTISEMENT REGISTER**

Table 9: Register 4: Auto-Negotiation Advertisement register

| Bit       | Name                      | Description                                                                                                                                                                                                                               | Mode | Default            |

|-----------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------------------|

| 4.15      | Next Page                 | 1 = Next Page enabled.<br>0 = Next Page disabled.                                                                                                                                                                                         | RW   | 0                  |

| 4.14      | Acknowledge               | This bit is set internally after receiving 3 consecutive and consistent FLP bursts.                                                                                                                                                       | RO   | 0                  |

| 4.[13:11] | Reserved                  | -                                                                                                                                                                                                                                         |      |                    |

| 4.10      | FDFC                      | Full-duplex flow control.  1 = Advertise that the DTE (MAC) has implemented both the optional MAC control sublayer and the pause function as specified in Clause 31 and Annex 31B of IEEE 802.3u.  0 = MAC does not support flow control. |      |                    |

| 4.9       | 100BASE-T4                | Technology not supported. This bit is always 0.                                                                                                                                                                                           | RO   | 0                  |

| 4.8       | 100BASE-TX<br>Full-Duplex | 1 = 100BASE-TX full-duplex capable. 0 = Not 100BASE-TX full-duplex capable. Default value: SPD100 && DUPLEX                                                                                                                               | RW   | See<br>description |

| 4.7       | 100BASE-TX                | 1 = 100BASE-TX half-duplex capable. 0 = Not TX half-duplex capable. Default value: SPD100 && (ANEN    !DUPLEX)                                                                                                                            | RW   | See<br>description |

| 4.6       | 10BASE-T Full<br>Duplex   | 1 = 10BASE-T full-duplex capable. 0 = Not 10BASE-T full-duplex capable. Default value: DUPLEX && (ANEN    !SPD100)                                                                                                                        | RW   | See<br>description |

| 4.5       | 10BASE-T                  | 1 = 10BASE-T half-duplex capable. 0 = Not 10BASE-T half-duplex capable. Default value: ANEN    (!SPD100 && !DUPLEX)                                                                                                                       | RW   | See<br>Description |

| 4.[4:0]   | Selector Field            | Protocol selection [00001] = IEEE 802.3.                                                                                                                                                                                                  | RO   | 00001              |

06/06/02 Register Description

# REGISTER 5: AUTO-NEGOTIATION LINK PARTNER ABILITY REGISTER/LINK PARTNER NEXT PAGE MESSAGE

Table 10: Register 5: Auto-Negotiation Link Partner Ability register/Link partner Next Page message

| Bit       | Name                      | Description                                                                                                                                 | Mode | Default |

|-----------|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|------|---------|

| 5.15      | Next Page                 | <ul><li>1 = Link partner desires a Next Page transfer.</li><li>0 = Link partner does not desire Next Page transfer.</li></ul>               | RO   | 0       |

| 5.14      | Acknowledge               | 1 = Link Partner acknowledges reception of FLP words. 0 = Not acknowledged by the link partner.                                             | RO   | 0       |

| 5.[13:10] | Reserved                  |                                                                                                                                             |      |         |

| 5.9       | 100BASE-T4                | 1 = 100BASE-T4 operation supported by the link partner. 0 = 100BASE-T4 operation not supported by the link partner.                         | RO   | 0       |

| 5.8       | 100BASE-TX<br>Full Duplex | 1 = 100BASE-TX full-duplex operation supported by the link partner. 0 = 100BASE-TX full-duplex operation not supported by the link partner. | RO   | 0       |

| 5.7       | 100BASE-TX                | 1 = 100BASE-TX half-duplex operation supported by the link partner. 0 = 100BASE-TX half-duplex operation not supported by the link partner. | RO   | 0       |

| 5.6       | 10BASE-T Full<br>Duplex   | 1 = 10 Mbps full-duplex operation supported by the link partner. 0 = 10 Mbps full-duplex operation not supported by the link partner.       | RO   | 0       |

| 5.5       | 10BASE-T                  | 1 = 10 Mbps half-duplex operation supported by the link partner. 0 = 10 Mbps half-duplex operation not supported by the link partner.       | RO   | 0       |

| 5.[4:0]   | Selector Field            | Protocol Selection [00001] = IEEE 802.3.                                                                                                    | RO   | 00001   |

NOTE—When this register is used as the Next Page message, the bit definition is the same as that is register 7.

#### **REGISTER 6: AUTO-NEGOTIATION EXPANSION REGISTER**

Table 11: Register 6: Auto-Negotiation Expansion register