### High power white LED driver with I<sup>2</sup>C interface

### **Features**

- Buck-boost DC-DC converter

- Drives one power white LED up to 800 mA from 2.7 V to 5.5 V in QFN

- Drives one power white LED up to 800 mA from 3.3 V to 5.5 V in BGA

- Efficient up to 92%

- Output current control

- 1.8 MHz typ. fixed frequency PWM

- Synchronous rectification

- Full I2C control

- Operational modes:

- Shutdown mode

- Shutdown + NTC

- Ready mode + auxiliary red LED

- Flash mode: up to 800 mA

- Torch mode: up to 200 mA

- Soft and hard triggering of flash

- Flash and torch dimming with 16 exponential values

- Dimmable red LED indicator auxiliary output

- Internally or externally timed flash operation

- Digitally programmable safety time-out in flash mode

- LED overtemperature detection and protection with external NTC resistor

- Opened and shorted LED failure detection and protection

- Chip over temperature detection and protection

- < 1 µA shutdown current</p>

- Packages:

- QFN20 (4 x 4)

- TFBGA25 (3 x 3)

### **Applications**

- Cell phone and smart phone

- Camera flashes/strobe

- PDAs and digital still cameras

### **Description**

The STCF03 is a high efficiency power supply solution to drive a single flash LED in camera phone, PDAs and other hand-held devices. It is a buck - boost converter to guarantee a proper LED current control over all possible conditions of battery voltage and output voltage; the output current control ensure a good current regulation over the forward voltage spread characteristics of the flash LED. Thanks to the high efficiency of the converter allows having the input current taken from the battery remain under 1.5 A.

Table 1. Device summary

| Order codes | Packages           | Packaging           |  |  |

|-------------|--------------------|---------------------|--|--|

| STCF03PNR   | QFN20 (4 x 4 mm)   | 4500 parts per reel |  |  |

| STCF03TBR   | TFBGA25 (3 x 3 mm) | 3000 parts per reel |  |  |

February 2011 Doc ID 13169 Rev 7 1/35

Contents STCF03

# **Contents**

| 1 | Desc  | cription (continued)6                                          |

|---|-------|----------------------------------------------------------------|

| 2 | Diag  | ram7                                                           |

| 3 | Pin c | configuration                                                  |

| 4 | Maxi  | mum ratings                                                    |

| 5 | Appl  | ication                                                        |

| 6 | Elec  | trical characteristics11                                       |

| 7 | Intro | duction                                                        |

|   | 7.1   | Buck-boost converter                                           |

|   | 7.2   | Logic pin description                                          |

|   |       | 7.2.1 SCL, SDA pins                                            |

|   |       | 7.2.2 TRIG pin13                                               |

|   |       | 7.2.3 ATN pin                                                  |

|   |       | 7.2.4 ADD pin                                                  |

|   |       | 7.2.5 TMSK pin                                                 |

|   | 7.3   | I <sup>2</sup> C bus interface                                 |

|   | 7.4   | Data validity                                                  |

|   | 7.5   | Start and stop conditions                                      |

|   | 7.6   | Byte format                                                    |

|   | 7.7   | Acknowledge                                                    |

|   | 7.8   | Writing to a single register                                   |

|   | 7.9   | Interface protocol                                             |

|   | 7.10  | Writing to multiple registers with incremental addressing 18   |

|   | 7.11  | Reading from a single register                                 |

|   | 7.12  | Reading from multiple registers with incremental addressing 19 |

| 8 | Desc  | ription of internal registers20                                |

|   | 8.1   | PWR_ON 20                                                      |

|    | 8.2      | TRIG_EN                                                                      | 20 |

|----|----------|------------------------------------------------------------------------------|----|

|    | 8.3      | TCH_ON                                                                       | 20 |

|    | 8.4      | NTC_ON                                                                       | 20 |

|    | 8.5      | FTIM_0~3                                                                     | 21 |

|    | 8.6      | TDIM_0~3                                                                     | 21 |

|    | 8.7      | FDIM_0~3                                                                     | 21 |

|    | 8.8      | AUXI_0~3                                                                     | 22 |

|    | 8.9      | AUXT_0~3                                                                     | 22 |

|    | 8.10     | F_RUN                                                                        | 23 |

|    | 8.11     | LED_F                                                                        | 23 |

|    | 8.12     | NTC_W                                                                        | 23 |

|    | 8.13     | NTC_H                                                                        | 23 |

|    | 8.14     | OT_F                                                                         | 23 |

|    | 8.15     | VOUTOK_N                                                                     | 24 |

| •  | <b>.</b> |                                                                              |    |

| 9  |          | led description                                                              |    |

|    | 9.1      | PowerON reset                                                                |    |

|    | 9.2      | Shutdown, shutdown with NTC                                                  | 25 |

|    | 9.3      | Ready mode                                                                   | 25 |

|    | 9.4      | Single or multiple Flash using external (microprocessor) temporization $\ .$ | 25 |

|    | 9.5      | External (microprocessor) temporization using TRIG_EN bit                    | 26 |

|    | 9.6      | Single Flash using internal temporization                                    | 26 |

|    | 9.7      | Multiple Flash using internal temporization                                  | 26 |

| 10 | Туріс    | al performance characteristics                                               | 27 |

| 11 | Packa    | age mechanical data                                                          | 29 |

| 12 | Revis    | sion history                                                                 | 34 |

List of tables STCF03

# List of tables

| Table 1.  | Device summary                                       | 1  |

|-----------|------------------------------------------------------|----|

| Table 2.  | Pin description                                      |    |

| Table 3.  | Absolute maximum ratings                             | 9  |

| Table 4.  | Thermal data                                         |    |

| Table 5.  | List of external components                          | 10 |

| Table 6.  | Electrical characteristics                           | 11 |

| Table 7.  | Address table                                        | 14 |

| Table 8.  | Interface protocol                                   | 17 |

| Table 9.  | I <sup>2</sup> C register mapping function           | 20 |

| Table 10. | Command register                                     | 20 |

| Table 11. | Dimming register                                     | 21 |

| Table 12. | Auxiliary register                                   | 22 |

| Table 13. | Auxiliary LED dimming table                          | 22 |

| Table 14. | Torch mode and flash mode dimming registers settings | 22 |

| Table 15. | Status register                                      | 23 |

| Table 16. | Status register details                              |    |

| Table 17. | QFN20 (4 x 4 mm.) mechanical data                    | 29 |

| Tahla 18  | Document revision history                            | 3/ |

STCF03 List of figures

# **List of figures**

| Figure 1.  | Block diagram                                                                            | 7  |

|------------|------------------------------------------------------------------------------------------|----|

| Figure 2.  | Pin connections (bottom view)                                                            |    |

| Figure 3.  | Application schematic                                                                    | 10 |

| Figure 4.  | Procedure for assigning a non-default I <sup>2</sup> C address                           | 14 |

| Figure 5.  | Data validity on the I <sup>2</sup> C Bus                                                | 15 |

| Figure 6.  | Timing diagram on I <sup>2</sup> C Bus                                                   | 15 |

| Figure 7.  | Bit transfer                                                                             | 16 |

| Figure 8.  | Acknowledge on I <sup>2</sup> C Bus                                                      | 16 |

| Figure 9.  | Writing to a single register                                                             | 17 |

| Figure 10. | Writing to multiple register with incremental addressing                                 | 18 |

| Figure 11. | Reading from a single register                                                           | 19 |

| Figure 12. | Reading from multiple registers                                                          | 19 |

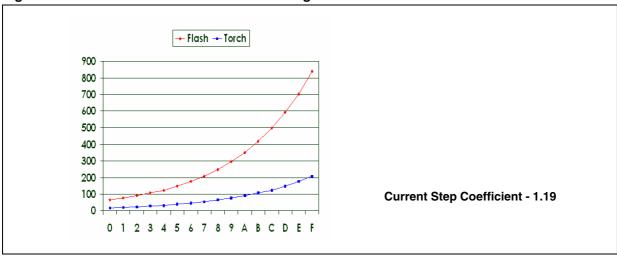

| Figure 13. | Flash and Torch current vs. dimming value                                                | 21 |

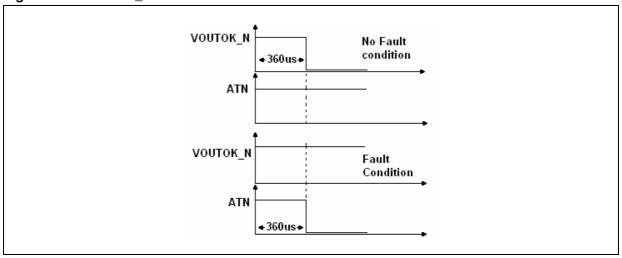

| Figure 14. | VOUTOK_N behavior                                                                        | 24 |

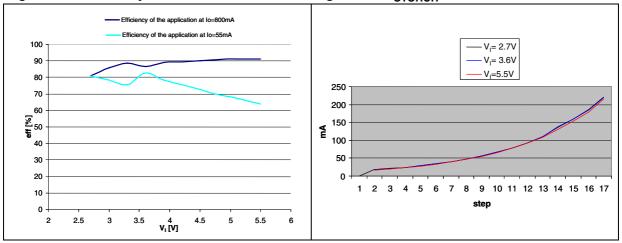

| Figure 15. | Efficiency                                                                               | 27 |

| Figure 16. | I <sub>OTORCH</sub> vs. T_DIMM                                                           | 27 |

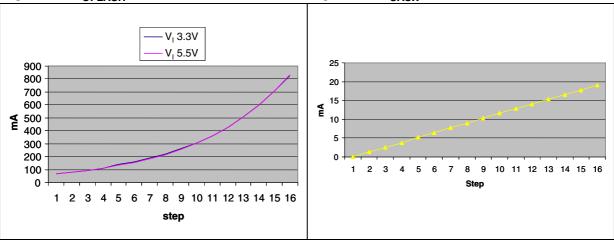

| Figure 17. | I <sub>OFLASH</sub> vs. F_DIMM                                                           | 27 |

| Figure 18. | IOAUX vs. AUXI                                                                           |    |

| Figure 19. | $I_{OFLASH}$ vs. temp. $V_I = 3.3 \text{ V} \dots$                                       |    |

| Figure 20. | VFB2 vs. temp. at $I_O$ = 800 mA, $V_I$ = 3.3 V                                          |    |

| Figure 21. | $I_Q$ vs. temp. $V_I = 5.5$ V ready-mode                                                 |    |

| Figure 22. | Start-up in flash mode 800 mA at V <sub>I</sub> = 3.6 V                                  |    |

| Figure 23. | Line transient in flash mode 800 mA, change of $V_{I}$ from 2.7 V to 3.3 V in 10 $\mu s$ |    |

| Figure 24. | QFN20 (4 x 4 mm.) drawing                                                                | 30 |

### 1 Description (continued)

All the functions of the device are controlled through the I<sup>2</sup>C which helps bus that allows to reduce logic pins on the package and to save PCB tracks on the board. Hard and soft-triggering of flash are both supported. The device includes many functions to protect the chip and the power LED such as: a soft start control, chip over temperature detection and protection as well as opened and shorted LED detection and protection. Besides, a digital programmable time out function protects the LED in case of a wrong command from the microprocessor. An optional external NTC resistor is supported to protect the LED against over heating.

In mobile phone applications it is possible to reduce immediately the flash LED current during the signal transmission using the TMSK pin. This saves battery life and gives more priority to supply RF transmission instead of flash function.

It is possible by I<sup>2</sup>C to separately program the current intensity in flash and torch mode using exponential steps. An auxiliary output can control an optional red LED to be used as a recording indicator.

The device is packaged in QFN (4 x 4 mm) 20L with a height less than 1 mm and in TFBGA25 (3 x 3 mm).

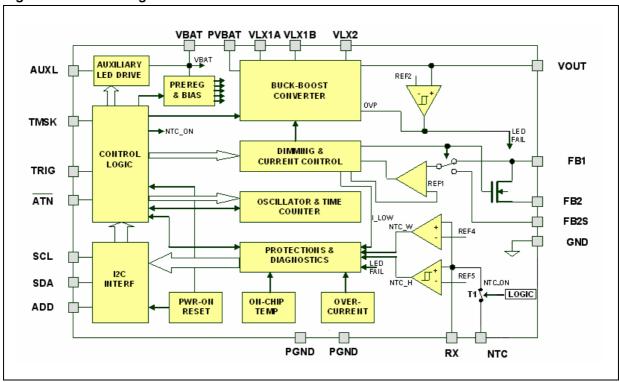

STCF03 Diagram

# 2 Diagram

Figure 1. Block diagram

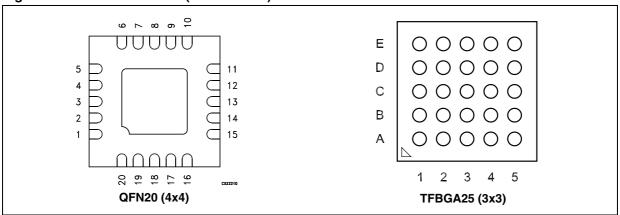

Pin configuration STCF03

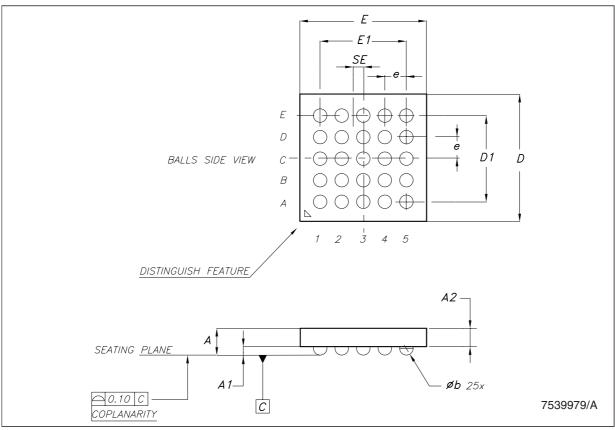

# 3 Pin configuration

Figure 2. Pin connections (bottom view)

Table 2. Pin description

| lable 2. Pin description |                      |       |                                                                                        |  |  |

|--------------------------|----------------------|-------|----------------------------------------------------------------------------------------|--|--|

| Pin n° for<br>QFN20      | QFN20 TFBGA25 Symbol |       | Name and function                                                                      |  |  |

| 1                        | E1, D2               | VLX2  | Inductor connection                                                                    |  |  |

| 2                        | B3                   | RX    | R <sub>X</sub> resistor connection                                                     |  |  |

| 3                        | A4                   | NTC   | NTC resistor connection                                                                |  |  |

| 4                        | D1, C2               | VOUT  | Output voltage                                                                         |  |  |

| 5                        | B5                   | FB1   | Feedback pin [I <sub>LED</sub> *(R <sub>FL</sub> +R <sub>TR</sub> )]                   |  |  |

| 6                        | A5                   | FB2   | R <sub>TR</sub> bypass                                                                 |  |  |

| 7                        | B4                   | FB2S  | Feedback sensing pin [I <sub>LED</sub> *R <sub>FL</sub> ]                              |  |  |

| 8                        | E2                   | GND   | Signal ground                                                                          |  |  |

| 9                        | D4                   | ADD   | I <sup>2</sup> C address selection                                                     |  |  |

| 10                       | D5                   | AUXL  | Auxiliary LED output                                                                   |  |  |

| 11                       | C5                   | TMSK  | TX mask input.                                                                         |  |  |

| 12                       | B1, C1               | PVBAT | Power supply voltage                                                                   |  |  |

| 13                       | A3                   | VBAT  | Supply voltage                                                                         |  |  |

| 14                       | A2                   | VLX1A | Inductor connection                                                                    |  |  |

| 15                       | A1, B2               | VLX1B | Inductor connection                                                                    |  |  |

| 16                       | E5                   | SCL   | I <sup>2</sup> C clock signal                                                          |  |  |

| 17                       | E3                   | SDA   | I <sup>2</sup> C data                                                                  |  |  |

| 18                       | C3, D3               | PGND  | Power ground                                                                           |  |  |

| 19                       | E4                   | ATN   | Attention (open drain output, active LOW)                                              |  |  |

| 20                       | C4                   | TRIG  | Flash trigger input                                                                    |  |  |

| Exposed pad              |                      | PGND  | To be connected to the PCB ground plane for optimal electrical and thermal performance |  |  |

STCF03 Maximum ratings

# 4 Maximum ratings

Table 3. Absolute maximum ratings (1)

| Symbol                                | Parameter                                              | Value                       | Unit |

|---------------------------------------|--------------------------------------------------------|-----------------------------|------|

| VBAT                                  | Signal supply voltage                                  | -0.3 to 6                   | V    |

| PVBAT                                 | Power supply voltage                                   | -0.3 to 6                   | V    |

| VLX1A, VLX1B                          | Inductor connection 1                                  | -0.3 to V <sub>I</sub> +0.3 | V    |

| VLX2                                  | Inductor connection 2                                  | -0.3 to V <sub>O</sub> +0.3 | V    |

| VOUT                                  | Output voltage                                         | -0.3 to 6                   | V    |

| AUXL                                  | Auxiliary LED                                          | -0.3 to V <sub>I</sub> +0.3 | V    |

| FB1, FB2, FB2S                        | Feedback and sense voltage                             | -0.3 to 3                   | V    |

| SCL, SDA, TRIG,<br>ATN, ADD TMSK      | Logic pin                                              | -0.3 to V <sub>I</sub> +0.3 | V    |

| R <sub>X</sub>                        | Connection for reference resistor                      | -0.3 to 3                   | V    |

| NTC                                   | Connection for LED temperature sensing                 | -0.3 to 3                   | V    |

| ESD                                   | Human body model                                       | ±2                          | kV   |

| P <sub>TOT</sub> (BGA) <sup>(2)</sup> | Continuous power dissipation (at T <sub>A</sub> =70°C) | 800                         | mW   |

| T <sub>OP</sub>                       | Operating junction temperature range                   | -40 to 85                   | °C   |

| T <sub>J</sub>                        | Junction temperature                                   | -40 to 150                  | °C   |

| T <sub>STG</sub>                      | Storage temperature range                              | -65 to 150                  | °C   |

Absolute maximum ratings are those values beyond which damage to the device may occur. Functional operation under these condition is not implied.

Table 4. Thermal data

| Symbol            | Parameter                           | QFN20 | TFBGA25 | Unit |

|-------------------|-------------------------------------|-------|---------|------|

| R <sub>thJA</sub> | Thermal resistance junction-ambient | 59    | 150     | °C/W |

<sup>2.</sup> Power dissipation is related parameter to used PCB. The recommended PCB design is included in the application note.

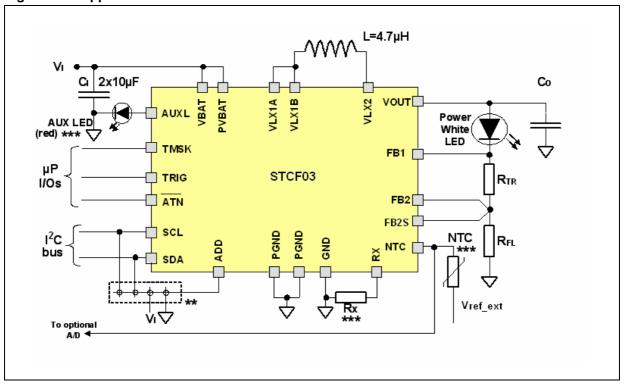

Application STCF03

# 5 Application

Figure 3. Application schematic

<sup>\*\*:</sup> Connect to  $V_I$ , or GND or SDA or SCL to choose one of the 4 different I<sup>2</sup>C Slave Addresses.

Table 5. List of external components

| Component                     | Manufacturer | Part number Value |        | Size               |

|-------------------------------|--------------|-------------------|--------|--------------------|

| C <sub>I</sub>                | TDK          | X5R0J106M         | 10 μF  | 0603               |

| Co                            | TDK          | X5R0J105M         | 1 μF   | 0603               |

| L (I <sub>FLASH</sub> = 0.5A) | TDK          | VLF3012ST-4R7MR91 | 4.7 μH | 2.6 x 2.8 x 1.2 mm |

| L (I <sub>FLASH</sub> = 0.8A) | TDK          | VLF4012AT-4R7M1R1 | 4.7 μH | 3.7 x 3.5 x 1.2 mm |

| NTC                           | Murata       | NCP21WF104J03RA   | 100 kΩ | 0805               |

| R <sub>FL</sub>               |              |                   | 0.27 Ω | 0603               |

| R <sub>TR</sub>               |              |                   | 1.8 Ω  | 0402               |

| R <sub>X</sub>                |              |                   | 15 kΩ  | 0402               |

Note: All of the above listed components refer to typical application. Operation of the STCF03 is not limited to the choice of these external components.

<sup>\*\*\*:</sup> Optional components to support auxiliary functions.

# 6 Electrical characteristics

$T_J$  = 25 °C,  $V_I$  = 3.6 V, 2 x  $C_I$  = 10  $\mu F,~C_O$  = 1  $\mu F,~L$  = 4.7  $\mu H,~R_{FL}$  = 0.27  $\Omega,~R_{TR}$  = 1.8  $\Omega,~R_X$  = 15 k $\Omega,~Typ.$  values @ 25 °C, unless otherwise specified.

Table 6. Electrical characteristics

| Symbol             | Parameter Test condition                                          |                                                                                                                                                                                                            | Min. | Тур. | Max. | Unit |  |

|--------------------|-------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|------|--|

| VI                 | Input operation supply voltage                                    |                                                                                                                                                                                                            | 2.7  |      | 5.5  | V    |  |

| V <sub>PW_ON</sub> | Power ON reset threshold                                          | V <sub>I</sub> rising                                                                                                                                                                                      |      | 2.3  |      | V    |  |

|                    |                                                                   | Flash mode for V <sub>I</sub> = 2.7 V to 5.5 V (STCF03PNR)                                                                                                                                                 | 60   |      | 800  |      |  |

|                    | Output current adjustment range I <sub>FLASH</sub>                | Flash mode for V <sub>I</sub> = 2.7 V to 3.3 V (STCF03TBR)                                                                                                                                                 | 60   |      | 600  |      |  |

| Io                 |                                                                   | Flash mode for V <sub>I</sub> =3.3 V to 5.5 V (STCF03TBR)                                                                                                                                                  | 60   |      | 800  | mA   |  |

|                    | Output current adjustment range I <sub>TORCH</sub>                | Torch mode V <sub>I</sub> = 2.7 V to 5.5 V                                                                                                                                                                 | 15   |      | 200  |      |  |

|                    | Auxiliary LED output current adjustment range I <sub>AUXLED</sub> | Ready mode, V <sub>I</sub> = 3.3 V to 5.5 V                                                                                                                                                                | 0    |      | 20   |      |  |

| Vo                 | Regulated voltage range                                           |                                                                                                                                                                                                            | 2.5  |      | 5.3  | V    |  |

| FB1                | Feedback voltage                                                  | Torch mode                                                                                                                                                                                                 | 30   |      | 250  | mV   |  |

| FB2                | Feedback voltage                                                  | Flash mode                                                                                                                                                                                                 | 30   |      | 250  | mV   |  |

| Δl <sub>O</sub>    | Output current tolerance                                          | Flash mode, I <sub>O</sub> = 160 mV/R <sub>FL</sub>                                                                                                                                                        | -10  |      | 10   | %    |  |

| R <sub>ON</sub> _  | FB1-FB2 ON resistance                                             | Torch mode, I <sub>O</sub> = 200 mA                                                                                                                                                                        |      | 90   |      | mΩ   |  |

|                    | Quiescent current in                                              | NTC_ON=0                                                                                                                                                                                                   |      | 1    |      |      |  |

| IQ                 | SHUTDOWN mode                                                     | NTC_ON=1                                                                                                                                                                                                   |      | 1    |      | μΑ   |  |

|                    | Quiescent current in ready - mode                                 |                                                                                                                                                                                                            |      | 1.8  |      | mA   |  |

| f <sub>s</sub>     | Frequency                                                         | V <sub>I</sub> = 2.7 V                                                                                                                                                                                     |      | 1.8  |      | MHz  |  |

|                    | Efficiency of the chip itself                                     | $V_I = 3.2$ to 4.2 V, flash mode, $I_O = 800$ mA                                                                                                                                                           |      | 87   |      |      |  |

| ν                  | Efficiency of the whole application                               | $V_{I}$ = 3.2 to 4.2 V, flash mode,<br>$I_{O}$ = 800 mA, $V_{O}$ = $V_{fLED\_max}$ + $V_{FB2}$ = 5.02 V<br>See the typical application schematic<br>It is included losses of inductor and sensing resistor |      | 76   |      | %    |  |

| OVP                | Output over voltage protection                                    | V <sub>I</sub> = 5.5 V, No Load                                                                                                                                                                            | 5.3  |      |      | V    |  |

| OV <sub>HYST</sub> | Over voltage hysteresis                                           | V <sub>I</sub> = 5.5 V, No Load                                                                                                                                                                            |      | 0.3  |      | V    |  |

| OTP                | Over temperature protection                                       | V <sub>I</sub> = 5.5 V                                                                                                                                                                                     |      | 140  |      | °C   |  |

| OT <sub>HYST</sub> | Over temperature hysteresis                                       | V <sub>I</sub> = 5.5 V                                                                                                                                                                                     |      | 20   |      | °C   |  |

| R <sub>ON</sub> T1 | RX-NTC switch ON resistance                                       | Ready mode                                                                                                                                                                                                 |      | 25   |      | Ω    |  |

Electrical characteristics STCF03

Table 6. Electrical characteristics (continued)

| Symbol              | Parameter                                              | Test condition                                   | Min. | Тур. | Max. | Unit |

|---------------------|--------------------------------------------------------|--------------------------------------------------|------|------|------|------|

| NTC <sub>LEAK</sub> | RX-NTC switch OFF leakage                              | Shutdown mode, $V_{NTC} = 2 V$<br>$V_{RX} = GND$ |      |      | 1    | μΑ   |

| V <sub>OL</sub>     | Output logic signal level low ATN                      | I <sub>OL</sub> = 10 mA                          |      |      | 0.2  | V    |

| I <sub>OZ</sub>     | Output logic leakage current ATN                       | V <sub>OZ</sub> = 3.3 V                          |      |      | 1    | mA   |

| V <sub>IL</sub>     | Input logic signal level SCL,                          | V <sub>I</sub> = 2.7 V to 5.5 V                  | 0    |      | 0.4  | V    |

| V <sub>IH</sub>     | SDA, TRIG, TEST, ADD                                   |                                                  | 1.4  |      | 3    |      |

| T <sub>ON</sub>     | LED current rise time $I_{LED} = 0$ to $I_{LED} = max$ |                                                  |      |      | 2    | ms   |

Note: Typical value, not production tested.

STCF03 Introduction

### 7 Introduction

The STCF03 is a buck-boost converter, dedicated to power and control the current of a power white LED in a camera cell phone. The device operates at a constant switching frequency of 1.8 MHz typ. It provides an output voltage down to 2.5 V and up to 5.3 V, from a 2.7 V to 5.5 V supply voltage. This supply range allows operation from a single cell Lithium-Ion battery. The I²C bus is used to control the device operation and for diagnostic purposes. The current in torch mode is adjustable from 15 mA to 200 mA. Flash mode current is adjustable up to 800 mA, BGA version is able to deliver 600 mA at battery range 2.7 V to 3.3 V. The Aux LED current can be adjusted from 0 to 20 mA. The device uses an external NTC resistor to sense the temperature of the white LED. These two last functions may not be needed in all applications, and in these cases the relevant external components can be omitted.

### 7.1 Buck-boost converter

The regulation of the PWM controller is done by sensing the current of the LED through external sensing resistors ( $R_{FL}$  and  $R_{TR}$ , see application schematic). Depending on the forward voltage of the flash LED, the device automatically can change the operation mode between buck (step down) and boost (step up) mode.

Three cases can occur: boost region ( $V_O > V_{BAT}$ ): this configuration is used in most of the cases, as the output voltage  $V_O = V_{fLED} + I_{LED} \times RFL$ ) is higher than  $V_{BAT}$ ; buck region ( $V_O \sim V_{BAT}$ ); buck - boost region ( $V_O \sim V_{BAT}$ ).

### 7.2 Logic pin description

### 7.2.1 SCL, SDA pins

These are the standard clock and data pins as defined in the I<sup>2</sup>C bus specification. External pull-up is required according to I<sup>2</sup>C bus specifications. The recommended maximum voltage of these signals should be 3.0 V.

### **7.2.2** TRIG pin

This input pin is internally AND-ed with the TRIG\_EN bit to generate the internal signal that activates the flash operation. This gives to the user the possibility to accurately control the flash duration using a dedicated pin, avoiding the I<sup>2</sup>C bus latencies (hard-triggering). No internal pull-up nor pull-down is provided.

### 7.2.3 ATN pin

This output pin (open-drain, active LOW) is provided to better manage the information transfer from the STCF03 to the microprocessor. Because of the limitations of a single master I²C bus configuration, the microprocessor should regularly poll the STCF03 to verify if certain operations have been completed, or to check diagnostic information. Alternatively, the microprocessor can use the ATN pin to be advised that new data are available in the STAT\_REG, thus avoiding continuous polling. Then the information can be read in the STAT\_REG by a read operation via I²C that, besides, automatically resets the ATN pin. The STAT\_REG bits affecting the ATN pin status are mapped in *Table 16*. No internal pull-up is provided.

Introduction STCF03

### **7.2.4** ADD pin

With this pin it is possible to select one of the 4 possible I<sup>2</sup>C slave addresses. No internal pull-up nor pull-down is provided. The pin has to be connected either GND, V<sub>I</sub>, SCL or SDA to select the desired I<sup>2</sup>C slave address (see *Table 6*)

Table 7. Address table

| ADD pin | A7 | <b>A</b> 6 | <b>A</b> 5 | <b>A</b> 4 | А3 | A2 | <b>A</b> 1 | Α0  |

|---------|----|------------|------------|------------|----|----|------------|-----|

| GND     | 0  | 1          | 1          | 0          | 0  | 0  | 0          | R/W |

| VBAT    | 0  | 1          | 1          | 0          | 0  | 0  | 1          | R/W |

| SDAL    | 0  | 1          | 1          | 0          | 0  | 1  | 0          | R/W |

| SCL     | 0  | 1          | 1          | 0          | 0  | 1  | 1          | R/W |

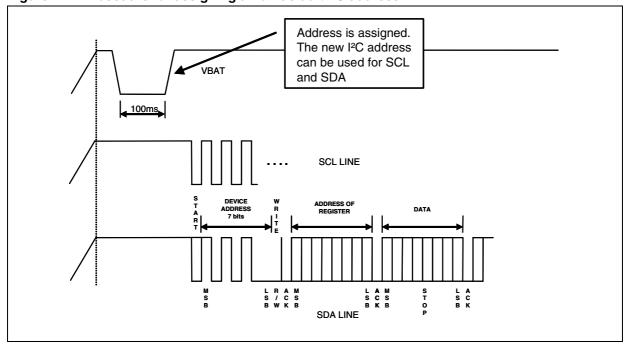

When ADD is connected to GND the I<sup>2</sup>C address is assigned automatically while in the other three configurations in which ADD pin is connected to VBAT or SDA or SCL, the following procedure must be activated in order that the right address is assigned.

After applying VBAT to the chip, the VBAT voltage must be pulled down to GND for a time longer than 100 ms. After that time the right I<sup>2</sup>C address is assigned to the chip. This procedure must be repeated every time the VBAT voltage is disconnected (see *Figure 4* below)

Figure 4. Procedure for assigning a non-default I<sup>2</sup>C address

### **7.2.5 TMSK pin**

This pin can be used to implement the TX masking function. This function has effect only for flash current settings higher than 200 mA (bit FDIM\_3 = 1). Under this condition, when this pin is pulled high by the P, the current flowing in the LED is forced at 200 mA typ. No internal pull-up nor pull-down is provided: to be externally wired to GND if TX masking function is not used.

STCF03 Introduction

### 7.3 I<sup>2</sup>C bus interface

Data transmission from the main microprocessor STCF03 and vice versa takes place through the 2 wires I<sup>2</sup>C bus interface wires, consisting of the two lines SDA and SCL (pull-up resistors to a positive supply voltage must be externally connected). The recommended maximum voltage of these signals should be 3.0 V.

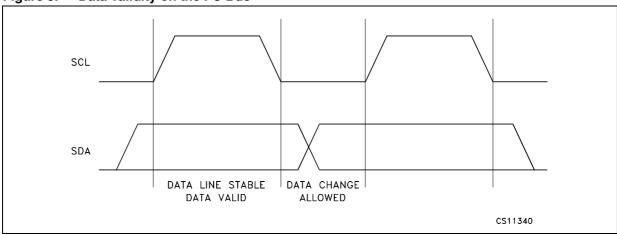

### 7.4 Data validity

As shown in *Figure 5*, the data on the SDA line must be stable during the high period of the clock. The HIGH and LOW state of the data line can only change when the clock signal on the SCL line is LOW.

Figure 5. Data validity on the I<sup>2</sup>C Bus

### 7.5 Start and stop conditions

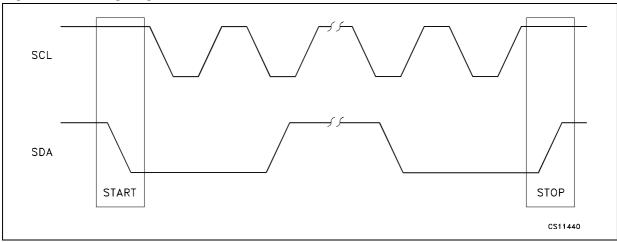

Both DATA and CLOCK lines remain HIGH when the bus is not busy. As shown in *Figure 6* a start condition is a HIGH to LOW transition of the SDA line while SCL is HIGH. The stop condition is a LOW to HIGH transition of the SDA line while SCL is HIGH. A STOP condition must be sent before each START condition.

Figure 6. Timing diagram on I<sup>2</sup>C Bus

Introduction STCF03

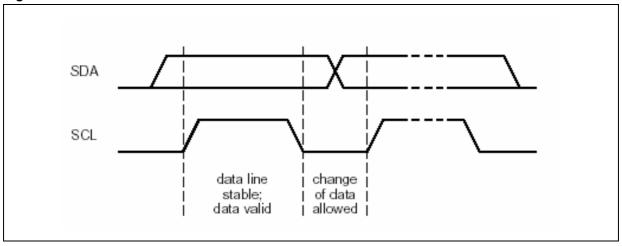

### 7.6 Byte format

Every byte transferred to the SDA line must contain 8 bits. Each byte must be followed by an acknowledge bit. The MSB is transferred first. One data bit is transferred during each clock pulse. The data on the SDA line must remain stable during the HIGH period of the clock pulse. Any change in the SDA line at this time will be interpreted as a control signal.

Figure 7. Bit transfer

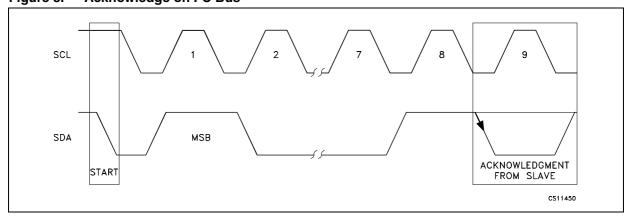

### 7.7 Acknowledge

The master (microprocessor) puts a resistive HIGH level on the SDA line during the acknowledge clock pulse (see *Figure 8*). The peripheral (STCF03) that acknowledges has to pull-down (LOW) the SDA line during the acknowledge clock pulse, so that the SDA line is stable LOW during this clock pulse. The peripheral which has been addressed has to generate an acknowledge pulse after the reception of each byte, otherwise the SDA line remains at the HIGH level during the ninth clock pulse duration. In this case the master transmitter can generate the STOP information in order to abort the transfer. The STCF03 won't generate the acknowledge if the V<sub>I</sub> supply is below the undervoltage lockout threshold.

Figure 8. Acknowledge on I<sup>2</sup>C Bus

STCF03 Introduction

Table 8. Interface protocol

|                       | D           | evid | ce a | ddre | ess · | + R/ | W b         | it     |     |       | F | Regi | ster | add | Ires | s |       |             |             |   |   | Da | ıta |   |   |     |             |                  |

|-----------------------|-------------|------|------|------|-------|------|-------------|--------|-----|-------|---|------|------|-----|------|---|-------|-------------|-------------|---|---|----|-----|---|---|-----|-------------|------------------|

|                       | 7           | 6    | 5    | 4    | 3     | 2    | 1           | 0      |     | 7     | 6 | 5    | 4    | 3   | 2    | 1 | 0     |             | 7           | 6 | 5 | 4  | 3   | 2 | 1 | 0   |             |                  |

| S<br>T<br>A<br>R<br>T | M<br>S<br>B |      |      |      |       |      | L<br>S<br>B | R<br>W | ACK | М S В |   |      |      |     |      |   | L S B | A<br>C<br>K | M<br>S<br>B |   |   |    |     |   |   | LSB | A<br>C<br>K | S<br>T<br>O<br>P |

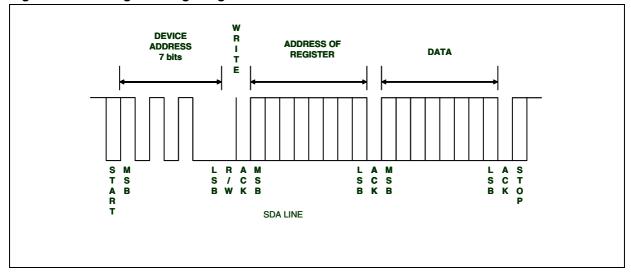

### 7.8 Writing to a single register

Writing to a single register starts with a START bit followed by the 7 bit device address of STCF03. The 8<sup>th</sup> bit is the R/W bit, which is 0 in this case. R/W = 1 means a reading operation. Then the master waits for an acknowledge from STCF03. Then the 8 bit address of register is sent to STCF03. It is also followed by an acknowledge pulse. The last transmitted byte is the data that is going to be written to the register. It is again followed by an acknowledge pulse from STCF03. Then master generates a STOP bit and the communication is over. See *Figure 9* below.

Figure 9. Writing to a single register

### 7.9 Interface protocol

The interface protocol is composed:

- A start condition (START)

- A Device address + R/W bit (read =1 / write =0)

- A Register address byte

- A sequence of data n\* (1 byte + acknowledge)

- A stop condition (STOP)

Introduction STCF03

The register address byte determines the first register in which the read or write operation takes place. When the read or write operation is finished, the register address is automatically increased.

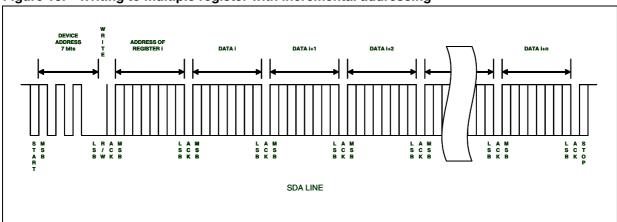

### 7.10 Writing to multiple registers with incremental addressing

It would be unpractical to send several times the device address and the address of the register when writing to multiple registers. STCF03 supports writing to multiple registers with incremental addressing. When the data is written to a register, the address register is automatically increased, so the next data can be sent without sending the device address and the register address again. See *Figure 10* below.

Figure 10. Writing to multiple register with incremental addressing

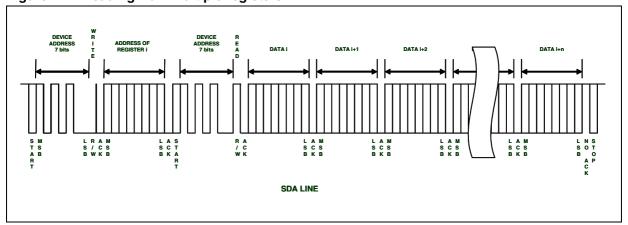

### 7.11 Reading from a single register

The reading operation starts with a START bit followed by the 7 bit device address of STCF03. The 8<sup>th</sup> bit is the R/W bit, which is 0 in this case. STCF03 confirms the receiving of the address + R/W bit by an acknowledge pulse. The address of the register which should be read is sent afterwards and confirmed again by an acknowledge pulse of STCF03 again. Then the master generates a START bit again and sends the device address followed by the R/W bit, which is 1 now. STCF03 confirms the receiving of the address + R/W bit by an acknowledge pulse and starts to send the data to the master. No acknowledge pulse from the master is required after receiving the data. Then the master generates a STOP bit to terminate the communication. See *Figure 11*.

STCF03 Introduction

DEVICE **ADDRESS** DEVICE ADDRESS **ADDRESS** DATA REGISTER 7 bits 7 bits D LNS SOT BO AP C K S M T S A B R T L A S S C T B K A R T LRAM S/CS BWKB RA / C WK **SDA LINE**

Figure 11. Reading from a single register

### 7.12 Reading from multiple registers with incremental addressing

Reading from multiple registers starts in the same way like reading from a single register. As soon as the first register is read, the register address is automatically increased. If the master generates an acknowledge pulse after receiving the data from the first register, then reading of the next register can start immediately without sending the device address and the register address again. The last acknowledge pulse before the STOP bit is not required. See the *Figure 12*.

Figure 12. Reading from multiple registers

#### **Description of internal registers** 8

Table 9. I<sup>2</sup>C register mapping function

| Register name | SUB ADDRESS (hex) | Operation |

|---------------|-------------------|-----------|

| CMD_REG       | 00                | R/W       |

| DIM_REG       | 01                | R/W       |

| AUX_REG       | 02                | R/W       |

| STAT_REG      | 03                | R only    |

Table 10. **Command register**

| CMD_REG<br>(write mode) | MSB    |         |        |        |        |        |        | LSB    |

|-------------------------|--------|---------|--------|--------|--------|--------|--------|--------|

| SUB ADD=00              | PWR_ON | TRIG_EN | TCH_ON | NTC_ON | FTIM_3 | FTIM_2 | FTIM_1 | FTIM_0 |

| Power ON<br>RESET Value | 0      | 0       | 0      | 0      | 0      | 0      | 0      | 0      |

#### 8.1 **PWR ON**

When set, it activates all analog and power internal blocks including the NTC supporting circuit, and the device is ready to operate (ready mode). As long as PWR\_ON=0, only the I<sup>2</sup>C interface is active, minimizing stand-by mode power consumption.

#### 8.2 TRIG EN

This bit is AND-ed with the TRIG pin to generate the internal signal FL\_ON that activates flash mode. By this way, both soft-triggering and hard-triggering of the flash are made possible. If soft-triggering (through I<sup>2</sup>C) is chosen, the TRIG pin is not used and must be kept HIGH (VI). If hard-triggering is chosen, then the TRIG pin has to be connected to a microprocessor I/O devoted to flash timing control, and the TRIG\_EN bit must be set in advance. Both triggering modes can benefit of the internal flash time counter, that uses the TRIG EN bit and can work either as a safety shut-down timer or as a flash duration timer. Flash mode can start only if PWR\_ON=1. LED current is controlled by the value set by the FDIM\_0~3 of the DIM\_REG.

#### 8.3 TCH ON

When set from ready mode, the STCF03 enters the torch mode. The LED current is controlled by the value set by the TDIM 0~3 of the DIM REG.

#### NTC\_ON 8.4

In ready mode, the comparators that monitor the LED temperature are activated if NTC\_ON bit is set. NTC-related blocks are always active regardless of this bit in torch mode and flash mode.

20/35 Doc ID 13169 Rev 7

### 8.5 FTIM\_0~3

This 4bit register defines the maximum flash duration. It is intended to limit the energy dissipated by the LED to a maximum safe value or to leave to the STCF03 the control of the flash duration during normal operation. Values from 0~15 correspond to 0~1.5 s (100 ms steps). The timing accuracy is related to the internal oscillator frequency that clocks the flash time counter (+/- 20 %). Entering flash mode (either by soft or hard triggering) activates the flash time counter, which begins counting down from the value loaded in the F\_TIM register. When the counter reaches zero, flash mode is stopped by resetting TRIG\_EN bit, and simultaneously the ATN pin is set to true (LOW) to alert the microprocessor that the maximum time has been reached. FTIM value remains unaltered at the end of the count.

Table 11. Dimming register

| DIM_REG<br>(write mode)                | MSB    |        |        |        |        |        |        | LSB    |

|----------------------------------------|--------|--------|--------|--------|--------|--------|--------|--------|

| SUB ADD=01                             | TDIM_3 | TDIM_2 | TDIM_1 | TDIM_0 | FDIM_3 | FDIM_2 | FDIM_1 | FDIM_0 |

| Power ON, SHUTDOWN<br>MODE RESET Value | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

### 8.6 TDIM\_0~3

These 4 bits define the LED current in torch mode with 16 values fitting an exponential law. Max torch current value is 25% of max flash current. (*Figure 13*)

### 8.7 FDIM\_0~3

These 4 bits define the LED current in flash mode with 16 values fitting an exponential law. The max value of the current is set by the external resistors  $R_{FL}$  and  $R_{TR}$ . (*Figure 13*)

Figure 13. Flash and Torch current vs. dimming value

Note: LED current values refer to  $R_{FL}$ =0.27  $\Omega$ ,  $R_{TR}$ =1.8  $\Omega$

Table 12. Auxiliary register

| AUX_REG<br>(write mode)                   | MSB    |        |        |        |        |        |        | LSB    |

|-------------------------------------------|--------|--------|--------|--------|--------|--------|--------|--------|

| SUB ADD=02                                | AUXI_3 | AUXI_2 | AUXI_1 | AUXI_0 | AUXT_3 | AUXT_2 | AUXT_1 | AUXT_0 |

| Power ON,<br>SHUTDOWN MODE<br>RESET Value | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

### 8.8 AUXI 0~3

This 4 bits register defines the AUX LED current from 0 to 20 mA. See AUX LED dimming table for reference. Loading any value between 1 and 15 also starts the AUX LED current source timer, if enabled. The AUX LED current source is active only in Ready Mode, and is deactivated in any other mode.

### 8.9 AUXT\_0~3

This 4 bit register controls the timer that defines the ON-time of the AUX LED current source. ON-time starts when the AUXI register is loaded with any value other than zero, and stops after the time defined in the AUXT register. Values from 1 to 14 of the AUXT register correspond to an ON-time of the AUX LED ranging from 100 to 1400 ms in 100 ms steps. The value 15 puts the AUX LED to the continuous light mode. The activation/deactivation of the AUX LED current source is controlled using only the AUXI register.

Table 13. Auxiliary LED dimming table (1)

| AUXI (hex)           | 0   | 1   | 2   | 3   | 4   | 5   | 6   | 7   | 8    | 9    | Α    | В    | С    | D    | Е    | F    |

|----------------------|-----|-----|-----|-----|-----|-----|-----|-----|------|------|------|------|------|------|------|------|

| AUX LED current [mA] | 0.0 | 1.3 | 2.6 | 4.0 | 5.3 | 6.6 | 8.0 | 9.3 | 10.6 | 12.0 | 13.3 | 14.6 | 16.0 | 17.3 | 18.6 | 20.0 |

<sup>1. 20</sup> mA output current is achievable only if the supply voltage is higher than 3.3 V.

Table 14. Torch mode and flash mode dimming registers settings

| T_DIM<br>(hex)            | 0                                       | 1                                       | 2                                       | 3                                       | 4                                       | 5                                       | 6                                       | 7                                       | 8                                       | 9                                       | Α                                       | В                                       | С               | D               | Е               | F               |                 |                 |                 |                 |                 |                 |                 |                 |

|---------------------------|-----------------------------------------|-----------------------------------------|-----------------------------------------|-----------------------------------------|-----------------------------------------|-----------------------------------------|-----------------------------------------|-----------------------------------------|-----------------------------------------|-----------------------------------------|-----------------------------------------|-----------------------------------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|

| F_DIM<br>(hex)            |                                         |                                         |                                         |                                         |                                         |                                         |                                         |                                         | 0                                       | 1                                       | 2                                       | 3                                       | 4               | 5               | 6               | 7               | 8               | 9               | А               | В               | С               | D               | Е               | F               |

| LED<br>current<br>[mA]    | 16                                      | 19                                      | 23                                      | 27                                      | 32                                      | 39                                      | 46                                      | 55                                      | 65                                      | 77                                      | 92                                      | 109                                     | 124             | 147             | 175             | 209             | 248             | 296             | 352             | 418             | 498             | 592             | 705             | 840             |

| Internal<br>step          | 1                                       | 2                                       | 3                                       | 4                                       | 5                                       | 6                                       | 7                                       | 8                                       | 9                                       | 10                                      | 11                                      | 12                                      | 13              | 14              | 15              | 16              | 17              | 18              | 19              | 20              | 21              | 22              | 23              | 24              |

| V <sub>REF1</sub><br>[mV] | 33                                      | 40                                      | 47                                      | 56                                      | 67                                      | 80                                      | 95                                      | 113                                     | 134                                     | 160                                     | 190                                     | 227                                     | 33              | 40              | 47              | 56              | 67              | 79              | 95              | 113             | 134             | 160             | 190             | 227             |

| Sense<br>Resist.          | R <sub>FL</sub><br>+<br>R <sub>TR</sub> | R <sub>FL</sub> |

Note: LED current values refer to  $R_{FL} = 0.27 \Omega$ ,  $R_{TR} = 1.8 \Omega$ .

22/35 Doc ID 13169 Rev 7

Table 15. Status register

| STAT_REG<br>(read mode)                   | MSB |       |       |       |       |      |     | LSB      |

|-------------------------------------------|-----|-------|-------|-------|-------|------|-----|----------|

| SUB ADD=03                                | N/A | F_RUN | LED_F | NTC_W | NTC_H | OT_F | N/A | VOUTOK_N |

| Power ON,<br>SHUTDOWN MODE<br>RESET Value | 0   | 0     | 0     | 0     | 0     | 0    | 0   | 0        |

### 8.10 F\_RUN

This bit is kept HIGH by the STCF03 during flash mode. By checking this bit, the microprocessor can verify if the flash mode is running or has been terminated by the time counter.

### 8.11 LED\_F

This bit is set by the STCF03 when the voltage seen on the LED pin is  $V_{REF2} > 5.3 \text{ V}$  during a torch or flash operation. This condition can be caused by an open LED, indicating a LED failure. The device automatically goes into ready mode to avoid damage. Internal high frequency filtering avoids false detections. This bit is reset by the STCF03 following a read operation of the STAT\_REG.

### 8.12 NTC W

This bit is set HIGH by the STCF03 and the ATN pin is pulled down, when the voltage seen on the pin  $R_X$  exceeds  $V_{REF4}$  = 0.56 V. This threshold corresponds to a warning temperature value at the LED measured by the NTC. The device is still operating, but a warning is sent to the microprocessor. This bit is reset by the STCF03 following a read operation of the STAT\_REG.

### 8.13 NTC H

This bit is set HIGH by the STCF03 and the ATN pin is pulled down, when the voltage seen on the pin  $R_X$  exceeds  $V_{REF5}$ . This threshold (1.2V) corresponds to an excess temperature value at the LED measured by the NTC. The device is put in Ready mode to avoid damaging the LED. This bit is reset by the STCF03 following a read operation of the STAT\_REG.

### 8.14 OT F

This bit is set HIGH by the STCF03 and the ATN pin is pulled down, when the chip over-temperature protection (~140 °C) has put the device in ready mode. This bit is reset by the STCF03 following a read operation of the STAT\_REG.

### 8.15 VOUTOK\_N

This bit is set by the STCF03. It is used to protect the device, if the output is shorted. The VOUTOK\_N bit is set to HIGH at the start-up. Then a current generator of 20 mA charges the output capacitor for 360 µs typ. and it detects when the output capacitor reaches 100 mV. If this threshold is reached the bit is set to LOW. If the output is shorted to ground or the LED is shorted this threshold is never reached: the bit stays HIGH, ATN pin is pulled down and the device will not start. This bit is reset following a read operation of the STAT\_REG.

Figure 14. VOUTOK\_N behavior

Table 16. Status register details

| Bit Name                         | F_RUN<br>(STAT_REG) | LED_F<br>(STAT_REG) | NTC_W<br>(STAT_REG) | NTC_H<br>(STAT_REG) | OT_F<br>(STAT_REG) | VOUTOK_N<br>(STAT_REG) |

|----------------------------------|---------------------|---------------------|---------------------|---------------------|--------------------|------------------------|

| Default value                    | 0                   | 0                   | 0                   | 0                   | 0                  | 0                      |

| Latched (1)                      | NO                  | YES                 | YES                 | YES                 | YES                | YES                    |

| Forces<br>Ready mode<br>when set | NO                  | YES                 | NO                  | YES                 | YES                | YES                    |

| Sets ATN<br>LOW when<br>set      | NO                  | YES                 | YES                 | YES                 | YES                | YES                    |

YES means that the bit is set by internal signals and is reset to default by an I<sup>2</sup>C read operation of STAT\_REG NO means that the bit is set and reset by internal signals in real-time.

STCF03 Detailed description

### 9 Detailed description

### 9.1 PowerON reset

This mode is initiated by applying a supply voltage above the  $V_{PW\_ON\ RESET}$  threshold value. An internal timing (~1 µs) defines the duration of this status. The logic blocks are powered, but the device doesn't respond to any input. The registers are reset to their default values, the ATN and SDA pins are in high-Z, and the l²C slave address is internally set by reading the ADD pin configuration. After the internally defined time has elapsed, the STCF03 automatically enters the Stand-by mode.

### 9.2 Shutdown, shutdown with NTC

In this mode only the I²C interface is alive, accepting I²C commands and register settings. The device enters this mode: automatically from Power ON reset status; by resetting the PWR\_ON bit from other operation modes. Power consumption is at the minimum (1  $\mu$ A max) if NTC is not activated (NTC\_ON=0). If PWR\_ON and NTC\_ON is set, the T1 is switched ON (see the block diagram), allowing the microprocessor to measure the LED temperature through its A/D converter. When NTC circuits are active and the V<sub>REF-EXT</sub> is present, the typ. current consumption is increased to 1  $\mu$ A, then it is recommended not to leave the STCF03 in this status if battery drain has to be minimized.

### 9.3 Ready mode

In this mode all internal blocks are turned ON, but the DC-DC converter is disabled and the White LED is disconnected. The NTC circuit can be activated to monitor the temperature of the LED and I²C commands and register settings are allowed to be executed immediately. Only in this mode the auxiliary LED is operational and can be turned ON and set at the desired brightness using the AUX REGISTER. The device enters this mode: from Stand-by by setting the PWR\_ON bit; from flash operation by resetting the TRIG pin or the TRIG\_EN bit or automatically from flash operation when the time counter reaches zero; from torch operation by resetting the TCH\_ON bit. The device automatically enters this mode also when an overload or an abnormal condition has been detected during flash or torch operation (*Table 16: Status register details*:).

# 9.4 Single or multiple Flash using external (microprocessor) temporization

To avoid the I²C bus time latency, it is recommended to use the dedicated TRIG pin to define the flash duration (hard-triggering). The TRIG\_EN bit of CMD\_REG should be set before starting each flash operation, because it could have been reset automatically in the previous flash operation. Flash duration is determined by the pulse length that drives the TRIG pin. As soon as the flash is activated, the system needs typically 1.2 ms to ramp up the output current on the power LED. The internal time counter will time-out flash operation and keep the LED dissipated energy within safe limits in case of software deadlock; FTIM register has to be set first, either in stand-by or in ready mode. Multiple flashes are possible by strobing the TRIG pin. Time out counter will cumulate every flash on-time until the defined time out is reached unless it is reloaded by updating the CMD\_REG. If single or multiple flash operation is timed-out, the device automatically goes in Ready mode by resetting the

Detailed description STCF03

TRIG\_EN bit, and also resets the F\_RUN bit. The ATN pin is pulled down to inform the microprocessor that the STAT REG has been updated.

### 9.5 External (microprocessor) temporization using TRIG\_EN bit

Even if it is possible, it is not recommended to use the TRIG\_EN bit to start and stop the flash operation, because of  $I^2C$  bus latencies: this would result in inaccurate flash timing. Nevertheless, if this operation mode is chosen, the TRIG pin has to be kept High (logic level or wired to  $V_{BAT}$ ), leaving the whole flash control to the  $I^2C$  bus. Also in this operation mode the time counter will time-out flash operation and keep the LED dissipated energy dissipated by the LED within safe limits in case of SW deadlock.

### 9.6 Single Flash using internal temporization

Flash triggering can be obtained either by TRIG pin (hard-triggering) or by I2C commands (soft-triggering). The first solution is recommended for an accurate start time, while the second is less accurate because of the I2C bus time latency. Stop time is defined by the STCF03 internal temporization and its accuracy is determined by the internal oscillator. For hard-triggering it is necessary to set the TRIG\_EN bit in advance. For soft-triggering the TRIG pin has to be kept High (logic level or wired to V<sub>BAT</sub>) and the flash can be started by setting the FTIM and the TRIG\_EN through I2C (both are located in the CMD REG). There is a delay time between the moment the flash is triggered and when it appears. This delay is caused by the time necessary to charge up the output capacitor, which is around 1.2 ms depending on battery voltage and output current value. Once triggered, the flash operation will be stopped when the time counter reaches zero. As soon as the flash is finished, the F\_RUN bit is reset, the ATN pin is pulled down for 11 µs to inform the microprocessor that the STAT REG has been updated and the device goes back to ready mode. If it is necessary to make a flash longer than the internal timer allows or a continuous flash, then the FTIM must be reloaded through I2C bus every time, before the internal timer reaches zero. For example: To get a continuous flash, set FTIM to 1.5 s and every 1 s reload the CMD REG.

### 9.7 Multiple Flash using internal temporization

This operation has to be processed as a sequence of single flashes using internal temporization starting from hard or soft triggering. Since the TRIG\_EN bit is reset at the end of each flash, it is necessary to reload the CMD\_REG to start the next one.

26/35 Doc ID 13169 Rev 7

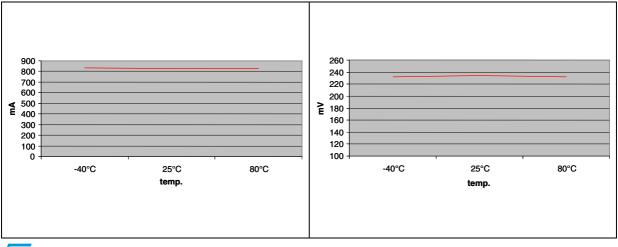

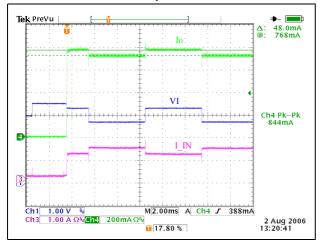

# 10 Typical performance characteristics

Figure 15. Efficiency

Figure 16. I<sub>OTORCH</sub> vs. T\_DIMM

Figure 17. I<sub>OFLASH</sub> vs. F\_DIMM

Figure 18. I<sub>OAUX</sub> vs. AUXI

Figure 19.  $I_{OFLASH}$  vs. temp.  $V_I = 3.3V$

Figure 20. VFB2 vs. temp. at  $I_0$  = 800mA,  $V_1$  = 3.3V

577

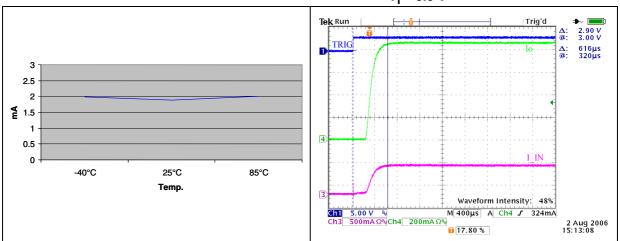

Figure 21.  $I_Q$  vs. temp.  $V_I$  = 5.5 V ready-mode Figure 22. Start-up in flash mode 800 mA at  $V_I$  = 3.6 V

Figure 23. Line transient in flash mode 800 mA, change of  $V_{I}$  from 2.7 V to 3.3 V in 10  $\mu s$

28/35 Doc ID 13169 Rev 7

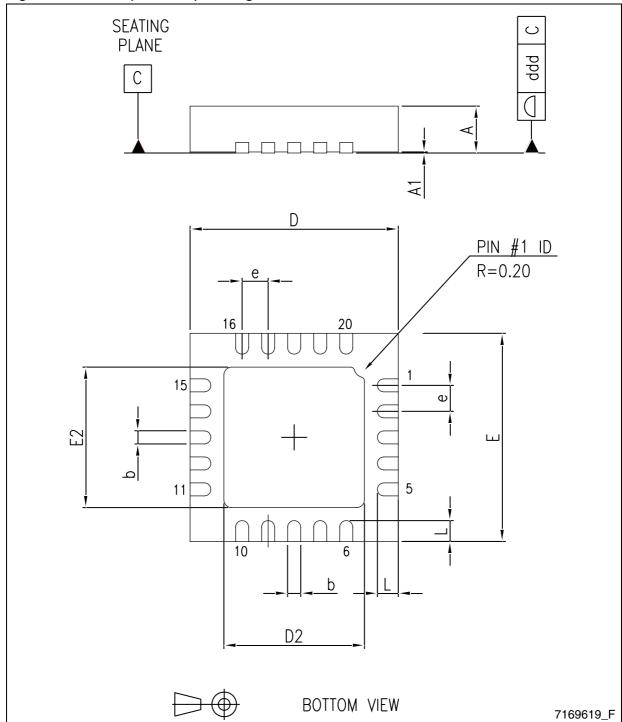

# 11 Package mechanical data

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: <a href="https://www.st.com">www.st.com</a>. ECOPACK<sup>®</sup> is an ST trademark.

Table 17. QFN20 (4 x 4 mm.) mechanical data

| Dim.   |      | mm.  |      |

|--------|------|------|------|

| Diiii. | Min. | Тур. | Max. |

| A      | 0.80 | 0.90 | 1.00 |

| A1     |      | 0.02 | 0.05 |

| b      | 0.18 | 0.25 | 0.30 |

| D      | 3.85 | 4.00 | 4.15 |

| D2     | 2.55 | 2.70 | 2.80 |

| E      | 3.85 | 4.00 | 4.15 |

| E2     | 2.55 | 2.70 | 2.80 |

| е      | 0.45 | 0.50 | 0.55 |

| L      | 0.30 | 0.40 | 0.50 |

| ddd    |      |      | 0.08 |

Figure 24. QFN20 (4 x 4 mm.) drawing

### **TFBGA25** mechanical data

| Dim. |      | mm.  |      |       | mils. |       |

|------|------|------|------|-------|-------|-------|

| Dim. | Min. | Тур. | Max. | Min.  | Тур.  | Max.  |

| А    | 1.0  | 1.1  | 1.16 | 39.4  | 43.3  | 45.7  |

| A1   |      |      | 0.25 |       |       | 9.8   |

| A2   | 0.78 |      | 0.86 | 30.7  |       | 33.9  |

| b    | 0.25 | 0.30 | 0.35 | 9.8   | 11.8  | 13.8  |

| D    | 2.9  | 3.0  | 3.1  | 114.2 | 118.1 | 122.0 |

| D1   |      | 2    |      |       | 78.8  |       |

| E    | 2.9  | 3.0  | 3.1  | 114.2 | 118.1 | 122.0 |

| E1   |      | 2    |      |       | 78.8  |       |

| е    |      | 0.5  |      |       | 19.7  |       |

| SE   |      | 0.25 |      |       | 9.8   |       |

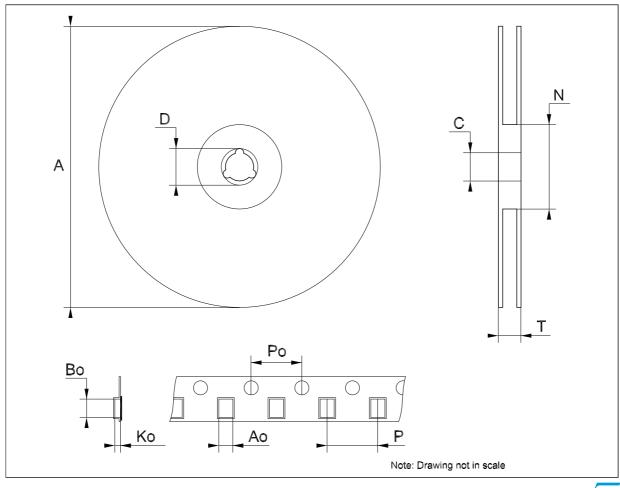

# Tape & reel QFNxx/DFNxx (4x4) mechanical data

| Dim.   |      | mm.  |      |       | inch. |        |

|--------|------|------|------|-------|-------|--------|

| Dilli. | Min. | Тур. | Max. | Min.  | Тур.  | Max.   |

| Α      |      |      | 330  |       |       | 12.992 |

| С      | 12.8 |      | 13.2 | 0.504 |       | 0.519  |

| D      | 20.2 |      |      | 0.795 |       |        |

| N      | 99   |      | 101  | 3.898 |       | 3.976  |

| Т      |      |      | 14.4 |       |       | 0.567  |

| Ao     |      | 4.35 |      |       | 0.171 |        |

| Во     |      | 4.35 |      |       | 0.171 |        |

| Ko     |      | 1.1  |      |       | 0.043 |        |

| Ро     |      | 4    |      |       | 0.157 |        |

| Р      |      | 8    |      |       | 0.315 |        |

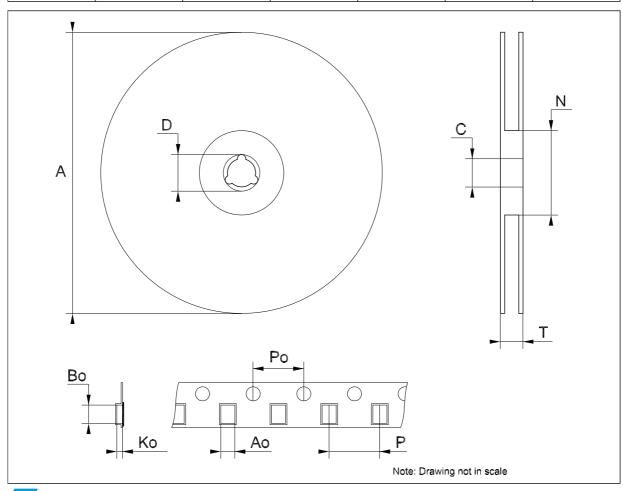

# Tape & reel TFBGA25 mechanical data

| Dim. | mm.  |      |      | inch. |       |        |

|------|------|------|------|-------|-------|--------|

|      | Min. | Тур. | Max. | Min.  | Тур.  | Max.   |

| Α    |      |      | 330  |       |       | 12.992 |

| С    | 12.8 |      | 13.2 | 0.504 |       | 0.519  |

| D    | 20.2 |      |      | 0.795 |       |        |

| N    | 60   |      |      | 2.362 |       |        |

| Т    |      |      | 14.4 |       |       | 0.567  |

| Ao   |      | 3.3  |      |       | 0.130 |        |

| Во   |      | 3.3  |      |       | 0.130 |        |

| Ko   |      | 1.60 |      |       | 0.063 |        |

| Po   | 3.9  |      | 4.1  | 0.153 |       | 0.161  |

| Р    | 7.9  |      | 8.1  | 0.311 |       | 0.319  |

Revision history STCF03

# 12 Revision history

Table 18. Document revision history

| Date        | Revision | Changes                                                               |  |

|-------------|----------|-----------------------------------------------------------------------|--|

| 30-Jan-2007 | 1        | First release.                                                        |  |

| 27-Mar-2007 | 2        | The OVP min. value on table 5 is changed: 5.5 V ==> 5.3 V.            |  |

| 28-Aug-2007 | 3        | Modified <i>Table 5</i> .                                             |  |

| 12-Sep-2007 | 4        | Modified Figure 2.                                                    |  |

| 10-Sep-2008 | 5        | Added Figure 4 on page 14.                                            |  |

| 24-Aug-2010 | 6        | Updated mechanical data.                                              |  |

| 23-Feb-2011 | 7        | Updated mechanical data Table 17 on page 29 and Figure 24 on page 30. |  |

#### Please Read Carefully:

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY AN AUTHORIZED ST REPRESENTATIVE, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER'S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2011 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com