The MAX196/MAX198 multirange, 12-bit data-acquisition systems (DAS) require only a single +5V supply for operation, yet convert analog signals at their inputs up to ±10V (MAX196) and ±4V (MAX198). These systems provide six analog input channels that are independently software programmable for a variety of ranges:  $\pm 10V$ ,  $\pm 5V$ , 0V to  $\pm 10V$ , and 0V to  $\pm 5V$  for the MAX196; ±VREF, ±VREF/2, 0V to +VREF, and 0V to +VREF/2 for the MAX198. This range switching increases the effective dynamic range to 14 bits and provides the flexibility to interface ±12V, ±15V, and 4mA to 20mA powered sensors to a single +5V system. In addition, these converters are fault protected to ±16.5V; a fault condition on any channel will not affect the conversion result of the selected channel. Other features include a 5MHz bandwidth track/hold, 100ksps throughput rate, software-selectable internal/external clock, internal/external acquisition control, 12-bit parallel interface, and internal 4.096V or external reference.

Two programmable power-down modes (STBYPD, FULLPD) provide low-current shutdown between conversions. In STBYPD mode, the reference buffer remains active, eliminating start-up delays.

The MAX196/MAX198 employ a standard microprocessor (µP) interface. A three-state data I/O port is configured to operate with 16-bit data buses, and dataaccess and bus-release timing specifications are compatible with most popular µPs. All logic inputs and outputs are TTL/CMOS compatible.

These devices are available in 28-pin DIP, wide SO, SSOP (55% smaller in area than wide SO), and ceramic SB packages. For 8+4 bus interface, see the MAX197 and the MAX199 data sheets. An evaluation kit will be available after December 1995 (MAX196EVKIT-DIP).

#### Applications

Industrial-Control Systems Robotics **Data-Acquisition Systems** Automatic Testing Systems Medical Instruments Telecommunications

Features

- ♦ 12-Bit Resolution, 1/2LSB Linearity

- **♦ Single +5V Supply Operation**

- **♦** Software-Selectable Input Ranges: ±10V, ±5V, 0V to +10V, 0V to +5V (MAX196) ±VREF, ±VREF/2, 0V to +VREF, 0V to +VREF/2 (MAX198)

- ♦ Internal 4.096V or External Reference

- ◆ Fault-Protected Input Multiplexer

- 6 Analog Input Channels

- ♦ 6µs Conversion Time, 100ksps Sampling Rate

- ♦ Internal or External Acquisition Control

- ♦ Two Power-Down Modes

- Internal or External Clock

#### Ordering Information

| PART       | TEMP. RANGE  | PIN-PACKAGE           |

|------------|--------------|-----------------------|

| MAX196ACNI | 0°C to +70°C | 28 Narrow Plastic DIP |

| MAX196BCNI | 0°C to +70°C | 28 Narrow Plastic DIP |

| MAX196ACWI | 0°C to +70°C | 28 Wide SO            |

| MAX196BCWI | 0°C to +70°C | 28 Wide SO            |

| MAX196ACAI | 0°C to +70°C | 28 SSOP               |

| MAX196BCAI | 0°C to +70°C | 28 SSOP               |

Ordering Information continued at end of data sheet.

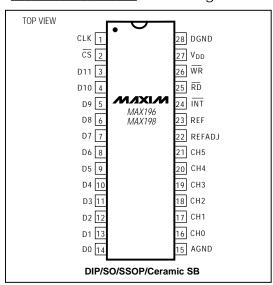

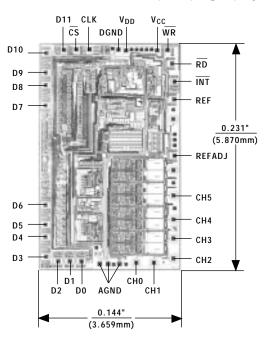

#### Pin Configuration

Functional Diagram appears at end of data sheet.

MIXIM

Maxim Integrated Products 1

Call toll free 1-800-722-8266 for free samples or literature.

### **ABSOLUTE MAXIMUM RATINGS**

| VDD to AGND. -0.3V to +7V   AGND to DGND. -0.3V to +0.3V   REF to AGND. -0.3V to (VDD + 0.3V)   REFADJ to AGND. -0.3V to (VDD + 0.3V) | Wide SO (derate 12.50mW/°C above +70°C)1000mW<br>SSOP (derate 9.52mW/°C above +70°C) |

|---------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|

| Digital Inputs to DGND                                                                                                                | MAX196_C_ I/MAX198_C_ I                                                              |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ )<br>Narrow Plastic DIP (derate 14.29mW/ $^{\circ}C$ above $+70^{\circ}C$ )1143mW | Storage Temperature Range65°C to +150°C Lead Temperature (soldering, 10sec)+300°C    |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{DD}$  = 5V ±5%; unipolar/bipolar range; external reference mode,  $V_{REF}$  = 4.096V; 4.7 $\mu F$  at REF pin; external clock,  $f_{CLK}$  = 2.0MHz with 50% duty cycle;  $T_A$  =  $T_{MIN}$  to  $T_{MAX}$ ; unless otherwise noted. Typical values are at  $T_A$  = +25°C.)

| PARAMETER                          | SYMBOL     | CONDITIONS                         |                                                              | MIN                     | TYP       | MAX      | UNITS  |

|------------------------------------|------------|------------------------------------|--------------------------------------------------------------|-------------------------|-----------|----------|--------|

| ACCURACY (Note 1)                  | !          | !                                  |                                                              |                         |           |          | ·      |

| Resolution                         |            |                                    |                                                              | 12                      |           |          | Bits   |

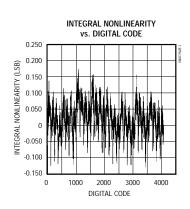

| Integral Naplinearity              | INI        | MAX196A                            | /MAX198A                                                     |                         |           | ±1/2     | LSB    |

| Integral Nonlinearity              | IINL       | MAX196B                            | /MAX198B                                                     |                         |           | ±1       | LSB    |

| Differential Nonlinearity          | DNL        |                                    |                                                              |                         |           | ±1       | LSB    |

|                                    |            | Unipolar                           | MAX196A/MAX198A                                              |                         |           | ±3       |        |

| Offset Error                       |            | Unipolai                           | MAX196B/MAX198B                                              |                         |           | ±5       | LSB    |

| Oliset Elloi                       |            | Bipolar                            | MAX196A/MAX198A                                              |                         |           | ±5       | LJD    |

|                                    |            | ыриаі                              | MAX196B/MAX198B                                              |                         |           | ±10      |        |

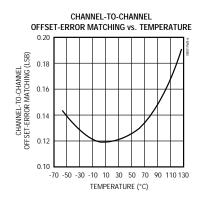

| Channel-to-Channel Offset          |            | Unipolar                           |                                                              |                         | ±0.1      |          | LSB    |

| Error Matching                     |            | Bipolar                            |                                                              |                         | ±0.5      |          | LJD    |

|                                    |            | Unipolar                           | MAX196A/MAX198A                                              |                         |           | ±7       |        |

| Gain Error                         |            | Ornpolai                           | MAX196B/MAX198B                                              |                         |           | ±10      | LSB    |

| (Note 2)                           |            | Bipolar                            | MAX196A/MAX198A                                              |                         |           | ±7       |        |

|                                    |            | ырога                              | MAX196B/MAX198B                                              |                         |           | ±10      |        |

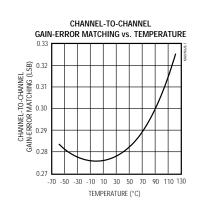

| Gain Temperature Coefficient       |            | Unipolar                           |                                                              |                         | 3         |          | ppm/°C |

| (Note 2)                           |            | Bipolar                            |                                                              |                         | 5         |          | ррии С |

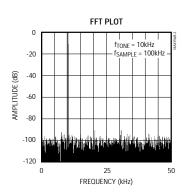

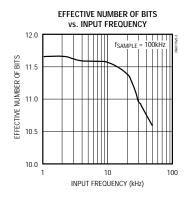

| DYNAMIC SPECIFICATIONS (10         | kHz sine-w | ave input, ±                       | 10Vp-p (MAX196) or $\pm 4.096$ Vp-p (MA                      | X198), f <sub>S</sub> , | AMPLE = 1 | 100ksps) |        |

| Signal-to-Noise + Distortion Ratio | SINAD      | MAX196A                            | /MAX198A                                                     | 70                      |           |          | dB     |

| Signal-to-Noise + Distortion Ratio | SINAD      | MAX196B                            | /MAX198B                                                     | 69                      |           |          | ub ub  |

| Total Harmonic Distortion          | THD        | Up to the                          | 5th harmonic                                                 |                         | -85       | -78      | dB     |

| Spurious-Free Dynamic Range        | SFDR       |                                    |                                                              | 80                      |           |          | dB     |

| Channel-to-Channel Crosstalk       |            | 50kHz, V <sub>II</sub><br>(Note 3) | $_{N} = \pm 5V \text{ (MAX196) or } \pm 4V \text{ (MAX198)}$ |                         | -86       |          | dB     |

| Aperture Delay                     |            | External C                         | LK mode/external acquisition control                         |                         | 15        |          | ns     |

|                                    |            | External C                         | LK mode/external acquisition control                         |                         | <50       |          | ps     |

| Aperture Jitter                    |            | Internal C<br>control (N           | LK mode/internal acquisition ote 4)                          |                         | 10        |          | ns     |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = 5V \pm 5\%; unipolar/bipolar range; external reference mode, V_{REF} = 4.096V; 4.7 \mu F at REF pin; external clock, f_{CLK} = 2.0 MHz with 50% duty cycle; T_A = T_{MIN} to T_{MAX}; unless otherwise noted. Typical values are at T_A = +25 °C.)$

| PARAMETER                                                    | SYMBOL              | CONDITIONS                           |                   | MIN                                | TYP                  | MAX    | UNITS               |                |    |

|--------------------------------------------------------------|---------------------|--------------------------------------|-------------------|------------------------------------|----------------------|--------|---------------------|----------------|----|

| ANALOG INPUT                                                 |                     |                                      |                   |                                    | '                    |        |                     |                |    |

| Track/Hold Acquisition Time                                  |                     | fcLK = 2.0                           | )MHz              |                                    |                      |        | 3                   | μs             |    |

|                                                              |                     |                                      | ±10V or ±         | V <sub>REF</sub> range             |                      | 5      |                     |                |    |

| Small Signal Bandwidth                                       |                     | -3dB                                 |                   | / <sub>REF</sub> /2 range          |                      | 2.5    |                     | MHz            |    |

| Small-Signal Bandwidth                                       |                     | rolloff                              | 0V to 10V         | or 0V to V <sub>REF</sub> range    |                      | 2.5    |                     | IVIHZ          |    |

|                                                              |                     |                                      | 0V to 5V o        | or 0V to V <sub>REF</sub> /2 range |                      | 1.25   |                     |                |    |

|                                                              |                     |                                      | MAX196            |                                    | 0                    |        | 10                  |                |    |

|                                                              |                     | Unipolar                             | IVIAXT70          |                                    | 0                    |        | 5                   |                |    |

|                                                              |                     | Unipolai                             | MAX198            |                                    | 0                    |        | VREF                |                |    |

| Input Voltage Range                                          | VIN                 |                                      | IVIAA 190         |                                    | 0                    |        | V <sub>REF</sub> /2 | \ <sub>\</sub> |    |

| (see Table 3)                                                | VIN                 |                                      | MAN/10/           |                                    | -10                  |        | 10                  | 1 <sup>v</sup> |    |

|                                                              |                     | Dinolor                              | MAX196            |                                    | -5                   |        | 5                   |                |    |

|                                                              |                     | Bipolar                              | MAY100            |                                    | -VREF                |        | VREF                |                |    |

|                                                              |                     |                                      | MAX198            |                                    | -V <sub>REF</sub> /2 |        | V <sub>REF</sub> /2 |                |    |

|                                                              |                     |                                      | MAX196            | 0V to 10V range                    |                      |        | 720                 |                |    |

|                                                              |                     | Unipolar                             | IVIAX 196         | 0V to 5V range                     |                      |        | 360                 | -              |    |

|                                                              |                     |                                      | MAX198            |                                    |                      | 0.1    | 10                  |                |    |

| Input Current                                                | liN                 |                                      | MAX19<br>Bipolar  | MAV104                             | ±10V range           | -1200  |                     | 720            | μA |

|                                                              |                     |                                      |                   |                                    | ±5V range            | -600   |                     | 360            |    |

|                                                              |                     | ырогаг                               | MAX198            | ±V <sub>REF</sub> range            | -1200                |        | 10                  |                |    |

|                                                              |                     |                                      | IVIAA 190         | ±V <sub>REF</sub> /2 range         | -600                 |        | 10                  |                |    |

| Input Resistance                                             | ΔVIN                | Unipolar                             |                   |                                    |                      | 21     |                     | kΩ             |    |

| input Resistance                                             | $\Delta I_{IN}$     | Bipolar                              |                   |                                    |                      | 16     |                     | N22            |    |

| Input Capacitance                                            |                     | (Note 5)                             |                   |                                    |                      |        | 40                  | pF             |    |

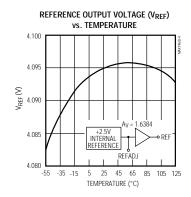

| INTERNAL REFERENCE                                           |                     |                                      |                   |                                    |                      |        |                     |                |    |

| REF Output Voltage                                           | VREF                | T <sub>A</sub> = +25°                | ,C                |                                    | 4.076                | 4.096  | 4.116               | V              |    |

| REF Output Tempco                                            |                     | MAX196_C/MAX198_C                    |                   |                                    | 15                   |        |                     |                |    |

| (Contact Maxim Applications for guaranteed temperature drift | TC V <sub>REF</sub> | MAX196_                              | E/MAX198_         | E                                  |                      | 30     |                     | ppm/°C         |    |

| specifications)                                              |                     |                                      | MAX196_M/MAX198_M |                                    |                      | 40     |                     |                |    |

| Output Short-Circuit Current                                 |                     |                                      |                   |                                    |                      |        | 30                  | mA             |    |

| Load Regulation                                              |                     | 0mA to 0.5mA output current (Note 6) |                   |                                    |                      | 10     | mV                  |                |    |

| Capacitive Bypass at REF                                     |                     |                                      |                   |                                    | 4.7                  |        |                     | μF             |    |

| REFADJ Output Voltage                                        |                     |                                      |                   |                                    | 2.465                | 2.500  | 2.535               | V              |    |

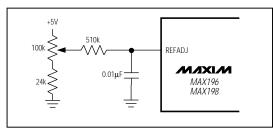

| REFADJ Adjustment Range                                      |                     | With recor                           | mmended c         | ircuit (Figure 1)                  |                      | ±1.5   |                     | %              |    |

| Buffer Voltage Gain                                          |                     |                                      |                   |                                    |                      | 1.6384 |                     | V/V            |    |

## **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = 5V \pm 5\%; unipolar/bipolar range; external reference mode, V_{REF} = 4.096V; 4.7 \mu F at REF pin; external clock, f_{CLK} = 2.0 MHz with 50% duty cycle; T_A = T_{MIN} to T_{MAX}; unless otherwise noted. Typical values are at T_A = <math>+25$ °C.)

| PARAMETER                              | SYMBOL            | CONDITIONS               |                                        | MIN                         | TYP                  | MAX       | UNITS |      |  |

|----------------------------------------|-------------------|--------------------------|----------------------------------------|-----------------------------|----------------------|-----------|-------|------|--|

| REFERENCE INPUT (buffer disa           | bled, refere      | nce input ap             | plied to REF p                         | in)                         |                      |           |       |      |  |

| Input Voltage Range                    |                   |                          |                                        |                             | 2.4                  |           | 4.18  | V    |  |

| Input Current                          | rent              |                          | Normal, or S<br>power-down             |                             |                      |           | 400   | μA   |  |

|                                        |                   | 4.18V                    | FULL power-                            | -down mode                  |                      |           | 1     |      |  |

| Input Resistance                       |                   | Normal, or               | STANDBY pov                            | ver-down mode               | 10                   |           |       | kΩ   |  |

| •                                      |                   | FULL powe                | er-down mode                           |                             | 5                    |           |       | МΩ   |  |

| REFADJ Threshold for<br>Buffer Disable |                   |                          |                                        |                             | V <sub>DD</sub> - 50 | mV        |       | V    |  |

| POWER REQUIREMENTS                     |                   |                          |                                        |                             |                      |           |       |      |  |

| Supply Voltage                         | V <sub>DD</sub>   |                          |                                        |                             | 4.75                 |           | 5.25  | V    |  |

|                                        |                   | Normal mo                | de, bipolar rai                        | nges                        |                      |           | 18    | mA   |  |

| Supply Current                         | IDD               | Normal mo                | de, unipolar ra                        | anges                       |                      | 6         | 10    | IIIA |  |

| Supply Current                         | טטי               |                          | power-down n                           |                             |                      | 700       | 850   | μA   |  |

|                                        |                   |                          | er-down mode                           | ` '                         |                      | 60        | 120   | μπ   |  |

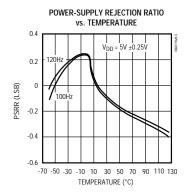

| Power-Supply Rejection Ratio           | PSRR              | External re              | ference = 4.09                         | 96V                         |                      | ±0.1      | ±1/2  | LSB  |  |

| (Note 8)                               | 1 JKK             | Internal ref             | erence                                 |                             |                      | $\pm 1/2$ |       | LJD  |  |

| TIMING                                 |                   |                          |                                        |                             |                      |           |       |      |  |

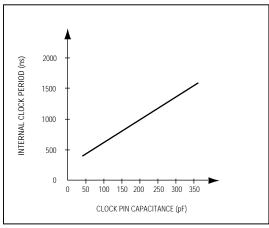

| Internal Clock Frequency               | fCLK              | C <sub>CLK</sub> = 100pF |                                        | 1.25                        | 1.56                 | 2.00      | MHz   |      |  |

| External Clock Frequency Range         | fCLK              |                          |                                        |                             | 0.1                  |           | 2.0   | MHz  |  |

|                                        | t. 001            | and Internal and         | t <sub>ACQI</sub> Internal acquisition | quicition                   | External CLK         | 3.0       |       |      |  |

| Acquisition Time                       | IACQI             | internal ac              | quisition                              | Internal CLK                | 3.0                  |           | 5.0   | μs   |  |

| Acquisition fillie                     | tacor             | External ac              | equisition (Note                       | e 9)                        | 3.0                  |           |       | μ3   |  |

|                                        | t <sub>ACQE</sub> | After FULL               | PD or STBYPE                           | )                           |                      | 5         |       |      |  |

| Conversion Time                        | tconv             | External Cl              | _K                                     |                             | 6.0                  |           |       | μs   |  |

| Conversion Time                        | ICONV             | Internal CL              | K, C <sub>CLK</sub> = 100              | )pF                         | 6.0                  | 7.7       | 10.0  | μ3   |  |

| Throughput Rate                        |                   | External Cl              | _K                                     |                             |                      |           | 100   | ksps |  |

| mioughput Nate                         |                   | Internal CL              | Internal CLK, C <sub>CLK</sub> = 100pF |                             | 62                   |           |       | KSPS |  |

| Bandgap Reference<br>Start-Up Time     |                   | Power-up (               | Note 10)                               |                             |                      | 200       |       | μs   |  |

| Reference Buffer Settling              |                   | To 0.1mV F               | REF bypass<br>Illy discharged          | CREF = 4.7µF<br>CREF = 33µF |                      | 8         |       | ms   |  |

| DIGITAL INPUTS (D7-D0, CLK,            | RD, WR, CS        | ) (Note 11)              | ·                                      | 1 1                         |                      |           |       | I    |  |

| Input High Voltage                     | VINH              | ,                        |                                        |                             | 2.4                  |           |       | V    |  |

| Input Low Voltage                      | VINL              |                          |                                        |                             |                      |           | 0.8   | V    |  |

| Input Leakage Current                  | lin               | VINI = OV O              | VIN = 0V or VDD                        |                             |                      |           | ±10   | μA   |  |

| Input Capacitance                      | CIN               | (Note 5)                 |                                        |                             |                      |           | 15    | pF   |  |

| тра опраснансе                         | L                 | (14016 3)                |                                        |                             |                      |           | 10    |      |  |

4 \_\_\_\_\_\_M/XI/M

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = 5V \pm 5\%; unipolar/bipolar range; external reference mode, V_{REF} = 4.096V; 4.7 \mu F$  at REF pin; external clock, f<sub>CLK</sub> = 2.0MHz with 50% duty cycle; T<sub>A</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>; unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C.)

| PARAMETER                      | SYMBOL          | CONDITIONS                                         | MIN                 | TYP | MAX | UNITS |

|--------------------------------|-----------------|----------------------------------------------------|---------------------|-----|-----|-------|

| DIGITAL OUTPUTS (D11-D0, INT)  |                 |                                                    |                     |     |     |       |

| Output Low Voltage             | Vol             | $V_{DD} = 4.75V$ , $I_{SINK} = 1.6mA$              |                     |     | 0.4 | V     |

| Output High Voltage            | V <sub>OH</sub> | V <sub>DD</sub> = 4.75V, I <sub>SOURCE</sub> = 1mA | V <sub>DD</sub> - 1 |     |     | V     |

| Three-State Output Capacitance | Cout            | (Note 5)                                           |                     |     | 15  | pF    |

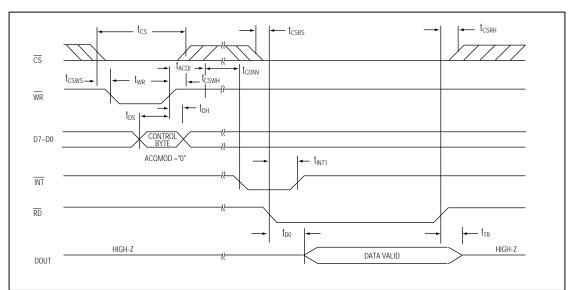

#### **TIMING CHARACTERISTICS**

$(V_{DD} = 5V \pm 5\%)$ ; unipolar/bipolar range; external reference mode,  $V_{REF} = 4.096V$ ;  $4.7\mu F$  at REF pin; external clock,  $f_{CLK} = 2.0MHz$  with 50% duty cycle;  $T_A = T_{MIN}$  to  $T_{MAX}$ ; unless otherwise noted.)

| PARAMETER                   | SYMBOL          | CONDITIONS                                 | MIN | TYP | MAX | UNITS |

|-----------------------------|-----------------|--------------------------------------------|-----|-----|-----|-------|

| CS Pulse Width              | tcs             |                                            | 80  |     |     | ns    |

| WR Pulse Width              | t <sub>WR</sub> |                                            | 80  |     |     | ns    |

| CS to WR Setup Time         | tcsws           |                                            | 0   |     |     | ns    |

| CS to WR Hold Time          | tcswh           |                                            | 0   |     |     | ns    |

| CS to RD Setup Time         | tcsrs           |                                            | 0   |     |     | ns    |

| CS to RD Hold Time          | tcsrh           |                                            | 0   |     |     | ns    |

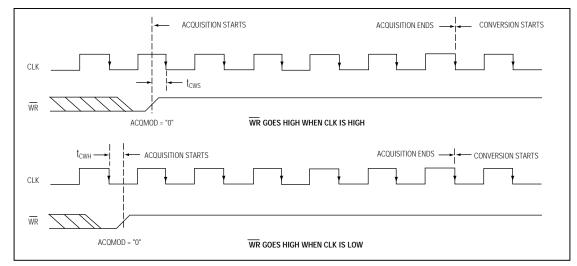

| CLK to WR Setup Time        | tcws            |                                            |     |     | 100 | ns    |

| CLK to WR Hold Time         | tcwh            |                                            |     |     | 50  | ns    |

| Data Valid to WR Setup      | t <sub>DS</sub> |                                            | 60  |     |     | ns    |

| Data Valid to WR Hold       | tDH             |                                            | 0   |     |     | ns    |

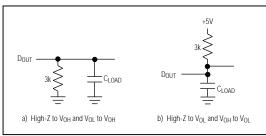

| RD Low to Output Data Valid | tDO             | Figure 2, C <sub>L</sub> = 100pF (Note 12) |     |     | 120 | ns    |

| RD High to Output Disable   | tTR             | (Note 13)                                  |     |     | 70  | ns    |

| RD Low to INT High Delay    | tINT1           |                                            |     |     | 120 | ns    |

- Note 1: Accuracy specifications tested at V<sub>DD</sub> = 5.0V. Performance at power-supply tolerance limits guaranteed by Power-Supply Rejection test. Tested for the ±10V (MAX196) and ±4.096V (MAX198) input ranges.

- Note 2: External reference: V<sub>REF</sub> = 4.096V, offset error nulled, ideal last code transition = FS 3/2LSB.

- Note 3: Ground "on" channel; sine wave applied to all "off" channels.

- Note 4: Maximum full-power input frequency for 1LSB error with 10ns jitter = 3kHz.

- Note 5: Guaranteed by design. Not tested.

- Note 6: Use static loads only.

- Note 7: Tested using internal reference.

- Note 8: PSRR measured at full-scale.

- Note 9: External acquisition timing: starts at data valid at ACQMOD = low control byte; ends at rising edge of WR with ACQMOD = high control byte.

- **Note 10:** Not subject to production testing. Provided for design guidance only.

- **Note 11:** All input control signals specified with  $t_R = t_F = 5$ ns from a voltage level of 0.8V to 2.4V.

- Note 12: tpo is measured with the load circuits of Figure 2 and defined as the time required for an output to cross 0.8V or 2.4V.

- Note 13:  $t_{TR}$  is defined as the time required for the data lines to change by 0.5V.

\_Typical Operating Characteristics

$(T_A = +25^{\circ}C, unless otherwise noted.)$

\_Pin Description

| PIN   | NAME            | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

|-------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| 1     | CLK             | Clock Input. In external clock mode, drive CLK with a TTL/CMOS-compatible clock. In internal clock mode, place a capacitor ( $C_{CLK}$ ) from this pin to ground to set the internal clock frequency; $f_{CLK} = 1.56 MHz$ typical with $C_{CLK} = 100 pF$ .                                                                                                                                                |  |  |  |  |  |

| 2     | CS              | Chip Select, active low                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| 3–14  | D11-D0          | Three-State Digital I/O, D11 = MSB                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| 15    | AGND            | Analog Ground                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| 16-21 | CH0-CH5         | Analog Input Channels                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

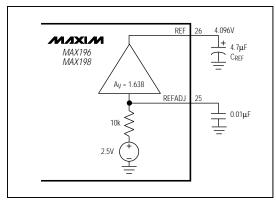

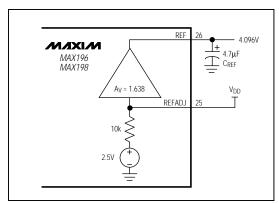

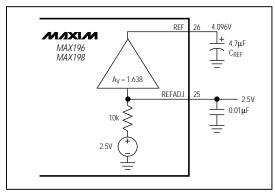

| 22    | REFADJ          | Bandgap Voltage-Reference Output/External Adjust Pin. Bypass with a $0.01\mu F$ capacitor to AGND. Connect to $V_{DD}$ when using an external reference at the REF pin.                                                                                                                                                                                                                                     |  |  |  |  |  |

| 23    | REF             | Reference Buffer Output/ADC Reference Input. In internal reference mode, the reference buffer provides a 4.096V nominal output, externally adjustable at REFADJ. In external reference mode, disable the internal buffer by pulling REFADJ to VDD.                                                                                                                                                          |  |  |  |  |  |

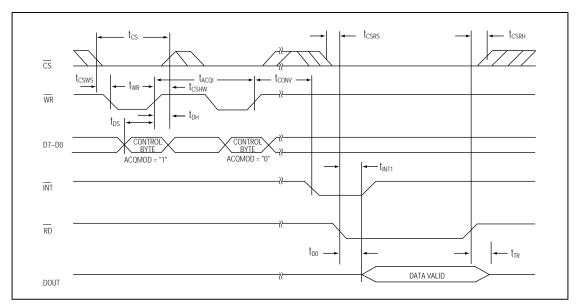

| 24    | ĪNT             | INT goes low when conversion is complete and output data is ready.                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| 25    | RD              | If $\overline{\text{CS}}$ is low, a falling edge on $\overline{\text{RD}}$ will enable a read operation on the data bus.                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| 26    | WR              | In the internal acquisition mode, when $\overline{CS}$ is low, a rising edge on $\overline{WR}$ latches in configuration data and starts an acquisition plus a conversion cycle. In the external acquisition mode, when $\overline{CS}$ is low, the first rising edge on $\overline{WR}$ starts an acquisition, and a second rising edge on $\overline{WR}$ ends acquisition and starts a conversion cycle. |  |  |  |  |  |

| 27    | V <sub>DD</sub> | +5V Supply. Bypass with 0.1μF capacitor to AGND.                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| 28    | DGND            | Digital Ground                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

Figure 1. Reference-Adjust Circuit

Figure 2. Load Circuits for Enable Time

## Detailed Description

#### Converter Operation

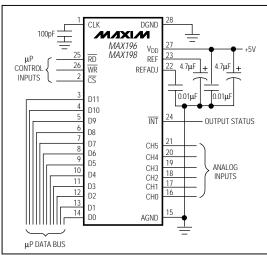

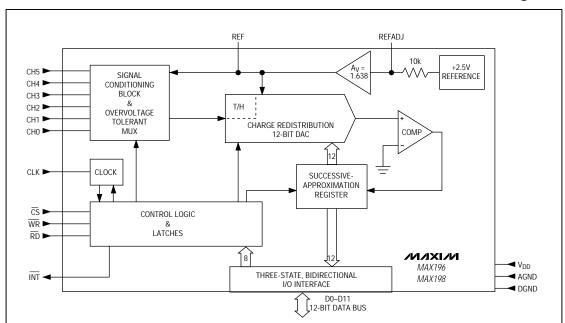

The MAX196/MAX198 multirange, fault-tolerant ADCs use successive approximation and internal input track/hold (T/H) circuitry to convert an analog signal to a 12-bit digital output. The 12-bit parallel-output format provides easy interface to microprocessors ( $\mu$ Ps). Figure 3 shows the MAX196/MAX198 in the simplest operational configuration.

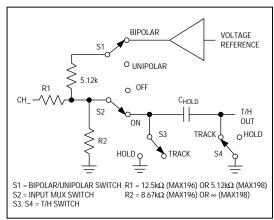

### Analog-Input Track/Hold

In the internal acquisition control mode (control bit D5 set to 0), the T/H enters its tracking mode on  $\overline{WR}$ 's rising edge, and enters its hold mode when the internally timed (6 clock cycles) acquisition interval ends. In bipolar mode and unipolar mode (MAX196 only), a low-impedance input source, which settles in less than 1.5 $\mu$ s, is required to maintain conversion accuracy at the maximum conversion rate.

When the MAX198 is configured for unipolar mode, the input does not need to be driven from a low-impedance source. The acquisition time  $(t_{AZ})$  is a function of the source output resistance  $(R_S)$ , the channel input resistance  $(R_{IN})$ , and the T/H capacitance.

Acquisition time is calculated as follows:

For OV to  $V_{REF}$ :  $t_{AZ} = 9 \text{ x } (R_S + R_{IN}) \text{ x } 16pF$ For OV to  $V_{REF}/2$ :  $t_{AZ} = 9 \text{ x } (R_S + R_{IN}) \text{ x } 32pF$

where  $R_{IN}=7k\Omega$  and  $t_{AZ}$  is never less than 2µs (0V to V\_{REF} range) or 3µs (0V to V\_{REF}/2 range).

In the external acquisition control mode (D5 = 1), the T/H enters its tracking mode on the first  $\overline{WR}$  rising edge and enters its hold mode when it detects the second  $\overline{WR}$  rising edge with D5 = 0 (see *External Acquisition* section).

Figure 3. Operational Diagram

Figure 4. Equivalent Input Circuit

#### Input Bandwidth

The ADC's input tracking circuitry has a 5MHz small-signal bandwidth. When using the internal acquisition mode with an external clock frequency of 2MHz, a 100ksps throughput rate can be achieved. It is possible to digitize high-speed transient events and measure periodic signals with bandwidths exceeding the ADC's sampling rate by using undersampling techniques. To avoid high-frequency signals being aliased into the frequency band of interest, anti-alias filtering is recommended (MAX274/MAX275 continuous-time filters).

### Input Range and Protection

Figure 4 shows the equivalent input circuit. The full-scale input voltage depends on the voltage at the reference (VREF). The MAX196 uses a scaling factor, which allows input voltage ranges of  $\pm 10V$ ,  $\pm 5V$ , 0V to  $\pm 10V$ , or 0V to  $\pm 5V$  with a 4.096V voltage reference (Table 1). Program the desired range by setting the appropriate control bits (D3, D4) in the control byte (Tables 2 and 3). The MAX198 does not use a scaling factor, so its input voltage range directly corresponds with the reference voltage. It can be programmed for input voltages of  $\pm VREF$ ,  $\pm VREF/2$ , 0V to VREF, or 0V to VREF/2 (Table 3). When an external reference is applied at REFADJ, the voltage at REF is given by  $VREF = 1.6384 \times VREFADJ$  (2.4V < VREF < 4.18V).

The input channels are overvoltage protected to  $\pm 16.5V$ . This protection is active even if the device is in power-down mode.

Even with  $V_{DD} = 0V$ , the input resistive network provides current-limiting that adequately protects the device.

### Digital Interface

Input data (control byte) and output data are multiplexed on a three-state parallel interface. This parallel I/O can easily be interfaced with a  $\mu P.$   $\overline{CS},$   $\overline{WR},$  and  $\overline{RD}$  control the write and read operations.  $\overline{CS}$  is the standard chip-select signal, which enables a  $\mu P$  to address the MAX196/MAX198 as an I/O port. When high, it disables the  $\overline{WR}$  and  $\overline{RD}$  inputs and forces the interface into a high-Z state.

Table 1. Full Scale and Zero Scale (MAX196 only)

| RANGE (V) | ZERO SCALE (V) | -FULL SCALE                | +FULL SCALE               |

|-----------|----------------|----------------------------|---------------------------|

| 0 to +5   | 0              | _                          | V <sub>REF</sub> x 1.2207 |

| 0 to +10  | 0              | _                          | V <sub>REF</sub> x 2.4414 |

| ±5        | _              | -V <sub>REF</sub> x 1.2207 | V <sub>REF</sub> x 1.2207 |

| ±10       | _              | -V <sub>REF</sub> x 2.4414 | V <sub>REF</sub> x 2.4414 |

## Table 2. Control-Byte Format

| D7 (MSB) | D6  | D5     | D4  | D3  | D2 | D1 | D0 (LSB) |

|----------|-----|--------|-----|-----|----|----|----------|

| PD1      | PD0 | ACQMOD | RNG | BIP | A2 | A1 | A0       |

| BIT     | NAME       | DESCRIPTION                                                                                   |

|---------|------------|-----------------------------------------------------------------------------------------------|

| 7, 6    | PD1, PD0   | These two bits select the clock and power-down modes (Table 4).                               |

| 5       | ACQMOD     | 0 = internally controlled acquisition (6 clock cycles), 1 = externally controlled acquisition |

| 4       | RNG        | Selects the full-scale voltage magnitude at the input (Table 3).                              |

| 3       | BIP        | Selects unipolar or bipolar conversion mode (Table 3).                                        |

| 2, 1, 0 | A2, A1, A0 | These are address bits for the input mux to select the "on" channel (Table 5).                |

## **Table 3. Range and Polarity Selection**

| ВІР | RNG | INPUT RANGE (V)<br>(MAX196) | INPUT RANGE (V)<br>(MAX198) |

|-----|-----|-----------------------------|-----------------------------|

| 0   | 0   | 0 to 5                      | 0 to V <sub>REF</sub> /2    |

| 0   | 1   | 0 to 10                     | 0 to V <sub>REF</sub>       |

| 1   | 0   | ±5                          | ±V <sub>REF</sub> /2        |

| 1   | 1   | ±10                         | ±V <sub>REF</sub>           |

### Table 4. Clock and Power-Down Selection

| PD1 | PD0 | DEVICE MODE                                           |  |  |

|-----|-----|-------------------------------------------------------|--|--|

| 0   | 0   | Normal Operation / External Clock Mode                |  |  |

| 0   | 1   | Normal Operation / Internal Clock Mode                |  |  |

| 1   | 0   | Standby Power-Down (STBYPD); clock mode is unaffected |  |  |

| 1   | 1   | Full Power-Down (FULLPD); clock mode is unaffected    |  |  |

### **Table 5. Channel Selection**

| A2 | A1 | A0 | CH0 | CH1 | CH2 | СНЗ | CH4 | CH5 |

|----|----|----|-----|-----|-----|-----|-----|-----|

| 0  | 0  | 0  | *   |     |     |     |     |     |

| 0  | 0  | 1  |     | *   |     |     |     |     |

| 0  | 1  | 0  |     |     | *   |     |     |     |

| 0  | 1  | 1  |     |     |     | *   |     |     |

| 1  | 0  | 0  |     |     |     |     | *   |     |

| 1  | 0  | 1  |     |     |     |     |     | *   |

#### Input Format

The control byte is latched into the device, on pins D7–D0, during a write cycle. Table 2 shows the control-byte format.

#### Output Data Format

The output data format is binary in unipolar mode and twos-complement binary in bipolar mode. When reading the output data,  $\overline{\text{CS}}$  and  $\overline{\text{RD}}$  must be low.

#### How to Start a Conversion

Conversions are initiated with a write operation, which selects the mux channel and configures the MAX196/ MAX198 for either a unipolar or bipolar input range. A write pulse  $(\overline{\text{WR}}+\overline{\text{CS}})$  can either start an acquisition interval or initiate a combined acquisition plus conversion. The sampling interval occurs at the end of the acquisition interval. The ACQMOD bit in the input control byte offers two options for acquiring the signal: internal or external. The conversion period lasts for 12 clock cycles in either internal or external clock or acquisition mode.

Writing a new control byte during a conversion cycle will abort the conversion and start a new acquisition interval.

#### Internal Acquisition

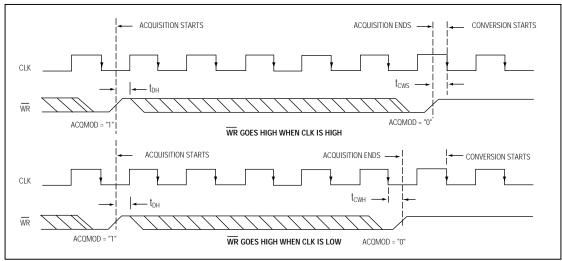

Select internal acquisition by writing the control byte with the ACQMOD bit cleared (ACQMOD = 0). This causes the write pulse to initiate an acquisition interval whose duration is internally timed. Conversion starts when this six-clock-cycle acquisition interval (3 $\mu$ s with f<sub>CLK</sub> = 2MHz) ends (see Figure 5).

#### External Acquisition

Use the external acquisition timing mode for precise control of the sampling aperture and/or independent control of acquisition and conversion times. The user controls acquisition and start-of-conversion with two separate write pulses. The first pulse, written with ACQMOD = 1, starts an acquisition interval of indeterminate length. The second write pulse, written with ACQMOD = 0, terminates acquisition and starts conversion on  $\overline{WR}$ 's rising edge (Figure 6). However, if the second control byte contains ACQMOD = 1, an indefinite acquisition interval is restarted.

The address bits for the input mux must have the same values on the first and second write pulses. Power-down mode bits (PD0, PD1) can assume new values on the second write pulse (see *Power-Down Mode* section).

#### How to Read a Conversion

A standard interrupt signal,  $\overline{\text{INT}}$ , is provided to allow the device to flag the  $\mu\text{P}$  when the conversion has ended and a valid result is available.  $\overline{\text{INT}}$  goes low when conversion is complete and the output data is ready (Figures 5 and 6). It returns high on the first read cycle or if a new control byte is written.

Figure 5. Conversion Timing Using Internal Acquisition Mode

Figure 6. Conversion Timing Using External Acquisition Mode

#### Clock Modes

The MAX196/MAX198 operate with either an internal or an external clock. Control bits (D6, D7) select either internal or external clock mode. Once the desired clock mode is selected, changing these bits to program power-down will not affect the clock mode. In each mode, internal or external acquisition can be used. At power-up, external clock mode is selected.

#### Internal Clock Mode

Select internal clock mode to free the  $\mu P$  from the burden of running the SAR conversion clock. To select this mode, write the control byte with D7 = 0 and D6 = 1. A 100pF capacitor between the CLK pin and ground sets this frequency to 1.56MHz nominal. Figure 7 shows a linear relationship between the internal clock period and the value of the external capacitor used.

#### External Clock Mode

Select external clock mode by writing the control byte with D7 = 0 and D6 = 0. Figure 8 shows CLK and  $\overline{WR}$  timing relationships in internal and external acquisition modes, with an external clock. A 100kHz to 2.0MHz external clock with 45% to 55% duty cycle is required for proper operation. Operating at clock frequencies lower than 100kHz will cause a voltage droop across the hold capacitor, and subsequently degrade performance.

Figure 7. Internal Clock Period vs. Clock Pin Capacitance

Figure 8a. External Clock and WR Timing (Internal Acquisition Mode)

Figure 8b. External Clock and  $\overline{WR}$  Timing (External Acquisition Mode)

### \_Applications Information

#### Power-On Reset

At power-up, the internal power-on reset circuitry sets INT high and puts the device in normal operation/external clock mode. This state is selected to keep the internal clock from loading the external clock driver when the part is used in external clock mode.

#### Internal or External Reference

The MAX196/MAX198 can operate with either an internal or external reference. An external reference can be connected to either the REF pin or the REFADJ pin (Figure 9).

To use the REF input directly, disable the internal buffer by tying REFADJ to  $V_{DD}$ . Using the REFADJ input eliminates the need to buffer the reference externally. When the reference is applied at REFADJ, bypass REFADJ with a  $0.01\mu F$  capacitor to AGND.

The REFADJ internal buffer gain is trimmed to 1.6384 to provide 4.096V at the REF pin from a 2.5V reference.

#### Internal Reference

The internally trimmed 2.50V reference is gained through the REFADJ buffer to provide 4.096V at REF. Bypass the REF pin with a  $4.7\mu\text{F}$  capacitor to AGND and the REFADJ pin with a  $0.01\mu\text{F}$  capacitor to AGND. The internal reference voltage is adjustable to  $\pm 1.5\%$  ( $\pm 65$  LSBs) with the reference-adjust circuit of Figure 1.

#### External Reference

At REF and REFADJ, the input impedance is a minimum of  $10k\Omega$  for DC currents. During conversions, an external reference at REF must be able to deliver 400µA DC load currents, and must have an output impedance of  $10\Omega$  or less. If the reference has higher output impedance or is noisy, bypass it close to the REF pin with a  $4.7\mu\text{F}$  capacitor to AGND.

With an external reference voltage of less than 4.096V at the REF pin or less than 2.5V at the REFADJ pin, the increase in the ratio of the RMS noise to the LSB value (FS / 4096) results in performance degradation (loss of effective bits).

#### Power-Down Mode

To save power, you can put the converter into low-current shutdown mode between conversions. Two programmable power-down modes are available: STBYPD and FULLPD. Select STBYPD or FULLPD by programming PDO and PD1 in the input control byte. When power-down is asserted, it becomes effective only after the end of conversion. In all power-down modes, the interface remains active and conversion

Figure 9a. Internal Reference

Figure 9b. External Reference, Reference at REF

Figure 9c. The external reference overdrives the internal reference.

results may be read. Input overvoltage protection is active in all power-down modes. The device returns to normal operation on the first  $\overline{\text{WR}}$  falling edge during write operation.

#### Choosing Power-Down Modes

The bandgap reference and reference buffer remain active in STBYPD mode, maintaining the voltage on the  $4.7\mu F$  capacitor at the REF pin. This is a "DC" state that does not degrade after power-down of any duration. Therefore, you can use any sampling rate with this mode, without regard to start-up delays.

However, in FULLPD mode, only the bandgap reference is active. Connect a 33µF capacitor between REF and AGND to maintain the reference voltage between conversions and to reduce transients when the buffer is enabled and disabled. Throughput rates down to 1ksps can be achieved without allotting extra acquisition time for reference recovery prior to conversion. This allows conversion to begin immediately after power-down ends. If the discharge of the REF capacitor during FULLPD exceeds the desired limits for accuracy (less

than a fraction of an LSB), run a STBYPD power-down cycle prior to starting conversions. Take into account that the reference buffer recharges the bypass capacitor at an 80mV/ms slew rate, and add 50 $\mu$ s for settling time. Throughput rates of 10ksps offer typical supply currents of 470 $\mu$ A, using the recommended 33 $\mu$ F capacitor value.

#### Auto-Shutdown

Selecting STBYPD on every conversion automatically shuts the MAX196/MAX198 down after each conversion without requiring any start-up time on the next conversion.

#### Transfer Function

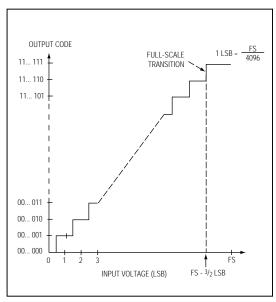

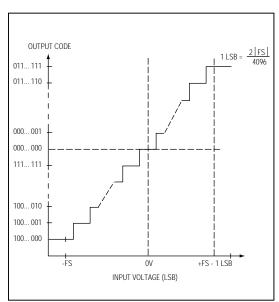

Output data coding for the MAX196/MAX198 is binary in unipolar mode with 1LSB = (FS / 4096) and twoscomplement binary in bipolar mode with 1LSB = [(2 x |FS|) / 4096]. Code transitions occur halfway between successive-integer LSB values. Figures 10 and 11 show the input/output (I/O) transfer functions for unipolar and bipolar operations, respectively. For full-scale (FS) values, refer to Table 1.

Figure 10. Unipolar Transfer Function

Figure 11. Bipolar Transfer Function

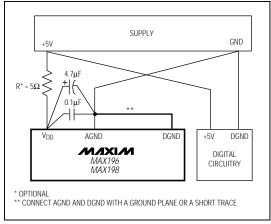

Layout, Grounding, and Bypassing Careful printed circuit board layout is essential for best system performance. For best performance, use a ground plane. To reduce crosstalk and noise injection, keep analog and digital signals separate. Digital ground lines can run between digital signal lines to minimize interference. Connect analog grounds and DGND in a star configuration to AGND. For noise-free operation, ensure the ground return from AGND to the supply ground is low impedance and as short as possible. Connect the logic grounds directly to the supply ground. Bypass  $V_{DD}$  with  $0.1\mu F$  and  $4.7\mu F$  capacitors to AGND to minimize high- and low-frequency fluctuations. If the supply is excessively noisy, connect a  $5\Omega$  resistor between the supply and  $V_{DD}$ , as shown in Figure 12.

Figure 12. Power-Supply Grounding Connection

### Functional Diagram

## \_Ordering Information (continued)

| PART       | TEMP. RANGE     | PIN-PACKAGE            |

|------------|-----------------|------------------------|

| MAX196BC/D | 0°C to +70°C    | Dice*                  |

| MAX196AENI | -40°C to +85°C  | 28 Narrow Plastic DIP  |

| MAX196BENI | -40°C to +85°C  | 28 Narrow Plastic DIP  |

| MAX196AEWI | -40°C to +85°C  | 28 Wide SO             |

| MAX196BEWI | -40°C to +85°C  | 28 Wide SO             |

| MAX196AEAI | -40°C to +85°C  | 28 SSOP                |

| MAX196BEAI | -40°C to +85°C  | 28 SSOP                |

| MAX196AMYI | -55°C to +125°C | 28 Narrow Ceramic SB** |

| MAX196BMYI | -55°C to +125°C | 28 Narrow Ceramic SB** |

| MAX198ACNI | 0°C to +70°C    | 28 Narrow Plastic DIP  |

| MAX198BCNI | 0°C to +70°C    | 28 Narrow Plastic DIP  |

| MAX198ACWI | 0°C to +70°C    | 28 Wide SO             |

| MAX198BCWI | 0°C to +70°C    | 28 Wide SO             |

| MAX198ACAI | 0°C to +70°C    | 28 SSOP                |

| MAX198BCAI | 0°C to +70°C    | 28 SSOP                |

| MAX198BC/D | 0°C to +70°C    | Dice*                  |

| MAX198AENI | -40°C to +85°C  | 28 Narrow Plastic DIP  |

| MAX198BENI | -40°C to +85°C  | 28 Narrow Plastic DIP  |

| MAX198AEWI | -40°C to +85°C  | 28 Wide SO             |

| MAX198BEWI | -40°C to +85°C  | 28 Wide SO             |

| MAX198AEAI | -40°C to +85°C  | 28 SSOP                |

| MAX198BEAI | -40°C to +85°C  | 28 SSOP                |

| MAX198AMYI | -55°C to +125°C | 28 Narrow Ceramic SB** |

| MAX198BMYI | -55°C to +125°C | 28 Narrow Ceramic SB** |

<sup>\*</sup> Dice are specified at  $T_A = +25$ °C, DC parameters only.

## \_Chip Topography

TRANSISTOR COUNT: 2956 SUBSTRATE CONNECTED TO GND

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

<sup>\*\*</sup> Contact factory for availability and processing to MIL-STD-883.