### **Philips Semiconductors**

| Data sheet                   |  |  |  |  |

|------------------------------|--|--|--|--|

| status Product specification |  |  |  |  |

| date of issue February 1991  |  |  |  |  |

# TDA1543 Dual 16-bit DAC (economy version) (I<sup>2</sup>S input format)

#### **FEATURES**

- · Low distortion

- · 16-bit dynamic range

- 4 x oversampling possible

- · Single 5 V power supply

- No external components required

- No requirement for external deglitcher circuitry due to fast settling output current

- · Adjustable bias current

- · Internal timing and control circuits

- I<sup>2</sup>S input format: time multiplexed, two's complement, TTL

#### **GENERAL DESCRIPTION**

The TDA1543 is a monolithic integrated dual 16-bit digital-to-analog converter (DAC) designed as an economy version for use in hi-fi digital audio equipment such as

Compact Disc players, digital tape or cassete recorders, digital sound in TV sets and in digital amplifiers.

### **ORDERING INFORMATION**

| EXTENDED    |      | PACKAGE      |          |               |  |  |

|-------------|------|--------------|----------|---------------|--|--|

| TYPE NUMBER | PINS | PIN POSITION | MATERIAL | CODE          |  |  |

| TDA1543     | 8    | DIL          | plastic  | SOT97         |  |  |

| TDA1543T    | 16   | mini-pack    | plastic  | SO16L;SOT162A |  |  |

### **QUICK REFERENCE DATA**

| SYMBOL            | PARAMETER                           | CONDITIONS                      | MIN. | TYP.                    | MAX.  | UNIT    |

|-------------------|-------------------------------------|---------------------------------|------|-------------------------|-------|---------|

| $V_{DD}$          | supply voltage                      |                                 | 3.0  | 5.0                     | 8.0   | V       |

| I <sub>DD</sub>   | supply current                      |                                 | -    | 50                      | 60    | mA      |

| IFS               | full scale output current           |                                 | 1.95 | 2.30                    | 2.65  | mA      |

| THD               | total harmonic distortion           | including noise                 | -    | <b>-75</b>              | -70   | dB      |

|                   |                                     | at 0 dB                         | _    | 0.018                   | 0.032 | %       |

| THD               | total harmonic distortion           | including noise                 | -    | -30                     | -23   | dB      |

|                   |                                     | at -60 dB                       | -    | 3.2                     | 7.9   | %       |

| t <sub>cs</sub>   | current settling time to ±1 LSB     |                                 | -    | 0.5                     | -     | μs      |

| BR                | input bit rate at data input        |                                 | -    | -                       | 9.2   | Mbits/s |

| fBCK              | clock frequency at clock input      |                                 | -    | -                       | 9.2   | MHz     |

| S/N               | signal-to-noise ratio               | at bipolar zero                 | 90   | 96                      | -     | dB      |

| TC <sub>FS</sub>  | full scale temperature coefficient  | at analog outputs<br>(AOL; AOR) | -    | ±500 x 10 <sup>-6</sup> | -     | K-1     |

| T <sub>amb</sub>  | operating ambient temperature range |                                 | -30  | -                       | +85   | °C      |

| P <sub>tot</sub>  | total power dissipation             |                                 | -    | 250                     | -     | mW      |

| I <sub>bias</sub> | bias current (adjustable)           |                                 | -0.6 | -                       | 5.0   | mA      |

**TDA1543**

### **TDA1543**

### **PINNING**

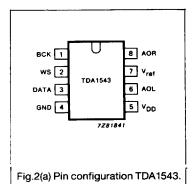

| SYMBOL           | PIN | DESCRIPTION                 |

|------------------|-----|-----------------------------|

| BCK              | 1   | bit clock input             |

| ws               | 2   | word select input           |

| DATA             | 3   | data input                  |

| GND              | 4   | ground                      |

| V <sub>DD</sub>  | 5   | +5 V supply voltage         |

| AOL              | 6   | left channel voltage output |

| V <sub>ref</sub> | 7   | reference voltage output    |

| AOR              | 8   | right channel output        |

### **PINNING**

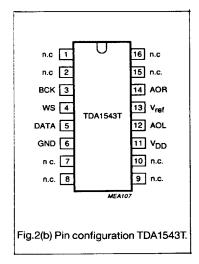

| SYMBOL           | PIN | DESCRIPTION              |  |  |

|------------------|-----|--------------------------|--|--|

| n.c.             | 1   | not connected            |  |  |

| n.c.             | 2   | not connected            |  |  |

| BCK              | 3   | bit clock input          |  |  |

| WS               | 4   | word select input        |  |  |

| DATA             | 5   | data input               |  |  |

| GND              | 6   | ground                   |  |  |

| n.c.             | 7   | not connected            |  |  |

| n.c.             | 8   | not connected            |  |  |

| n.c.             | 9   | not connected            |  |  |

| n.c.             | 10  | not connected            |  |  |

| $V_{DD}$         | 11  | +5 V supply voltage      |  |  |

| AOL              | 12  | left channel output      |  |  |

| V <sub>ref</sub> | 13  | reference voltage output |  |  |

| AOR              | 14  | right channel output     |  |  |

| n.c.             | 15  | not connected            |  |  |

| n.c.             | 16  | not connected            |  |  |

**TDA1543**

### Dual 16-bit DAC (economy version) (12S input format)

**TDA1543**

#### **FUNCTIONAL DESCRIPTION**

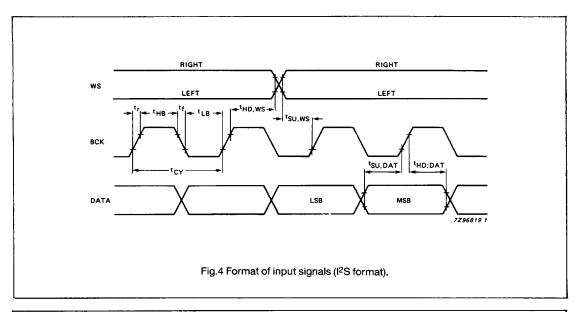

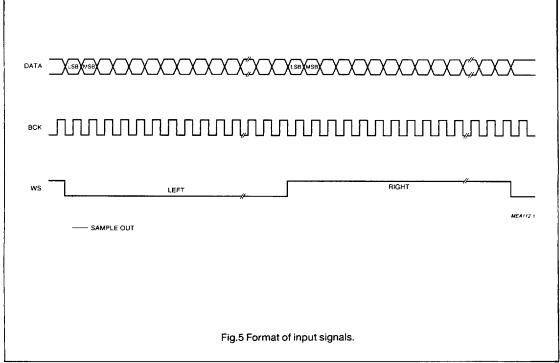

The TDA1543 accepts input serial data formats in two's complement with any bit length. Left and right data words are time multiplexed. The most significant bit (bit 1) must always be first. The format of data input is shown in Fig.4 and Fig.5.

This flexible input data format (I<sup>2</sup>S) allows easy interfacing with signal processing chips such as interpolation filters, error correction circuits and audio signal processor circuits (ASP).

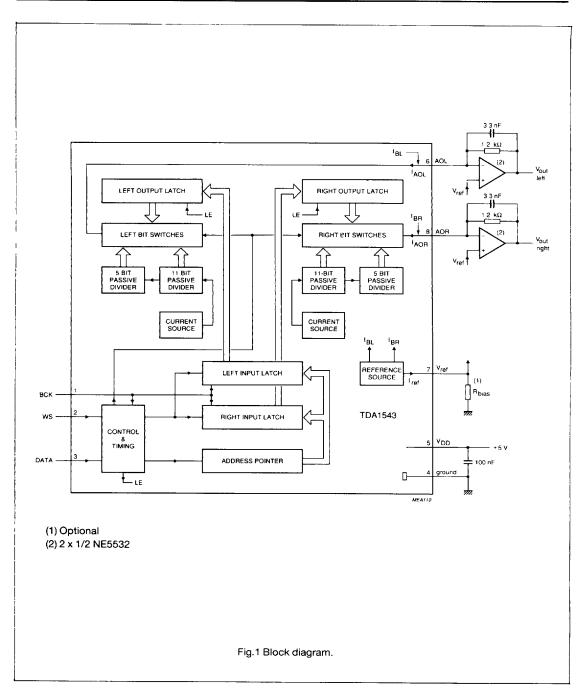

The high maximum input bit-rate and fast settling current facilitates application in 4 x oversampling systems. An adjustable current is added to the output currents to bias output operational amplifiers (OP1; OP2) for maximum dynamic range (see Fig.1).

With a LOW level on the word select (WS) input data is placed in the left input register and with a HIGH level on the WS input data is placed in the right input register. The data in the input registers is simultaneously latched in the output registers which control the bit switches.

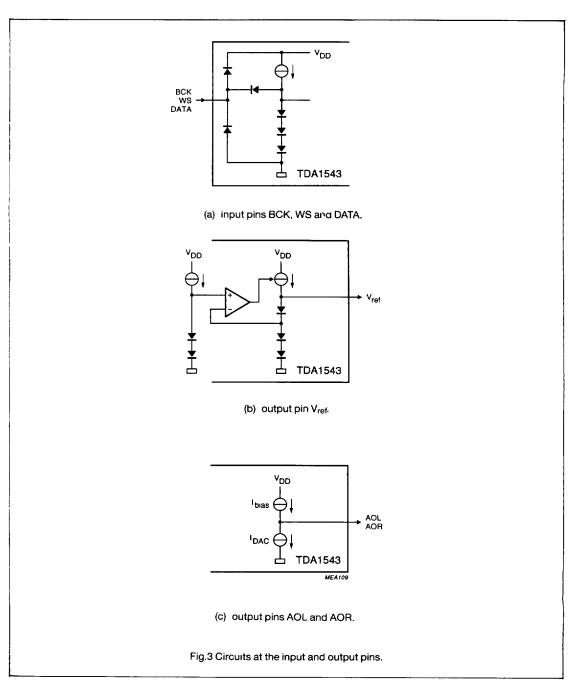

The output current of the DAC is a sink current. The current  $I_{ref}$  at the  $V_{ref}$  output is adjusted by a resistor or a current source. The current  $I_{ref}$  is amplified with gain  $A_{lbias}$  to the bias currents ( $I_{BL}$ ;  $I_{BR}$ ) which are added to the output currents.

#### **LIMITING VALUES**

In accordance with the Absolute Maximum System (IEC 134)

| SYMBOL           | PARAMETER                           | CONDITIONS | MIN.  | MAX.  | UNIT |

|------------------|-------------------------------------|------------|-------|-------|------|

| $V_{DD}$         | supply voltage range                |            | 0     | 9     | V    |

| TXTAL            | crystal temperature                 |            | -     | +150  | °C   |

| T <sub>stg</sub> | storage temperature range           |            | -55   | +150  | °C   |

| T <sub>amb</sub> | operating ambient temperature range |            | -30   | +85   | °C   |

| V <sub>es</sub>  | electrostatic<br>handling*          |            | -2000 | +2000 | ٧    |

### THERMAL RESISTANCE

| SYMBOL              | PARAMETER                | TYP. | UNIT |

|---------------------|--------------------------|------|------|

| R <sub>th j-a</sub> | from junction to ambient | 100  | K/W  |

<sup>\*</sup> Equivalent to discharging a 100 pF capacitor through a 1.5 k $\Omega$  series resistor.

**TDA1543**

### **CHARACTERISTICS**

$V_{DD}$  = 5 V;  $T_{amb}$  = +25 °C;  $I_{ref}$  = 0 mA; measured in the circuit of Fig.1; unless otherwise specified

| SYMBOL              | PARAMETER                                             | CONDITIONS                    | MIN.             | TYP.                    | MAX.                 | UNIT     |

|---------------------|-------------------------------------------------------|-------------------------------|------------------|-------------------------|----------------------|----------|

| Supply              |                                                       |                               | <u> </u>         | <u> </u>                |                      | ·        |

| V <sub>DD</sub>     | supply voltage range                                  |                               | 3.0              | 5.0                     | 8.0                  | V        |

| I <sub>DD</sub>     | supply current                                        | note 1                        | -                | 50                      | 60                   | mA       |

| RR                  | ripple rejection                                      | note 2                        | -                | 50                      | -                    | dB       |

| Digital in          | outs                                                  |                               |                  |                         |                      |          |

| I <sub>IL</sub>     | input current pins (1, 2 and 3)<br>digital inputs LOW | V <sub>i</sub> = 0.8 V        | -                | -                       | -0.4                 | mA       |

| t <sub>IH</sub>     | digital inputs HIGH                                   | V <sub>1</sub> = 2.0 V        | -                | <u> </u>                | 20                   | μА       |

| f <sub>BCK</sub>    | input frequency/bit rate<br>clock input pin 1         |                               | -                | -                       | 9.2                  | MHz      |

| BR                  | bit rate data input pin 3                             |                               | - <del> </del> - | -                       | 9.2                  | Mbits/s  |

| fws                 | word select input pin 2                               |                               | -                | -                       | 192                  | kHz      |

| Analog or           | utputs (AOL; AOR)                                     |                               |                  | •                       |                      | <u> </u> |

| Res                 | resolution                                            |                               | -                | -                       | 16                   | bits     |

|                     | output voltage compliance                             |                               |                  |                         |                      |          |

| V <sub>OC(AC)</sub> | AC                                                    |                               | -                | ±25                     | T                    | mV       |

| V <sub>OC(DC)</sub> | DC                                                    |                               | 1.8              | -                       | V <sub>DD</sub> -1.2 | V        |

| IFS                 | full scale current                                    |                               | 1.95             | 2.30                    | 2.65                 | mA       |

| T <sub>CFS</sub>    | full scale temperature coefficient                    |                               | -                | ±500 x 10 <sup>-6</sup> | -                    | K-1      |

| loffset             | offset current                                        | I <sub>ref</sub> = 0 mA       | -0.1             | 0.0                     | 0.1                  | mA       |

| I <sub>bias</sub>   | bias current (adjustable)                             |                               | -0.6             | -                       | 5.0                  | mA       |

| Al <sub>bias</sub>  | bias current gain                                     |                               | 1.9              | 2.0                     | 2.1                  |          |

| Analog or           | utputs (V <sub>ref</sub> )                            |                               |                  |                         |                      |          |

| $V_{ref}$           | reference voltage output                              |                               | 2.10             | 2.20                    | 2.30                 | V        |

| I <sub>ref</sub>    | reference current output                              |                               | -0.3             | -                       | 2.5                  | mA       |

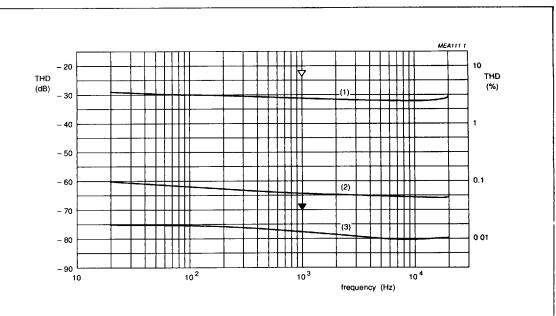

| THD                 | total harmonic distortion                             | including noise at 0 dB;      |                  | -75                     | -70                  | dB       |

|                     |                                                       | note 3, Fig.6                 |                  | 0.018                   | 0.032                | %        |

| THD                 | total harmonic distortion                             | including noise at<br>-60 dB; | -                | -30                     | -23                  | dB       |

|                     |                                                       | note 3, Fig.6                 | -                | 3.2                     | 7.9                  | %        |

| t <sub>cs</sub>     | settling time ±1 LSB                                  |                               | -                | 0.5                     | -                    | μs       |

| α.                  | channel separation                                    |                               | 85               | 90                      | -                    | dB       |

| d <sub>IO</sub>     | unbalance between outputs                             | note 4                        | -                | < 0.2                   | 0.3                  | dB       |

| t <sub>d</sub>      | time delay between outputs                            |                               | -                | < 0.2                   | -                    | μs       |

| S/N                 | signal-to-noise ratio                                 | at bipolar zero;<br>note 5    | 90               | 96                      | -                    | dB       |

**TDA1543**

| SYMBOL              | PARAMETER                   | CONDITIONS | MIN. | TYP. | MAX. | UNIT |

|---------------------|-----------------------------|------------|------|------|------|------|

| Timing (Fi          | g.4)                        |            |      |      |      |      |

| tr                  | rise time                   |            | -    | -    | 32   | ns   |

| tr                  | fall time                   |            | -    | -    | 32   | ns   |

| tcy                 | bit clock cycle time        |            | 108  | -    | -    | ns   |

| t <sub>HB</sub>     | bit clock HIGH time         |            | 22   | -    | -    | ns   |

| t <sub>LB</sub>     | bit clock LOW time          |            | 22   | T-   | -    | ns   |

| tsu:DAT             | data set-up time            |            | 32   | -    |      | ns   |

| t <sub>HD:DAT</sub> | data hold time to bit clock | note 6     | 2    | -    | -    | ns   |

| t <sub>HD:WS</sub>  | word select hold time       | note 6     | 2    | -    | -    | ns   |

| tsu:ws              | word select set-up time     |            | 32   | -    | -    | ns   |

### Notes to the characteristics

- 1. Measured at  $I_{AOL}=0$  mA and  $I_{AOR}=0$  mA (code 8000H) and  $I_{bias}=0$  mA.

- 2.  $V_{ripple} = 1\%$  of supply voltage and  $f_{ripple} = 100$  Hz.

- 3. Measured with 1 kHz sinewave generated at a sampling rate of 192 kHz.

- 4. Measured with 1 kHz full scale sinewave generated at a sampling rate of 192 kHz.

- 5. At code 0000H.

- 6. At this point  $t_{HD;DAT} = 0$  ns, this value has been fixed on 2 ns due to tolerances.

**TDA1543**

February 1991

1373

**7**110826 0081496 266 **\*\*\***

**TDA1543**

- (1) Measured including all distortion plus noise over a 20 kHz bandwidth at a level of -60 dB

- (2) Measured including all distortion plus noise over a 20 kHz bandwidth at a level of -24 dB

- (3) Measured including all distortion plus noise over a 20 kHz bandwidth at a level of -0 dB

Fig.6 Distortion as a function of frequency (4FS)

### Notes to Fig.6

- The sample frequency 4FS: 176.4 kHz.

- The supply voltage at the measurement = + 5 V (DC).

- Ref: 0 dB is the output level of a full scale digital sine wave stimulus.

- The graphs are constructed from average values of a small amount of engineering samples therefore no guarantee for typical values is implied.

- The arrows indicate the specification limits for 0 dB and -60 dB level signals.