**TENTATIVE**

TOSHIBA CMOS DIGITAL INTEGRATED CIRCUIT SILICON MONOLITHIC

# TC9432F

# DIGITAL SERVO SINGLE CHIP PROCESSOR BUILT IN 1 BIT DA CONVERTER

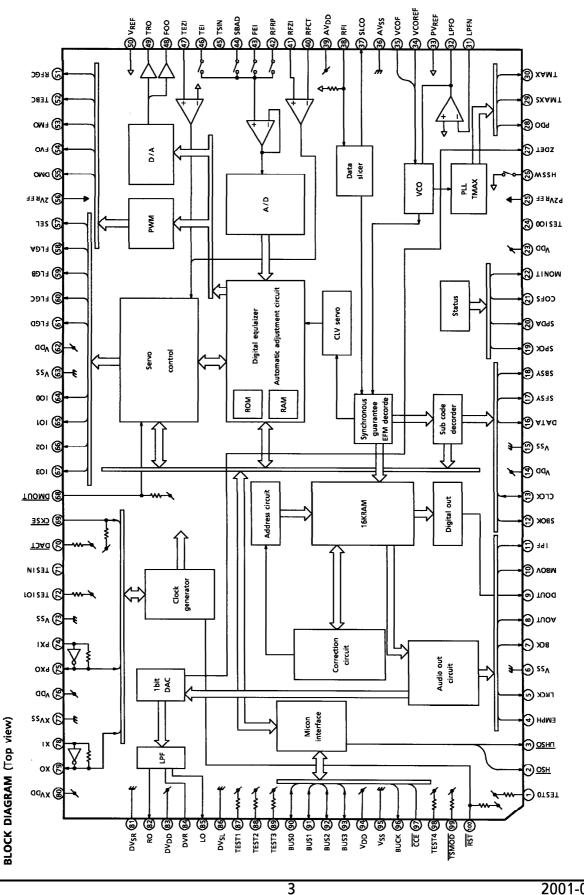

The TC9432F is a single chip processor which incorporates the following function: synchronous separation protection and interpolation, EFM demodulation, Error correction, microcontroller interface, digital equalizer for use in servo LSI and servo control circuit. In addition, the TC9432F incorporates a 1 bit DA converter. In combination with the head amplifier TA2109F for digital servo, the TC9432F allow simplified, adjustment-free structuring of CD player system.

### Weight: 1.6g (Typ.)

#### **FEATURES**

- Sync pattern detection, sync signal protection and synchronization can be made correctly.

- Built in EFM demodulation circuit, subcode demodulation circuit.

- Capable of correcting dual C1 correction and quadruple C2 correction using the CIRC correction theoretical format.

- The TC9432F respond to variable playback system.

- Jitter absorbing capacity of ±6 frames.

- Built in 16KRAM.

- Built in digital out circuit.

- Built in L/R independent digital attenuator.

- Audio output responds to bilingual function.

- Reed timing free subcode Q data and capable of synchronous output with audio data.

- Built in data slicer and analog PLL (free-adjustment VCO).

- Capable of automatic adjustment function of focus servo and tracking servo, for loop gain, offset and balance.

- Built in RF gain automatic adjustment circuit.

- Built in digital equalizer for phase compensation.

- Built in RAM for digital equalizer for coefficient, and capable of variable pickup.

- Built in focus, tracking servo control circuit.

- Search control corresponds to every mode and can realize high speed and stable search.

- Lens-kick are using speed controlled form.

- Built in AFC circuit and APC circuit for CLV servo of disc motor.

- Built in anti-defect and anti-shock circuit.

- Built in 8 times oversampling 1bit DA converter.

- Built in analog filter for 1bit DA converter.

- Built in zero data detect output circuit.

- The TC9432F capable of 4 times speed operation.

- Built in microcontroller interface circuit.

- CMOS silicon structure and high speed, low power consumption.

- 100 pin flat package.

2001-06-19

TC9432F - 3

# PIN FUNCTION

| PIN No. | SYMBOL          | 1/0      | FUNCTIONAL DESCRIPTION                                                                                                                        | REMARKS                |

|---------|-----------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| 1       | TEST0           | I        | Test mode terminal. Normally, keep at open.                                                                                                   | With pull-up resistor. |

| 2       | HSO             | 0        | Playback speed mode flag output terminal.    UHSO   HSO   PLAYBACK SPEED   H   H   Nomal                                                      |                        |

| 3       | UHSO            | 0        | H L 2 times L H 4 times L L —                                                                                                                 |                        |

| 4       | ЕМРН            | O        | Subcode Q data emphasis flag output terminal.<br>Emphasis ON at "H" level and OFF at "L" level.<br>The output polarity can invert by command. | _                      |

| 5       | LRCK            | 0        | Channel clock output terminal. (44.1kHz) L-ch at "L" level and R-ch at "H" level. The output polarity can invert by command.                  | _                      |

| 6       | Vss             | _        | Digital GND terminal.                                                                                                                         | _                      |

| 7       | ВСК             | 0        | Bit clock output terminal. (1.4122MHz)                                                                                                        | _                      |

| 8       | AOUT            | 0        | Audio data output terminal.                                                                                                                   | _                      |

| 9       | DOUT            | 0        | Digital data output terminal.                                                                                                                 | _                      |

| 10      | MBOV            | 0        | Buffer memory over signal output terminal.  Over at "H" level.                                                                                | _                      |

| 11      | IPF             | 0        | Correction flag output terminal.  At "H" level, AOUT output is made to correction impossibility by C <sub>2</sub> correction processing.      | _                      |

| 12      | SBOK            | 0        | Subcode Q data CRCC check adjusting result output terminal. The adjusting result is OK at "H" level.                                          | _                      |

| 13      | CLCK            | 1/0      | Subcode P~W data readout clock input/output terminal. This terminal can select by command bit.                                                | _                      |

| 14      | $V_{DD}$        | _        | Digital power supply voltage terminal.                                                                                                        | _                      |

| 15      | VSS             | _        | Digital GND terminal.                                                                                                                         | _                      |

| 16      | DATA            | 0        | Subcode P~W data output terminal.                                                                                                             | _                      |

| 17      | SFSY            | 0        | Play-back frame sync signal output terminal.                                                                                                  | _                      |

| 18      | SBSY            | 0        | Subcode block sync signal output terminal.                                                                                                    | _                      |

| 19      | SPCK            | 0        | Processor status signal readout clock output terminal.                                                                                        | _                      |

| 20      | SPDA            | 0        | Processor status signal output terminal.                                                                                                      | _                      |

| 21      | COFS            | 0        | Correction frame clock output terminal. (7.35kHz)                                                                                             | _                      |

| 22      | MONIT           | 0        | Internal signal (DSP internal flag and PLL clock) output terminal. Selected by command.                                                       | _                      |

| 23      | V <sub>DD</sub> | <b> </b> | Digital power supply voltage terminal.                                                                                                        | _                      |

| PIN No. | SYMBOL             | 1/0 | FUNCTIONAL DESCRIPTION                                                                                                                                                                             | REMARKS                                                                        |

|---------|--------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|

| 24      | TESIO0             | ı   | Test input/output terminal. Normally, keep at "L" level.                                                                                                                                           | _                                                                              |

| 25      | P2V <sub>REF</sub> | _   | PLL double reference voltage supply terminal.                                                                                                                                                      | _                                                                              |

| 26      | HSSW               | 0   | 2/4 times speed at "V <sub>REF</sub> " voltage.                                                                                                                                                    | 2-state output.<br>(PV <sub>REF</sub> , HiZ)                                   |

| 27      | ZDET               | 0   | 1bit DA converter zero detect flag output terminal.                                                                                                                                                | _                                                                              |

| 28      | PDO                | 0   | Phase difference signal output terminal of EFM signal and PLCK signal.                                                                                                                             | 3-state output.<br>(P2V <sub>REF</sub> , PV <sub>REF</sub> , V <sub>SS</sub> ) |

| 29      | TMAXS              | 0   | TMAX detection result output terminal. Selected by command bit (TMPS).                                                                                                                             | 3-state output.<br>(P2V <sub>REF</sub> , PV <sub>REF</sub> , V <sub>SS</sub> ) |

| 30      | TMAX               | O   | TMAX detection result output terminal. Selected by command bit (TMPS).  DIFFERENCE RESULT TMAX OUTPUT Longer than fixed freq. "P2VREF" Shorter than fixed freq. "VSS" Within the fixed freq. "HiZ" | 3-state output.<br>(P2V <sub>REF</sub> , HiZ, V <sub>SS</sub> )                |

| 31      | LPFN               | I   | LPF amplifier inverting input terminal for PLL.                                                                                                                                                    | Analog input.                                                                  |

| 32      | LPFO               | 0   | LPF amplifier output terminal for PLL.                                                                                                                                                             | Analog output.                                                                 |

| 33      | $PV_{REF}$         | _   | PLL reference voltage supply terminal.                                                                                                                                                             | _                                                                              |

| 34      | VCOREF             | ı   | VCO center frequency reference level terminal.<br>Normally, keep at "PV <sub>REF</sub> " level.                                                                                                    | _                                                                              |

| 35      | VCOF               | 0   | VCO filter terminal.                                                                                                                                                                               | Analog output.                                                                 |

| 36      | AVSS               | _   | Analog GND terminal.                                                                                                                                                                               | _                                                                              |

| 37      | SLCO               | 0   | Data slice level output terminal.                                                                                                                                                                  | Analog output.                                                                 |

| 38      | RFI                | I   | RF signal input terminal.                                                                                                                                                                          | Analog input. (Z <sub>in</sub> : selected by command)                          |

| 39      | $AV_{DD}$          | _   | Analog power supply voltage terminal.                                                                                                                                                              | _                                                                              |

| 40      | RFCT               | ı   | RFRP signal center level input terminal.                                                                                                                                                           | Analog input. ( $Z_{in}$ : $50k\Omega$ )                                       |

| 41      | RFZI               | I   | RFRP zero cross input terminal.                                                                                                                                                                    | Analog input.                                                                  |

| 42      | RFRP               | I   | RF ripple signal input terminal.                                                                                                                                                                   | Analog input.                                                                  |

| 43      | FEI                | I   | Focus error signal input terminal.                                                                                                                                                                 | Analog input.                                                                  |

| 44      | SBAD               |     | Sub-beam adder signal input terminal.                                                                                                                                                              | Analog input.                                                                  |

| 45      | TSIN               | ı   | Test input terminal. Normally, keep at "V <sub>REF</sub> " level.                                                                                                                                  | Analog input.                                                                  |

| 46      | TEI                | I   | Tracking error signal input terminal.  Take in at tracking servo on.                                                                                                                               | Analog input.                                                                  |

| 47      | TEZI               | ı   | Tracking error zero cross input terminal.                                                                                                                                                          | Analog input. ( $Z_{in}: 10k\Omega$ )                                          |

| 48      | FOO                | 0   | Focus servo equalizer output terminal.                                                                                                                                                             | Analog output.                                                                 |

| 49      | TRO                | 0   | Tracking servo equalizer output terminal.                                                                                                                                                          | (2V <sub>REF</sub> ~AV <sub>SS</sub> )                                         |

| 50      | V <sub>REF</sub>   | _   | Analog reference voltage supply terminal.                                                                                                                                                          |                                                                                |

| PIN No. | SYMBOL            | 1/0 | FUNCTIONAL DESCRIPTION                                                                                                                                                                      | REMARKS                                                                      |

|---------|-------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|

|         |                   |     |                                                                                                                                                                                             |                                                                              |

| 51      | RFGC              | 0   | RF amplitude adjustment control signal output terminal.                                                                                                                                     | 3-state PWM signal                                                           |

| 52      | TEBC              | 0   | Tracking balance control signal output terminal.                                                                                                                                            | output.                                                                      |

| 53      | TEBC              | 0   | Feed equalizer output terminal.                                                                                                                                                             | (2V <sub>REF</sub> , V <sub>REF</sub> , V <sub>SS</sub> )                    |

| 54      | TEBC              | 0   | Speed error signal or feed search equalizer output terminal.                                                                                                                                | (PWM carrier = 88.2kHz)                                                      |

| 55      | DMO               | 0   | Disk equalizer output terminal. (PWM carrier = 88.2kHz for DSP, Synchronize to PXO)                                                                                                         | 3-state output.<br>(2V <sub>REF</sub> , V <sub>REF</sub> , V <sub>SS</sub> ) |

| 56      | 2V <sub>REF</sub> | _   | Analog double reference voltage supply terminal.                                                                                                                                            | _                                                                            |

| 57      | SEL               | 0   | APC circuit ON/OFF indication signal output terminal. At the laser on time, UHF = L at "Hi-Z" level and UHF = H at "H" level.                                                               | _                                                                            |

| 58      | FLGA              | O   | External flag output terminal for internal signal. Can select signal from TEZC, FOON, FOK and RFZC by command.                                                                              | _                                                                            |

| 59      | FLGB              | O   | External flag output terminal for internal signal. Can select signal from DFCT, FOON, FMON and RFZC by command.                                                                             | _                                                                            |

| 60      | FLGC              | o   | External flag output terminal for internal signal.  Can select signal from TRON, TRSR, FOK and  SRCH by command.                                                                            | _                                                                            |

| 61      | FLGD              | O   | External flag output terminal for internal signal. Can select signal from TRON, DMON, HYS and SHC by command.                                                                               | _                                                                            |

| 62      | $V_{DD}$          | _   | Digital power supply voltage terminal.                                                                                                                                                      | _                                                                            |

| 63      | $V_{SS}$          | _   | Digital GND terminal.                                                                                                                                                                       | _                                                                            |

| 64      | 100               |     | General I/O terminal. Can change over input                                                                                                                                                 |                                                                              |

| 65      | IO1               | 1   | port or output port by command. At the input mode time can readout a state of terminal (H/L) by read command. At the output mode time can control a state of terminal (H/L/HiZ) by command. |                                                                              |

| 66      | 102               | 1/0 |                                                                                                                                                                                             | _                                                                            |

| 67      | IO3               |     |                                                                                                                                                                                             |                                                                              |

| 68      | DMOUT             | I   | This terminal controls IO0~IO3 terminal.  At "L" level time, IO0, 1 out feed equalizer signal of 2-state PWM, IO2, 3 out disk equalizer signal of 2-state PWM.                              | With pull-up resistor.                                                       |

| 69      | CKSE              | ı   | Normally, keep at open.                                                                                                                                                                     | With pull-up resistor.                                                       |

| 70      | DACT              | I   | DAC test mode terminal. Normally, keep at open.                                                                                                                                             | With pull-up resistor.                                                       |

| 71      | TESIN             | I   | Test input terminal. Normally, keep at "L" level.                                                                                                                                           | Analog input.                                                                |

| 72      | TESIO1            | I   | Test input/output terminal. Normally, keep at "L" level.                                                                                                                                    | Analog input.                                                                |

| 73      | V <sub>SS</sub>   |     | Digital GND terminal.                                                                                                                                                                       | _                                                                            |

| PIN No. | SYMBOL           | 1/0 | FUNCTIONAL DESCRIPTION                                                                                          | REMARKS                |

|---------|------------------|-----|-----------------------------------------------------------------------------------------------------------------|------------------------|

| 74      | PXI              | I   | Crystal oscillator connecting input terminal for DSP. Normally, keep at "L" level.                              | _                      |

| 75      | PXO              | 0   | Crystal oscillator connecting output terminal for DSP.                                                          |                        |

| 76      | $V_{DD}$         | _   | Digital power supply voltage terminal.                                                                          | _                      |

| 77      | XVSS             | _   | Oscillator GND terminal for system clock.                                                                       | _                      |

| 78      | ΧI               | ı   | Crystal oscillator connecting input terminal for system clock.                                                  | _                      |

| 79      | хо               | 0   | Crystal oscillator connecting output terminal for system clock.                                                 | _                      |

| 80      | χν <sub>DD</sub> | _   | Oscillator power supply voltage terminal for system clock.                                                      | _                      |

| 81      | DVSR             | _   | Analog GND terminal for DA converter. (R-ch)                                                                    | _                      |

| 82      | RO               | 0   | R channel data forward output terminal.                                                                         | _                      |

| 83      | DV <sub>DD</sub> | _   | Analog supply voltage terminal for DA converter.                                                                | _                      |

| 84      | DVR              | _   | Reference voltage terminal for DA converter.                                                                    | _                      |

| 85      | LO               | 0   | L channel data forward output terminal.                                                                         | _                      |

| 86      | DV <sub>SL</sub> | _   | Analog GND terminal for DA converter. (L-ch)                                                                    | _                      |

| 87      | TEST1            | I   | Test mode terminal. Normal, keep at open.                                                                       | With pull-up resistor. |

| 88      | TEST2            | I   | Test mode terminal. Normal, keep at open.                                                                       | With pull-up resistor. |

| 89      | TEST3            | I   | Test mode terminal. Normal, keep at open.                                                                       | With pull-up resistor. |

| 90      | BUS0             | 1/0 |                                                                                                                 |                        |

| 91      | BUS1             | 1/0 |                                                                                                                 | Schmit input.          |

| 92      | BUS2             | 1/0 | Micon interface data input/output terminal.                                                                     | With pull-up resistor. |

| 93      | BUS3             | 1/0 |                                                                                                                 |                        |

| 94      | $V_{DD}$         | _   | Digital power supply voltage terminal.                                                                          | _                      |

| 95      | VSS              | _   | Digital GND terminal.                                                                                           | _                      |

| 96      | BUCK             | I   | Micon interface clock input terminal.                                                                           | Schmit input.          |

| 97      | CCE              | I   | Command and data sending/receiving chip enable signal input terminal. The bus line becomes active at "L" level. | Schmit input.          |

| 98      | TEST4            | I   | Test mode terminal. Normal, keep at open.                                                                       | With pull-up resistor. |

| 99      | TSMOD            | I   | Local test mode selection terminal.                                                                             | With pull-up resistor. |

| 100     | RST              | I   | Reset signal input terminal. Reset at "L" level.                                                                | With pull-up resistor. |

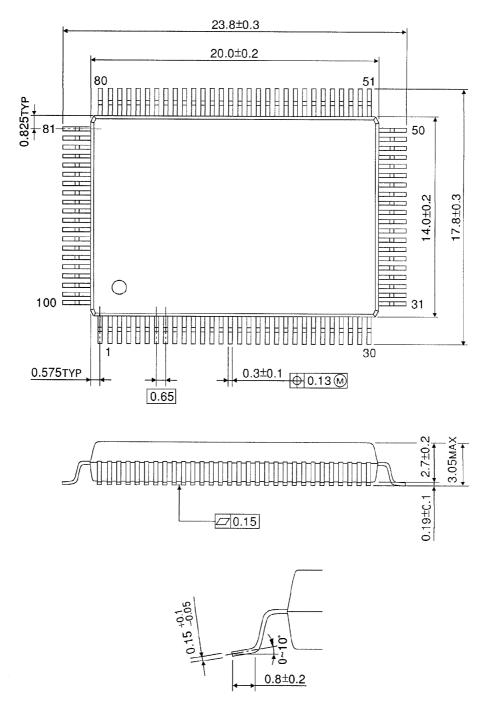

## **PACKAGE DIMENSIONS**

QFP100-P-1420-0.65A Unit: mm

Weight: 1.6g (Typ.)

#### RESTRICTIONS ON PRODUCT USE

000707EBA

- TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such TOSHIBA products could cause loss of human life, bodily injury or damage to property. In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the "Handling Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability Handbook" etc..

- The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These TOSHIBA products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunction or failure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc.. Unintended Usage of TOSHIBA products listed in this document shall be made at the customer's own risk.

- The products described in this document are subject to the foreign exchange and foreign trade laws.

- The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA CORPORATION for any infringements of intellectual property or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any intellectual property or other rights of TOSHIBA CORPORATION or others.

- The information contained herein is subject to change without notice.