# 2MHz, 3A Synchronous Step Down Converter

#### **FEATURES**

- Two 50mΩ (typical) MOSFETs for High Efficiency at 3A Loads

- 200kHz to 2MHz Switching Frequency

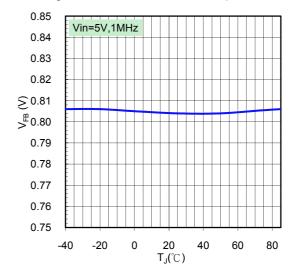

- 0.803V ± 1% Voltage Reference

- Synchronizes to External Clock from 300kHz to 2MHz

- Adjustable Slow Start/Sequencing

- UV and OV Power Good Output

- Low Operating and Shutdown Quiescent Current

- Cycle by Cycle Current Limit, Thermal and Frequency Fold Back Protection

- RoHS Compliant and 100% Lead (Pb)-Free

## **APPLICATIONS**

- DSPs, FPGAs, ASIC, and Microprocessors

- I/O Supplies

- System Power Supplies

#### DESCRIPTION

The APE1543 is a synchronous step down converter designed with integrated MOSFETs. The current mode PWM DC/DC converter decreases external component counts and up to 2MHz switching frequency also reduces the inductor size.

The APE1543 integrates  $50m\Omega$  MOSFET and  $500\mu A$  operation current to maximize the efficiency. The 1% high accurate of reference voltage over temperature provides well load regulation. APE1543 works in dual operating modes. PSM mode is for high efficiency in light loading. PWM mode is for low noise operation.

The soft start time is adjustable by an external capacitor at SS pin. The UVLO threshold is set at 2.6V internally, and can be increase by a programmable resistor at the EN pin. The APE1543 also features the frequency fold back and thermal shutdown to protect the device against the over-current fault condition.

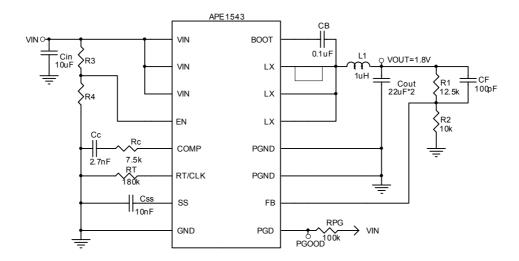

#### TYPICAL APPLICATION

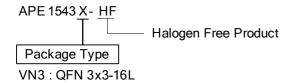

## **ORDERING / PACKAGE INFORMATION**

# ABSOLUTE MAXIMUM RATINGS (at T<sub>A</sub>=25°C)

| VIN                                             | -0.3V to 6V    |

|-------------------------------------------------|----------------|

| EN                                              | -0.3V to 6V    |

| LX                                              | -0.3V to 6V    |

| BOOT                                            | LX+6V          |

| RT/CLK                                          | -0.3V to 6V    |

| FB, SS                                          | -0.3V to 6V    |

| PGD                                             | -0.3V to 6V    |

| PGD Sink Current                                | 10mA           |

| GND, PGND                                       | -0.3V to 0.3V  |

| Storage Temperature Range (T <sub>ST</sub> )    | -65 to +150°C  |

| Junction Temperature (T <sub>J</sub> )          | 150°C          |

| Lead Temperature (Soldering, 10sec.)            | 260°C          |

| Thermal Resistance from Junction to Ambient (R6 | $\theta_{JA})$ |

| QFN 3x3-16L                                     | 60°C/W         |

## **RECOMMENDED OPERATING CONDITIONS**

| VIN                         | 2.95V to 6V   |

|-----------------------------|---------------|

| EN                          | -0.3V to 6V   |

| LX                          | -0.3V to 6V   |

| Operating Temperature Range | -40°C to 85°C |

## **ELECTRICAL SPECIFICATIONS**

(VIN=2.95 to 6V,  $T_A$  =25°C, unless otherwise specified)

| PARAMETER                                      | SYM               | TEST CONDITION                                 | MIN   | TYP   | MAX   | UNIT |

|------------------------------------------------|-------------------|------------------------------------------------|-------|-------|-------|------|

| Input                                          |                   |                                                |       |       |       |      |

| Operation Voltage Range                        | $V_{IN}$          |                                                | 2.95  |       | 6     | V    |

| Under Voltage Lockout                          | UVLO              | Rising                                         |       | 2.6   | 2.8   | V    |

| Threshold                                      |                   | hysteresis                                     |       | 200   |       | mV   |

| Quiescent Current                              | IQ                | $V_{IN}$ =5V, $V_{FB}$ =0.9V, RT=400k $\Omega$ |       | 500   |       | μΑ   |

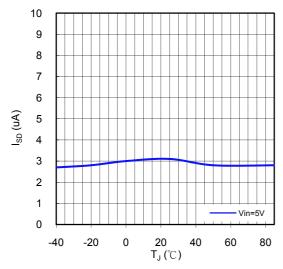

| Shutdown Current                               | $I_{SD}$          | EN=0V, 0.95V≦VIN≦6V                            |       | 3     |       | μΑ   |

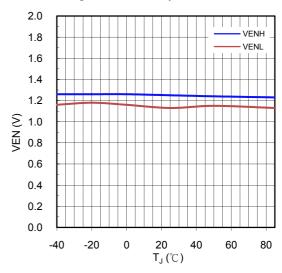

|                                                | V <sub>EN</sub>   | Rising                                         |       | 1.25  |       | V    |

| EN Threshold                                   |                   | Falling                                        |       | 1.18  |       | V    |

| EN la seri Command                             | I <sub>EN</sub>   | V <sub>EN</sub> + 50mV                         |       | -3.2  |       | μΑ   |

| EN Input Current                               |                   | V <sub>EN</sub> - 50mV                         |       | -0.65 |       | μΑ   |

| Reference Voltage                              | $V_{FB}$          | VIN=2.95 to 6V                                 | 0.795 | 0.803 | 0.811 | V    |

| Controller                                     |                   |                                                | •     |       |       |      |

| High Side Switch                               | _                 | BOOT-LX=5V                                     |       | 50    |       | mΩ   |

| Resistance (Note1)                             | $R_{DRVH}$        | BOOT-LX=2.95V                                  |       | 64    |       | mΩ   |

| Low Side Switch Resistance (Note1)             | R <sub>DRVL</sub> | V <sub>IN</sub> =5V                            |       | 50    |       | mΩ   |

|                                                |                   | V <sub>IN</sub> =2.95V                         |       | 64    |       | mΩ   |

| Switching Current Limit                        | $I_{LM}$          |                                                | 5     |       |       | Α    |

| LX Rise/Fall Time (Note1)                      |                   | V <sub>IN</sub> =5V                            |       | 1.5   |       | V/ns |

| BOOT Charge Resistance                         |                   | V <sub>IN</sub> =5V                            |       | 16    |       | Ω    |

| Error Amplifier                                |                   |                                                | •     |       |       |      |

| COMP Leakage Current                           |                   |                                                |       | 7     |       | nA   |

| EA Transconductance (Note1)                    | gm <sub>EA</sub>  | $I_{COMP} = \pm 2\mu A, V_{COMP} = 1V$         |       | 225   |       | μΑ/V |

| COMP Sink/Source Current                       |                   | V <sub>COMP</sub> =1V, 0.1V overdrive          |       | ±20   |       | μΑ   |

| Current Sense to COMP Transconductance (Note1) | $gm_CS$           |                                                |       | 13    |       | A/V  |

# **ELECTRICAL SPECIFICATIONS (Continued)**

(T<sub>A</sub> =25 °C, unless otherwise specified)

| PARAMETER                        | SYM                  | TEST CONDITION                                                 | MIN | TYP | MAX  | UNIT             |

|----------------------------------|----------------------|----------------------------------------------------------------|-----|-----|------|------------------|

| Resistor Timing and Extern       | al Clock             | (RT/CLK)                                                       | l   |     | J    | -1.              |

| Switching Frequency Range        |                      | RT mode                                                        | 200 |     | 2000 | kHz              |

|                                  |                      | CLK mode                                                       | 300 |     | 2000 | kHz              |

| Switching Frequency              | fsw                  | RT=400kΩ                                                       | 400 | 500 | 600  | kHz              |

| Minimum CLK ON Time              | T <sub>CLK_MIN</sub> |                                                                |     | 75  |      | ns               |

| RT/CLK Voltage                   | V <sub>RT/CLK</sub>  | RT=400kΩ                                                       |     | 0.5 |      | V                |

| DT/01/47                         |                      | High                                                           | 2.2 |     |      | V                |

| RT/CLK Threshold                 |                      | Low                                                            |     |     | 0.4  | V                |

| Delay Time (Note1)               | t <sub>D</sub>       | RT/CLK falling to LX rising edge, fsw=500kHz, with RT resistor |     | 150 |      | ns               |

| Soft Start (SS)                  |                      |                                                                |     |     |      |                  |

| SS Charge Current                | I <sub>SS</sub>      | Vss=0.4V                                                       |     | 1.8 |      | μA               |

| SS Discharge Current             | I <sub>SS-D</sub>    | UVLO, EN, Tthermal fault,<br>V <sub>IN</sub> =5V, Vss=0.5V     |     | 20  |      | mA               |

|                                  |                      | Over-current, V <sub>FB</sub> =0V                              |     | 20  |      | μA               |

| Power Good (PGD)                 |                      | ,                                                              | •   | •   | •    | 1                |

|                                  | V <sub>FB-R1</sub>   | Rising                                                         |     | 93  |      | %V <sub>FB</sub> |

| FB Threshold (Good)              | V <sub>FB-F1</sub>   | Falling                                                        |     | 105 |      | %V <sub>FB</sub> |

| FB Threshold (Fault)             | $V_{FB-R2}$          | Rising                                                         |     | 91  |      | %V <sub>FB</sub> |

|                                  | V <sub>FB-F2</sub>   | Falling                                                        |     | 107 |      | %V <sub>FB</sub> |

| PGD Leakage Current              | I <sub>PGD</sub>     | V <sub>FB</sub> =V <sub>REF</sub> , V <sub>PGD</sub> =5.5V     |     | 0.1 |      | μA               |

| PGD On Resistance (Note1)        | $R_{PGD}$            |                                                                |     | 10  |      | Ω                |

| PGD Output Low                   |                      | I <sub>PGD</sub> =3.5mA                                        |     | 0.3 |      | V                |

| Minimum VIN for Valid PGD Output |                      | V <sub>PGD</sub> <0.5V at 100μA                                |     | 1.2 |      | V                |

| Thermal Shutdown                 |                      | •                                                              | •   | •   | •    |                  |

| Thermal Shutdown                 | <b>T</b>             |                                                                |     | 150 |      | °C               |

| Threshold (Note1)                | $T_{SD}$             | Hysteresis                                                     |     | 20  |      | °C               |

Note1: Guarantee by design, not production tested.

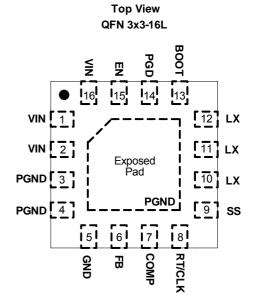

# **PIN DESCRIPTIONS**

| PIN No.    | PIN SYMBOL  | PIN DESCRIPTION                                                               |

|------------|-------------|-------------------------------------------------------------------------------|

| 1, 2, 16   | VIN         | Input supply voltage from 2.95V to 6V.                                        |

| 3, 4       | PGND        | Power ground.                                                                 |

| 5          | GND         | Analog ground.                                                                |

| 6          | FB          | Output feedback pin.                                                          |

| 7          | СОМР        | Compensation pin. Connect frequency compensation components at this           |

|            |             | pin.                                                                          |

| 8          | RT/CLK      | Resistor timing or external clock input pin.                                  |

| 9          | SS          | Soft-start pin. Connect an external capacitor to adjust the output rise time. |

| 10, 11, 12 | LX          | Switching node.                                                               |

| 42         | 13 BOOT     | Supply input for internal high-side N-MOSFET gate drive (boot terminal).      |

|            |             | Connect a bootstrap capacitor from this pin to LX node.                       |

| 1/         | 14 PGD      | Power good output pin. PGD is an open-drain output. Pull up to VIN rail       |

|            |             | with a pull-up resistor.                                                      |

| 15         | EN          | Enable pin, internal pull-up current source.                                  |

| 17         | Exposed pad | Connect to power ground directly.                                             |

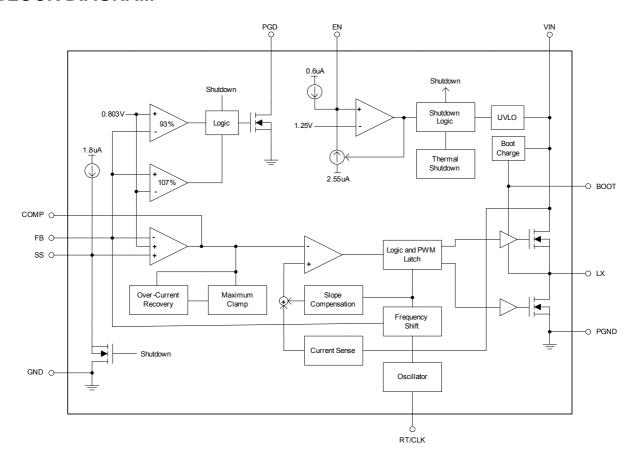

## **BLOCK DIAGRAM**

# TYPICAL PERFORMANCE CHARACTERISTICS ΕN EN $V_{\mathsf{LX}}$ $V_{OUT}$ $V_{\text{OUT}}$ **PGD** PGD $I_{LX}$ $I_{LX}$ Fig.1 Enable, 5Vi to 1.8Vo/0A Fig.2 Enable, 5Vi to 1.8Vo/3A Tek Stop ΕN ΕN $V_{LX}$ $V_{LX}$ $V_{\text{OUT}}$ $V_{\text{OUT}}$ PGD PGD $I_{LX}$ (RI) 2.00 V Fig.2 Enable, 3.3Vi to 1.8Vo/3A Fig.1 Enable, 3.3Vi to 1.8Vo/0A $V_{\mathsf{LX}}$ $V_{\mathsf{LX}}$ V<sub>OUT</sub>, 100mV/div V<sub>OUT</sub>, 100mV/div I<sub>OUT</sub>, 0~3A I<sub>OUT</sub>, 0~3A

Fig.5 Load Transient, Vin=5V, Vo=1.8V

Fig.6 Load Transient, Vin=3.3V, Vo=1.8V

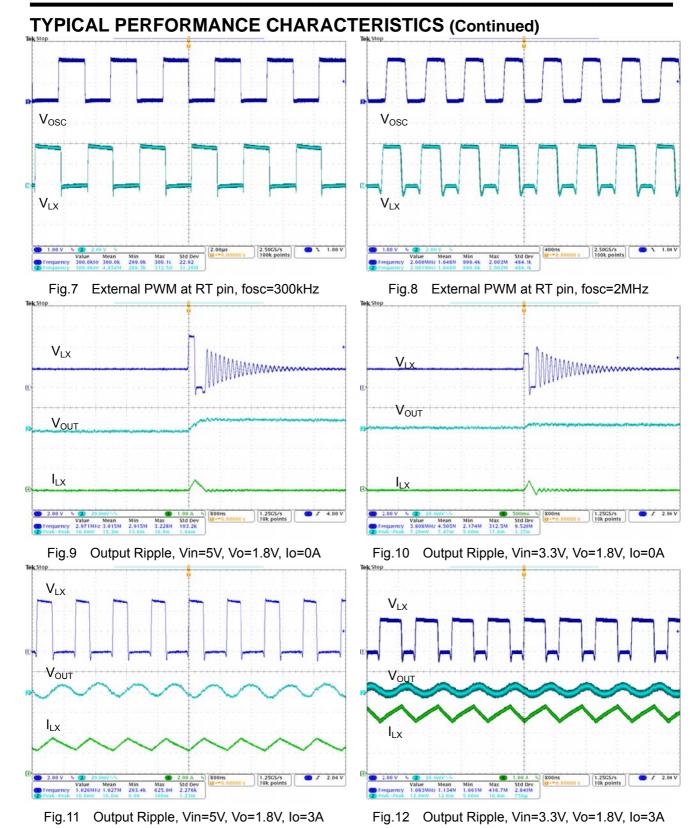

# TYPICAL PERFORMANCE CHARACTERISTICS (Continued)

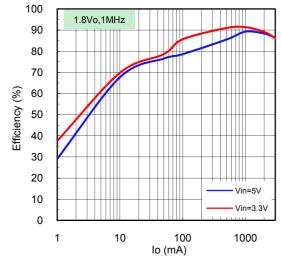

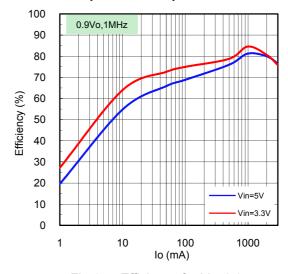

Fig.13 Efficiency for Vo=1.8V

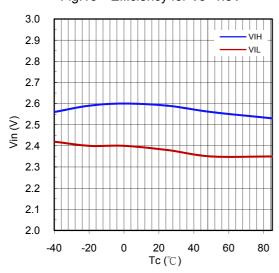

Fig.15 UVLO Threshold vs. Temperature

Fig.17 Shutdown Current vs. Temperature

Fig.14 Efficiency for Vo=0.9

Fig.16 EN Threshold vs. Temperature

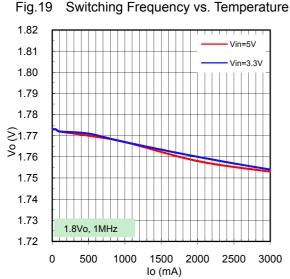

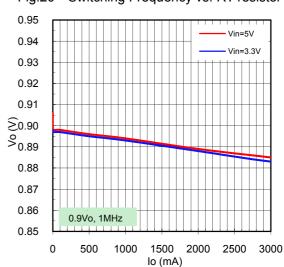

Fig.18 Feedback Voltage vs. Temperature

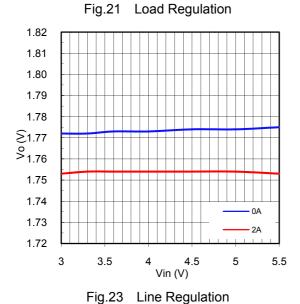

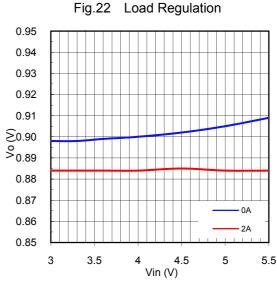

# **TYPICAL PERFORMANCE CHARACTERISTICS (Continued)**

## **APPLICATION INFORMATION**

The APE1543 is designed in low noise, adjustable fixed frequency, and current mode PWM control. At light load condition, the APE1543 operates in power save, pulse-skip mode (PSM) which blanks the ON pulse automatically to maintain high efficiency. In PSM, the internal Zero-Cross comparator looks for inductor current. When zero current is detected, the converter enters PSM and turns low-side MOSFET off on each cycle. When the output load current increases from light load to heavy load, the inductor current does not cross zero and reaches to the continuous conduction. The transition load point between discontinuous and continuous conduction mode, I<sub>OUT(LB)</sub>, can be calculated by:

$$I_{OUT(LB)} = \frac{1}{2 \times L \times f_{sw}} \frac{(V_{IN} - V_{OUT}) \times V_{OUT}}{V_{IN}}$$

#### **Under-Voltage Lockout**

The APE1543 has VIN under-voltage lockout protection (UVLO). This is a non-latched protection. When the VIN voltage is lower than 2.6V, the APE1543 is off. If higher UVLO is needed, use EN pin as TYPICAL APPLICATION circuit to adjust the UVLO threshold by using two external resistors, R3 and R4. When the EN pin floats, the internal 0.6µA current source provides the APE1543 default operation. If the EN voltage exceeds 1.25V, an additional 2.55µA hysteresis current is added. If the EN voltage is below 1.18V, the hysteresis current is removed.

$$R3 = \frac{0.944 \times V_{UVLO-H} - V_{UVLO-L}}{2.58 \times 10^{-6}}$$

$$R4 = \frac{1.18 \times R3}{V_{UVLO-L} - 1.18 + R3 \times 3.15 \times 10^{-6}}$$

The UVLO has two thresholds,  $V_{UVLO-H}$  for power up when the input voltage is rising and  $V_{UVLO-L}$  for power down when the input voltage is falling.

#### **Soft Start**

The APE1543 has an internal 1.8µA current source which charges external capacitor to implement a soft start time. When the EN pin voltage rises above the enable threshold, the converter enters its start-up sequence. The soft start time can be calculated by:

$$t_{SS}(ms) = \frac{C_{SS}(nF) \times V_{REF}(V)}{I_{SS}(\mu A)} = \frac{C_{SS}(nF) \times 0.803(V)}{1.8(\mu A)}$$

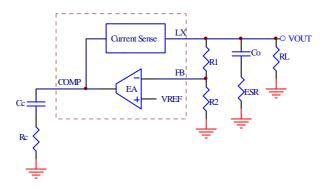

### **Output Voltage Setting**

The output voltage is adjusted with a resistor divider from the output to the FB pin. It can be calculated as:

$$V_{OUT} = 0.803V \times (\frac{R1}{R2} + 1)$$

## **APPLICATION INFORMATION (Continued)**

#### **Power Good Output**

The APE1543 provides a power good (PGD) output, which is an open-drain output requiring a pull-up resistor. Typically connect to +5V voltage source or less through a resistor between the values of  $1k\Omega$  and  $100k\Omega$ . The PGD comparator continuously monitors the FB voltage. In shutdown and soft start period, PGD is actively low. If the FB voltage rises above 93% or falls below 105% of the internal reference voltage, the PGD is high. If the FB voltage falls below 91% or rises above 107% of the internal reference voltage, the PGD becomes low immediately which enters the fault condition.

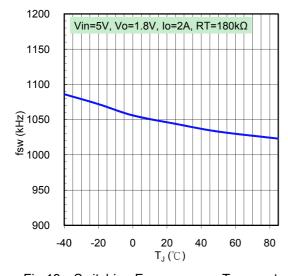

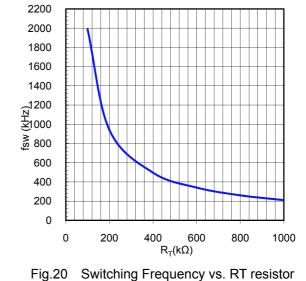

#### Switch frequency

The switching frequency is adjustable from 200kHz to 2MHz by a preset resistor connected to the RT/CLK pin. This pin is fixed at 0.5V when using an external resistor to ground to determine the switching frequency. The external resistor, RT, is given as:

$$RT(k\Omega) = \frac{311890}{f_{SW}(kHz)^{1.0793}}$$

The high switching frequency allows lower value inductor and smaller output capacitor. However, the highest switching frequency causes more switching loss. A moderate switching frequency of 1MHz is selected to achieve both a small solution size and a high efficiency operation. So that, RT is calculated to be  $180k\Omega$ .

#### **Synchronize**

The RT/CLK pin is also used to synchronize the converter to an external clock. Connect a square wave with a 75ns on time at least to the RT/CLK pin to determine the synchronization frequency ranging from 300kHz to 2MHz. The amplitude of square wave must converse lower than 0.6V and higher than 1.6V. The internal amplifier is disabled if the RT/CLK pin is pulled above the 1.6V threshold and the pin becomes a synchronization input. The rising edge of the LX is synchronized to the falling edge of external clock.

#### **Frequency Compensation**

The APE1543 has the transconductance amplifier with Type II compensation control loop. Figure25 shows the small signal equivalent model for the APE1543 control loop which can check frequency response and dynamic load response. The APE1543 adds a compensating ramp to the switch current signal. This slope compensation prevents sub-harmonic oscillations when duty cycle increases.

Fig.25 Simple small signal model

## **APPLICATION INFORMATION (Continued)**

In Figure25, the error amplifier is a transconductance amplifier with a gm of  $225\mu\text{A/V}$ . The current sense transconductance with a gm of 13A/V is the proportion of the variation in switch current and the variation in COMP pin voltage. The small signal transfer function is dominated by a DC gain and developed by a pole at  $f_P$  and a zero at  $f_Z$ .

$$GAIN = gm_{CS} \times R_{L}$$

$$f_p = \frac{1}{2\pi \times R_L \times C_{OUT}}$$

$$f_Z = \frac{1}{2\pi \times R_{ESR} \times C_{OUT}}$$

$$f_C = \sqrt{f_P \times f_Z}$$

Proper compensation of the system is allowed for a calculable bandwidth. The targeted compensation network is to provide the closed loop transfer function with 0dB crossover frequency (fc, one tenth of fsw typically) and sufficient phase margin (greater than 45°). As the load current decreases, the gain increases and the pole frequency lowers to keep the same 0dB crossover frequency for the varied load conditions.

The compensation network Rc, Cc can take as following:

$$R_{C} = \frac{2\pi \times f_{C} \times V_{OUT} \times C_{OUT}}{V_{REF} \times gm_{EA} \times gm_{CS}}$$

Choose the compensation resistor (Rc) to set the desired crossover frequency.

$$C_{C} = \frac{R_{L} \times C_{OUT}}{R_{C}}$$

Choose the compensation capacitor (Cc) to achieve the desired phase margin.

#### **Inductor Selection**

The inductor value determines the ripple current and the ripple voltage of the converter. This inductor choice provides trade-offs between size vs. efficiency. Low inductor values cause large ripple currents, resulting in the smallest size, but poor efficiency and high output noise. The inductor selection is based on the ripple current which is typically set between 1/10 to 3/10 of the maximum load current. The switching frequency and ripple current determine the inductor which can be calculated as follows:

$$L = \frac{V_{OUT}(V_{IN}^{-}V_{OUT})}{\Delta I_{L} \times f_{SW} \times V_{IN}}$$

The ripple current can be given by:

$$\Delta I_{L} = \frac{V_{OUT}(V_{IN} - V_{OUT})}{L \times f_{SW} \times V_{IN}}$$

# **APPLICATION INFORMATION (Continued)**

#### **Output Capacitor Selection**

The output capacitor needs to be selected based on three considerations, the output ripple, load transient, and the modulator pole. Below equation shows the minimum output capacitance necessary to perform this.

$$C_{\rm OUT} > \frac{2 \times \Delta I_{\rm OUT}}{f_{\rm SW} \times \Delta V_{\rm OUT}}$$

The low ESR ceramic capacitor is recommended. Low ESR capacitors are preferred to keep the output voltage ripple low. The output voltage ripple can be estimated by:

$$\Delta V_{OUT} = ESR/\Delta I_{L}$$

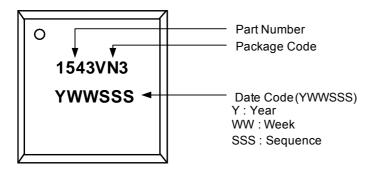

## **MARKING INFORMATION**

### QFN 3x3-16L