# XC8100 FPGA Family

June 1, 1996 (Version 1.0)

Preliminary Product Specification

### **Features**

- · Synthesis-targeted sea-of-gates architecture

- Efficient results with top-down design

- Design without architecture knowledge

- Predictable pre-layout timing estimation

- Accurate back-annotation

- Very high routability

- ASIC design flow

- · Fine-grain architecture

- High, predictable utilization: >95%

- TrueMap logic mapping

- · Innovative programmable cell

- Combinatorial, synchronous, or three-state

- High logic utilization for all designs

- Family of devices: 1K-45K usable gates

- Same pinout as XC4000 and XC5200

- MicroVia™ antifuse technology

- Low power CMOS

- System features

- JTAG boundary scan

- Fast, wide internal decode

- On-chip three-state for internal bussing

- I/O drive = 24 mA; PCI drive compliant

- Slew-rate options to control ground bounce

- Modular clock/buffer resources

- 5 V, 3.3 V operation

- One-time programmable, single-chip solution

- Design security

- Xilinx and third party programmers

- Self-test logic for 100% testability

- Automatic post-programming test

- XACTstep™ Series 8000 development system

- Xilinx unified design entry libraries

- Floorplanning, incremental design

- High-speed PowerMaze<sup>™</sup> router

- PC: Windows 3.1/95/NT

- WS: Sparcstation, HP PA, RS6000

- Supported by XACTstep Foundation Series

### **Table 1: Product Line**

| Product            | XC8100  | XC8101  | XC8103  | XC8106   | XC8109   | XC8112*   | XC8116*   | XC8120*   |

|--------------------|---------|---------|---------|----------|----------|-----------|-----------|-----------|

| Max Logic Gates    | 1K      | 2K      | 7K      | 13K      | 20K      | 27K       | 36K       | 45K       |

| Typical Gate Range | .6 - 1K | 1K - 2K | 3K - 7K | 6K - 13K | 9K - 20K | 12K - 27K | 16K - 36K | 20K - 45K |

| Cells              | 192     | 384     | 1024    | 1728     | 2688     | 3744      | 4800      | 6144      |

| Flip-Flops (Max)   | 96      | 192     | 512     | 864      | 1344     | 1872      | 2400      | 3072      |

| I/O                | 32      | 72      | 128     | 168      | 192      | 248       | 280       | 320       |

Note: \* Future product plans

## Description

The XC8100 family of field programmable gate arrays (FPGAs) provides the same overall benefits as other Xilinx FPGAs: fast time-to-market, reduced design risk, low power, standard product availability, and the use of existing design methodologies. It combines the density of mask gate arrays with the flexibility of programmable logic.

The XC8100 family is targeted to be extremely efficient and cost effective when using top-down, technology-independent design methods. The XC8100 employs a new sea-ofgates FPGA architecture. The basic cell is small and was specifically architected for technology-independent design. A new process, the Xilinx MicroVia technology, minimizes the area taken up by the many interconnect elements used in a fine-grain structure. Programmable interconnect elements are stacked vertically between metal layers and are above the logic cells, using significantly less area than other programmable logic technologies. (Note that architectural diagrams in this data sheet do not necessarily show this internal structure). The result is that XC8100 devices have very rich interconnect resources while maintaining cost effectiveness. The XC8100 sea-of-gates architecture delivers high gate utilization, high routability, low cost, and fast design cycles. For high speed, the MicroVia antifuse has a typical on-resistance less than 50  $\Omega$ .

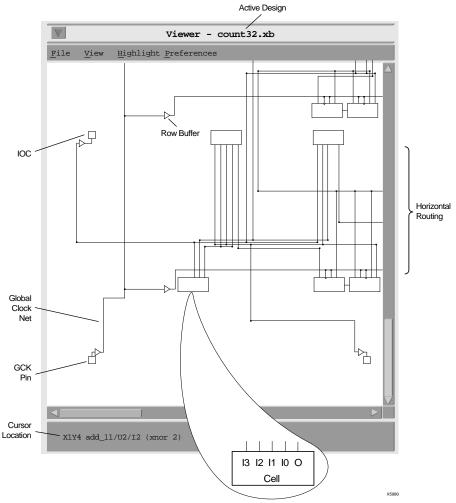

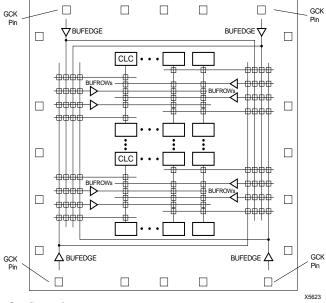

Like all true FPGAs, as shown in Figure 1, the XC8100 family consists of an array of logic cells and programmable routing resources surrounded by a ring of I/O connections. Unlike most FPGAs, which attempt to offer the "best" fixed cell, the XC8100 logic cells are themselves programmable. They can implement synchronous, combinatorial, or three-state functions. This means the XC8100 software has the flexibility to choose the best cell structure, depending on the logic to be implemented. A design does not have to be evaluated to see if it "fits", but instead can be implemented top-down.

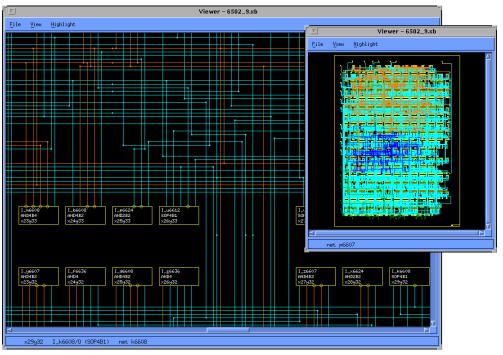

Figure 1: XC8100 Architecture in Viewer Window

Compared to Xilinx XC2000, XC3000, or XC4000 FPGAs, this architecture has many more cells, each with fewer gates. It also has fewer preconfigured resources — for example, no flip-flops in the logic cells or in the I/O cells. Routing resources are abundant and there is a very large ratio of interconnects to logic cell inputs and outputs. The architecture's objective is to achieve the highest gate utilization and routability across a diverse set of applications.

Unlike Xilinx SRAM FPGAs, which are infinitely reprogrammable, the XC8100 family is one-time programmable (OTP). XC8100 devices use MicroVia process technology, a combination of CMOS, a metal-to-metal antifuse and three layers of metal. Programming is done by Xilinx or third-party programmers, similar to OTP PLDs. There is no need for configuration storage in the target application and design security is very high.

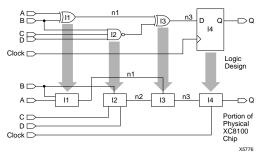

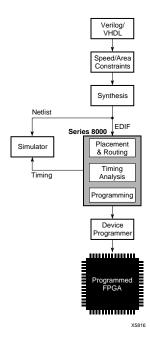

The XC8100 design flow is exactly like that of an ASIC or gate array. Designs are entered and simulated with third-party CAE tools and then placed and routed by Xilinx XACT*step* Series 8000 tools. A key feature of the synthesis design flow is that technology mapping occurs in the synthesizer. All instance names, net names, and hierarchy in the EDIF netlist from the synthesizer are maintained by the Series 8000 software. Every logic gate in the design corresponds to a logic gate/CLC in the FPGA. Every net in the design corresponds to a net in the FPGA. Therefore, this information and the associated timings are available for backannotation, simulation and debugging. Figure 2 shows this mapping process – called TrueMap.

The XC8100 architecture maximizes the chance that a design will be completed automatically. Because of the architecture and new software written for it, device utiliza-

Figure 2: TrueMap™ Logic Mappings

tion does not degrade when technology independent design entry is used. Designs can be entered in HDLs with little concern for the IC architecture. With the very high probability of routing, different logic implementations can be accurately evaluated before place and route.

The Series 8000 software allows user control, primarily for maximizing the speed of the design. High level floorplanning works with constraints based on hierarchical block names. The fast PowerMaze router makes incremental design easier. The router can route a fully-utilized XC8106 in less than one minute – in most cases in only seconds.

# **Applications**

The XC8100 family is targeted at three primary applications:

- 1. High-level design language (HDL) using logic synthesis. The architecture was developed to give very high gate utilization and low cost when designs are entered with a technology-independent methodology. Most synthesis algorithms were originally designed for gate arrays, and they are sub-optimal for the different architectures used in FPGAs and complex PLDs. The XC8100 architecture was specifically designed to fit the logic implementations that are produced by synthesis algorithms. During development, architectural simulations were run using actual synthesis products. The XC8100 programmable cell and design library were chosen to give cost-effective results when using logic synthesis. The XC8100 software is very ASIC-like and gives accurate estimations when synthesizing and evaluating architectural tradeoffs before place and route.

- 2. General logic applications, especially telecommunications and industrial control. The XC8100 offers high and predictable utilization over a wide range of logic functions. It can handle designs that are heavily synchronous or heavily combinatorial. Since the architecture delivers "usable gates" irrespective of the target application, designs can be quickly entered and results will be predictable. There is no need to analyze the target design for flip-flops, latches, three-states, etc., to determine how well the design "fits."

- XC8100 devices, especially the XC8100 and XC8101, can also implement logic traditionally done in CPLDs, with less than one-tenth the power.

- 3. Applications requiring a single-chip FPGA. These include high security and fast initial power-up operation.

## **Security**

The XC8100 offers a high level of security for designs that are subject to reverse-engineering. The security strategy includes the software, the IC architecture, and the process.

The XC8100 software automatically stores design information (.xb file) in a compressed and encrypted file format. In addition, there is an optional password capability that only allows the design file to be used for programming, not for viewing or writing or manipulating. In other words, the password-protected design file can be given out for device programming while still maintaining security.

XC8100 devices receive programming information through the JTAG (boundary scan) port and data registers. While this information can be read back for factory testing purposes, these JTAG instructions are not documented. The user can program a bit which defeats the JTAG test/programming readback instructions, thereby eliminating this form of reverse engineering.

The third part of the security strategy involves the process. The physical implementation of a design occurs by programming the desired connection pattern. The connection is formed by creating a metal filament through a layer of amorphous silicon. Only a small percentage of the antifuses are programmed. In a typical design in the XC8106, about 2% of the approximately 700,000 antifuses will be programmed. The functionality of the design can only be copied by knowing exactly which of the antifuses were programmed.

The antifuses are located between the second and third layer of metal. This means that programmed and unprogrammed antifuses are covered by a layer of metal and a protective passivation layer. It is impossible to distinguish programmed antifuses from unprogrammed antifuses by inspection of the top of the chip. Attempts to remove the protection and metal layers will certainly result in damage or removal of the conductive filament between the metal layers.

Moreover, antifuses, whether programmed or unprogrammed, are difficult to distinguish from regular, permanent connections between the second and third layers of metal (vias). Note that this is different from a gate array, where vias only exist where connections are intended. In the XC8100, vias, programmed antifuses, and unprogrammed antifuses all exist simultaneously.

Another method of reverse engineering is hot spot analysis, which relies on distinguishing programmed from unprogrammed fuses by investigation of heat dissipation. Since

the on-resistance of the programmed antifuses is very low, the heat dissipation is very low also. This makes this technique useless for determination of the state of the antifuse.

### **Performance Overview**

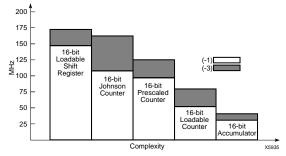

The XC8100 family has been benchmarked with many actual customer designs running synchronous clock rates of 20-40 MHz (-1 speed grade). The performance of any design depends on the type of circuit implemented, including the delay through the combinatorial and sequential logic elements plus the delay in the interconnect routing. Figure 3 shows some performance numbers for representative circuits, using worst case timing parameters. A rough estimate of timing can be made by assuming 6 ns per logic level. This includes 3 ns for the CLC delay and 3 ns for the routing delays. More accurate estimations can be made using the information in the next section.

Figure 3: Representative Circuit Performance

|                                | XC8100 Performance |      |     |  |

|--------------------------------|--------------------|------|-----|--|

| Function                       | -1                 | -3*  |     |  |

| 16-bit decoder from input pads |                    |      |     |  |

| (delay from strobe)            | 7.6                | 5.1  | ns  |  |

| (delay for full decode)        | 11.7               | 7.9  | ns  |  |

| 16-to-1 multiplexer            | 18.8               | 14.2 | ns  |  |

| 16-bit loadable shift register | 148                | 172  | MHz |  |

| 16-bit Johnson counter         | 109                | 161  | MHz |  |

| 16-bit prescaled counter       | 91                 | 125  | MHz |  |

| 16-bit loadable counter        | 51                 | 77   | MHz |  |

| 16-bit accumulator             | 28                 | 41   | MHz |  |

<sup>\*</sup>Advance Information

The XC8100 architecture and software are architected to deliver the maximum device performance when using synthesis CAE tools. This is possible due to:

- CLC designed to fit synthesis algorithms

- predictable prelayout timing for accurate synthesis

- block-level hierarchical floorplanning

- buffer resources for high fanout nets or critical signals

- flexible CLC many flip-flops possible allows pipelining

- cascade

- High drive outputs specified for 50 pF

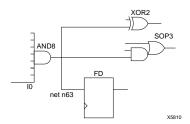

Figure 4: Example Path Delay Calculation

## **Estimating XC8100 Timing**

Like an ASIC or FPGA, XC8100 circuit timings depend on the actual layout (placement and routing) of the design. XC8100 software calculates the timing using a very accurate SPICE-like timing model. However, prior to layout actual circuit performance can be estimated. This is done automatically by synthesis tools using the XC8100 library and can be done manually using information in this data sheet.

Accurate timing estimates prior to place and route are necessary when exploring a design space with synthesis tools. This allows the synthesizer to make the proper speed/area trade-offs without leaving the synthesis environment (i.e. without going through a full place and route cycle). The timing estimates for the XC8100 architecture are accurate to within 10% of the post place and route numbers. This high correlation between pre- and post- timing numbers is a result of the following architecture and design flow features:

- No logic mapping the placed and routed design matches the synthesized design netlist exactly. There is no technology mapping phase where logic gates from the design netlist are mapped into different physical gates on the chip.

- All cell delays are built into the synthesis library. This, in conjunction with point 1, means that all cell delays used in the synthesis tool are preserved in the final chip.

- The wire load model is well characterized. The abundant routing in the architecture increases the likelihood of direct routes between CLCs rather than circuitous paths. This reduces the standard deviation of the estimated versus actual net delays.

The timing for the XC8100 is modeled with two elements: the cell delay and a fanout-dependent net delay (wireload model). Cell delay timings for most of the primitive library elements are shown in the AC Timing section of the data sheet. For example, the data sheet shows four numbers for the AND4 primitive. Worst-case numbers are worst-case voltage, worst-case temperature, worst-case process, and

worst-case falling or rising edge. Note that the XC8100 library has input-to-output numbers, both rising and falling edges, for all pins. Synthesis software will automatically take advantage of the fastest pin if required, and schematic users can do this manually.

Pre-layout net delays are modeled as a function of fanout and can be estimated by using Table 2. Note that various buffers, as explained later, can be used to limit the delay of wide fanout nets.

Table 2: Pre-Layout Net Delays vs. Fanout

| Fanout | Net Delay (ns) (-1) |

|--------|---------------------|

| 1      | 1.2                 |

| 2      | 2                   |

| 3      | 3                   |

| 4      | 4                   |

| n      | n                   |

For example, in Figure 4, net n63 has a fanout of 3, so the estimated delay (-1 speed grade) from the I0 input of the AND8 to the D input of FD is: 3.0 + 3 = 6.0 ns.

## **Architecture**

Xilinx field-programmable gate arrays are comprised of three major configurable elements: configurable cells, input/output blocks and interconnections. The cells provide the functional elements for constructing the design's logic. The I/O cells provide the interface between the package pins and internal signal lines. The programmable interconnect resources provide routing paths to connect the inputs and outputs of the cells and I/O blocks onto the appropriate nets. In the XC8100, user configuration is established by one-time programming of MicroVia antifuses that deter-

mine the cell logic functions, I/O functions, and the interconnections.

## Programmable Cell (CLC)

The XC8100 implements combinatorial and sequential logic by configuring and interconnecting identical Configurable Logic Cells (CLC). Each CLC is equivalent to 3.25 "LSI-Logic gates." This figure was derived by synthesizing a range of designs first to the XC8100, and then to an LSI Logic library.

In order to allow the widest range of logic - combinatorial, synchronous, and three-state - to map efficiently to the XC8100 architecture, CLCs are internally programmable. While this is also true of Xilinx SRAM FPGAs, other antifuse FPGA architectures have fixed cell structures with only programmable interconnect. A programmable cell ensures that logic will more frequently fit efficiently into a cell. The cell is programmable as to: input inversions, combinatorial function choice, synchronous logic internal feedback path, three-state, and cascade enable. The XC8100 software automatically configures the cell based on the user's design netlist. The variety of building blocks means a higher device utilization for a range of logic functions.

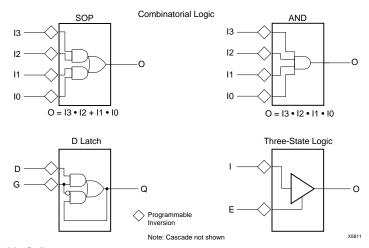

Figure 5 shows the different possible implementations of a single CLC. Each CLC has four logic inputs plus a cascade input, and one logic output plus a cascade output (cascade not shown). The logic output has three-state control, and each CLC is also connected to a global reset network. Each of the four inputs can be configured as inverted or non-inverted, so input signal inversions ("bubbling") are free and output bubbles don't matter. Cells do not have to be "wasted" as inverters, which would lower the gate utilization. Any input can be hardwired to logic zero or one.

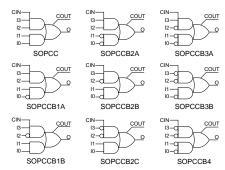

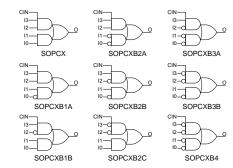

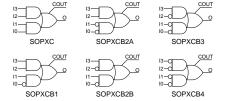

Figure 5: Programmable Cell

For combinatorial logic, the cell has two programmable functions, AND or Sum-of-Products (SOP). Pairs of CLC inputs are internally ANDed, and the two signals are then combined in a circuit programmable as either an OR or an AND gate. The SOP can also be considered a 2-input multiplexer, or a 2-input XOR and XNOR.

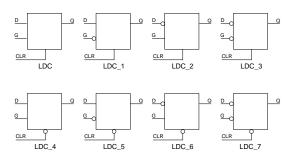

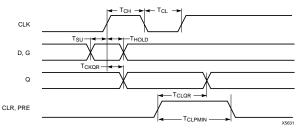

For synchronous logic, configuring the cell-internal feed-back path makes any CLC a latch with D and G inputs (LD primitive). When G is high, the latch is in the pass-through state. Both inputs can be configured to be either active High or active Low. A two-cell latch (LDC primitive) adds an asynchronous CLR input. All latches are also controlled by the global Reset signal.

The XC8100 software automatically combines two adjacent latches through the Cascade connection to create a D-flip-flop. One CLC is the master latch and the second is the slave latch. The flip-flop has a global Reset which does not involve user routing and also has an overriding asynchronous Clear input (FDC primitive). It can also have an asynchronous Preset input that overrides the D input (FDP primitive). Note that neither the feedback connections of both latches nor the master-slave connection use general routing elements, or have programming elements in their paths. This gives the flip-flops excellent speed and metastability behavior. The XC8100 "semi-dedicated" flip-flops combine performance with flexibility in utilization.

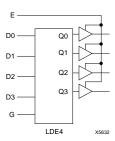

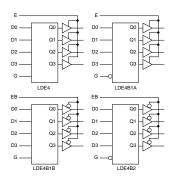

For three-state logic, one of the CLC inputs controls a tristate buffer in the output path (BUFE primitive). The Data and Enable control inputs can be configured active High or active Low. Combining the latch and three-state functions gives a register file capability (LDE4 primitive) which can be used to build FIFOs, see Figure 6.

Figure 6: Quad Latch Bank with Three-State Output Uses Four CLCs

### Global Reset

A global reset signal is automatically distributed to each CLC latch, and therefore each flip-flop. It is controlled internally by the GRST library primitive. It is activated automatically on power-up. When active, the net presets all asynchronous preset flip-flops (FDP primitive) and resets all other flip-flops. In the case of the latches, the clear only takes place when the latches are in the latching state. In

other words, reset does not affect the output in passthrough mode. Global reset is typically complete within 100 ns. See AC timings.

### **Master Reset**

A master reset of the chip is accomplished by pulling the  $\overline{\text{MR}}$  pin low. This starts the power-on reset sequence, presetting all asynchronous preset flip-flops (FDP) and resetting all other flip-flops and latches. The master reset locks out the device for several ms. See the AC timings. The primary use of the master reset is as part of a system, board or module reset.

### Cascade

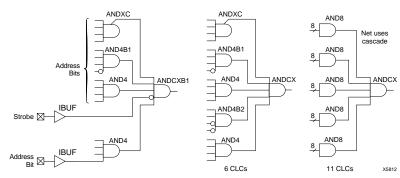

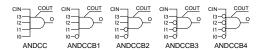

Each CLC has a fifth input and second output for cascade. The cascade inputs and outputs use dedicated routing to the nearest cells, extending along an entire row. See Figure 8. Combining two adjacent CLCs through their cascade connection expands the functionality. For synchronous logic, cascade is used to automatically build flip-flops, as explained earlier. For combinatorial functions, the software cascades CLCs to build the wider ANDs and SOPS in the primitive library. Cascade can also be used (with ANDCC and SOPCC primitives) to build functions like wide decode and fast shift registers. The cascade connection has several advantages over conventional routing:

- It is faster because it doesn't need a programmable element and it avoids the delay of the cell output driver.

- It has known timing.

- It does not consume any general routing resources.

### **Address Decoders**

The cascade can be used to build wide decode functions. See Figure 7. For example, five CLCs, each configured as a four-input AND gate, can feed a CLC configured as a four-input AND with cascade (ANDCX). The delay for this 20 input decoder is less than 12 ns. Using two-CLC AND8 primitives produces a forty-input decoder that has a delay less than 15 ns. If the address is available, the strobe delay is about 8 ns (-1).

## Programmable Interconnect

Most programmable logic devices have to balance routing/ interconnect resources with die size and cost. However, the XC8100 architecture offers a small die size with an abundant amount of routing, both metal-segment wires and interconnections. The routing software has many alternatives to make sure a design is fully routed.

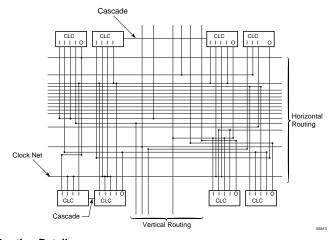

Figure 8 is an example diagram of the interconnect, showing only the wires actually used for nets in a design. In the horizontal direction, there are 47 wires that each cell can connect to (not all shown in Figure 8). There are 5 separate types, three of which can also be connected horizontally:

Figure 7: Wide Decode Using Cascade

- single-block (a block is 4 cells wide) length wires extend for one block only. They are used primarily to connect the cells within the block.

- double-block length wires connect left and right to adjacent blocks.

- quad-block length wires connect left and right for a length of four blocks. They can connect any cells that are spanned within the four-block length.

- horizontal long lines run the entire width of the device.

They can connect any cells in a row. These wires are optionally used by the row buffers.

- · constant 0 used for logic 0 and 1 inputs.

There are two wire types in the vertical direction:

- double-block length wires, analogous to the horizontal ones.

- quad-block length wires.

In addition to the wires that run along all the rows and columns of the device, there are twelve vertical long lines (VLLs) on each side of the device. They interconnect with any horizontal wire and make routing with preassigned I/Os easier.

### **Global Nets**

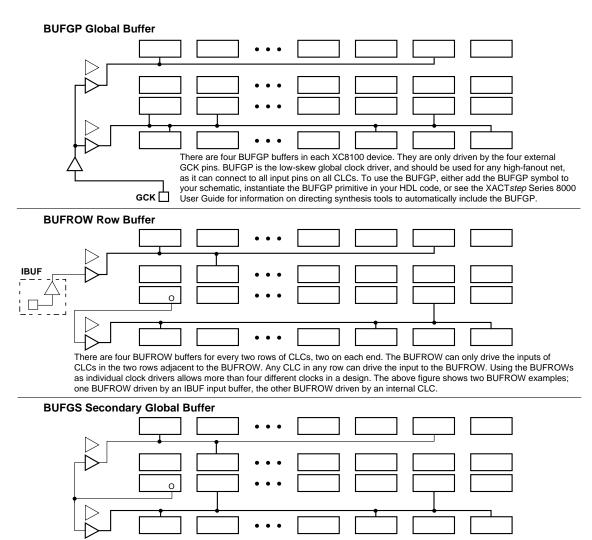

Global nets are those needing optimized timing or low skew for the distribution of clock, time-critical and/or high fan-out control signals. The XC8100 has dedicated hardware resources for this purpose. The XC8100 system is very flexible since the various buffers can be used independently or together, for clocks or data. See Table 3, Figure 9, and Figure 10. Four package pins, GCK1-4, feed four dedicated high drive buffers (BUFEDGE) that drive four vertical long lines (not part of the general lines described in the Programmable Interconnect section) on two sides of the device. If the GCK pins are not used, they are available for user I/O. Each pair of rows of CLCs also has four dedicated buffers (BUFROW). To limit fanout, the XC8100 software can also use CLCs as buffers (BUF1X primitive). These buffers can be automatically selected by the synthesis software.

Figure 8: Example Routing Detail

Table 3: XC8100 Buffers

| Name   | Description                                                                                                                                                                                                                                                                                                                                                                                                                               |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BUFGP  | This global buffer is formed by a BUFEDGE driving some number of BUFROWs. The source for this buffer is one of four specific external pins, GCK1 - 4. The output of the buffer can drive all CLCs in a chip. The maximum number of BUFGP buffers is four.                                                                                                                                                                                 |

| BUFGS  | This can be thought of as an internal BUFGP. It is accessible internally and can drive any number of BUFROWs.                                                                                                                                                                                                                                                                                                                             |

| BUF1X  | This buffer is formed by using a single CLC. It has the same drive and fanout characteristics as the CLC. It can be automatically selected by synthesis tools to limit fanout in critical paths.                                                                                                                                                                                                                                          |

| BUFROW | This is a dedicated high drive buffer whose output drives all CLCs in the driven row. The input to this buffer is from a CLC or from external pads through IBUF cells. Using this buffer automatically constrains the placement of the driven CLCs to the row. Each BUFROW drives two rows of CLC/FFs:  XC8100  48 CLCs (24 FFs)  XC8101  48 CLCs (24 FFs)  XC8103  64 CLCs (32 FFs)  XC8106  96 CLCs (48 FFs)  XC8109  112 CLCs (56 FFs) |

Figure 9: XC8100 Buffer Configurations

BUFGS is a library primitive that utilizes BUFROWs to form a global low-skew driver. The BUFGS can drive any number of CLCs, since it uses a BUFROW to drive the CLCs in each row. If there are no driven CLCs in a row, then no BUFROW is used in that row. Like the BUFROW, the BUFGS can be driven by a CLC (shown above) or by an IBUF input buffer.

X593

Figure 10: XC8100 Buffer Usage

## Input/Output Cell (IOC)

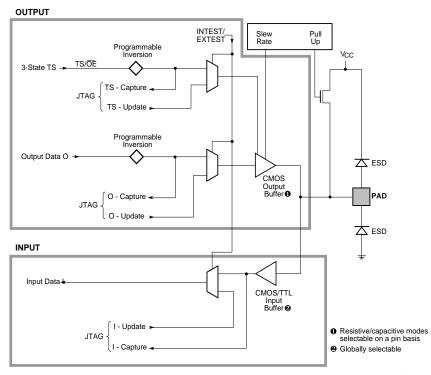

The IOCs form the interface between the internal logic and the I/O pads of the device. Each IOC consist of a programmable output section that drives the pad, and a programmable input section that receives data from the pad. See Figure 11. Aside from being connected to the same pad, the input and output sections have nothing else in common.

### Input

The input section receives data from the pad or the JTAG circuitry and passes it to the interconnect structure. Inputs can be globally programmed for TTL or CMOS input thresholds. TTL is the default. There are two input buffer timing specifications. The faster one is selected by using the IBUF library element, while a delayed timing is available with the DBUF library element. The DBUF is used for the data signal to guarantee zero hold time if data and clock signals are going from external pins to an internal flip-flop.

## **Pull-up Resistor**

Each I/O pad can be programmed with or without a pull-up resistor. This selection is independent of the IOC usage. The default is for the software to automatically program the pull-up resistor to prevent a floating input. The pullup is about 50K ohms.

## **Output**

The output section takes data and three-state control information from the interconnect structure. It can also take data from the JTAG scan circuitry. Output data can be inverted or non-inverted.

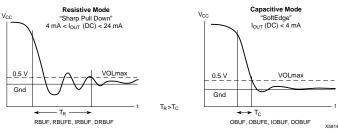

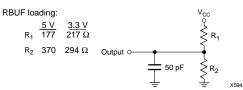

The output driver has four options: 1) it can be permanently disabled, making the pad an input-only pad (IBUF, DBUF primitives); 2) the driver can be permanently active, making the pad output only (OBUF, RBUF primitives); 3) it can be three-state controlled from either the internal logic or the JTAG circuitry (OBUFE, RBUFE primitives): or 4) a combination (IOBUF). The three-state control signal can be inverted, allowing the signal to be thought of as either active Low Output Enable, or active Low three-state. The outputs are CMOS compatible, which results in an unloaded rail-to-rail signal swing. Each output can be individually configured for either of two slew-rate options, which affect only the pull-down operation. See Figure 12.

When programmed for resistive mode (RBUF, RBUFE primitives), the pull-down transistor is driven hard, resulting in a practically constant on-resistance of < 20  $\Omega$ . This results in the fastest High-to-Low transition, and the capability to sink up to 24 mA. Resistive mode is required for driving terminated transmission lines with 4 to 24 mA of dc sink current and for highly capacitive loads (>200 pF). When many resistive mode outputs switch simultaneously High to Low, this configuration option may result in excessive ground bounce. The user must limit the number of simultaneous transitions per package ground pin - see the DC specification section.

The slew rate limited configuration is capacitive mode (OBUF, OBUFE). This mode uses a novel, patent-pending method of slew rate control that reduces ground bounce without any significant delay penalty. The High-to-Low transition starts as described above, but the drive to the pull-down transistor is reduced as soon as the output voltage reaches a value around 1V. This results in a higher resistance in the pull-down transistor, a slowing down of the falling edge, and significantly reduced ground bounce. In this mode the output driver sinks 4 mA at V<sub>OL</sub>. This mode is recommended for outputs requiring less than 4 mA DC or for capacitive loads of less than 200 pF. See Figure 13 for typical output V/I characteristics.

Figure 11: Input/Output Cell Diagram

X5775

Figure 12: Output Slew Rate Options

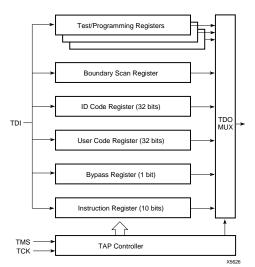

## IEEE 1149.1 Boundary Scan

The XC8100 has similar IEEE 1149.1/JTAG (Joint Test Action Group) capabilities as the XC4000. Three differences are that:

- The XC8100 JTAG pins TDI, TDO, TMS and TCK are dedicated.

- The XC8100 supports the JTAG instruction IDCODE.

- The XC8100 instruction word length is 10 bits.

JTAG is an industry-standard serial access interface designed to provide an efficient and convenient means of testing and monitoring integrated circuit components on a circuit board. It was designed to provide an alternative to the traditional bed-of-nails circuit board testers which have difficulty accommodating high pin count, fine pitch component packages, and which are unable to support surface mount boards with components on both sides. In the XC8100, the JTAG interface both serves its traditional board testing role and is also the primary test and antifuse programming interface. Virtually all factory test and programming operations are accessed via the JTAG interface.

The 1149.1 interface consists of four pins, TDI, TDO, TCK, and TMS. The basic concept is that the TDI and TDO pins form the beginning and end of serial shift registers within the device. See Figure 14. TCK and TMS provide a means to select a specific shift register and when and what to shift.

Figure 13: Typical Output V/I Characteristics

In order to provide control of the JTAG data registers, the JTAG specification includes a definition of what is called the test access port (TAP) controller. Since there are only two pins to control it, the TAP controller is designed as a state machine with one input, TMS. The XC8100 TAP controller is clocked by the TMS pin and uses the standard IEEE JTAG state diagram. The XC8100 provides the full set of IEEE 1149.1 boundary scan instructions, including the optional IDCODE. See the following Table:

| Instruction Code | Instruction       | Description                  |

|------------------|-------------------|------------------------------|

| 000000000        | INTEST/<br>EXTEST | Forces state of I/O cells    |

| 000000001        | SAMPLE            | Samples state of I/O cells   |

| 1111111101       | USERCODE          | User-programmable register   |

| 1111111110       | IDCODE            | Samples existing device code |

| 1111111111       | BYPASS            | Selects bypass register      |

### INTEST/EXTEST

This instruction combines the mandatory JTAG EXTEST with the optional INTEST instruction. When selected, this instruction uses the JTAG boundary scan register values to:

- Drive the signal at the output of the input buffer (INTEST)

- Drive the data input of the output buffer (EXTEST)

- Drive the enable input of the output buffer (EXTEST)

To do this, the signals which normally drive these nodes are disabled via multiplexers.

### **SAMPLE**

This instruction samples the logic values at each pin. For a bidirectional I/O pin, three values are sampled:

- . The signal at the output of the input buffer

- The signal at the data input of the output buffer

- The signal at the enable input of the output buffer

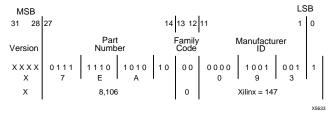

### **IDCODE**

This instruction provides access to a 32-bit data register that always captures a 32-bit word built into the device. The register can be read by the programming software. See Figure 15.

Figure 14: XC8100 IEEE 1149.1 Architecture

In hex, the IDCODEs are:

| XC8100 | _  | X7E90093 |

|--------|----|----------|

| XC8101 | 1X | X7E94093 |

| XC8101 | 2X | X7E95093 |

| XC8103 | 1X | X7E9C093 |

| XC8103 | 2X | X7E9D093 |

| XC8106 | 1X | X7EA8093 |

| XC8106 | 2X | X7EA9093 |

| XC8109 | 2X | X7B58093 |

#### **USERCODE**

This instruction provides access to a 32-bit data register which can be programmed by the user, for example with the design version.

#### **BYPASS**

This instruction places a single flip-flop between TDI and TDO. Its capture value is 0.

The Boundary Scan Register bits are shown in the pinout tables (The pinout tables section begins on page 25). There are three bits for each I/O pin. The bits are TS, O, and I, as shown in Figure 11, with TS closest to the TDO end. There is a fourth bit for the four GCK/I/O pins.

# **Power Consumption**

The XC8100 has the power consumption characteristics of Xilinx CMOS FPGAs. There are two components to the power. DC quiescent power is low and almost all of the power dissipation is a function of the design speed, the number of nodes toggling, and the capacitive loading on the outputs.

Quiescent current can be minimized by attention to its six sources:

- 1. Using the TTL input voltage mode draws current of about 8 mA to 30 mA, worst case, depending on the device, the package, and the voltage state of the input pins. There are two components to this current. First, the reference circuit draws 8 mA worst case, 4 mA typical, independent of device. Second, each I/O pin will draw about 100 μA worst-case if the input to the pin is held at DC low. Therefore this component depends on the circuit and the package (number of I/Os available). Both components are eliminated by selecting CMOS input levels (2.2 V trip point). At 3.3 V operation, the input level must be CMOS, so this source of current is not applicable.

- Pulling down an I/O pin with the weak pull-up transistor enabled draws about 50 μA per pin at 3.3 V, 100 μA per pin at 5 V. The weak I/O pull-ups are automatically enabled by the design software (although they are automatically turned off when an I/O is driven by the FPGA). They can be disabled within the Series 8000 software by the command: set\_attribute -port my\_input\_pin pullup false.

- 3. Leaving a non-pulled up I/O pin floating can produce a worst-case current of about 0.5 mA per pin at 3.3 V, 1mA per pin at 5 V. This occurs when the input voltage is at the I/O trip point. To eliminate this source of quiescent current, do not allow non-pulled up pins to float. Remember the default is that all I/Os have pull-ups. The JTAG TCK pin, which by the IEEE specification may not have a pullup or pulldown, must be connected to V<sub>CC</sub> or GND to eliminate it as a source of quiescent current.

- 4. MicroVia leakage current depends on the design and is not under user control. It is typically very small and can be calculated after the design is placed and routed. Series 8000 software has a command (report -

Figure 15: XC89106 IDCODE Register

stress\_factor) that shows the number of antifuses to be programmed in the design and the number of "critical" antifuses. Critical antifuses are those which have the potential of being between two active and different nets. Only these antifuses can contribute to quiescent current. The worst-case theoretical MicroVia leakage current, assuming all critical antifuses have opposite logic potential on their terminals, is calculated by multiplying each critical antifuse by 100 pA at 3.3 V, 10 nA at 5 V. On small designs (XC8100, XC8101) this number is typically less than a few hundred  $\mu\text{A}$ , worst case temperature and 5.25 V. At room temperature, 5.0 V, the MicroVia leakage would be about an order of magnitude less.

- CMOS leakage current is proportional to the device and is not under user control. It is typically a few μA. Current (May 96) test limits are a few mA for the XC8106 at 5 V with other devices proportionally less or more.

- 6. A small current is used by an internal voltage detector on the VPP pin. With VPP tied to VCC, this current is about 100  $\mu$ A at 5 V, 30  $\mu$ A at 3.3 V. A larger current exists if VPP is tied to ground. A minor enhancement is scheduled for 2H 1996 to eliminate this source of current.

Attention to these factors can result in a typical quiescent current of a few  $\mu As$  for small designs at 3.3 V.

Almost all power is dynamic, and is determined by the number of nodes, their capacitance, and the frequency they are discharging and charging. This number is very design dependent, especially on the number and frequency of inputs that are toggling, not just the circuit implementation in the FPGA.

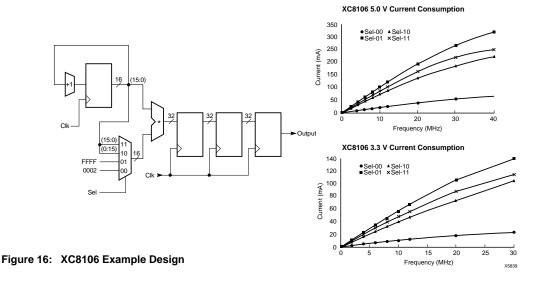

Figure 16 is a test design that illustrates the power consumption of an XC8106 at 5 V and 3.3 V. The design uses 1550 CLCs (90% of the XC8106), with 10% sequential logic and 90% combinational. All outputs are unloaded. The design consists of a 16-bit counter, a 16-bit 4-to-1 MUX, and a 16-bit multiplier. The select lines, by controlling one of the multiplier inputs, determine the number of nodes that switch.

# 3.3 V Operation

XC8100 devices can be operated at 5 V or 3.3 V. At 3.3, the timing parameters are derated (see "Device Specifications" on page 33). I/O pins cannot be directly driven above  $V_{CC}$ , although there are standard resistor solutions. The CMOS/TTL input voltage choice should be set in the software to CMOS.

# **Programming**

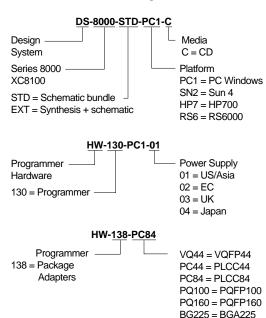

Programming XC8100 FPGAs is supported by several methods: 1) the Xilinx HW-130 Programmer; 2) selected third-party programmers; 3) distributors; and 4) Xilinx for volume designs. Series 8000 software has a Demo Mode where no key is needed. The software can be copied for programming XC8100 devices in parallel using multiple PCs or workstations. Another option is to run multiple Windows 95 sessions to multiple serial ports.

On the device, only 5 pins are required for the programming interface. The JTAG pins TDI, TDO, TCK, and TMS are used for addressing the elements to be programmed, for shifting the programming data in, for verification, and for testing. The Vpp pin provides a high voltage during programming and is used to measure the resistance of the programmed antifuse.

June 1, 1996 (Version 1.0)

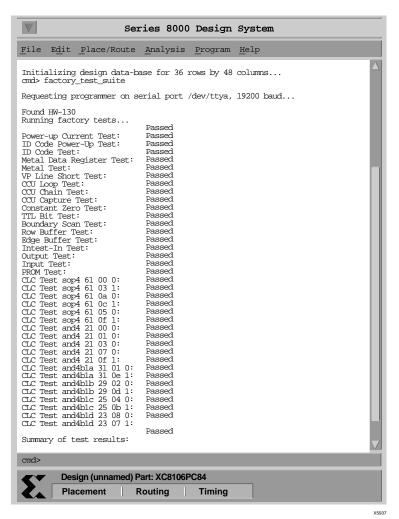

Figure 17: Series 8000 Software Testing a Device in an HW-130

The programming algorithm includes measuring the resistance of the programmed MicroVia antifuse to guarantee the speed and functionality of the part. Since this is the one aspect that cannot be verified during factory test, it completes the 100% functional testing of the device.

There are several unique capabilities in the XC8100 programming architecture. They are aimed at addressing the issues of accurate programming and 100% post-programming yield. Series 8000 programming software takes advantage of a unique XC8100 feature that each and every antifuse can be randomly addressed. The capabilities include:

Series 8000 software can run a complete functional factory test on an unprogrammed part in a programmer using the JTAG port. Figure 17 is a screen shot of the Series 8000 software running the test suite on an unprogrammed device

- As noted above, during programming the actual resistance of each programmed fuse is measured;

- To guarantee post-programming yield, after programming all nets are checked to see that only intended nets have been programmed, i.e. no unintended antifuses have been programmed. This is done without user test vectors;

- While these capabilities ensure that XC8100 devices are 100% testable without vectors, it is possible to apply post-programming test vectors using the programmer hardware. The XC8100 software can take simulation vectors and apply them to the device and read back the results through the JTAG port.

5-14 June 1, 1996 (Version 1.0)

## **Testing**

The functionality of gate arrays and older one-time programmable (OTP) PLDs has to be verified with test vectors after personalization. Even then, fault coverage is often below the standards of off-the-shelf devices. XC8100 FPGAs address this problem through the following:

- · An architecture designed for testability.

- · The use of extensive on-chip test circuitry.

- A novel method of post-programming net verification.

The test circuitry is used in conjunction with a set of special test instructions which are written to the dedicated JTAG port. This circuitry allows each device function — except the actual antifuses to be programmed — to be separately isolated and 100% tested before shipping. The programmed antifuses are later verified by the programmer. The result is the XC8100 family achieves the 100% tested level of Xilinx SRAM-based reprogrammable devices.

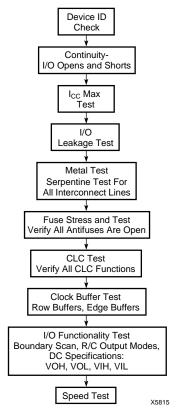

In concept, XC8100 FPGAs are tested in four stages. The first three are done at the factory before programming, the last by the programming hardware. First, both the functionality and speed performance of all CMOS logic on the device are verified. This includes programming circuitry, the CLC logic, the IOC logic, and the long line and clock buffers. The inputs and outputs of all the internal logic are accessible for 100% testing. Second, all metal interconnect lines are tested. Special patented circuitry allows all metal lines to be accessible. Third, all antifuses are stressed and tested to be in the correct state (off) before programming. Fourth, during programming the programmer checks that all interconnect elements meet their resistance specification after programming. The current through each programmed antifuse is measured so that the resistance meets the speed specification. Moreover, all nets are tested to ensure no antifuses have been inadvertently programmed.

# **Metastability Calculation**

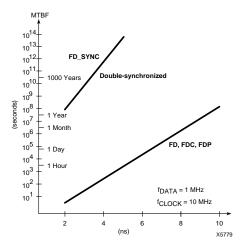

Whenever a clocked flip-flop synchronizes an asynchronous input, there is a small probability that the flip-flop will exhibit an unpredictable clock-to-Q delay. This occurs when the input transition not only violates the setup and hold time specifications, but actually occurs within the tiny timing window where the flip-flop accepts the new input. This results in the flip-flop's output being between a logic zero and logic one — a "metastable" state. The time required to transition from the metastable state to a valid logic one or zero is the delay. The Mean Time Between Failure (MTBF) for metastability is defined statistically. Figure 19 shows the data for the XC8100 using a 1 MHz data rate and a 10 MHz clock.

The XC8100 offers two options in designing for metastability. The standard XC8100 flip-flops (FD, FDC, FDP) provide MTBFs that are in the range of programmable logic devices today. An additional option is the four-CLC, double-synchronized versions of the flip-flop elements, (FD\_SYNC),

Figure 18: XC8100 Factory Test Flow Chart Used for the Factory Test of all XC8100 FPGAs

which automatically use two flip-flops connected through cascade. This option has one additional clock cycle of latency. This may make sense for certain signals given the large number of CLCs/FFs on XC8100 FPGAs. Figure 19 shows that for these flip-flops, a delay of 3 ns has a MTBF over 100 years.

Figure 19: Metastable MTBF

# XACT step Series 8000 Development System

The XC8100 development system, part of the Xilinx XACTstep system, employs many new features to take advantage of the new architecture:

- · command shell and unified database structure

- new placement and routing software

- ASIC-like design flow

- 1-to-1 mapping between input netlist and CLCs in the device: TrueMap Logic

- maintains hierarchical information throughout the design flow

- maintains original net and instance names throughout the flow

- · EDIF and SDF for CAE tool interfacing

Similar to other Xilinx FPGAs, the XC8100 FPGA design flow is based on a four-step process:

- Design entry and functional verification using standard CAE tools.

- 2. Design implementation using XC8100 tools.

- 3. Design verification using standard CAE tools.

- 4. For the XC8100, programming is the fourth step.

## Design Entry

The design is first described using a variety of methods: Verilog, VHDL, schematic, equations, or state machine. The designer uses standard CAE tools in this phase — Xilinx supplies a design kit (synthesis models, schematic library) for the third-party CAE vendor's tool. Some CAE vendors supply the design kit themselves. The flexibility of the XC8100 architecture means that the user can design

with little concern for the architecture or implementation details. In most cases, the software automatically chooses all the capabilities described in the Architecture section.

## **Design Implementation**

The second step in the process takes an EDIF netlist output from the design entry stage and:

- · reads the design netlist, including hierarchy.

- places the netlist primitives on specific CLCs without changing any of the logic. This insures a 1-1 correspondence between design and implementation.

- routes all nets. The router uses rip-up-and-retry algorithms to shift congestion.

- calculates actual timing delays for all nets. This

information is used for timing analysis and by third party

timing/simulation tools.

- shows a view of the design at the physical level.

Figure 21 is an output of the Viewer, showing the dense routing used to implement a 6502 VHDL model in an XC8106.

- generates fusemap and files for the programmer hardware.

## **Design Verification**

The third step lets the designer use third-party CAE tools for analysis or simulation of the timings exported by Series 8000 software.

## **Programming**

All programming software is included in XACT*step* Series 8000. The software connects to the programmer hardware through a serial port.

### **Platforms**

The XC8100 software runs under Windows 3.1, Windows 95, Windows NT, SunOS 4.1.1 or later, Solaris 2.4 or later, HPUX 9.05 or later, and AIX 3.2 or later. Platforms include PC, Sparcstation, HP PA, and RS6000.

### Workstation General Requirements

- minimum 32 MB of memory

- hard disk with at least 40 MB available for XC8100 programs, symbol libraries and data files

- minimum swap space of 100 MB

- color console monitor (any text terminal is sufficient when using only the XC8100 command shell)

- two or three-button mouse (no mouse is required when using only XC8100 command shell)

- postscript printer such as the Apple Laser Writer II

## Sun Sparcstation

- SunOS 4.1.1 or later, Solaris 2.4 or later

- access to CD ROM drive

- Motif Window Manager or OpenLook Window

### HP PA series

- access to CD ROM drive

- HPUX 9.0 or later

- HP VUE 3.0 or later

### RS 6000 series

- access to CD ROM drive

- AIX 3.2 or later

## IBM Compatible PC's

- Run on 386 or 486, Pentium recommended

- 8 MB RAM (small designs), 16 MB recommended

- hard disk space varies with the selected installation:

8 MB min, 13 MB typ, and 57 MB full

- color monitor capable of running in VGA mode or better

- two or three button Windows-compatible mouse

- Windows driver program for graphics adapter and display

- access to CD ROM drive

## HW-130 Programmer

- PC or workstation serial port

Figure 20: XC8100 Synthesis Design Flow

## Series 8000 Software Ordering Information

Figure 21: XC8100 Architecture in Software Viewer

5-18

# XC8100 Synthesis Library

The XC8100 synthesis library is the set of primitives used by synthesis CAE tools to generate the gate-level EDIF net list for the XC8100 software tools. It does not include macros used for schematic design entry. The library uses the standardized conventions of the Xilinx unified library.

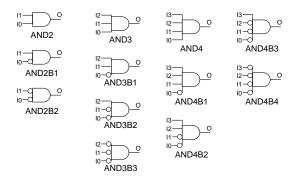

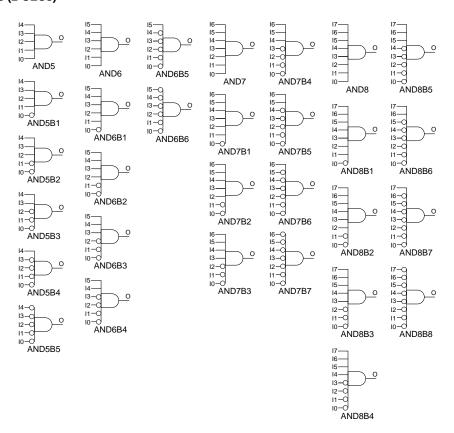

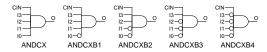

## AND Gates (1 CLC)

## **AND Gates (2 CLCs)**

### ANDCC - AND with Cascade In and Out

### 1 CLC

### ANDCX – AND with Cascade In

## ANDXC - AND with Cascade Out

### 1 CLC

### **BUF - Clock/Net Buffers**

### **BUFE - Three-State Buffers**

### 1 CLC

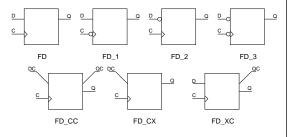

### FD - D Flip-Flops

## 2 CLCs

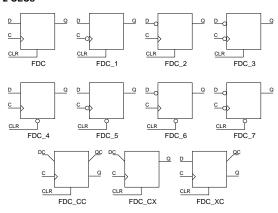

## FDC - D Flip-Flop with Asynchronous Clear

### 2 CLCs

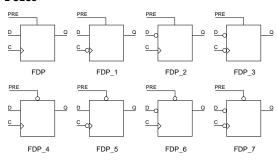

## FDP - D Flip-Flop with Asynchronous Preset

### 2 CLCs

## **GND - Ground Signal Tag**

### 0 CLCs

### **GRST**

#### 0 CLCs

### IBUF, DBUF - Input Pad Buffers

## **INV** - Inverting Buffers

### 1 CLC

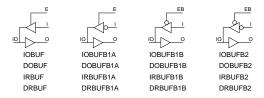

# IOBUF, DBUF, IRBUF, DRBUF - Bidirectional Three-State Pad Buffers

### 0 CLCs

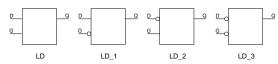

## LD - Transparent Data Latches

### 1 CLC

# LDC - Transparent Data Latch with Asynchronous Clear

### 2 CLCs

## LDE4 - Quad Latch Bank with Three-State Output

### 4 CLCs

## M2\_1 - 2 to 1 Multiplexers

### 1 CLC

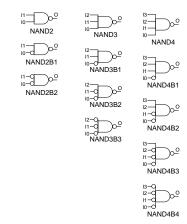

## NAND Gates (1 CLC)

### 1 CLC

## NAND Gates (2 CLCs)

## 2 CLCs

## NOR Gates (1 CLC)

1 CLC

## NOR Gates (2 CLCs)

2 CLCs

## **OBUF, RBUF - Output Pad Buffers (C, R modes)**

0 CLCs

# OBUFE, RBUFE – Output Pad Three-State Buffers

0 CLCs

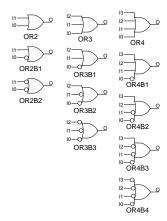

## OR Gates (1 CLC)

1 CLC

## OR Gates (2 CLCs)

2 CLCs

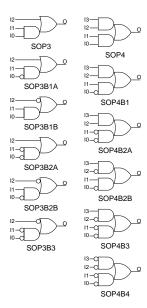

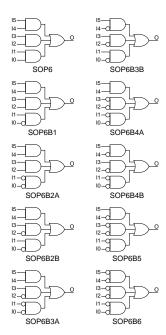

## SOP - Sum of Products (1 CLC)

1 CLC

# SOP - Sum of Products (2 CLCs)

2 CLCs

# SOPCC – Sum of Products with Cascade In and Out

1 CLC

# SOPCX – Sum of Products with Cascade In 1 CLC

# SOPXC – Sum of Products with Cascade Out 1 CLC

# VCC - V<sub>CC</sub> Signal Tag

0 CLCs

# XOR2, XNOR2 – Two-Input Exclusion OR/NOR 1 CLC

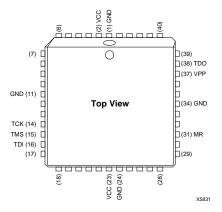

# **Pin Descriptions**

### $V_{CC}$

Two or more, depending on the package type. All must be connected to the +5 V/3.3 V supply voltage.

### $V_{PP}$

$\rm V_{pp}$  is the programming voltage. This pin can be left floating, but will draw slightly less ICCO if connected to  $\rm V_{CC}$  during operation.

#### **GND**

Four or more, depending on the package type. All must be connected to ground.

#### GCK1 - GCK4 - I/O

Four global clock inputs each connect to a dedicated internal global buffer (bufedge) with short delay and minimal skew. If not used for this purpose, these pins are user I/O.

#### **TDO**

Test Data Output pin for JTAG operation and testing. This is a dedicated pin and is not available for user I/O. It has no pull-up or pull-down.

### TDI, TCK, TMS

Test Data In, Test Clock, and Test Mode Select inputs for JTAG boundary scan, programming, and testing. These are dedicated pins and are not available for user I/O. TMS and TDI have pull-ups, TCK does not.

### **MASTER RESET**

This active-low pin has the same functionality as removing  $V_{CC}$  and then reapplying power. It resets all synchronous logic. Master Reset three-states all I/O pins while held low, and can be useful for board testing. The pin has an internal pull-up resistor, so no external resistor is needed if the pin

is unused. All synchronous logic is reset time TMRQ after  $\overline{MR}$  is raised high. It is recommended that  $\overline{MR}$  on the XC8100 (625 gate) device have a  $1k\Omega$  resistor in series to limit current from signals that violate the  $V_{IN}$  specification of -0.5V.

#### I/O

These pins are configured by the user to be either input or output. Programmable options include input voltage levels (CMOS or TTL on a per-chip basis) and output slew rate (resistive or capacitive mode on a per-pin basis). If an I/O is not used, an internal pull-up resistor is automatically enabled, so no external resistor is required.

# **XC8100 Pin Assignments**

The XC8100 pinout is based on the XC4000 pinouts. This means that, for any package, power and control pins are on the same pins as in the XC4000. However, not all the control pins have the same function. Typically the XC4000 M0/M1/M2 pins are fixed. If JTAG is not used on the XC8100, this is compatible. DONE can be an input or an output. If it's an input, the XC8100 trace would have to be cut. The  $V_{PP}$  pin is compatible with either CCLK as an input or outputs, although  $V_{PP}$  has a larger input capacitance. Following is the mapping:

| XC8100          | XC4000                                            |

|-----------------|---------------------------------------------------|

| Same as XC4000  | _                                                 |

| Same as XC4000  | _                                                 |

| TMS             | MO                                                |

| TCK             | M1                                                |

| TDI             | M2                                                |

| TDO             | TDO                                               |

| V <sub>PP</sub> | CCLK                                              |

| MR              | DONE                                              |

|                 | Same as XC4000 Same as XC4000 TMS TCK TDI TDO VPP |

# Number of Available I/O Pins

| Device |         |      |      | Packages |       |       |       |

|--------|---------|------|------|----------|-------|-------|-------|

| Device | Max I/O | PC44 | VQ44 | PC84     | PQ100 | PQ160 | BG225 |

| XC8100 | 32      | 32   | 32   | _        | -     | _     | _     |

| XC8101 | 72      | (32) | (32) | 61       | 72    | _     | _     |

| XC8103 | 128     | 32   | 32   | 61       | 64    | (128) | -     |

| XC8106 | 168     | _    | _    | 61       | 76    | (129) | (168) |

| XC8109 | 192     | _    | _    | 61       | _     | 129   | 192   |

Note: Parentheses indicates future products

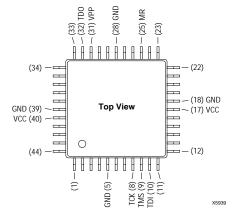

# **XC8100 Pinouts**

| Pin<br>Description | PC44 | VQ44 | Bound<br>Scan |

|--------------------|------|------|---------------|

| VCC                | 2    | 40   | -             |

| I/O                | 3    | 41   | 69            |

| I/O                | 4    | 42   | 72            |

| I/O                | 5    | 43   | 75            |

| I/O                | 6    | 44   | 78            |

| I/O                | 7    | 1    | 81            |

| I/O                | 8    | 2    | 84            |

| GCK1-I/O           | 9    | 3    | 87            |

| I/O                | 10   | 4    | 91            |

| GND                | 11   | 5    | -             |

| I/O                | 12   | 6    | 94            |

| I/O                | 13   | 7    | 97            |

| TCK                | 14   | 8    | -             |

| TMS                | 15   | 9    | -             |

|                    |      |      |               |

| Pin<br>Description | PC44 | VQ44 | Bound<br>Scan |

|--------------------|------|------|---------------|

| TDI                | 16   | 10   | -             |

| GCK2-I/O           | 17   | 11   | 0             |

| I/O                | 18   | 12   | 4             |

| I/O                | 19   | 13   | 7             |

| I/O                | 20   | 14   | 10            |

| I/O                | 21   | 15   | 13            |

| I/O                | 22   | 16   | 16            |

| VCC                | 23   | 17   | -             |

| GND                | 24   | 18   | -             |

| I/O                | 25   | 19   | 19            |

| I/O                | 26   | 20   | 22            |

| I/O                | 27   | 21   | 25            |

| I/O                | 28   | 22   | 28            |

| I/O                | 29   | 23   | 31            |

| I/O                | 30   | 24   | 34            |

| Pin         |      |      | Bound |

|-------------|------|------|-------|

| Description | PC44 | VQ44 | Scan  |

| MR          | 31   | 25   | _     |

| I/O         | 32   | 26   | 38    |

| GCK3-I/O    | 33   | 27   | 41    |

| GND         | 34   | 28   | _     |

| I/O         | 35   | 29   | 44    |

| I/O         | 36   | 30   | 47    |

| VPP         | 37   | 31   | _     |

| TDO         | 38   | 32   | -     |

| I/O         | 39   | 33   | 51    |

| GCK4-I/O    | 40   | 34   | 54    |

| I/O         | 41   | 35   | 57    |

| I/O         | 42   | 36   | 60    |

| I/O         | 43   | 37   | 63    |

| I/O         | 44   | 38   | 66    |

| GND         | 1    | 39   | _     |

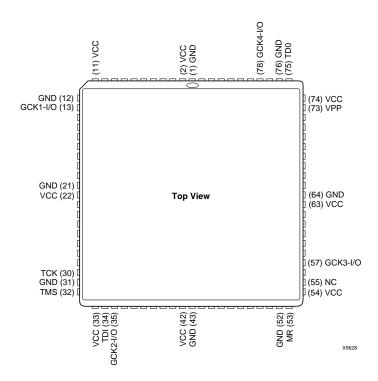

# **XC8101 Pinouts**

| Pin<br>Description | PC84 | PQ100 | Bound<br>Scan |

|--------------------|------|-------|---------------|

| VCC                | 2    | 92    | Ocan          |

|                    |      |       |               |

| 1/0                | 3    | 93    | 159           |

| I/O                | 4    | 94    | 162           |

| I/O                | -    | 95    | 165           |

| I/O                | -    | 96    | 168           |

| I/O                | 5    | 97    | 171           |

| I/O                | 6    | 98    | 174           |

| I/O                | 7    | 99    | 177           |

| I/O                | 8    | 100   | 180           |

| I/O                | -    | -     | 193           |

| I/O                | -    | -     | 196           |

| I/O                | 9    | 1     | 189           |

| I/O                | 10   | 2     | 192           |

| VCC                | 11   | 3     | -             |

| GND                | 12   | 4     | -             |

| GCK1-I/O           | 13   | 5     | 195           |

| I/O                | 14   | 6     | 199           |

| I/O                | 15   | 7     | 202           |

| I/O                | 16   | 8     | 205           |

| I/O                | 17   | 9     | 208           |

| I/O                | 18   | 10    | 211           |

| NC                 | -    | 11    | -             |

| I/O                | 19   | 12    | 214           |

| I/O                | 20   | 13    | 217           |

| GND                | 21   | 14    | -             |

| VCC                | 22   | 15    | -             |

| I/O                | 23   | 16    | 220           |

| I/O                | 24   | 17    | 223           |

| NC                 | -    | 18    | -             |

| I/O                | 25   | 19    | 226           |

| I/O                | 26   | 20    | 229           |

| I/O                | 27   | 21    | 232           |

| I/O                | -    | 22    | 235           |

| I/O                | 28   | 23    | 238           |

| I/O                | 29   | 24    | 241           |

| TCK                | 30   | 25    | -             |

| Pin<br>Description | PC84 | PQ100 | Bound<br>Scan |

|--------------------|------|-------|---------------|

| GND                | 31   | 26    | -             |

| TMS                | 32   | 27    | -             |

| VCC                | 33   | 28    | -             |

| TDI                | 34   | 29    | -             |

| GCK2-I/O           | 35   | 30    | 0             |

| I/O                | 36   | 31    | 4             |

| I/O                | -    | -     | 7             |

| I/O                | -    | -     | 10            |

| I/O                | -    | 32    | 13            |

| I/O                | 37   | 33    | 16            |

| I/O                | 38   | 34    | 19            |

| I/O                | 39   | 35    | 22            |

| I/O                | -    | 36    | 25            |

| I/O                | -    | 37    | 28            |

| I/O                | 40   | 38    | 31            |

| I/O                | 41   | 39    | 34            |

| VCC                | 42   | 40    | -             |

| GND                | 43   | 41    | -             |

| I/O                | 44   | 42    | 37            |

| I/O                | 45   | 43    | 40            |

| I/O                | -    | 44    | 43            |

| I/O                | -    | 45    | 46            |

| I/O                | 46   | 46    | 49            |

| I/O                | 47   | 47    | 52            |

| I/O                | 48   | 48    | 55            |

| I/O                | 49   | 49    | 58            |

| I/O                | -    | -     | 61            |

| I/O                | -    | -     | 64            |

| I/O                | 50   | 50    | 67            |

| I/O                | 51   | 51    | 70            |

| GND                | 52   | 52    | -             |

| MR                 | 53   | 53    | -             |

| VCC                | 54   | 54    | -             |

| NC                 | 55   | 55    | -             |

| I/O                | 56   | 56    | 74            |

GCK3-I/O

| Pin<br>Description | PC84 | PQ100 | Bound<br>Scan |

|--------------------|------|-------|---------------|

| I/O                | 58   | 58    | 80            |

| I/O                | -    | 59    | 83            |

| I/O                | 59   | 60    | 86            |

| I/O                | 60   | 61    | 89            |

| NC                 | -    | 62    | -             |

| NC                 | -    | 63    | -             |

| I/O                | 61   | 64    | 92            |

| I/O                | 62   | 65    | 95            |

| VCC                | 63   | 66    | -             |

| GND                | 64   | 67    | -             |

| I/O                | 65   | 68    | 98            |

| I/O                | 66   | 69    | 101           |

| NC                 | -    | 70    | -             |

| I/O                | 67   | 71    | 104           |

| I/O                | 68   | 72    | 107           |

| I/O                | 69   | 73    | 110           |

| I/O                | 70   | 74    | 113           |

| I/O                | 71   | 75    | 116           |

| I/O                | 72   | 76    | 119           |

| VPP                | 73   | 77    | -             |

| VCC                | 74   | 78    | -             |

| TDO                | 75   | 79    | -             |

| GND                | 76   | 80    | -             |

| I/O                | 77   | 81    | 123           |

| GCK4-I/O           | 78   | 82    | 126           |

| I/O                | -    | -     | 129           |

| I/O                | -    | -     | 132           |

| I/O                | 79   | 83    | 135           |

| I/O                | 80   | 84    | 138           |

| I/O                | 81   | 85    | 141           |

| I/O                | 82   | 86    | 144           |

| I/O                | -    | 87    | 147           |

| I/O                | -    | 88    | 150           |

| I/O                | 83   | 89    | 153           |

| I/O                | 84   | 90    | 156           |

| GND                | 1    | 91    | -             |

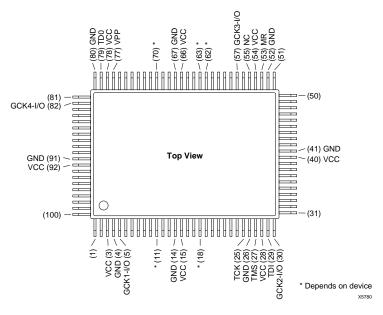

# **XC8103 Pinouts**

| Pin         |         |         | Bound      |

|-------------|---------|---------|------------|

| Description | PC84    | PQ100   | Scan       |

| VCC         | 2       | 92      | -          |

| I/O         | 3       | 93      | 123        |

| I/O         | 4       | 94      | 126        |

| NC NC       | -       | 95      | -          |

| NC          | -       | 96      | -          |

| I/O         | 5       | 97      | 129        |

| I/O         | 6       | 98      | 132        |

| -           | -       | -       | -          |

| -           | -       | -       | -          |

| GND         | _       | -       | -          |

| -           | -       | -       | -          |

| -           | _       | -       | -          |

| I/O         | 7       | 99      | 135        |

| I/O         | 8       | 100     | 138        |

| I/O         | -       | -       | -          |

| I/O         | -       | -       | -          |

| I/O         | 9       | 1       | 141        |

| I/O         | 10      | 2       | 144        |

| VCC         | 11      | 3       | -          |

| GND         | 12      | 4       | -          |

| GCK1-I/O    | 13      | 5       | 147        |

| 1/0         | 14      | 6       | 151        |

| 1/0         | -       | -       | -          |

| 1/0         | -       | -       | -          |

| 1/0         | 15      | 7       | 154        |

| 1/0         | 16      | 8       | 157        |

|             |         |         |            |

| -           | -       | -       | -          |

| GND         | -       | -       | -          |

| -           | -       | -       | -          |

| -           | -       | -       | -          |

| I/O         | 17      | 9       | 160        |

| I/O         | 18      | 10      | 163        |

| NC          | -       | 11      | -          |

| 1/0         | -       | -       | -          |

| 1/0         | 19      | 12      | 166        |

| 1/0         | 20      | 13      | 169        |

| GND         | 21      | 14      |            |

| VCC         | 22      | 15      | -          |

| I/O         | 23      | 16      | 172        |

| 1/0         | 23      | 17      | 172<br>175 |

|             |         |         |            |

| NC<br>I/O   | -       | 18      | -          |

| 1/0         | 25      | 19      | 178        |

| 1/0         | 26      | 20      | 181        |

|             |         |         |            |

| -           | -       | -       | -          |

| -<br>GND    | -       | -       | -          |

| GND         | -       | -       | -          |

|             |         |         |            |

| -<br>I/O    | -<br>27 | -<br>21 | 184        |

|             |         |         |            |

| 1/0         | -       | 22      | 187        |

| 1/0         | -       | -       | -          |

| I/O         | -       | -       | -          |

| Pin         |      |       | Bound    |

|-------------|------|-------|----------|

| Description | PC84 | PQ100 | Scan     |

| I/O         | 28   | 23    | 190      |

| I/O         | 29   | 24    | 193      |

| TCK         | 30   | 25    | -        |

| GND         | 31   | 26    | -        |

| TMS         | 32   | 27    | -        |

| VCC         | 33   | 28    | -        |

| TDI         | 34   | 29    | -        |

| GCK2-I/O    | 35   | 30    | 0        |

| I/O         | 36   | 31    | 4        |

| I/O         | -    | -     | -        |

| I/O         | -    | -     | -        |

| I/O         | -    | 32    | 7        |

| I/O         | 37   | 33    | 10       |

| -           | -    | -     | -        |

| -           | -    | -     | -        |

| GND         | -    | -     | -        |

| -           | -    | -     | -        |

| -           | -    | -     | -        |

| I/O         | 38   | 34    | 13       |

| I/O         | 39   | 35    | 16       |

| NC          | -    | 36    | -        |

| NC          | -    | 37    | -        |

| 1/0         | 40   | 38    | 19       |

| 1/0         | 41   | 39    | 22       |

| VCC         | 42   | 40    |          |

| GND         | 43   | 41    | -        |

| I/O         | 43   |       | -        |

|             |      | 42    | 25<br>28 |

| 1/0         | 45   |       | -        |

| NC          | -    | 44    | -        |

| NC NC       | -    | 45    | -        |

| 1/0         | 46   | 46    | 31       |

| I/O         | 47   | 47    | 34       |

| -           | -    | -     | -        |

| -           | -    | -     | -        |

| GND         | -    | -     | -        |

| -           | -    | -     | -        |

| -           | -    | -     | -        |

| I/O         | 48   | 48    | 37       |

| I/O         | 49   | 49    | 40       |

| I/O         | -    | -     | -        |

| I/O         | -    | -     | -        |

| I/O         | 50   | 50    | 43       |

| I/O         | 51   | 51    | 46       |

| GND         | 52   | 52    | -        |

| MR          | 53   | 53    | -        |

| VCC         | 54   | 54    | -        |

| NC          | 55   | 55    | -        |

| I/O         | 56   | 56    | 50       |

| GCK3-I/O    | 57   | 57    | 53       |

| I/O         | -    | -     | -        |

| I/O         | -    | -     | -        |

| I/O         | 58   | 58    | 56       |

| I/O         | -    | 59    | 59       |

|             |      |       |          |

| Pin         |          |       | Parind |

|-------------|----------|-------|--------|

|             | 2004     |       | Bound  |

| Description | PC84     | PQ100 | Scan   |

| - OND       | -        | -     |        |

| GND         | -        | -     |        |

| -           | -        | -     |        |

| -           | -        | -     |        |

| I/O         | 59       | 60    | 62     |

| I/O         | 60       | 61    | 65     |

| NC          | -        | 62    | -      |

| NC          | -        | 63    | -      |

| I/O         | 61       | 64    | 68     |

| I/O         | 62       | 65    | 71     |

| VCC         | 63       | 66    | -      |

| GND         | 64       | 67    | -      |

| I/O         | 65       | 68    | 74     |

| I/O         | 66       | 69    | 77     |

| NC          | -        | 70    | -      |

| I/O         | -        | -     | -      |

| I/O         | 67       | 71    | 80     |

| I/O         | 68       | 72    | 83     |

| -           | -        | -     | -      |

| -           | -        | -     | -      |

| GND         | -        | -     | -      |

| -           | -        | -     | -      |

| -           | -        | -     | -      |

| I/O         | 69       | 73    | 86     |

| I/O         | 70       | 74    | 89     |

| I/O         | -        | -     | -      |

| I/O         | -        | -     | -      |

| I/O         | 71       | 75    | 92     |

| I/O         | 72       | 76    | 95     |

| VPP         | 73       | 77    | -      |

| VCC         | 74       | 78    | -      |

| TDO         | 75       | 79    | -      |

| GND         | 76       | 80    | -      |

| I/O         | 77       | 81    | 99     |

| GCK4-I/O    | 78       | 82    | 102    |

| 1/0         | -        | -     | -      |

| I/O         | -        | -     | -      |

| I/O         | 79       | 83    | 105    |

| I/O         | 80       | 84    | 108    |

| -           | -        | -     | -      |

| <u> </u>    | -        | -     |        |

| GND         | -        | -     | -      |

|             |          |       |        |

| -           | -        | -     | -      |

| I/O         |          | -     | - 111  |

|             | 81       | 85    | 111    |

| I/O         | 82       | 86    | 114    |

| - NC        | -        | - 07  | -      |

| NC          | <u> </u> | 87    | -      |

| NC<br>L/O   | -        | 88    | -      |

| 1/0         | 83       | 89    | 117    |

| I/O         | 84       | 90    | 120    |

| GND         | 1        | 91    | -      |

|             |          |       |        |

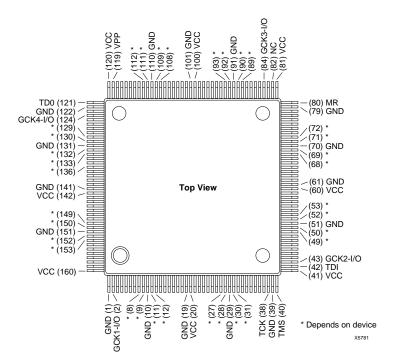

# **XC8106 Pinouts**

| Pin         |      |       | Bound |       | Pin         | Bound |       | Pin  |       |             | Bound |       |      |       |

|-------------|------|-------|-------|-------|-------------|-------|-------|------|-------|-------------|-------|-------|------|-------|

| Description | PC84 | PQ100 | Scan  | PQ160 | Description | PC84  | PQ100 | Scan | PQ160 | Description | PC84  | PQ100 | Scan | PQ160 |

| VCC         | 2    | 92    | -     | 142   | I/O         | 28    | 23    | 250  | 36    | I/O         | -     | -     | -    | 90    |

| I/O         | 3    | 93    | 165   | 143   | I/O         | 29    | 24    | 253  | 37    | GND         | -     | -     | -    | 91    |

| I/O         | 4    | 94    | 168   | 144   | TCK         | 30    | 25    | -    | 38    | 1/0         | -     | -     | -    | 92    |

| 1/0         | -    | 95    | 171   | 145   | GND         | 31    | 26    | -    | 39    | 1/0         | -     | -     | -    | 93    |

| 1/0         | -    | 96    | 174   | 146   | TMS         | 32    | 27    | -    | 40    | I/O         | 59    | 60    | 86   | 94    |

|             | 5    |       |       |       | VCC         | 33    |       |      |       |             | 60    |       |      |       |

| 1/0         |      | 97    | 177   | 147   |             |       | 28    | -    | 41    | 1/0         | _     | 61    | 89   | 95    |

| 1/0         | 6    | 98    | 180   | 148   | TDI         | 34    | 29    | -    | 42    | 1/0         | -     | -     | -    | 96    |

| I/O         | -    | -     | -     | 149   | GCK2-I/O    | 35    | 30    | 0    | 43    | NC          | -     | 62    | -    | -     |

| I/O         | -    | -     | -     | 150   | I/O         | 36    | 31    | 4    | 44    | I/O         | -     | 63    | 92   | 97    |

| GND         | -    | -     | -     | 151   | I/O         | -     | -     | 7    | 45    | I/O         | 61    | 64    | 95   | 98    |

| I/O         | -    | -     | -     | 152   | I/O         | -     | -     | 10   | 46    | I/O         | 62    | 65    | 98   | 99    |

| I/O         | -    | -     | -     | 153   | I/O         | -     | 32    | 13   | 47    | VCC         | 63    | 66    | -    | 100   |

| I/O         | 7    | 99    | 183   | 154   | I/O         | 37    | 33    | 16   | 48    | GND         | 64    | 67    | -    | 101   |

| I/O         | 8    | 100   | 186   | 155   | I/O         | -     | -     | -    | 49    | I/O         | 65    | 68    | 101  | 102   |

| I/O         | -    | -     | 189   | 156   | I/O         | -     | -     | -    | 50    | I/O         | 66    | 69    | 104  | 103   |