## DAC1204/1214

PRELIMINARY INFORMATION SUBJECT TO CHANGE WITHOUT NOTICE

# QUAD Monolithic 12-Bit DIGITAL-TO-ANALOG CONVERTER (Serial Interface)

## **FEATURES**

- QUAD MONOLITHIC 12-BIT DAC

Current Output: 1mA Span

Minimal External Components Required;

One Op Amp Only

Internal Feedback Resistor (R<sub>FB</sub>) for

External I/V Amp Trimmed at Wafer Level;

DAC1204: V<sub>OUT</sub> = ±10V

DAC1214: V<sub>OUT</sub> = ±5V, 0 to 10V

Internal High Stability Voltage Reference

- HIGH SPEED SERIAL INTERFACE: 10MHz Clock

- FOUR DAC'S SIMULTANEOUS UPDATE FUNCTION: Available Individual Updating

- PROGRAMMABLE FUNCTION FOR BIPOLAR/UNIPOLAR OUTPUT SELECT

- CLEAR FUNCTION FOR RESET TO OUTPUT ZERO

- SINGLE +5V SUPPLY

- 28-PIN SOIC

## **APPLICATIONS**

- MOTOR CONTROL

- ATE PIN-ELECTRONICS LEVEL SETTING

- PROCESS CONTROL

- AUTO CALIBRATION CIRCUIT

- DSP PROCESSOR BOARD

- UPGRADE REPLACEMENT FOR MULTIPLYING DAC

### DESCRIPTION

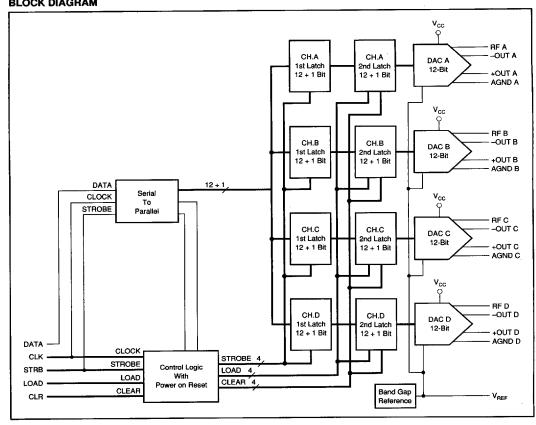

The DAC1204 and DAC1214 are serial interface, quad 12-bit current output digital-to-analog converters. These DACs consist of four separate DACs with high stability feedback resistors, a high-stability bandgap reference and a 16-bit serial-to-parallel register which is followed by four separate double-buffered registers on a single monolithic chip. The optimum performance is achieved from a combination of state-of-the art Bi CMOS process and advanced laser trimming technology.

The current output stage of the DAC1204 and DAC1214 has a pair of feedback resistors which are trimmed at wafer level. The feedback resistors of the DAC1204 are specified for ±10V output range, while the later is specified for ±5V (or 0 to 10V) output range. Thus the external I/V converter is possible with only one op amp for both bipolar and unipolar output range.

The DAC1204 and DAC1214 have a high speed serial interface capable of clocking in data at a rate of 10MHz. The serial data is a 16-bit word including channel address bits, output mode select (bipolar or unipolar mode) bits and actual DAC data. Serial data is clocked into the 16-bit shift register (MSB first) then latched into the DAC's first register. All DAC analog outputs can be simultaneously updated using asynchronous load (LOAD) signal. Also, DAC registers can be updated independently. These DACs have an asynchronous clear (CLR) control for reset to bipolar zero or unipolar zero depending on the output mode selected. This feature is useful for power-on-reset or system calibration.

All digital pins are CMOS/TTL compatible. Power supply voltage is +5VDC. The DAC1204 and DAC1214 are available in 28 pin plastic SOIC package.

International Airport Industrial Park • Mailing Address: PO Box 11400 • Tucson, AZ 85734 • Street Address: 6730 S. Tucson Blvd. • Tucson, AZ 85706

Tel: (602) 746-1111 • Twx: 910-952-1111 • Cable: BBRCORP • Telex: 066-6491 • FAX: (602) 889-1510 • Immediate Product Info: (800) 548-6132

3.134

PDS-1273

1731365 0029254 742

# Or, Call Customer Service at 1-800-548-6132 (USA Only)

## **SPECIFICATIONS**

### **ELECTRICAL**

$T_A = 25^{\circ}C$ ,  $V_{CC} \approx V_{DD} = 5.0V$ ,  $V_{REF} =$  internal or external 2.500V, with external I/V amp using internal feedback resistor and suitable op-amp unless otherwise noted.

| DADAMETER                                                                     | DAC1204U, DAC1214U |               | DAC1204UB, DAC1214UB |                                        |                 | 1    |                |

|-------------------------------------------------------------------------------|--------------------|---------------|----------------------|----------------------------------------|-----------------|------|----------------|

| PARAMETER                                                                     | MIN                | TYP           | MAX                  | MIN                                    | TYP             | MAX  | UNITS          |

| DIGITAL INPUT                                                                 |                    |               |                      |                                        |                 |      |                |

| Resolution                                                                    | 1                  | 12            |                      |                                        |                 |      | Bits           |

| Digital Input Voitage                                                         | 1                  |               |                      | 1                                      |                 |      |                |

| V <sub>IH</sub>                                                               | 2.0                |               | 5.0                  |                                        | ŀ               |      | l v            |

| V <sub>IL</sub>                                                               | 0                  |               | 0.8                  |                                        |                 |      | Ιί             |

| Digital Input Current                                                         |                    |               | İ                    |                                        |                 |      | 1              |

| $I_{iH}$ at $V_{iH} = 5V$                                                     |                    | 1             | 10                   |                                        |                 |      | μΑ             |

| I <sub>IL</sub> at V <sub>IL</sub> = 0V                                       |                    | !             | 100                  |                                        | l               | •    | μA             |

| Maximum Input Clock Frequency                                                 | 10                 |               |                      |                                        | 1               |      | MHz            |

| Input Pulse Width                                                             | i                  |               | 1                    | 1                                      | 1               |      |                |

| T <sub>WH</sub> <sup>(1)</sup>                                                | 40                 |               | 1                    | i •                                    | i               |      | ns             |

| T <sub>WL</sub> <sup>(1)</sup>                                                | 40                 |               | l                    |                                        |                 |      | ns             |

| Input Set-up Time(1)                                                          |                    | 1             | 20                   |                                        |                 | •    | ns             |

| Input Hold Time(1)                                                            |                    |               | 20                   |                                        |                 | •    | ns             |

| TRANSFER CHARACTERISTICS                                                      | 1                  | T             |                      |                                        |                 |      |                |

| DC ACCURACY                                                                   | 1                  |               | 1                    |                                        |                 |      | İ              |

| Integral Linearity Error                                                      | -1.0               |               | +1.0                 | -0.5                                   |                 | 0.5  |                |

| Differential Linearity Error                                                  | -1.0               | 1             | +1.0                 | -0.5<br>-0.5                           |                 | +0.5 | LSB            |

| Gain Error <sup>(2)</sup>                                                     | -8.0               | 1             | +8.0                 | <del>-</del> 0.5<br>  <del>-4</del> .0 |                 | +0.5 | LSB            |

| Bipolar Zero Error <sup>(2)</sup>                                             | -4.0               |               | +4.0                 | -2.0                                   |                 | +4.0 | LSB            |

| Unipolar Zero Error <sup>(2)</sup> (DAC1214 Only)                             | -2.0               | 1             | +2.0                 | -1.0                                   |                 | +2.0 | LSB            |

| Monotonicity (0 to 70°C)                                                      | "."                | Guaranteed    |                      | -1.0                                   | l<br>Guaranteed | +1.0 | LSB            |

| MISMATCH AMONG CHANNELS                                                       | -                  |               | ·                    | <u> </u>                               | - Juanamileed   |      |                |

| Integral Linearity Error                                                      | 1                  |               | 1                    |                                        |                 |      |                |

| Differential Linearity Error                                                  | 1                  | 1.0           | TBD                  |                                        | 0.5             | TBD  | LSB            |

| Gain Error <sup>(2)</sup>                                                     | 1                  | 1.0           | TBD                  |                                        | 0.5             | TBD  | LSB            |

| Bipolar Zero Error <sup>(2)</sup>                                             | 1                  | 8.0           | TBD                  |                                        | 4.0             | TBD  | LSB            |

| Unipolar Zero Error <sup>(2)</sup> (DAC1214 Only)                             | 1                  | 4.0           | TBD                  |                                        | 2.0             | TBD  | LSB            |

| ·                                                                             | L                  | 2.0           | TBD                  | 1                                      | 1.0             | TBD  | LSB            |

| DRIFT (0 to 70°C)                                                             |                    |               |                      |                                        | T               |      |                |

| Gain Drift <sup>(2)</sup> with External V <sub>REF</sub>                      | 1                  | ±10           | TBD                  | į.                                     |                 | TBD  | ppm/°C         |

| Gain Drift <sup>(2)</sup> with Internal V <sub>REF</sub>                      | 1                  | ±25           | TBD                  |                                        |                 | TBD  | ppm/°C         |

| Bipolar Zero Drift <sup>(2)</sup> with External/Internal V <sub>REF</sub>     | 1                  | ±5            | TBD                  |                                        |                 | TBD  | ppm FSR/       |

| Unipolar Zero Drift(2) with External/Internal V <sub>REF</sub> (DAC1214 Only) | 1                  | ±5            | TBD                  |                                        |                 | TBD  | ppm FSR/       |

| AC PERFORMANCE                                                                | 1                  |               |                      |                                        |                 |      | ppin r Ort     |

| Settling Time; (to 0.012% of FSR, Load to I <sub>OUT</sub> )                  | ı                  | 500           |                      |                                        | 1 .             |      | ŀ              |

| Glitch Energy(3)                                                              | i                  |               |                      |                                        | [               |      | ns             |

| Crosstalk;(3)                                                                 |                    | 20            |                      |                                        | '               |      | nV-s           |

| Digital-to-Analog                                                             |                    | 20            |                      |                                        |                 |      |                |

| Channel-to-Channel                                                            |                    | -78           |                      |                                        | ;               |      | nV-s           |

| REFERENCE                                                                     | +                  | -/8           |                      |                                        |                 |      | dB             |

|                                                                               | 1                  |               |                      |                                        |                 |      |                |

| External Reference Voltage Range                                              | 2.45               | 2.50          | 2.55                 | ٠                                      |                 | •    | V              |

| External Reference Current Drain at V <sub>REF</sub> = 2.500V                 | l .                | ±10           | ±50                  |                                        | ٠ ا             | •    | μА             |

| ANALOG OUTPUT                                                                 |                    |               |                      |                                        |                 |      |                |

| /oltage Output Configuration                                                  |                    |               |                      |                                        |                 |      | 1              |

| Bipolar Range                                                                 |                    |               |                      |                                        |                 |      | 1              |

| DAC1204                                                                       |                    | ±10           |                      |                                        |                 |      | l v            |

| DAC1214                                                                       |                    | ±10           |                      |                                        |                 |      |                |

| Unipolar Range                                                                | 1                  | -             |                      |                                        |                 |      | V              |

| DAC1214                                                                       | 1                  | 0 to +10      |                      |                                        |                 |      | .,             |

| Dutput Impedance at Output to Ground                                          | 1                  | 1.0           |                      |                                        |                 |      | V V            |

| Short Circuit Duration                                                        | Inde               | finite to Gro | nund                 |                                        |                 |      | kΩ             |

| POWER SUPPLY REQUIREMENTS                                                     | +                  |               |                      |                                        |                 |      |                |

| · · · · · · · · · · · · · · · · · · ·                                         |                    |               |                      |                                        |                 |      | l              |

| Supply Voltage                                                                | 1                  |               |                      | l                                      |                 |      | 1              |

| V <sub>CC</sub> , V <sub>DD</sub>                                             | 4.75               | 5.00          | 5.25                 |                                        |                 |      | v              |

| Supply Current (No Load)                                                      | 1                  |               | 5.25                 |                                        |                 | į    | l <sup>v</sup> |

| $I_{CC} + I_{DD} (V_{CC} = V_{DD} = 5.0V)$                                    | I                  | 20            | TBD                  |                                        |                 |      |                |

| Power Dissipation                                                             |                    | 100           | TBD                  |                                        |                 |      | mA<br>m\Al     |

| Power Supply Rejection Ratio <sup>(2)</sup>                                   |                    | ±0.001        | 100                  |                                        |                 |      | mW             |

| EMPERATURE RANGE                                                              | <b>├</b> ──        | 10.001        |                      |                                        |                 |      | % of FSR/%     |

| Specification                                                                 | ] .                |               |                      |                                        |                 |      |                |

| Specification<br>Operating                                                    | 0                  |               | 70                   | •                                      |                 | •    | °C             |

| Storage                                                                       | -40                | j             | +85                  |                                        |                 | •    | °C             |

| No. 1290                                                                      | -55                | 1             | +125                 | •                                      | [               |      | °C             |

NOTES: (1) See serial interface timing for details. (2) Offset, linearity and CMRR of external Op-Amp influence each performance. (3) Specified condition (Clock/Signal frequency. Op-Amp, Band-Width, etc.) should be determined.

1731365 0029255 689 🖿

Burr-Brown IC Data Book—Data Conversion Products

3.135

## For Immediate Assistance, Contact Your Local Salesperson

#### **BLOCK DIAGRAM**

1731365 0029256 515

## Or, Call Customer Service at 1-800-548-6132 (USA Only)

### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>DD</sub> to DGND           | 0 to +6V                       |

|-----------------------------------|--------------------------------|

| V <sub>CC</sub> to AGND           |                                |

| AGND to DGND                      |                                |

| Digital Input to DGND             | 0.3V to +V <sub>DD</sub> +0.3V |

| External Voltage applied to;      |                                |

| Internal Feed-back Resistor       | ±25V                           |

| V <sub>REF IN</sub>               | 0.3V to V <sub>CC</sub> +0.3V  |

| -Out/+Out                         | 0.3V to V <sub>CC</sub> +0.3V  |

| Lead Temperature; (soldering, 5s) |                                |

|                                   | +235°C                         |

| Max Junction Temperature          | +125°C                         |

NOTE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. Exposure to absolute maximum conditions for extended periods may affect device reliability.

### ORDERING INFORMATION

| MODEL                             | OUTPUT RANGE                  | LINEARITY ERR             | PACKAGE                                   |

|-----------------------------------|-------------------------------|---------------------------|-------------------------------------------|

| DAC1204U<br>DAC1204UB<br>DAC1214U | ±10V<br>±10V<br>±5V, 0 to 10V | ±1LSB<br>±0.5LSB<br>±1LSB | 28-Pin SOIC<br>28-Pin SOIC<br>28-Pin SOIC |

| DAC1214UB                         | ±5V, 0 to 10V                 | ±0.5LSB                   | 28-Pin SOIC                               |

## PACKAGE INFORMATION®

| MODEL        | PACKAGE     | PACKAGE DRAWING<br>NUMBER |

|--------------|-------------|---------------------------|

| DAC1204U, UB | 28-Pin SOIC | 809                       |

| DAC1204UB    | 28-Pin SOIC | 809                       |

| DAC1214U     | 28-Pin SOIC | 809                       |

| DAC1214UB    | 28-Pin SOIC | 809                       |

NOTE: (1) For detailed drawing and dimension table, please see end of data sheet, or Appendix D of Burr-Brown IC Data Book.

## PIN CONNECTIONS

| Top View | SOIC                |

|----------|---------------------|

|          |                     |

| -OUTA 1  | 28 –OUTD            |

| +OUTA 2  | 27 +OUTD            |

| AGNDA 3  | 26 AGNDD            |

| RFA 4    | 25 RFD              |

| STRB 5   | 24 AGND             |

| DATA 6   | 23 AGND             |

| CLK 7    | 22 V <sub>CC</sub>  |

| LOAD 8   | 21 V <sub>CC</sub>  |

| CLR 9    | 20 V <sub>REF</sub> |

| RFB 10   | 19 RFC              |

| AGNDB 11 | 18 AGNDC            |

| +OUTB 12 | 17 +OUTC            |

| -OUТВ 13 | 16 -OUTC            |

| DGND 14  | 15 V <sub>DD</sub>  |

#### PIN DESCRIPTIONS

| PIN | NAME             | FUNCTION                                                           |  |  |  |

|-----|------------------|--------------------------------------------------------------------|--|--|--|

| 1   | -OUTA            | DAC A Current Output.                                              |  |  |  |

| 2   | +OUTA            | DAC A Common Current Output.                                       |  |  |  |

| 3   | AGNDA            | DAC A Analog Ground.                                               |  |  |  |

| 4   | RFA              | DAC A Feed-back Resistor.                                          |  |  |  |

| 5   | STRB             | 1st Latch Register Update. Data is latched in on negative edge.    |  |  |  |

| 6   | DATA             | Serial Data Input. Data is clocked in on positive edge of the CLK. |  |  |  |

| 7   | CLK              | Serial Clock Input.                                                |  |  |  |

| 8   | LOAD             | Load DAC Input (active low) - 2nd Latch Register Update.           |  |  |  |

| 9   | CLR              | Reset to DAC Output zero (active low).                             |  |  |  |

| 10  | RFB              | DAC B Feed-back Resistor.                                          |  |  |  |

| 11  | AGNDB            | DAC B Analog Ground.                                               |  |  |  |

| 12  | +OUTB            | DAC B Common Current Output.                                       |  |  |  |

| 13  | -OUTB            | DAC B Current Output.                                              |  |  |  |

| 14  | DGND             | Digital Ground.                                                    |  |  |  |

| 15  | V <sub>DD</sub>  | Digital Power Supply, +5V typ.                                     |  |  |  |

| 16  | -outc            | DAC C Current Output.                                              |  |  |  |

| 17  | +OUTC            | DAC C Common Current Output.                                       |  |  |  |

| 18  | AGNDC            | DAC C Analog Ground.                                               |  |  |  |

| 19  | RFC              | DAC C Feed-back Resistor.                                          |  |  |  |

| 20  | V <sub>REF</sub> | Reference Voltage Input.                                           |  |  |  |

| 21  | V <sub>cc</sub>  | Analog Power Supply, +5V typ.                                      |  |  |  |

| 22  | V <sub>cc</sub>  | Analog Power Supply, +5V typ.                                      |  |  |  |

| 23  | AGND             | Analog Power Ground.                                               |  |  |  |

| 24  | AGND             | Analog Power Ground.                                               |  |  |  |

| 25  | RFD              | DAC D Feed-back Resistor.                                          |  |  |  |

| 26  | AGNDD            | DAC D Analog Ground.                                               |  |  |  |

| 27  | +OUTD            | DAC D Common Current Output.                                       |  |  |  |

| 28  | -OUTD            | DAC D Current Output.                                              |  |  |  |

The information provided herein is believed to be reliable; however, BURR-BROWN assumes no responsibility for inaccuracies or omissions. BURR-BROWN assumes no responsibility for the use of this information, and all use of such information shall be entirely at the user's own risk. Prices and specifications are subject to change without notice. No patent rights or licenses to any of the circuits described herein are implied or granted to any third party. BURR-BROWN does not authorize or warrant any BURR-BROWN product for use in life support devices and/or systems.

**■** 1731365 0029257 451 **■**

Burr-Brown IC Data Book—Data Conversion Products

## For Immediate Assistance, Contact Your Local Salesperson

## DIGITAL INPUTS DESCRIPTION

#### **INPUT CODES**

All digital inputs are TTL and CMOS compatible. For bipolar output range, input codes for the DAC1204 and DAC1214 are Binary Two's Compliment (BTC) code. For unipolar output range, input codes are Unipolar Straight Binary (USB) code. The input/output relationship is shown in Table Ia and Ib.

| DIGITAL INPUT CODE (BTC) | ANALOG OUTPUT (BIPOLAR) |

|--------------------------|-------------------------|

| 7FF <sub>HEX</sub>       | +FS                     |

| 000 <sub>HEX</sub>       | BPZ                     |

| FFF <sub>HEX</sub>       | BPZ -1LSB               |

| 800 <sub>HEX</sub>       | _FS                     |

TABLE Ia. Digital Input/Bipolar Output Relationships.

| DIGITAL INPUT CODE (USB) | ANALOG OUTPUT (UNIPOLAR) |  |  |

|--------------------------|--------------------------|--|--|

| FFF <sub>HEX</sub>       | FS                       |  |  |

| 800 <sub>HEX</sub>       | FS/2                     |  |  |

| 7FF <sub>HEX</sub>       | FS/2 -1LSB               |  |  |

| 000 <sub>HEX</sub>       | ZERO                     |  |  |

TABLE Ib.Digital Input/Unipolar Output Relationships.

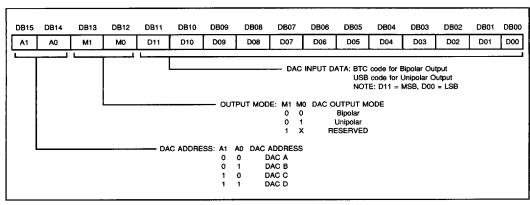

#### **SERIAL INPUT DATA FORMAT**

Serial data is a 16-bit word per channel and is clocked in on the raising edge of clock (CLK) into the internal 16-bit shift register with MSB first format. Figure 1 shows the serial data input format. The 16-bit serial input format comprises two DAC address bits (A1, A0), two output mode select bits (M1, M0) and twelve bits of DAC data (D11...D00). A1 and A0 shown in Table IIa set the DAC address, and M1 and M0 shown in Table IIb select the output range of bipolar or unipolar.

| A1 | A0 | SELECTED DAC |

|----|----|--------------|

| 0  | 0  | DAC A        |

| 0  | 1  | DAC B        |

| 1  | 0  | DAC C        |

| 1  | 1  | DAC D        |

TABLE IIa. DAC Address.

| M1              | Mo                   | DAC OUTPUT MODE .          |

|-----------------|----------------------|----------------------------|

| 0               | 0                    | Bipolar Output             |

| 0               | 1                    | Unipolar Output            |

| 1               | X                    | Reserved                   |

| NOTES: 0 = logi | cal "Low", 1 = logic | al "High", X = Don't Care. |

TABLE IIb. DAC Output Mode Select.

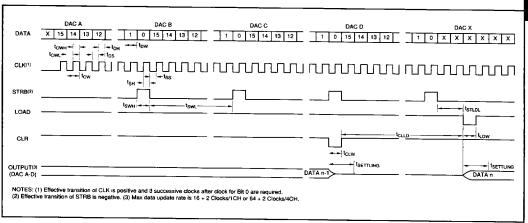

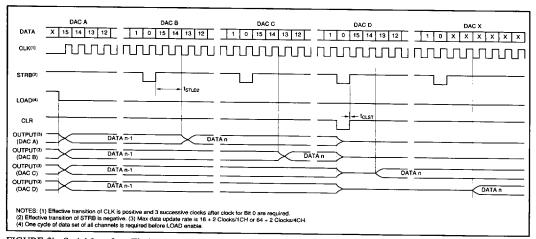

#### **DIGITAL INTERFACE TIMING**

Interface logic signals of the DAC1204 and DAC1214 consist of the serial data clock (CLK), serial data (DATA), strobe (STRB), load (LOAD) and clear (CLR) controls. Figure 2 shows a typical interface timing diagram. The serial data is clocked in on positive edge of CLK into the shift register until all 16 bits of data are entered and then is transferred into the addressed DAC first latch register from the shift register on negative edge of STRB. The DAC data is allowed to stay in each first register until each first latch register is updated by next STRB signal. Also the STRB signal and DAC address bits (A0, A1) on serial data frame with LOAD signal allow DAC update; independently or simultaneously. The STRB signal must be "High" for at least one clock cycle before going "Low" and must be held "Low" for at least one cycle after the signal is changed from "High" to "Low" as shown in Figure 2.

FIGURE 1. Serial Input Data Format.

**1731365 0029258 398**

BBB

## Or, Call Customer Service at 1-800-548-6132 (USA Only)

LOAD signal is asynchronous with respect to DATA, CLK and STRB signals and can simultaneously update all four DAC second latch registers. When LOAD signal is changed "High" to "Low", the data on all first latch registers are loaded into corresponding second latch registers and DAC's outputs are updated simultaneously. This mode is a Latch Mode. In this case, if the LOAD signal become "Low" within two clocks from the negative edge of STRB signal, the previous data of first latch register is loaded into the second latch register. If LOAD signal is fixed "Low", the data on the first latch register addressed by A1, A0 is loaded into corresponding second latch register on second negative edge of CLK after STRB goes "Low", and in this case, DAC's output can be updated independently. This is a Transparent Mode.

CLR signal, also, is asynchronous with respect to DATA, CLK, STRB signals and can simultaneously reset to bipolar zero or unipolar zero depending on the output mode selected  $(M_0,\,M_1)$  when the CLR is "Low".

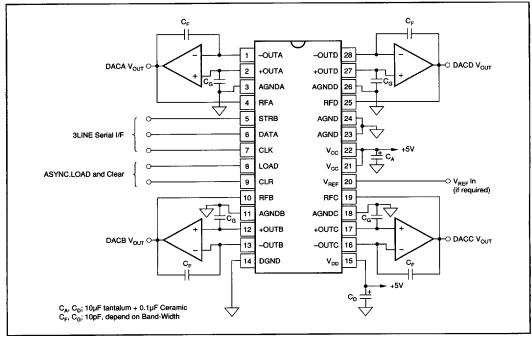

#### CIRCUIT CONNECTION

Figure 3 shows a typical connection diagram for the DAC1204 and DAC1214. The output stage of the DAC1204 and DAC1214 is current output mode.

For optimum performance and noise rejection, the DACs and I/V op amp should be located close to each other and power supply decoupling capacitors should be located close to the DACs.

FIGURE 2a. Serial Interface Timing Diagram (Latch Mode).

FIGURE 2b. Serial Interface Timing Diagram (Transparent Mode).

**■ 1731365 0029259 224 ■**

Burr-Brown IC Data Book—Data Conversion Products

3.139

## For Immediate Assistance, Contact Your Local Salesperson

### **TIMING SPECIFICATION**

| SYMBOL             | DESCRIPTION                                                  | MIN | TYP | MAX | UNITS |

|--------------------|--------------------------------------------------------------|-----|-----|-----|-------|

| t <sub>cw</sub>    | CLOCK (CLK) width                                            | 100 |     |     | ns    |

| t <sub>CWL</sub>   | CLOCK (CLK) low width                                        | 40  | 1   |     | ns    |

| town               | CLOCK (CLK) high width                                       | 40  |     | i   | ns    |

| t <sub>swL</sub>   | STROBE (STRB) low width                                      | 1   |     | l   | CLOCK |

| tswn               | STROBE (STRB) high width                                     | 1   |     | l . | CLOCK |

| t <sub>DW</sub>    | DATA (DATA) width                                            | 100 | l . | 1   | ns    |

| tLDW               | LOAD (LOAD) low width                                        | 40  | 1   |     | ns    |

| tclw               | CLEAR (CLR) low width                                        | 40  | 1   |     | ns    |

| tos                | DATA (DATA) to CLOCK (CLK) set-up time                       | 20  | 1   |     | пѕ    |

| t <sub>DH</sub>    | DATA (DATA) to CLOCK (CLK) hold time                         | 20  |     |     | ns    |

| tss                | STROBE (STRB) to CLOCK (CLK) set-up time                     | 20  |     | į.  | ns    |

| t <sub>SH</sub>    | STROBE (STRB) to CLOCK (CLK) hold time                       | 20  | ŀ   | i   | ns    |

| t <sub>STLD1</sub> | STROBE (STRB) to LOAD (LOAD) delay time for latch mode       | 2.5 | i   | ŀ   | CLOCK |

| t <sub>STLD2</sub> | STROBE (STRB) to LOAD (LOAD) delay time for transparent mode |     |     | 2.5 | CLOCK |

| t <sub>CLLD</sub>  | CLEAR (CLR) to LOAD (LOAD) delay time                        | 100 | 1   |     | ns    |

| tolst              | CLEAR (CLR) to STROBE (STRB) delay time                      | 0   |     | ļ   | ns    |

FIGURE 3. Typical I/V Amp Connection.

1731365 0029260 T46 **-**