# M5L8255AP-5

T-51-19

PROGRAMMABLE PERIPHERAL INTERFACE

### DESCRIPTION

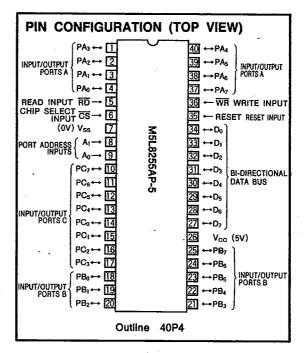

The M5L8255AP-5 is a family of general-purpose programmable input/ output devices designed for use with an 8-bit/16-bit parallel CPU as input/output ports, Device is fabricated using N-channel silicon-gate ED-MOS technology for a single supply voltage. They are simple input and output interfaces for TTL circuits, having 24 input/output pins which correspond to three 8-bit input/output ports.

### **FEATURES**

- Single 5V supply voltage

- TTL compatible.

- Darlington drive capability

- 24 programmable I/O pins

- Direct bit set/reset capability

### **APPLICATION**

Input/output ports for microprocessor

#### **FUNCTION**

These PPIs have 24 input/output pins which may be individually programmed in two 12-bit groups A and B with mode control commands from a CPU. They are used in three major modes of operation, mode 0, mode 1 and mode 2. Operating in mode 0, each group of 12 pins may be programmed in sets of 4 to be inputs or outputs. In mode 1, the 24 I/O terminals may be programmed in two 12-bit groups, group A and group B. Each group contains one 8-bit data port, which may be programmed to serve as input or output, and one 4-bit control port used for handshaking and interrupt control signals. Mode 2 is used with group A only, as one 8-

bit bidirectional bus port and one 5-bit control port. Bit set/ reset is controlled by CPU. A high-level reset input (RESET) clears the control register, and all ports are set to the input mode (high-impedance state).

# MITSUBISHI (MICMPTR/MIPRC)

### PROGRAMMABLE PERIPHERAL INTERFACE

# T-52-33-05

### **FUNCTIONAL DESCRIPTION**

#### RD (Read) Input

At low-level, the status or the data at the port is transferred to the CPU from the PPI. In essence, it allows the CPU to read data from the PPI.

#### WR (Write) Input

At low-level, the data or control words are transferred from the CPU and written in the PPI.

#### An At (Port address) Input

These input signals are used to select one of the three ports: port A, port B, and port C, or the control register. They are normally connected to the least significant 2 bits of the address bus.

### RESET (Reset) Input

At high-level, the control register is cleared. Then all ports are set to the input mode (high-impedance state).

#### CS (Chip-Select) Input

At low-level, the communication between the PPI and the CPU is enabled. While at high-level, the data bus is kept in the high-impedance state, so that commands from the CPU are ignored. Then the previous data is kept at the output port.

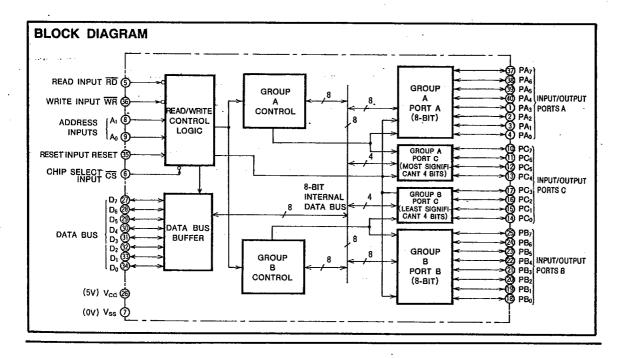

### Read/Write Control Logic

The function of this block is to control transfers of both data and control words. It accepts the address signals ( $A_0$ ,  $A_1$ ,  $\overline{CS}$ ), I/O control signals ( $\overline{RD}$ ,  $\overline{WR}$ ) and RESET signal, and then issues commands to both of the control groups in the PPI.

#### Data Bus Buffer

This three-state, bidirectional, 8-bit buffer is used to transfer the data when an input or output instruction is executed by the CPU. Control words and status information are also transferred through the data bus buffer.

#### Group A and Group B Control

Accepting commands from the read/write control logic, the control blocks (Group A, Group B) receive 8-bit control words from the internal data bus and issue the proper commands for the associated ports. Control group A is associated with port A and the 4 high-order bits of port C. Control group B is associated with port B and the 4 low-order bits of port C. The control register, which stores control words, can only be written into.

### Port A, Port B and Port C

The PPI contains three 8-bit ports whose modes and input/ output settings are programmed by the system software.

Port A has an output latch/buffer and an input latch/buffer. Port B has an input-output latch/buffer. Port C has an output latch/buffer and an input buffer. Port C can be divided into two 4-bit ports which can be used as ports for control signals for port A and port B.

The basic operations are shown in Table 1.

### Table 1 Basic Operations

| Aı | Αo  | cs | RD | WR | Operation                           |

|----|-----|----|----|----|-------------------------------------|

| 0  | 0   | L  | L  | Н  | Data bus ← Port A                   |

| 0  | 1   | L  | L  | Н  | Data bus Port B                     |

| 1  | 0   | L  | L  | н  | Data bus ← Port C                   |

| 0  | 0   | L  | н  | L  | Port A ← Data bus                   |

| 0  | . 1 | L  | Н  | L  | Port B ← Data bus                   |

| 1  | 0   | L  | Н  | L  | Port C ← Data bus                   |

| 1  | 1   | L  | Н  | L  | Control register ← Data bus         |

| х  | ×   | Н  | X  | х  | Data bus is in high-impedance state |

| 1  | 1   | L  | L  | Н  | Illegal condition                   |

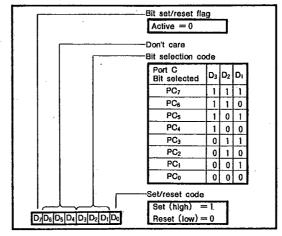

#### Bit Set/Reset

When port C is used as an output port, any 1 bit of the 8 bits can be set (high) or reset (low) by a control word from the CPU. This bit set/reset can be operated in the same way as the mode set, but the control word format is different. This operation is also used for INTE (interrupt enable flag) set/reset in mode 1 and mode 2.

different. This operation is also used for INTE set/reset in mode 1 and mode 2 .

Fig. 1. Control word format for port C set/reset

(group A only)

# M5L8255AP-5

T-52-33-05

# MITSUBISHI (MICMPTR/MIPRC)

# PROGRAMMABLE PERIPHERAL INTERFACE

### **BASIC OPERATING MODES**

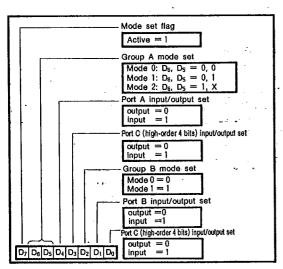

The PPI can operate in any one of three selected basic modes.

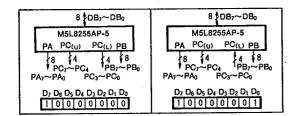

Mode 0: Basic input/output (group A, group B)

Mode 1: Strobed input/output (group A, group B)

Mode 2: Bidirectional bus

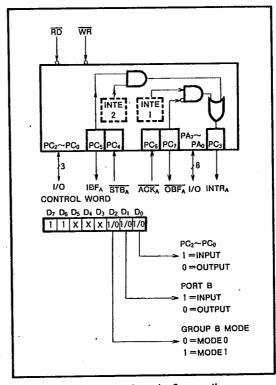

The mode of both group A and group B can be selected independently. The control word format for mode set is shown in Fig. 2.

Fig. 2 Control word format for mode set.

# 1. Mode 0 (Basic Input/Output)

This functional configuration provides simple input and output operations for each of the 3 ports. No "handshaking" is required; data is simply written in, or read from, the specified port. Output data from the CPU to the port can be held, but input data from the port to the CPU cannot be held. Any one of the 8-bit ports and 4-bit ports can be used as an input port or an output port. The diagrams following show the basic input/output operating modes.

| 8 ∤DB₁~DB₀                                                                                                                                 | 8 ∤DB <sub>7</sub> ~DB <sub>0</sub>                                                                                                        |

|--------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| M5L8255AP-5 PA PC(u) PC(L) PB                                                                                                              | M5L8255AP-5<br>PA PC(u) PC(L) PB                                                                                                           |

| 8 44 4 8<br>PC7~PC4 PB7~PB0<br>PA7~PA0 PC3~PC0                                                                                             | 8 4 4 8<br>PC7~PC4 PB7~PB0<br>PA7~PA0 PC3~PC0                                                                                              |

| D <sub>7</sub> D <sub>6</sub> D <sub>5</sub> D <sub>4</sub> D <sub>3</sub> D <sub>2</sub> D <sub>1</sub> D <sub>0</sub> 1 0 0 0 0 1 0      | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                      |

| 8 ∤DB7~DB0                                                                                                                                 | 8 ≵DB <sub>7</sub> ~DB <sub>0</sub>                                                                                                        |

| M5L8255AP-5<br>PA PC(u) PC(L) PB                                                                                                           | M5L8255AP-5 PA PC(u) PC(L) PB :                                                                                                            |

| 8                                                                                                                                          | 8 4 4 8<br>PC,~PC4 PB,~PB0<br>PA,~PA0 PC3~PC0                                                                                              |

| D <sub>7</sub> D <sub>6</sub> D <sub>5</sub> D <sub>4</sub> D <sub>3</sub> D <sub>2</sub> D <sub>1</sub> D <sub>0</sub> 1 0 0 0 1 0 0 0    | D <sub>7</sub> D <sub>6</sub> D <sub>5</sub> D <sub>4</sub> D <sub>3</sub> D <sub>2</sub> D <sub>1</sub> D <sub>0</sub> 1 0 0 0 1 0 0 1    |

| 8 ∤DB <sub>7</sub> ~DB <sub>0</sub>                                                                                                        | 8 ∤DB <sub>7</sub> ~DB <sub>0</sub>                                                                                                        |

| M5L8255AP-5 PA PC(u) PC(L) PB                                                                                                              | M6L8255AP-5 PA PC(u) PC(L) PB                                                                                                              |

| 8 4 4 8 PC <sub>3</sub> ~PC <sub>4</sub> PB <sub>7</sub> ~PB <sub>7</sub> PA <sub>9</sub> PC <sub>3</sub> ~PC <sub>0</sub>                 | 8 14 14 18<br>PC7~PC4 PB7~PB0<br>PA7~PA0. PC3~PC0                                                                                          |

| D <sub>7</sub> D <sub>6</sub> D <sub>5</sub> D <sub>4</sub> D <sub>3</sub> D <sub>2</sub> D <sub>1</sub> D <sub>0</sub><br>1 0 0 0 1 0 1 0 | D <sub>7</sub> D <sub>6</sub> D <sub>5</sub> D <sub>4</sub> D <sub>3</sub> D <sub>2</sub> D <sub>1</sub> D <sub>0</sub> 1 0 0 0 1 0 1 1    |

| 8 ≯DB₁~DB₀                                                                                                                                 | 8 ∤ DB <sub>7</sub> ~ DB <sub>0</sub>                                                                                                      |

| M5L8255AP-5 PA PC(u) PC(L) PB                                                                                                              | M5L8255AP-5 PA PC(u) PC(L) PB                                                                                                              |

| 8 4 4 8<br>PC7~PC4 PB7~PB0<br>PA7~PA0 PC3~PC0                                                                                              | 8 4 4 8<br>PC7~PC4 PB7~PB0<br>PA7~PA0 PC3~PC0                                                                                              |

| D <sub>7</sub> D <sub>6</sub> D <sub>5</sub> D <sub>4</sub> D <sub>3</sub> D <sub>2</sub> D <sub>1</sub> D <sub>0</sub> 1 0 0 1 0 0 0 0    | D <sub>7</sub> D <sub>6</sub> D <sub>5</sub> D <sub>4</sub> D <sub>3</sub> D <sub>2</sub> D <sub>1</sub> D <sub>0</sub> 1 0 0 1 0 0 0 1    |

| 8 ‡DB₁~DB₀                                                                                                                                 | 8 ≯DB₁~DB₀                                                                                                                                 |

| M5L8255AP-5 PA PC(u) PC(L) PB                                                                                                              | M5L8255AP-5 PA PC(u) PC(L) PB                                                                                                              |

| 8 4 4 8<br>PC7~PC4 PB7~PB0<br>PA7~PA0 PC3~PC0                                                                                              | 18 4 4 8<br>PC7~PC4 PB7~PB0<br>PA7~PA0 PC3~PC0                                                                                             |

| D <sub>7</sub> D <sub>6</sub> D <sub>5</sub> D <sub>4</sub> D <sub>3</sub> D <sub>2</sub> D <sub>1</sub> D <sub>0</sub> 1 0 0 1 0 0 1 0    | D <sub>7</sub> D <sub>6</sub> D <sub>5</sub> D <sub>4</sub> D <sub>3</sub> D <sub>2</sub> D <sub>1</sub> D <sub>0</sub><br>1 0 0 1 0 0 1 1 |

| 8 ‡D8₁~DBc                                                                                                                                 | 8 ≯DB₁~DB₀                                                                                                                                 |

| M5L8255AP-5<br>PA PC <sub>IU</sub> PC <sub>IL</sub> PB                                                                                     | M5L8255AP-5 PA PC(u) PC(L) PB                                                                                                              |

| 8 4 4 8<br>PC7~PC4 PB7~PB0<br>PA7~PA0 PC3~PC0                                                                                              | 8 4 4 8<br>PC7~PC4 PB7~PB0<br>PA7~PA0 PC3~PC0                                                                                              |

| D <sub>7</sub> D <sub>6</sub> D <sub>5</sub> D <sub>4</sub> D <sub>3</sub> D <sub>2</sub> D <sub>1</sub> D <sub>0</sub>                    | D <sub>7</sub> D <sub>6</sub> D <sub>5</sub> D <sub>4</sub> D <sub>3</sub> D <sub>2</sub> D <sub>1</sub> D <sub>0</sub>                    |

| 8 DB <sub>7</sub> ~DB <sub>0</sub>                                                                                                         | 8 ≯DB <sub>7</sub> ~DB <sub>0</sub>                                                                                                        |

| M5L8255AP-5                                                                                                                                | M5L8255AP-5                                                                                                                                |

| PA PC(u) PC(L) PB                                                                                                                          | PA PC(L) PC(L) PB                                                                                                                          |

| 1 PC7~PC4 PB7~PB0<br>PA7~PA0 PC3~PC0                                                                                                       | \$ \$4 \$4 \$8<br>PC7~PC4 PB7~PB0<br>PA7~PA0 PC3~PC0                                                                                       |

| D <sub>7</sub> D <sub>6</sub> D <sub>5</sub> D <sub>4</sub> D <sub>3</sub> D <sub>2</sub> D <sub>1</sub> D <sub>0</sub> 1 0 0 1 1 0 1 0    | D <sub>7</sub> D <sub>6</sub> D <sub>5</sub> D <sub>4</sub> D <sub>3</sub> D <sub>2</sub> D <sub>1</sub> D <sub>0</sub> 1 0 0 1 1 0 1 1    |

MITSUBISHI(MICMPTR/MIPRC)

T-52-33-05

#### PROGRAMMABLE PERIPHERAL INTERFACE

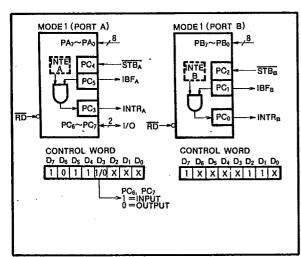

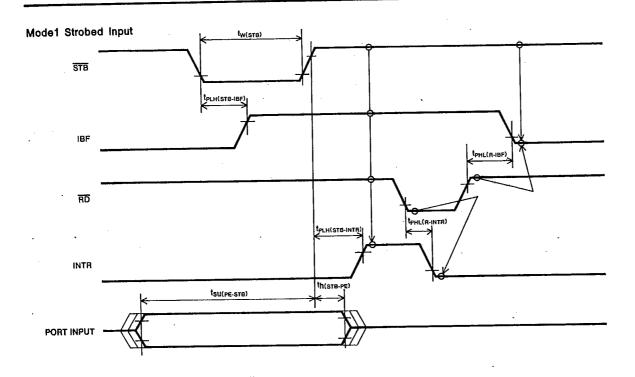

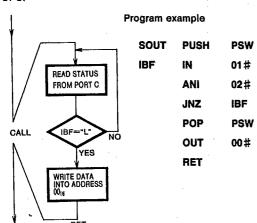

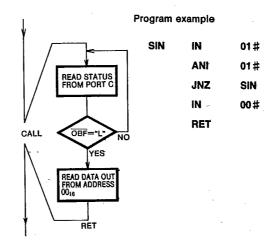

# 2. Mode 1 (Strobed Input/Output)

This function can be set in both group A and B. Both groups are composed of one 8-bit data port and one 4-bit control data port. The 8-bit port can be used as an input port or an output port. The 4-bit port is used for control and status signals affecting the 8-bit data port. The following shows operations in mode 1 for using input ports.

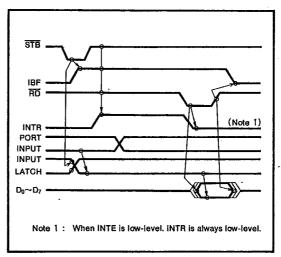

### STB (Strobe Input)

A low-level on this input latches the output data from the terminal units into the input register of the port. In short, this is a clock for data latching. The data from the terminal units can be latched by the PPI independent of the control signal from the CPU. This data is not sent to the data bus until the instruction IN is executed.

### IBF (Input Buffer Full Flag Output)

A high-level on this output indicates that the data from the terminal units has been latched into the input register. IBF is set to high-level by the falling edge of the  $\overline{\text{STB}}$  input, and is reset to low-level by the rising edge of the  $\overline{\text{RD}}$  input.

#### **INTR** (Interrupt Request Output)

This can be used to interrupt the CPU when an input device is requesting service. When INTE (interrupt enable flag) of the PPI is high-level, INTR is set to high-level by the rising edge of the  $\overline{\text{STB}}$  input and is reset to low-level by the falling edge of  $\overline{\text{RD}}$  input.

INTE<sub>A</sub> of group A is controlled by bit setting of PC<sub>4</sub>. INTE<sub>B</sub> of group B is controlled by bit setting of PC<sub>2</sub>.

Mode 1 Input state is shown in Fig. 3, and the timing diagram is shown in Fig. 4.

Fig. 3 An example of mode 1 input state

Fig. 4 Timing diagram

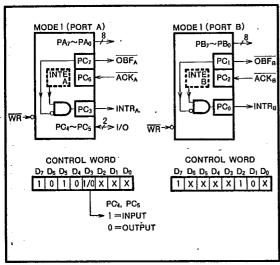

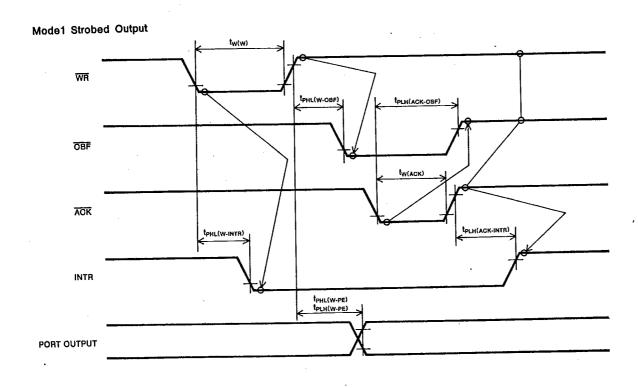

The following shows operations using mode 1 for output ports.

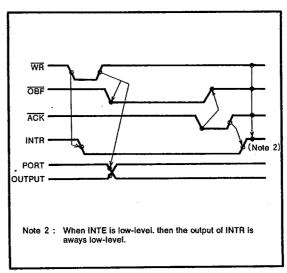

#### OBF (Output Buffer Full Flag Output)

This is reset to low-level by the rising edge of the  $\overline{\text{WR}}$  signal and is set to high-level by the falling edge of the  $\overline{\text{ACK}}$  (acknowledge input). In essence, the PPI indicates to the terminal units by the  $\overline{\text{OBF}}$  signal that the CPU has sent data to the port.

#### **ACK** (Acknowledge Input)

Receiving this signal from a terminal unit can indicate to the PPI that the terminal unit has accepted data from a port.

### **INTR** (Interrupt Request)

When a peripheral unit is accepting data from the CPU, seting INTR to high-level can be used to interrupt the CPU. When INTE (interrupt enable flag) is high-level and  $\overrightarrow{OBF}$  is set to high-level by the rising edge of an  $\overrightarrow{ACK}$  signal, then INTR will also be set to high-level by the rising edge of the  $\overrightarrow{ACK}$  signal. Also, INTR is reset to low-level by the falling edge of the  $\overrightarrow{WR}$  signal when the PPI has been receiving data from the CPU.

INTE<sub>A</sub> of group A is controlled by bit setting of  $PC_6$ . INTE<sub>B</sub> of group B is controlled by bit setting of  $PC_2$ .

Mode 1 output state is shown in Fig. 5, and the timing diagram is shown in Fig. 6.

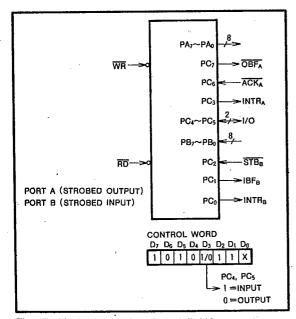

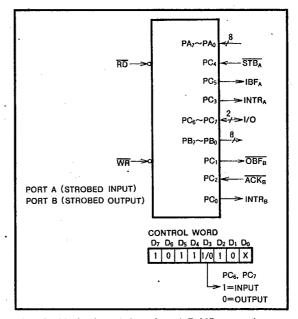

Combinations for using port A and port B as input or output in mode 1 are shown in Fig. 7 and Fig. 8.

# MITSUBISHI(MICMPTR/MIPRC)

T-52-33-05

### PROGRAMMABLE PERIPHERAL INTERFACE

Fig. 5 An example of mode 1 output state

Fig. 6 Timing diagram

Fig. 7 Mode 1 port A and port B I/O example

Fig. 8 Mode 1 port A and port B I/O example

# MITSUBISHI (MICMPTR/MIPRC)

T-52-33-05

### PROGRAMMABLE PERIPHERAL INTERFACE

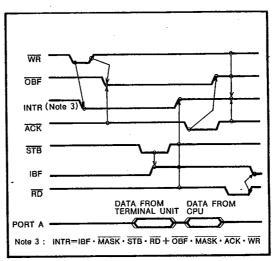

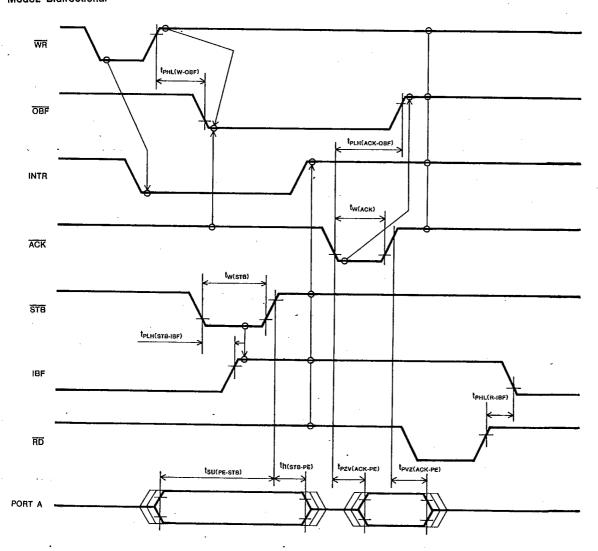

3. Mode 2 (Strobed Bidirectional Bus Input/ Output)

Mode 2 can provide bidirectional operations, using one 8-bit bus for communicating with terminal units. Mode 2 is only valid with group A and uses one 8-bit bidirectional bus port (port A) and a 5-bit control port (high-order 5 bits of port C). The bus port (port A) has two internal registers, one for input and the other for output. On the other hand, the control port (port C) is used for communicating control signals and bus-status signals. These control signals are similar to mode 1 and can also be used to control interruption of the CPU. When group A is programmed as mode 2, group B can be programmed independently as mode 0 or mode 1. When group A is in mode 2, the following 5 control signals can be used.

### **OBF** (Output Buffer Full Flag Output)

The OBF output will go low-level to indicate that the CPU has sent data to the internal register of port A. This signal lets the terminal units know that the data is ready for transfer from the CPU. When this occurs, port A remains in the floating (high-impedance) state.

### **ACK** (Acknowledge Input)

A low-level ACK input will cause the data of the internal register to be transferred to port A. For a high-level ACK input, the output buffer will be in the floating (high-impedance) state.

### STB (Strobe Input)

When the STB input is low-level, the data from terminal units will be held in the internal register, and the data will be sent to the system data bus with an RD signal to the PPI.

### IBF (Input Buffer Full Flag Output)

When data from terminal units is held on the internal register, IBF will be high-level.

# INTR (Interrupt Request Output)

This output is used to interrupt the CPU and its operations the same as in mode 1. There are two interrupt enable flags that correspond to INTE<sub>A</sub> for mode 1 output and mode 1 input.

INTE<sub>1</sub> is used in generating INTR signals in combination with OBF and ACK. INTE<sub>1</sub> is controlled by bit setting of PC<sub>6</sub>.

INTE $_2$  is used in generating INTR signals in combination with  $\overline{\text{IBF}}$  and  $\overline{\text{STB}}$ . INTE $_2$  is controlled by bit setting of PC $_4$ .

Fig. 9 shows the timing diagram of mode 2, and Fig. 10 is an example of mode 2 operation.

Fig. 9 Mode 2 timing diagram

Fig. 10 An example of mode 2 operation

# M5L8255AP-5

T-52-33-05

### PROGRAMMABLE PERIPHERAL INTERFACE

### 4. Control Signal Read

In mode 1 or mode 2 when using port C as a control port, by CPU execution of an IN instruction, each control signal and bus status from port C can be read.

### 5. Control Word Tables

Control word formats and operation details for mode 0, mode 1, mode 2 and set/reset control of port C are given in Tables 3, 4, 5 and 6, respectively.

Table 2 Read-out control signals

| Data<br>Mode   | D <sub>7</sub> | D <sub>6</sub>    | D <sub>5</sub>   | D <sub>4</sub>    | D <sub>3</sub>    | D <sub>2</sub> | Dı               | D <sub>0</sub> |

|----------------|----------------|-------------------|------------------|-------------------|-------------------|----------------|------------------|----------------|

| Mode 1, input  | 1/0            | 1/0               | IBF <sub>A</sub> | INTEA             | INTR <sub>A</sub> | INTEB          | IBF <sub>B</sub> | INTR           |

| Mode 1, output | OBF            | INTE              | 1/0              | 1/0               | INTRA             | INTE           | OBFs             | INTR           |

| Mode 2         | OBFA           | INTE <sub>1</sub> | IBF <sub>A</sub> | INTE <sub>2</sub> | INTRA             | Вуд            | roup B r         | node           |

Table 3 Mode 0 control words

|                |                |    |    | Cont           | trol w         | ords |                |             |        | Group A                    | Group B                   |        |

|----------------|----------------|----|----|----------------|----------------|------|----------------|-------------|--------|----------------------------|---------------------------|--------|

| D <sub>7</sub> | D <sub>6</sub> | Dş | D4 | D <sub>3</sub> | D <sub>2</sub> | Dı   | D <sub>0</sub> | Hexadecimal | Port A | Port C (high-order 4 bits) | Port C (low-order 4 bits) | Port B |

| 1              | 0              | 0  | 0  | 0              | Ø              | 0 -  | O_             | 80          | OUT    | OUT                        | OUT                       | OUT    |

| 1              | 0              | 0  | 0  | 0              | .0             | 0    | 1              | 81          | OUT    | ОИТ                        | IN                        | OUT    |

| <br>1          | 0              | 0  | 0  | 0              | 0              | 1    | 0              | 82          | OUT    | OUT                        | OUT                       | IN     |

| 1              | 0              | 0  | 0  | 0              | 0              | 1    | 1              | 83          | OUT    | OUT                        | in                        | IN     |

| 1              | 0              | 0  | 0  | 1              | 0              | 0    | 0              | 88          | OUT    | IN                         | OUT                       | OUT    |

| 1              | 0              | 0  | 0  | 1              | 0              | 0    | 1              | 89          | OUT    | IN                         | IN                        | OUT    |

| 1              | 0              | 0  | 0  | 1              | 0              | 1    | 0              | 8A          | OUT    | IN                         | OUT                       | IN     |

| 1              | 0              | 0  | 0  | 1              | 0              | 1    | 1              | 8B          | OUT    | IN ·                       | IN                        | IN     |

| 1              | 0              | 0  | 1  | 0              | 0              | 0    | 0              | 90          | iN     | OUT                        | OUT                       | OUT    |

| 1              | 0              | 0  | 1  | Q              | 0              | 0    | 1              | 91          | IN     | OUT                        | IN                        | OUT    |

| 1              | 0              | 0  | 1  | 0              | Q              | 1    | 0              | 92          | IN     | OUT                        | OUT                       | IN     |

| 1              | 0              | 0  | 1  | 0              | 0              | 1    | 1              | 93          | IN     | OUT                        | IN .                      | IN     |

| 1              | 0              | 0  | 1  | 1              | 0              | 0    | 0              | 98          | IN     | - IN                       | OUT                       | OUT    |

| 1              | 0              | 0  | 1  | 1              | 0              | 0    | 1              | 99          | IN     | IN                         | IN                        | OUT    |

| <br>1          | 0              | 0  | 1  | 1              | 0              | 1    | . 0            | 9A          | IN     | IN ·                       | OUT                       | IN     |

| 1              | 0              | 0  | 1  | 1              | 0              | 1    | 1              | 9B          | IN     | IN                         | IN                        | IN     |

Note 4: OUT indicates output port, and IN indicates input port.

Table 4 Mode 1 control words -

|                |                |      | -              | ont | rol    | wo             | rds            |                | 1        |        |                 | Grou             | A qu             | <del></del>     |                 |                  | Gro              | up B              |        |

|----------------|----------------|------|----------------|-----|--------|----------------|----------------|----------------|----------|--------|-----------------|------------------|------------------|-----------------|-----------------|------------------|------------------|-------------------|--------|

| D <sub>7</sub> | D <sub>i</sub> | 6 Ds | D <sub>4</sub> |     | <br>l3 | D <sub>2</sub> | D <sub>t</sub> | D <sub>0</sub> | Hexa-    | Port A |                 |                  | Port C           | r               |                 |                  | Port C           | ·                 | Port B |

|                |                |      |                |     |        |                |                |                | decimal  |        | PC <sub>7</sub> | PC <sub>6</sub>  | PC <sub>5</sub>  | PC <sub>4</sub> | PC <sub>3</sub> | PC <sub>2</sub>  | PC <sub>1</sub>  | PC₀               |        |

| 1              | 0              | 1    | 0              | C   | )      | 1              | 0              | x              | A4<br>A5 | OUT    | OBFA            | ACK <sub>A</sub> | 01               | UT              | INTRA           | ACKB             | OBFB             | INTR <sub>B</sub> | оит    |

| 1              | 0              | 1    | 0              | C   | )      | 1              | 1              | x              | A6<br>A7 | OUT    | OBFA            | ACKA             | O                | UT              | INTRA           | STBB             | IBF <sub>B</sub> | INTRe             | IN     |

| 1              | 0              | 1    | 0              | 1   |        | 1              | 0              | x              | AC<br>AD | OUT    | OBFA            | ACKA             | - I              | N               | INTRA           | ACKB             | OBFB             | INTRe             | оит    |

| 1              | 0              | 1    | 0              | 1   |        | 1              | . 1            | x              | AE<br>AF | OUT    | OBFA            | ACKA             | 11               | N               | INTR            | STBB             | IBF <sub>B</sub> | INTR              | IN:    |

| 1              | 0              | 1    | 1              | C   | )      | 1              | 0              | x              | B4<br>B5 | IN     | 0               | UT               | IBF <sub>A</sub> | STBA            | INTRA           | ACK <sub>B</sub> | OBFB             | INTR <sub>B</sub> | OUT    |

| 1              | 0              | 1    | 1              | (   | )      | 1              | 1              | ×              | 86<br>87 | IN     | 0               | UT               | IBF <sub>A</sub> | STBA            | INTR            | STBB             | IBF8             | INTR              | IN     |

| 1              | 0              | 1    | 1              | 1   | i      | 1              | 0              | x              | BC<br>BD | IN     | 1               | N                | IBFA             | STBA            | INTRA           | ACKB             | OBF <sub>B</sub> | INTRe             | оит    |

| 1              | 0              | 1    | 1              | 1   | 1      | 1              | 1              | X              | BE<br>BF | IN     | - 1             | N                | IBF <sub>A</sub> | STBA            | INTRA           | STBB             | IBF <sub>e</sub> | INTR <sub>B</sub> | IN     |

Note 5: Mode of group A and group B can be programmed independently.

6: It is not necessary for both group A and group B to be in mode 1.

# PROGRAMMABLE PERIPHERAL INTERFACE

Table 5 Mode 2 control words

|          |                |                | С  | ont      | rol          | wo             | rds            |    |                 |                      |                 | Group A          | <b>A</b>         |                 |       | Group B         |                 |       |        |  |

|----------|----------------|----------------|----|----------|--------------|----------------|----------------|----|-----------------|----------------------|-----------------|------------------|------------------|-----------------|-------|-----------------|-----------------|-------|--------|--|

|          |                |                |    |          |              |                |                |    | Hexa-           | •                    |                 |                  | Port C           |                 |       |                 | PortC           | 4     | Port B |  |

| D7       | D <sub>6</sub> | D <sub>5</sub> | Dą | D        | 3            | D <sub>2</sub> | D <sub>1</sub> | Đţ | decimal<br>(Ex) | Port A               | PC <sub>7</sub> | PC <sub>6</sub>  | PC₅              | PC <sub>4</sub> | PC₃   | PC <sub>2</sub> | PC <sub>1</sub> | PC₀   | FOILD  |  |

| 1        | 1              |                | ×  | ×        | (            | 0              | 0              | 0  | C0              | Bidirectional<br>bus | OBFA            | ACK <sub>A</sub> | IBFA             | STBA            | INTRA |                 | OUT             |       | OUT    |  |

| 1        | 1              | ×              | X  |          | <del>-</del> | 0              | 0              | 1  | C1              | Bidirectional .      | OBFA            | ACKA             | IBF <sub>A</sub> | STBA            | INTRA |                 | IN              |       | OUT    |  |

| 1        | 1              | ×              | ×  | >        | (            | 0              | 1              | 0  | C2              | Bidirectional<br>bus | OBFA            | ACKA             | IBFA             | STBA            | INTRA |                 | OUT             |       | IN     |  |

| <u> </u> | 1              | X              | X  |          | ·-           | 0              | 1              | 1  | C3              | Bidirectional<br>bus | OBFA            | ACKA             | IBF <sub>A</sub> | STBA            | INTRA |                 | IN              |       | IN     |  |

| ì        | <u> </u>       | X              | X  | <u> </u> | ·-           | 1              | 0              | ×  | C4              | Bidirectional<br>bus | OBFA            | ACKA             | IBFA             | STBA            | INTRA | ACKB            | OBFe            | INTRB | OUT    |  |

| <u>.</u> | <u>:</u>       | - <u>``</u>    | ×  | _,       |              | 1              | 1              | ×  | C6              | Bidirectional<br>bus | OBFA            | ACKA             | IBFA             | STBA            | INTRA | STB             | IBFs            | INTRe | IN     |  |

Table 6 Port C bit set/reset control words

|                |                |    | Co             | ontro | l wo           | rds |                  |                  |                 |                 |                 | Poi             | t C |                 |                 |          | Remarks                                       |

|----------------|----------------|----|----------------|-------|----------------|-----|------------------|------------------|-----------------|-----------------|-----------------|-----------------|-----|-----------------|-----------------|----------|-----------------------------------------------|

| D <sub>7</sub> | D <sub>6</sub> | Dş | D <sub>4</sub> | D3    | D <sub>2</sub> | Dı  | D <sub>0</sub> . | Hexa-<br>decimal | PC <sub>7</sub> | PC <sub>6</sub> | PC <sub>5</sub> | PC <sub>4</sub> | PC₃ | PC <sub>2</sub> | PC <sub>1</sub> | PC₀      | **                                            |

| 0              | X              | х  | Х              | 0     | 0              | 0   | 0                | 00               |                 |                 |                 |                 |     |                 |                 | 0        |                                               |

| 0              | х              | х  | х              | 0     | 0              | 0   | 1                | 01               |                 | <b>.</b>        |                 |                 | L   |                 |                 | 1_       |                                               |

| 0              | ×              | х  | Х              | 0     | 0              | 1   | 0                | 02               |                 |                 |                 |                 |     |                 | 0               |          |                                               |

| σ              | х              | х  | Х              | 0     | 0              | 1   | 1                | 03               |                 |                 |                 |                 |     | <u> </u>        | 1               | <u> </u> |                                               |

| - 0            | х              | х  | х              | 0     | 1              | 0   | 0                | 04               |                 |                 |                 |                 |     | 0               |                 |          | INTE <sub>B</sub> set/reset for mode 1 input  |

| 0              | х              | х  | х              | 0     | 1              | 0   | 1                | 05               |                 |                 |                 |                 |     | 1               |                 |          | INTE <sub>B</sub> set/reset for mode 1 output |

| 0              | X              | ×  | х              | 0     | 1              | 1   | 0                | 06               |                 |                 |                 |                 | 0   |                 |                 |          |                                               |

| 0              | х              | ×  | х              | 0     | 1              | 1   | 1                | 07               |                 |                 |                 |                 | 1   |                 |                 |          |                                               |

| 0              | ×              | Х  | х              | 1     | 0              | 0   | 0                | 08               |                 |                 |                 | 0               |     |                 | Ī               |          | INTE <sub>A</sub> set/reset for mode 1 input  |

| 0              |                | ×  | -              |       | 0              | 0   | 1                | 09               |                 |                 |                 | 1               |     |                 |                 |          | INTE <sub>2</sub> set/reset for mode 2        |

| 0              | ×              | ×  | ×              | 1     | 0              | 1   | 0                | 0A               |                 |                 | 0               |                 |     |                 |                 |          |                                               |

| 0              |                | ×  |                |       | 0              | 1   | 1                | 0B               |                 |                 | 1               |                 |     |                 | Τ               |          |                                               |

| 0              |                | ×  |                |       | 1              | 0   | 0                | 0C               |                 | 0               |                 |                 |     |                 |                 |          | INTE <sub>A</sub> set/reset for mode 1 output |

| 0              |                | ×  |                |       | 1              | . 0 | 1                | 0D               | 1.              | 1               |                 |                 |     |                 |                 |          | INTE: set/reset for mode 2                    |

| 0              |                |    |                |       | 1              | 1   | 0                | 0E               | 0               |                 | Γ               |                 |     |                 |                 |          |                                               |

| 0              |                |    | ×              | 1     | 1              | 1   | 1                | 0F               | 1               |                 |                 | T -             |     |                 |                 |          |                                               |

Note 7: The terminals of port C should be programmed for the output mode, before the bit set/reset operation is executed.

8: Also used for controlling the interrupt enable flag(INTE).

# MITSUBISHI (MICMPTR/MIPRC)

T-52-33-05

### PROGRAMMABLE PERIPHERAL INTERFACE

### **ABSOLUTE MAXIMUM RATINGS**

| Symbol           | Parameter                            | Conditions                      | Ratings            | Unit             |

|------------------|--------------------------------------|---------------------------------|--------------------|------------------|

| Voc              | Supply voltage                       |                                 | -0.5~7             | V                |

| Vı               | Input voltage                        | With respect to V <sub>SS</sub> | -0.5~7             | - ·              |

| Vo               | Output voltage                       | •                               | -0.5~7             | - ·              |

| Pd               | Power dissipation                    | Ta=25°C                         | 1000               | mW               |

| Topr             | Operating free-air temperature range |                                 | -20~75             | *                |

| T <sub>stg</sub> | Storage temperature range            |                                 | <del>-65~150</del> | <del>  ~~~</del> |

# RECOMMENDED OPERATING CONDITIONS ( $\tau_a = -20 \sim 75 \, \text{C}$ , unless otherwise noted)

| Symbol | Parameter            |       | Limits |      | 11-11 |

|--------|----------------------|-------|--------|------|-------|

|        | t arameter           | Min   | Nom    | Max  | Unit  |

| Vcc    | Supply voltage       | 4. 75 | 5      | 5.25 | V     |

| Vss    | Supply voltage (GND) |       | 0      |      | V     |

# ELECTRICAL CHARACTERISTICS (Ta=-20~75°C, Vco=5 V±5 %, Vss=0 V, unless otherwise noted)

| Symbol           | Parameter                         |          | Test conditions                                                          |      | Limits |      |      |

|------------------|-----------------------------------|----------|--------------------------------------------------------------------------|------|--------|------|------|

|                  | - aramotor                        |          | rest conditions                                                          | Min  | Тур    | Max  | Unit |

| VIH              | High-level input voltage          |          |                                                                          | 2.0  |        | Vcc  |      |

| VIL              | Low-level input voltage           |          |                                                                          | -0.5 |        | 0.8  | v    |

| V <sub>OH</sub>  | High-level output voltage         | Data bus | I <sub>OH</sub> =-400μA                                                  |      |        |      |      |

| TOR              | Trigit-level output voltage       | Port     | I <sub>OH</sub> =-200μA                                                  | 2.4  |        |      | ٧    |

| Vol              | Low-level output voltage          | Data bus | I <sub>OL</sub> =2.5mA                                                   |      | -      | l    |      |

| VOL.             | con-level output voltage.         | Port     | I <sub>OL</sub> =1.7mA                                                   |      |        | 0.45 | ٧    |

| Іон              | High-level output current (Note10 | )        | V <sub>OH</sub> =1.5V, R <sub>EXT</sub> =750Ω                            | -1   |        | -4   | mA   |

| loo              | Supply current from Vcc           |          |                                                                          |      |        | 120  | mA   |

| h <sub>H</sub>   | High-level input current          |          | V <sub>I</sub> =V <sub>CC</sub>                                          |      |        | ±10  | μА   |

| կլ               | Low-level input current           |          | V <sub>I</sub> =0V                                                       |      |        | ±10  | μА   |

| loz              | Off-state output current          |          | Vo=0V~Vcc                                                                | 1    |        | ±10  | μA   |

| Cį               | Input terminal capacitance        |          | V <sub>IL</sub> =V <sub>SS</sub> , f=1MHz, 25mVrms T <sub>a</sub> =25°C  | 1    |        | 10   | pF   |

| C <sub>i/o</sub> | Input/output terminal capacitance |          | V <sub>VOL</sub> =V <sub>SS</sub> , f=1MHz, 25mVrms T <sub>a</sub> =25°C |      |        | 20   | pF   |

Note 9: Current flowing into an IC is positive: out is negative.

10: It is valid only for any 8 input/output pins of PB and PC.

# TIMING REQUIREMENTS ( $T_a = -20 \sim 75^{\circ}C$ , $V_{co} = 5 \text{ V} \pm 5 \%$ , $V_{ss} = 0 \text{ V}$ , unless otherwise noted)

| Symbol               | Prameter                            | Test conditions                       |     | Limits |     |      |

|----------------------|-------------------------------------|---------------------------------------|-----|--------|-----|------|

|                      | , ranger.                           | rest conditions                       | Min | Тур    | Max | Unit |

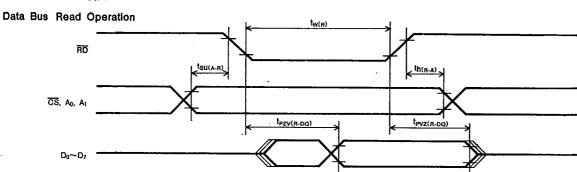

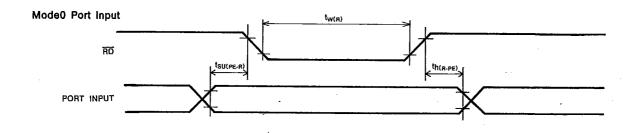

| tw(R)                | Read pulse width                    |                                       | 300 |        |     | ns   |

| tsu(PE-R)            | Peripheral setup time before read   |                                       | 0   |        |     | ns   |

| th(R-PE)             | Peripheral hold time after read     |                                       | 0   |        |     | ns   |

| t <sub>SU(A-R)</sub> | Address setup time before read      |                                       | 0   |        |     | ns   |

| th(R-A)              | Address hold time after read        |                                       | 0   |        |     | ns   |

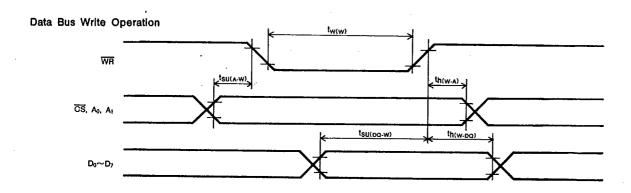

| tw(w)                | Write pulse width                   |                                       | 300 |        |     | ns   |

| tsu(po-w)            | Data setup time before write        | · · · · · · · · · · · · · · · · · · · | 100 |        |     | ns   |

| th(w-pq)             | Data hold time after write          |                                       | 30  |        |     | ns   |

| tsu(A-W)             | Address setup time before write     |                                       | 0   |        |     | ns   |

| th(W-A)              | Address hold time after write       | <del></del>                           | 20  | -      |     | ns   |

| tw(ACK)              | Acknowledge pulse width             | · · · · · ·                           | 300 |        |     | ns   |

| tw(ste)              | Strobe pulse width                  | <del>' '</del>                        | 500 |        | -   | ns   |

| tsu(PE-STB)          | Peripheral setup time before strobe |                                       | 0   | -      |     | ns   |

| th(sts-PE)           | Peripheral hold time after strobe   |                                       | 180 |        |     | ns   |

| t <sub>C(RW)</sub>   | Read/write cycle time               |                                       | 850 |        |     | ns   |

### MITSUBISHI LSIs

# M5L8255AP-5

MITSUBISHI (MICMPTR/MIPRC)

T-52-33-65

# PROGRAMMABLE PERIPHERAL INTERFACE

# SWITCHING CHARACTERISTICS ( $\tau_a = -20 \sim 75 \, \text{C}$ ; $V_{cc} = 5 \, \text{V} \pm 5 \, \text{\%}$ , $V_{ss} = 0 \, \text{V}$ , unless otherwise noted)

|                          |                                                             |                       |     | Limits |     | Unit |

|--------------------------|-------------------------------------------------------------|-----------------------|-----|--------|-----|------|

| Symbol                   | Parameter                                                   | Test conditions       | Min | Тур    | Max | Unit |

| PZV(R-DQ)                | Propagation time from read to data output                   |                       |     |        | 200 | ns   |

| t <sub>PVZ</sub> (R-DQ)  | Propagation time from read to data floating (Note11)        |                       | 10  |        | 100 | ns   |

| t <sub>PHL</sub> (W-PE)  | Propagation time from write to output                       |                       |     |        | 350 | ns   |

| tern(ate-iet)            | Propagation time from strobe to IBF flag                    | :                     |     |        | 300 | ns   |

| telH(STB-INTR)           | Propagation time from strobe to interrupt                   |                       | Ĺ   |        | 300 | ns   |

| PHL(R-INTR)              | Propagation time from read to interrupt                     | C <sub>L</sub> =150pF |     |        | 400 | ns   |

| t <sub>PHL</sub> (R-IBF) | Propagation time from read to IBF flag                      |                       | Ĺ   |        | 300 | ns   |

| tehr(W-INTR)             | Propagation time from write to interrupt                    | ]                     |     |        | 850 | ns   |

| tpsk(W-OBF)              | Propagation time from write to OBF flag                     |                       |     |        | 650 | ns   |

| PLH(ACK-OBF)             | Propagation time from acknowledge to OBF flag               |                       |     |        | 350 | ns   |

| PLH(ACK-INTR)            | Propagation time from acknowledge to interrupt              |                       |     |        | 350 | ns   |

| tpzy(ACK-PE)             | Propagation time from acknowledge to data output            | 1.                    |     |        | 300 | ns   |

| tpvz(ACK-PE)             | Propagation time from acknowledge to data floating (Note11) | 1                     | 20  |        | 250 | ns   |

Note 11: Test conditions are not applied

12: A.C Testing waveform

input pulse level

input pulse rise time

input pulse fall time

Reference level input

output

output

0.45~2.4V

0. 45~2. 4V 20ns 20ns V<sub>IH</sub>=2V, V<sub>IL</sub>=0. 8V V<sub>OH</sub>=2V, V<sub>OL</sub>=0. 8V

# M5L8255AP-5

T-52-33-05

### PROGRAMMABLE PERIPHERAL INTERFACE

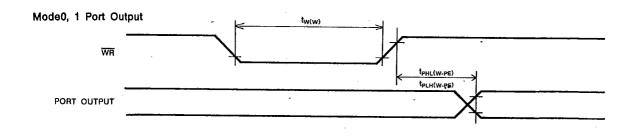

### **TIMING DIAGRAM**

MITSUBISHI LSIs

# M5L8255AP-5

T-52-33-05

# MITSUBISHI(MICMPTR/MIPRC)

# PROGRAMMABLE PERIPHERAL INTERFACE

# M5L8255AP-5

T-52-33-05

# PROGRAMMABLE PERIPHERAL INTERFACE

# Mode2 Bidirectional

Note 13:  $INTR=IBF \cdot \overline{MASK} \cdot \overline{STB} \cdot \overline{RD} + \overline{OBF} \cdot \overline{MASK} \cdot \overline{ACK} \cdot \overline{WR}$

# M5L8255AP-5

T-52-33-05

# PROGRAMMABLE PERIPHERAL INTERFACE

# CIRCUIT EXAMPLES FOR APPLICATIONS

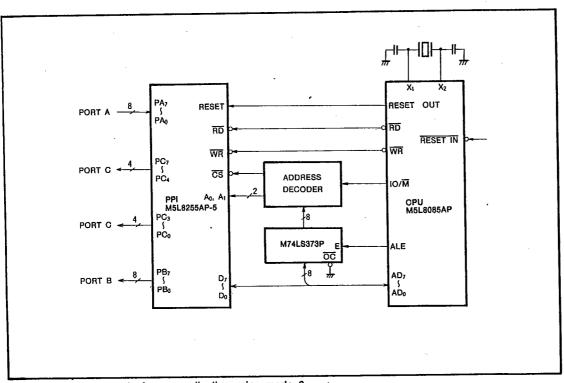

### 1. Mode 0

An example of a circuit for an application using mode 0 is shown in Fig. 11.

Fig. 11 Circuit example for an application using mode 0.

In this example, the PPI is in mode 0, and the control word should be  $10010000 \ (90_{16})$ .

MVI A, 90#

OUT 03#

The PPI will be initialized by executing the above two instructions.

Then, for example, to read data from port A and to output data to port B and C, the following three instructions can be used.

IN 00# CPU A register ← Port A

OUT 01# Port B ← A register

OUT 02# Port C ← A register

After setting the mode, each port operates as a normal port. After setting the mode, as shown in Fig. 11, to read data from port A, to output to port B, and to set the first bit of port C=1, the following four instructions can be used.

IN 00 # CPU A register ← Port A

OUT 01 # Port B ← A register

OUT 01 # Port B ← A register

MVI A, 01 # Bit-setting control word for PC₀

OUT 03# Outputting to control address  $(\overline{CS} = "L", A_1 = A_0 = 1)$

The other bits of port C, in this case, are not affected.

# M5L8255AP-5

T-52-33-05

# PROGRAMMABLE PERIPHERAL INTERFACE

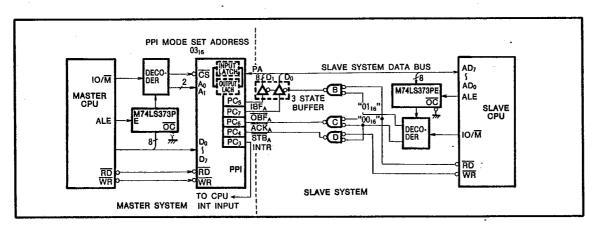

#### 2. Mode 1

An example of a circuit for an application using mode 1 is shown in Fig. 12.

FROM ADDRESS A FROM ADDRESS A FROM DECODER FROM CPU RESE INPUT DATA WR WR RD PA, PPI M5L8255AP-5D DATA STROBE D STB TO DATA BUS PC<sub>5</sub> IBFA D INTR, PB<sub>0</sub>~PB<sub>7</sub> {8 TO RST7.5 (INTERRUPT INPUT)

Fig. 12 A circuit for an application using mode 1

Transferring data from a terminal unit to port A and sending a strobe signal to  $PC_4$  will hold the data in the internal latch of the PPI, and  $PC_5$  (IBF input buffer full flag) is set to highlevel. If a bit-set of  $PC_4$  has been executed in advance, the CPU can be interrupted by the INTR signal of  $PC_3$  when the input data is latched in the PPI. In this way, port A becomes an interrupting port; and at the same time, port B can select its mode independently.

The actual program for the circuit of Fig. 12 is as follows:

MVI A, B0# Control word is 10110000, port A is the mode 1 input and the others are output

OUT 03# Outputting to the control address

MVI A, 09# PC<sub>4</sub>bit-set 00001001

OUT 03# Outputting to the control address

EI Interrupt enable

Halt

If the data has been set in a terminal unit, and the strobe signal has been input, then the data will be latched in port A and the CPU RST7.5 goes high-level. In the case of Fig. 11, a jump to  $003C_{16}$  is executed to continue the program as follows:

003C<sub>16</sub> IN 00# CPU register A ← Port A

PC₃ interrupt signal becomes low-level

EI

RET

# **M5L8255AP-5** T-52-33-05

### PROGRAMMABLE PERIPHERAL INTERFACE

#### 3, Mode 2

An example of a circuit for an application using mode 2 is shown in Fig. 13.

In Fig. 13, the data bus of the slave system is connected with the corresponding PPI A bit of the master station. The input port consists of a three-state buffer and gate B which allow the slave CPU to read flag outputs (IBF, OBF) of the PPI as data.

When the following instruction is executed in this example, the action is as described:

#### IN 01 # (reading in from 01<sub>16</sub> input port)

The data which is made up of the least significant bit  $(D_0)$ , the  $\overline{OBF}$  (output buffer full flag output) and the next least significant bit  $(D_1)$ , the IBF (input buffer full flag output) will be read into the slave CPU.

When the following instruction is executed, the action is as described:

### IN 00# (reading in from 00<sub>16</sub> input port)

ACK (PC<sub>6</sub>) of the PPI becomes low-level by gate C, and the contents of the port A output latch will be read into the slave CPU.

When the following instruction is executed, the action is as described:

### OUT 00# (writing out to 0016 output port)

STB (PC<sub>4</sub>) of the PPI becomes low-level by gate D, then the contents of the slave CPU register A will be written into the port A input latch of the PPI.

Actual operations are as follows:

- 1. PPI is set in mode 2 by the master CPU (03 address).

- The master CPU writes the data, which is transferred to the slave CPU, into port A of the PPI (in turn, OBF becomes low-level).

- The slave CPU continues to read the state of flags (OBF and IBF) as data while OBF is high-level (i.e. no data from the master CPU).

- 4. When the slave CPU senses that OBF has become low-level, the slave CPU starts to read the data from 00<sub>16</sub> (Which is the input address for the preceding data) which is in the output latch of port A (in turn, OBF returns to high-level).

- 5. During this period, the master CPU reads the status flags (reading in from 02 of port C) and checks the states of both the bit 7 (OBF) and bit 5 (IBF). If OBF is low-level, it indicates that the slave CPU has not yet received the data; so the master does not write new data. If OBF is high-level, the master CPU writes the next data.

- When data is to be transferred to the master CPU, the contents of the slave CPU A register will be transmited to the port input latch of the PPI. The slave CPU transfers the data to address 00<sub>16</sub> (in turn, the IBF becomes highlevel).

- 7. The master CPU transfers data to port C and then checks the status flag. If the input latch contains data from the slave CPU, which is indicated by IBF having a high-level output, the data is read from port (00<sub>16</sub>) (in turn, the IBF returns to low-level).

- The slave CPU reads the status flag from 01<sub>16</sub> to determine if IBF has returned to low-level. If it has not, new data will not be written as long as IBF is high-level.

- In this way, data can be exchanged. Since there are two sets of independent registers, input latch and output latch, used by port A of the PPI, it is not necessary to alternate input/output transfers.

A program which has operating functions as described above, is explained as follows.

The operation, in mode 2, for group A of the PPI is considered here.

Fig. 13 A circuit for an application using mode 2

# M5L8255AP-5

# T-52-33-05

### PROGRAMMABLE PERIPHERAL INTERFACE

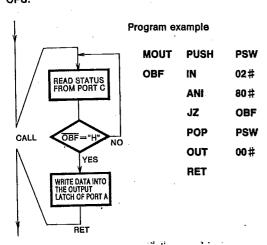

- Master CPU subroutine for transmitting data to the slave

CPU

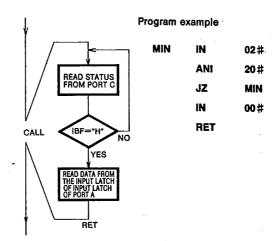

- 2. Subroutine for receiving data from the slave CPU.

- 3. Slave CPU subroutine for transmitting data to the master CPU.

- 4. Subroutine for receiving data from the master CPU.

# M5L8255AP-5

T-52-33-05

### PROGRAMMABLE PERIPHERAL INTERFACE

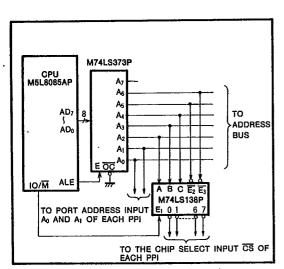

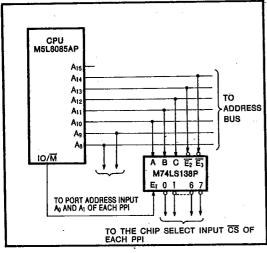

#### 4. Address Decoding

Address decoding with multiple PPI units is shown in Figs. 14 and 15. These are functionally equal.

The same address data is output to both the upper and lower 8 bits address bus with the execution of IN or OUT instruction by the CPU.

Fig. 14 PPI address decoding (case 1)

Fig. 15 PPI address decoding (case 2)

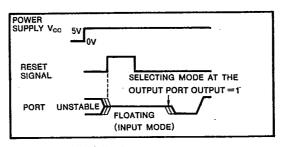

### 5. PPI Initialization

It is advisable to rest the PPI with a system initial reset and to select the mode at the beginning of a system program. The initial state of the PPI used as an output port is shown in Fig. 16.

Fig. 16 PPI initialization

Note 14: Period of reset pulse must be at least 50 µs during or after power on. Subsequent reset pulse can be 500ns minimum.