#### **Features**

- High performance, low power Atmel<sup>®</sup> AVR<sup>®</sup> 8-bit Microcontroller

- Advanced RISC architecture

- 131 powerful instructions most single clock cycle execution

- 32 x 8 general purpose working registers

- Fully static operation

- Up to eight MIPS throughput at 8MHz

- . High endurance non-volatile memory segments

- 16K/32Kbytes of in-system self-programmable flash (Atmel ATmega16HVB/32HVB)

- 512/1Kbytes EEPROM

- 1K/2Kbytes internal SRAM

- Write/erase cycles 10,000 flash/100,000 EEPROM

- Data retention: 20 years at 85°C/100 years at 25°C (1)

- Optional boot code section with independent lock bits In-system programming by on-chip boot program

True read-while-write operation

- Programming lock for software security

- · Battery management features

- Two, three or four cells in series

- High-current protection (charge and discharge)

- Over-current protection (charge and discharge)

- Short-circuit protection (discharge)

- High-voltage outputs to drive N-channel charge/discharge FETs

- Optional deep under voltage recovery mode allowing 0-volt charging without external precharge FET

- Optional high-voltage open drain output allowing 0-volt charging with external precharge FET

- Integrated cell balancing FETs

- Peripheral features

- Two configurable 8-bit or 16-bit timers with separate prescaler, optional input capture (IC), compare mode and CTC

- SPI serial peripheral interface

- 12-bit voltage ADC, six external and one internal ADC input

- High resolution coulomb counter ADC for current measurements

- TWI serial interface supporting SMBus implementation

- Programmable watchdog timer

- · Special microcontroller features

- debugWIRE on-chip debug system

- In-system programmable via SPI ports

- Power-on reset

- On-chip voltage regulator with short-circuit monitoring interface

- External and Internal interrupt sources

- Sleep modes: idle, ADC noise reduction, power-save, and power-off

- Additional secure authentication features available only under NDA

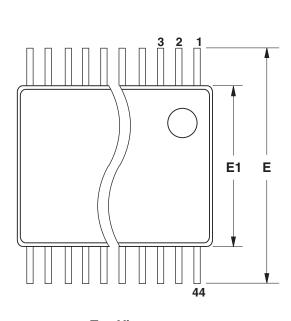

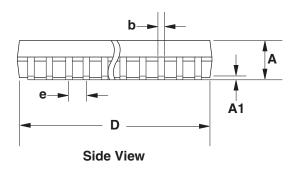

- Packages

- 44-pin TSSOP

- Operating voltage: 4V -18V

- Maximum withstand voltage (high-voltage pins): 35V

- Temperature range: -40°C to 85°C

- Speed grade: 1MHz 8MHz

Note: 1. See "Data retention" on page 8 for details.

8-bit **AVR**®

Microcontroller with

16K/32Kbytes

In-System

Programmable

Flash

ATmega16HVB ATmega32HVB

Summary

8042ES-AVR-09/2013

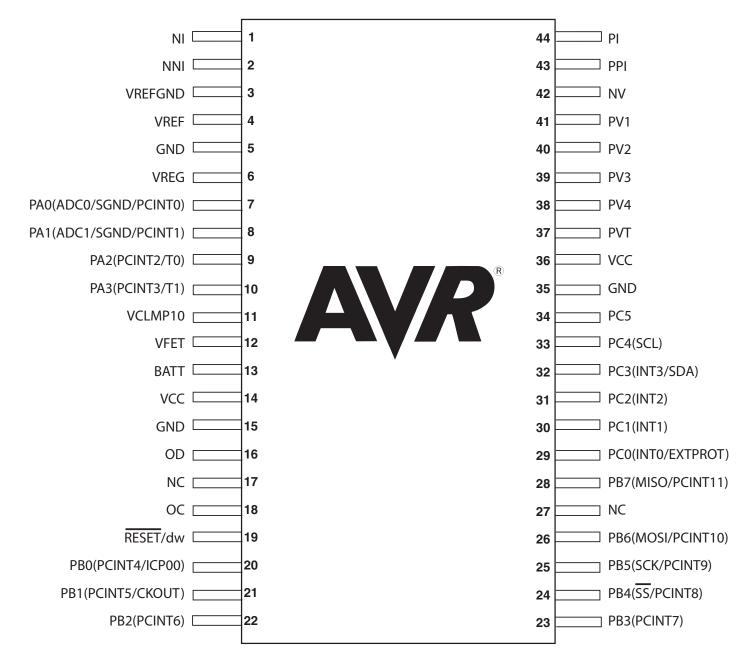

### 1. Pin configurations

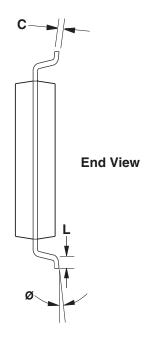

#### 1.1 TSSOP

Figure 1-1. TSSOP - pinout the Atmel ATmega16HVB/32HVB.

#### 1.2 Pin descriptions

#### 1.2.1 VFET

High voltage supply pin. This pin is used as supply for the internal voltage regulator, described in "Voltage regulator" on page 129.

#### 1.2.2 VCLMP10

Internal 10V clamping of VFET voltage for external decoupling.

#### 1.2.3 VCC

Digital supply voltage. Normally connected to VREG.

#### 1.2.4 VREG

Output from the internal voltage regulator. Used for external decoupling to ensure stable regulator operation. For details, see "Voltage regulator" on page 129.

#### 1.2.5 VREF

Internal voltage reference for external decoupling. For details, see "Voltage reference and temperature sensor" on page 122.

#### 1.2.6 VREFGND

Ground for decoupling of internal voltage reference. For details, see "Voltage reference and temperature sensor" on page 122. Do not connect to GND or SGND on PCB.

#### 1.2.7 GND

Ground.

#### 1.2.8 Port A (PA3..PA0)

Port A serves as a low-voltage 4-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). As inputs, Port A pins that are externally pulled low will source current if the pull-up resistors are activated. The Port A pins are tri-stated when a reset condition becomes active, even if the clock is not running.

Port A also serves the functions of various special features of the Atmel ATmega16HVB/32HVB as listed in "Alternate functions of Port A" on page 74.

#### 1.2.9 Port B (PB7..PB0)

Port B is a low-voltage 8-bit bi-directional I/O port with internal pull-up resistors (selected for each bit). As inputs, Port B pins that are externally pulled low will source current if the pull-up resistors are activated. The Port B pins are tri-stated when a reset condition becomes active, even if the clock is not running.

Port B also serves the functions of various special features of the ATmega16HVB/32HVB as listed in "Alternate functions of Port B" on page 75.

#### 1.2.10 Port C (PC5)

Port C (PC5) is a high voltage Open Drain output port.

#### 1.2.11 Port C (PC4..PC0)

Port C is a 5-bit high voltage Open Drain bi-directional I/O port.

#### 1.2.12 OC/OD

High voltage output to drive Charge/Discharge FET. For details, see "FET driver" on page 145.

#### 1.2.13 PI/NI

Filtered positive/negative input from external current sense resistor, used to by the Coulomb Counter ADC to measure charge/discharge currents flowing in the battery pack. For details, see "Coulomb counter – Dedicated fuel gauging Sigma-Delta ADC" on page 108.

#### 1.2.14 PPI/NNI

Unfiltered positive/negative input from external current sense resistor, used by the battery protection circuit, for over-current and short-circuit detection. For details, see "Battery protection" on page 132.

#### 1.2.15 NV/PV1/PV2/PV3/PV4

NV, PV1, PV2, PV3, and PV4 are the inputs for battery cells one, two, three and four, used by the Voltage ADC to measure each cell voltage. For details, see "Voltage ADC – 7-channel general purpose 12-bit Sigma-Delta ADC" on page 116.

#### 1.2.16 PVT

Defines the source voltage level for the Charge FET driver. For details, see "FET driver" on page 145.

#### 1.2.17 BATT

Input for detecting when a charger is connected. Defines the source voltage level for the Discharge FET driver. For details, see "FET driver" on page 145.

#### 1.2.18 RESET/dw

Reset input. A low level on this pin for longer than the minimum pulse length will generate a reset, even if the clock is not running. The minimum pulse length is given in Table 32-3 on page 227. Shorter pulses are not guaranteed to generate a reset. This pin is also used as debugWIRE communication pin.

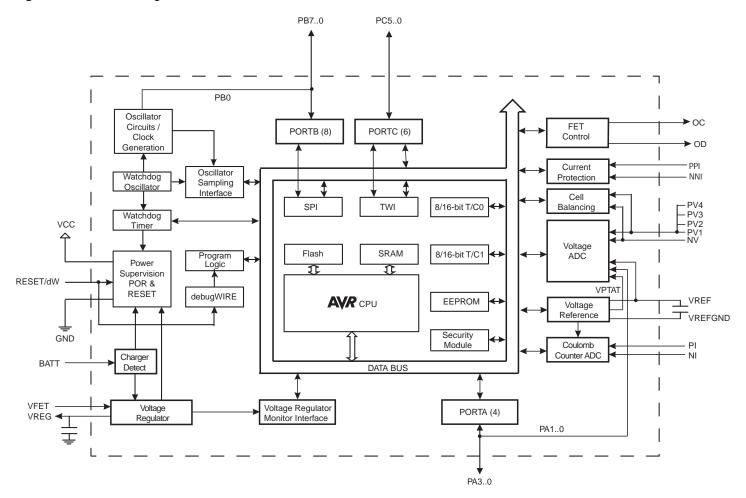

#### 2. Overview

The Atmel ATmega16HVB/32HVB is a monitoring and protection circuit for 3- and 4-cell Li-ion applications with focus on highest safety including safe authentication, low cost and high utilization of the cell energy. The device contains secure authentication features as well as autonomous battery protection during charging and discharging. The External Protection Input can be used to implement other battery protection mechanisms using external components, for example, protection against chargers with too high charge voltage can be easily implemented with a few low cost passive components. The feature set makes the ATmega16HVB/32HVB a key component in any system focusing on high security, battery protection, high system utilization and low cost.

Figure 2-1. Block diagram.

ATmega16HVB/32HVB provides the necessary redundancy on-chip to make sure that the battery is protected in critical failure modes. The chip is specifically designed to provide safety for the battery cells in case of pin shorting, loss of power (either caused by battery pack short or VCC short), illegal charger connection or software runaway. This makes ATmega16HVB/32HVB the ideal one-chip solution for applications with focus on high safety.

The ATmega16HVB/32HVB features an integrated voltage regulator that operates at a wide range of input voltages, 4 - 18 volts. This voltage is regulated to a constant supply voltage of

nominally 3.3 volts for the integrated logic and analog functions. The regulator capabilities, combined with an extremely low power consumption in the power saving modes, greatly enhances the cell energy utilization compared to existing solutions.

The chip utilizes the Atmel patented Deep Under-voltage Recovery (DUVR) mode that supports pre-charging of deeply discharged battery cells without using a separate Pre-charge FET. DUVR mode cannot be used in 2-cell applications. Optionally, Pre-charge FETs are supported for integration into many existing battery charging schemes.

The battery protection monitors the charge and discharge current to detect illegal conditions and protect the battery from these when required. A 12-bit Voltage ADC allows software to monitor each cell voltage individually with high accuracy. The ADC also provides one internal input channel to measure on-chip temperature and two input channels intended for external thermistors. An 18-bit ADC optimized for Coulomb Counting accumulates charge and discharge currents and reports accumulated current with high resolution and accuracy. It can also be used to provide instantaneous current measurements with 13-bit resolution. Integrated Cell Balancing FETs allow cell balancing algorithms to be implemented in software.

The MCU provides the following features: 16K/32Kbytes of In-System Programmable Flash with Read-While-Write capabilities, 512/1Kbytes EEPROM, 1K/2Kbytes SRAM. 32 general purpose working registers, 12 general purpose I/O lines, five general purpose high voltage open drain I/O lines, one general purpose super high voltage open drain output, debugWIRE for on-chip debugging and SPI for In-system Programming, a SM-Bus compliant TWI module, two flexible Timer/Counters with Input Capture and compare modes.

Internal and external interrupts, a 12-bit Sigma Delta ADC for voltage and temperature measurements, a high resolution Sigma Delta ADC for Coulomb Counting and instantaneous current measurements, integrated cell balancing FETs, Additional Secure Authentication Features, an autonomous Battery Protection module, a programmable Watchdog Timer with internal Oscillator, and software selectable power saving modes.

The AVR core combines a rich instruction set with 32 general purpose working registers. All the 32 registers are directly connected to the Arithmetic Logic Unit (ALU), allowing two independent registers to be accessed in one single instruction executed in one clock cycle. The resulting architecture is more code efficient while achieving throughputs up to ten times faster than conventional CISC microcontrollers.

The device is manufactured using the Atmel high voltage high density non-volatile memory technology. The On-chip ISP Flash allows the program memory to be reprogrammed In-System, through an SPI serial interface, by a conventional non-volatile memory programmer or by an On-chip Boot program running on the AVR core. The Boot program can use any interface to down-load the application program in the Application Flash memory. Software in the Boot Flash section will continue to run while the Application Flash section is updated, providing true Read-While-Write operation. By combining an 8-bit RISC CPU with In-System Self-Programmable-Flash and highly accurate analog front-end in a monolithic chip.

The Atmel ATmega16HVB/32HVB is a powerful microcontroller that provides a highly flexible and cost effective solution. It is part of the AVR Battery Management family that provides secure authentication, highly accurate monitoring and autonomous protection for Lithium-ion battery cells.

The ATmega16HVB/32HVB AVR is supported with a full suite of program and system development tools including: C Compilers, Macro Assemblers, Program Debugger/Simulators, and Onchip Debugger.

## ATmega16HVB/32HVB

### 2.1 Comparison between the Atmel ATmega16HVB and the Atmel ATmega32HVB

The ATmega16HVB and the ATmega32HVB differ only in memory size for flash, EEPROM and internal SRAM. Table 2-1 summarizes the different configuration for the two devices.

Table 2-1.

Configuration summary.

| Device      | Flash | EEPROM | SRAM |

|-------------|-------|--------|------|

| ATmega16HVB | 16K   | 512    | 1K   |

| ATmega32HVB | 32K   | 1K     | 2K   |

#### 3. Disclaimer

All parameters contained in this datasheet are preliminary and based on characterization of the Atmel ATmega16/32HVB.

#### 4. Resources

A comprehensive set of development tools, application notes and datasheets are available for download on <a href="http://www.atmel.com/avr">http://www.atmel.com/avr</a>.

### 5. About code examples

This documentation contains simple code examples that briefly show how to use various parts of the device. These code examples assume that the part specific header file is included before compilation. Be aware that not all C compiler vendors include bit definitions in the header files and interrupt handling in C is compiler dependent. Please confirm with the C compiler documentation for more details.

For I/O registers located in extended I/O map, "IN", "OUT", "SBIS", "SBIC", "CBI", and "SBI" instructions must be replaced with instructions that allow access to extended I/O. Typically "LDS" and "STS" combined with "SBRS", "SBRC", "SBR", and "CBR".

#### 6. Data retention

Reliability Qualification results show that the projected data retention failure rate is much less than one PPM over 20 years at 85°C or 100 years at 25°C.

## 7. Register summary

| Address                    | Name                 | Bit 7 | Bit 6   | Bit 5   | Bit 4   | Bit 3     | Bit 2    | Bit 1   | Bit 0   | Page |

|----------------------------|----------------------|-------|---------|---------|---------|-----------|----------|---------|---------|------|

| (0xFF)                     | Reserved             | -     | -       | -       | -       | -         | -        | -       | -       |      |

| (0xFE)                     | BPPLR                | -     | -       | -       | -       | -         | -        | BPPLE   | BPPL    | 137  |

| (0xFD)                     | BPCR                 | ı     | -       | EPID    | SCD     | DOCD      | COCD     | DHCD    | CHCD    | 138  |

| (0xFC)                     | BPHCTR               | I     | -       |         | •       | HCF       | PT[5:0]  | •       | ·       | 140  |

| (0xFB)                     | BPOCTR               | I     | -       |         |         | OCF       | PT[5:0]  |         |         | 139  |

| (0xFA)                     | BPSCTR               | I     |         |         |         | SCPT[6:0] |          |         |         | 139  |

| (0xF9)                     | BPCHCD               |       | •       |         | CHC     | DL[7:0]   |          |         |         | 142  |

| (0xF8)                     | BPDHCD               |       |         |         | DHC     | DL[7:0]   |          |         |         | 142  |

| (0xF7)                     | BPCOCD               |       |         |         | COC     | DL[7:0]   |          |         |         | 142  |

| (0xF6)                     | BPDOCD               |       |         |         | DOC     | DL[7:0]   |          |         |         | 141  |

| (0xF5)                     | BPSCD                |       |         |         | SCI     | DL[7:0]   |          |         |         | 141  |

| (0xF4)                     | Reserved             | -     | -       | -       | _       | -         | -        | -       | -       |      |

| (0xF3)                     | BPIFR                | -     | _       | -       | SCIF    | DOCIF     | COCIF    | DHCIF   | CHCIF   | 144  |

| (0xF2)                     | BPIMSK               | -     | -       | -       | SCIE    | DOCIE     | COCIE    | DHCIE   | CHCIE   | 143  |

| (0xF1)                     | CBCR                 | 1     | _       | _       | _       | CBE4      | CBE3     | CBE2    | CBE1    | 152  |

| (0xF0)                     | FCSR                 | 1     | _       | _       | _       | DUVRD     | CPS      | DFE     | CFE     | 149  |

| (0xEF)                     | Reserved             | l     | _       | _       | _       | _         | _        | -       | -       |      |

| (0xEE)                     | Reserved             | -     | -       | -       | -       | -         | -        | -       | -       |      |

| (0xED)                     | Reserved             | -     | -       | -       | -       | -         | -        | -       | -       |      |

| (0xEC)                     | Reserved             |       | -       | -       | -       | -         | -        | -       | -       |      |

| (0xEB)                     | Reserved             | ı     | -       | -       | _       | _         | -        | -       | -       |      |

| (0xEA)                     | CADRDC               |       |         |         | CADE    | DC[7:0]   |          |         |         | 115  |

| (0xE9)                     | CADRCC               |       |         |         | CADR    | CC[7:0]   |          |         |         | 114  |

| (0xE8)                     | CADCSRC              | -     | -       | -       | -       | -         | -        | -       | CADVSE  | 114  |

| (0xE7)                     | CADCSRB              | -     | CADACIE | CADRCIE | CADICIE | -         | CADACIF  | CADRCIF | CADICIF | 112  |

| (0xE6)                     | CADCSRA              | CADEN | CADPOL  | CADUB   | CADA    | \S[1:0]   | CAD      | SI[1:0] | CADSE   | 111  |

| (0xE5)                     | CADICH               |       | •       | •       | CADI    | C[15:8]   |          |         |         | 114  |

| (0xE4)                     | CADICL               |       |         |         |         | IC[7:0]   |          |         |         | 114  |

| (0xE3)                     | CADAC3               |       |         |         |         | C[31:24]  |          |         |         | 114  |

| (0xE2)                     | CADAC2               |       |         |         |         | C[23:16]  |          |         |         | 114  |

| (0xE1)                     | CADAC1               |       |         |         |         | C[15:8]   |          |         |         | 114  |

| (0xE0)                     | CADAC0               |       |         |         |         | AC[7:0]   |          |         |         | 114  |

| (0xDF)                     | Reserved             | -     | _       | _       | _       | _         | _        | -       | -       |      |

| (0xDE)                     | Reserved             | -     | =       | -       | _       | _         | _        | -       | -       |      |

| (0xDD)                     | Reserved             | _     | -       | -       | _       | -         | -        | _       | _       |      |

| (0xDC)                     | Reserved             | -     | -       | -       | -       | -         | -        | -       | -       |      |

| (0xDB)                     | Reserved             | -     | =       | -       | _       | _         | _        | -       | -       |      |

| (0xDA)                     | Reserved             | 1     | _       | _       | _       | _         | _        | -       | -       |      |

| (0xD9)                     | Reserved             | -     | =       | -       | _       | _         | _        | -       | -       |      |

| (0xD8)                     | Reserved             | -     | =       | -       | _       | _         | _        | -       | -       |      |

| (0xD7)                     | Reserved             | _     | -       | -       | _       | -         | -        | _       | _       |      |

| (0xD6)                     | Reserved             | _     | _       | _       | _       | _         | _        | -       | _       |      |

| (0xD5)                     | Reserved             | -     | -       | -       | _       | _         | _        | -       | _       |      |

| (0xD4)                     | CHGDCSR              | _     | _       | _       | BATTPVL | CHGDISC1  | CHGDISC1 | CHGDIF  | CHGDIE  | 128  |

| (0xD3)                     | Reserved             | _     | -       | _       | -       | -         | -        | -       | -       | -    |

| (0xD2)                     | BGCSR                | -     | _       | BGD     | BGSCDE  | _         | _        | BGSCDIF | BGSCDIE | 125  |

| (0xD1)                     | BGCRR                |       |         |         |         | R[7:0]    |          |         |         | 124  |

| (0xD0)                     | BGCCR                | _     | _       |         |         |           | C[5:0]   |         |         | 9    |

| (0xCF)                     | Reserved             | _     | _       | _       | _       | _         | -        | _       | _       |      |

| (0xCE)                     | Reserved             | _     | _       | _       | _       | _         | _        | _       | _       |      |

| (0xCD)                     | Reserved             | _     | _       | _       | _       | _         | _        | _       | _       |      |

| (0xCC)                     | Reserved             | _     | _       | _       | _       | _         | _        | _       | _       |      |

| (0xCB)                     | Reserved             | _     | _       | _       | _       | _         | _        | _       | _       |      |

| (0xCA)                     | Reserved             | _     | _       | _       | _       | _         | _        | _       | _       |      |

| (0xC9)                     | Reserved             | _     | _       | _       | _       | _         | _        | _       | _       |      |

| (0xC8)                     | ROCR                 | ROCS  | _       | _       | ROCD    | _         | _        | ROCWIF  | ROCWIE  | 131  |

| (0xC7)                     | Reserved             | -     | _       | _       | -       | _         | _        | -       | -       |      |

|                            | Reserved             | _     | _       | _       | _       | _         | _        | _       | _       |      |

| (OXCB)                     |                      | _     | _       | _       | _       | _         | _        | _       | _       |      |

| (0xC6)<br>(0xC5)           | Reserved             |       |         |         |         | _         | _        | _       | _       |      |

| (0xC5)                     | Reserved<br>Reserved | 1     | _       |         | _       |           |          |         |         |      |

| (0xC5)<br>(0xC4)           | Reserved             | _     | _       | _       | -       |           |          |         |         |      |

| (0xC5)<br>(0xC4)<br>(0xC3) | Reserved<br>Reserved | -     | -       | -       | -       | -         | -        | -       | -       |      |

| (0xC5)<br>(0xC4)           | Reserved             |       |         |         |         |           |          |         |         |      |

| A al alue e e    | Neme                 | D# 7       | Dit C   | D:4 5    | D:4.4            | D:4 2               | D:4 0  | D:4.4  | D:4 0     | Dono |

|------------------|----------------------|------------|---------|----------|------------------|---------------------|--------|--------|-----------|------|

| Address          | Name                 | Bit 7      | Bit 6   | Bit 5    | Bit 4            | Bit 3               | Bit 2  | Bit 1  | Bit 0     | Page |

| (0xBF)           | Reserved             | -          | -       | -        | -                | -                   |        |        | -         |      |

| (0xBE)           | TWBCSR               | TWBCIF     | TWBCIE  | -        | - TIMMAN (C. C.) | -                   | TWBDT1 | TWBDT0 | TWBCIP    | 184  |

| (0xBD)           | TWAMR                | TAMAT      | T. 45.4 | T14/07.4 | TWAM[6:0]        | 711110              | T.A.E. |        | -<br>TAUE | 184  |

| (0xBC)           | TWCR                 | TWINT      | TWEA    | TWSTA    | TWSTO            | TWWC                | TWEN   | -      | TWIE      | 181  |

| (0xBB)           | TWDR                 |            |         |          |                  | erface Data Regis   | ter    |        | THOOF     | 183  |

| (0xBA)           | TWAR                 |            |         | TW017-01 | TWA[6:0]         |                     |        | TWDO4  | TWGCE     | 183  |

| (0xB9)           | TWSR                 |            |         | TWS[7:3] |                  | Bit B-t- Bi         | -      | TWPS1  | TWPS0     | 182  |

| (0xB8)           | TWBR                 |            |         |          |                  | ace Bit Rate Reg    |        |        |           | 181  |

| (0xB7)           | Reserved             | -          |         | -        | -                | -                   | _      | -      | -         |      |

| (0xB6)           | Reserved<br>Reserved | -          | _       | -        | -                | -                   | -      | -      | -         |      |

| (0xB5)<br>(0xB4) |                      | _          | -       | _        | _                | _                   | _      | _      | _         |      |

| (0xB4)<br>(0xB3) | Reserved<br>Reserved | _          | _       | -        | _                | _                   | _      | -      | _         |      |

| (0xB3)           | Reserved             | _          | _       | _        | _                | _                   | _      | _      | _         |      |

| (0xB2)           | Reserved             | _          | _       | _        | _                | _                   |        | _      | _         |      |

| (0xB1)           | Reserved             |            | _       | _        | _                | _                   | _      | _      | _         |      |

| (0xB0)           | Reserved             | _          | _       | -        | -                | _                   | _      | _      | _         |      |

| (0xAE)           | Reserved             | _          | _       | _        | _                | _                   | _      | _      | _         |      |

| (0xAL)           | Reserved             | _          |         | _        | _                | _                   | _      | _      | _         |      |

| (0xAC)           | Reserved             | _          | _       | _        | _                | _                   | _      | _      | _         |      |

| (0xAB)           | Reserved             | _          | _       | _        | _                | _                   | _      | _      | _         |      |

| (0xAA)           | Reserved             | _          | _       | _        | _                | _                   | _      | _      | _         |      |

| (0xA9)           | Reserved             | _          | _       | -        | _                | -                   | _      | _      | _         |      |

| (0xA8)           | Reserved             | -          | _       | _        | _                | _                   | _      | _      | _         |      |

| (0xA7)           | Reserved             | _          | _       | _        | _                | _                   | _      | _      | _         |      |

| (0xA6)           | Reserved             | _          | _       | _        | _                | -                   | _      | _      | _         |      |

| (0xA5)           | Reserved             | -          | _       | _        | _                | -                   | _      | _      | _         |      |

| (0xA4)           | Reserved             | -          | _       | -        | -                | -                   | -      | -      | _         |      |

| (0xA3)           | Reserved             | _          | -       | _        | -                | -                   | _      | _      | _         |      |

| (0xA2)           | Reserved             | -          | _       | -        | -                | -                   | -      | -      | _         |      |

| (0xA1)           | Reserved             | _          | -       | _        | -                | _                   | _      | _      | _         |      |

| (0xA0)           | Reserved             | _          | -       | _        | -                | -                   | _      | _      | _         |      |

| (0x9F)           | Reserved             | -          | _       | -        | -                | -                   | _      | _      | _         |      |

| (0x9E)           | Reserved             | -          | -       | -        | -                | -                   | -      | -      | -         |      |

| (0x9D)           | Reserved             | -          | -       | -        | -                | -                   | -      | -      | -         |      |

| (0x9C)           | Reserved             | -          | -       | -        | -                | -                   | -      | -      | _         |      |

| (0x9B)           | Reserved             | -          | -       | -        | -                | -                   | _      | -      | _         |      |

| (0x9A)           | Reserved             | _          | -       | -        | -                | -                   | _      | _      | _         |      |

| (0x99)           | Reserved             | _          | -       | -        | -                | _                   | _      | -      | _         |      |

| (0x98)           | Reserved             | _          | _       | _        | _                | -                   | _      | _      | _         |      |

| (0x97)           | Reserved             | -          | -       | -        | -                | -                   | -      | -      | -         |      |

| (0x96)           | Reserved             | -          | -       | -        | -                | -                   | -      | -      | -         |      |

| (0x95)           | Reserved             | -          | -       | -        | -                | -                   | -      | _      | -         |      |

| (0x94)           | Reserved             | -          | -       | -        | -                | -                   | -      | _      | -         |      |

| (0x93)           | Reserved             | -          | -       | -        | -                | -                   | -      | -      | _         |      |

| (0x92)           | Reserved             | -          | -       | -        | -                | -                   | -      | -      | -         |      |

| (0x91)           | Reserved             | -          | -       | -        | -                | -                   | -      | -      | -         |      |

| (0x90)           | Reserved             | -          | -       | -        | -                | -                   | -      | -      | -         |      |

| (0x8F)           | Reserved             | -          | -       | -        | -                | -                   | -      | -      | -         |      |

| (0x8E)           | Reserved             | -          | -       | -        | -                | -                   | -      | -      | -         |      |

| (0x8D)           | Reserved             | -          | -       | -        | -                | -                   | _      | -      | -         |      |

| (0x8C)           | Reserved             | -          | -       | -        | -                | -                   | -      | -      | -         |      |

| (0x8B)           | Reserved             | _          | -       | -        | -                | -                   | _      | _      | -         |      |

| (0x8A)           | Reserved             | _          | -       |          | -                |                     |        | _      | -         |      |

| (0x89)           | OCR1B                |            |         |          |                  | put Compare Reg     |        |        |           | 95   |

| (0x88)           | OCR1A                |            |         |          |                  | put Compare Reg     |        |        |           | 95   |

| (0x87)           | Reserved             | -          | -       | -        | -                | -                   | -      | -      | -         |      |

| (0x86)           | Reserved             | -          | -       | -        |                  |                     | =      | -      | -         |      |

| (0x85)           | TCNT1H               |            |         |          |                  | 1 (8 Bit) High Byte |        |        |           | 95   |

| (0x84)           | TCNT1L               |            |         |          |                  | 1 (8 Bit) Low Byte  |        |        |           | 95   |

| (0x83)           | Reserved             | -          | _       | -        | -                | -                   | -      | _      | -         |      |

| (0x82)           | Reserved             | -          | _       | -        | -                | -                   | -      | -      | -         |      |

| (0x81)           | TCCR1B               | -<br>TOM/4 | -       | -        | -                | -                   | CS12   | CS11   | CS10      | 81   |

|                  |                      | TCW1       | ICEN1   | ICNC1    | ICES1            | ICS1                | _      | _      | WGM10     | 94   |

| (0x80)<br>(0x7F) | TCCR1A<br>Reserved   | -          | -       | -        | -                | -                   | _      | _      | _         |      |

# ■ ATmega16HVB/32HVB

| Address                    | Name                 | Bit 7      | Bit 6                            | Bit 5      | Bit 4             | Bit 3                                | Bit 2       | Bit 1             | Bit 0        | Page     |

|----------------------------|----------------------|------------|----------------------------------|------------|-------------------|--------------------------------------|-------------|-------------------|--------------|----------|

| (0x7D)                     | Reserved             | - Dit 7    | - Dit 0                          | Dit 3      | Dit 4             | Bit 3                                | Dit 2       | Dit 1             | -            | 1 age    |

| (0x7C)                     | VADMUX               |            |                                  |            |                   | _                                    | VADN        | MUX[3:0]          |              | 119      |

| (0x7B)                     | Reserved             | _          | _                                | _          | _                 | _                                    | _           | -                 | _            |          |

| (0x7A)                     | VADCSR               | _          | _                                | _          | -                 | VADEN                                | VADSC       | VADCCIF           | VADCCIE      | 119      |

| (0x79)                     | VADCH                | -          | -                                | -          | -                 |                                      | VADC Data R | egister High byte | '            | 120      |

| (0x78)                     | VADCL                |            | -                                |            | VADC Data R       | egister Low byte                     |             |                   |              | 120      |

| (0x77)                     | Reserved             | _          | _                                | -          | -                 | -                                    | -           | -                 | _            |          |

| (0x76)                     | Reserved             | _          | _                                | -          | _                 | -                                    | -           | -                 | -            |          |

| (0x75)                     | Reserved             | _          | _                                | -          | -                 | -                                    | -           | -                 | -            |          |

| (0x74)                     | Reserved             | _          | _                                | -          | _                 | -                                    | _           | -                 | -            |          |

| (0x73)                     | Reserved             | -          | -                                | -          | _                 | -                                    | _           | _                 | -            |          |

| (0x72)<br>(0x71)           | Reserved<br>Reserved | _          | _                                | _          | -                 | _                                    | -           | _                 | _            |          |

| (0x71)<br>(0x70)           | Reserved             |            | _                                |            |                   | _                                    |             | _                 | _            |          |

| (0x6F)                     | TIMSK1               | _          | _                                | _          | _                 | ICIE1                                | OCIE1B      | OCIE1A            | TOIE1        | 96       |

| (0x6E)                     | TIMSK0               | _          | _                                | _          | _                 | ICIE0                                | OCIE0B      | OCIE0A            | TOIE0        | 96       |

| (0x6D)                     | Reserved             | _          | _                                | -          | -                 | -                                    | -           | _                 | -            |          |

| (0x6C)                     | PCMSK1               |            |                                  | •          | PCIN              | IT[15:8]                             |             | •                 | •            | 60       |

| (0x6B)                     | PCMSK0               | =          | -                                | -          | -                 |                                      | PCII        | NT[3:0]           |              | 61       |

| (0x6A)                     | Reserved             | -          | _                                | -          | -                 | -                                    | -           | -                 | -            |          |

| (0x69)                     | EICRA                | ISC31      | ISC30                            | ISC21      | ISC20             | ISC11                                | ISC10       | ISC01             | ISC00        | 58       |

| (0x68)                     | PCICR                | -          | -                                | -          | -                 | -                                    | -           | PCIE1             | PCIE0        | 60       |

| (0x67)                     | Reserved             | =          | -                                | -          |                   |                                      | =           | -                 | -            |          |

| (0x66)                     | FOSCCAL              |            |                                  |            | Fast Oscillator C | alibration Registe                   |             |                   |              | 32       |

| (0x65)<br>(0x64)           | Reserved<br>PRR0     | -          | PRTWI                            | PRVRM      | -                 | PRSPI                                | PRTIM1      | PRTIM0            | PRVADC       | 40       |

| (0x64)<br>(0x63)           | Reserved             | _          | – FRIWI                          | - FRVRIVI  | _                 |                                      | - FRIIVII   | - FRIIVIO         | - FRVADC     | 40       |

| (0x62)                     | Reserved             | _          | _                                | _          | _                 | _                                    | _           | _                 | _            |          |

| (0x61)                     | CLKPR                | CLKPCE     | _                                | _          | _                 | _                                    | _           | CLKPS1            | CLKPS0       | 32       |

| (0x60)                     | WDTCSR               | WDIF       | WDIE                             | WDP3       | WDCE              | WDE                                  | WDP2        | WDP1              | WDP0         | 49       |

| 0x3F (0x5F)                | SREG                 | I          | Т                                | Н          | S                 | V                                    | N           | Z                 | С            | 10       |

| 0x3E (0x5E)                | SPH                  | SP15       | SP14                             | SP13       | SP12              | SP11                                 | SP10        | SP9               | SP8          | 13       |

| 0x3D (0x5D)                | SPL                  | SP7        | SP6                              | SP5        | SP4               | SP3                                  | SP2         | SP1               | SP0          | 13       |

| 0x3C (0x5C)                | Reserved             | _          | -                                | -          | _                 | -                                    | -           | -                 | -            |          |

| 0x3B (0x5B)                | Reserved             | _          | _                                | -          | -                 | -                                    | -           | -                 | -            |          |

| 0x3A (0x5A)                | Reserved             | _          | _                                | _          | -                 | -                                    | _           | -                 | -            |          |

| 0x39 (0x59)                | Reserved             | _          | _                                | -          | -                 | -                                    | _           | -                 | -            |          |

| 0x38 (0x58)<br>0x37 (0x57) | Reserved<br>SPMCSR   | -<br>SPMIE | -<br>RWWSB                       | -<br>SIGRD | -<br>CTPB         | -<br>RFLB                            | PGWRT       | PGERS             | -<br>SPMEN   | 202      |

| 0x36 (0x56)                | Reserved             | SPINIE -   | RWWSB                            | - SIGRD    | - CIPB            | - KFLD                               | PGWRI       | - PGERS           | SPIVIEIN –   | 202      |

| 0x35 (0x55)                | MCUCR                | _          | _                                | CKOE       | PUD               | _                                    | _           | IVSEL             | IVCE         | 78/32    |

| 0x34 (0x54)                | MCUSR                | _          | _                                | _          | OCDRF             | WDRF                                 | BODRF       | EXTRF             | PORF         | 49       |

| 0x33 (0x53)                | SMCR                 | _          | _                                | _          | -                 |                                      | SM[2:0]     | l                 | SE           | 39       |

| 0x32 (0x52)                | Reserved             | -          | -                                | -          | -                 | -                                    | -           | -                 | -            |          |

| 0x31 (0x51)                | DWDR                 |            |                                  |            | debugWIRE         | Data Register                        |             |                   |              | 187      |

| 0x30 (0x50)                | Reserved             | _          | _                                | _          | -                 | -                                    | _           | -                 | _            |          |

| 0x2F (0x4F)                | Reserved             | =          | -                                | -          | -                 | =                                    | =           | -                 | -            |          |

| 0x2E (0x4E)                | SPDR                 |            | ı                                |            |                   | a Register                           |             |                   |              | 107      |

| 0x2D (0x4D)                | SPSR                 | SPIF       | WCOL                             | -          | -<br>NOTE         | -                                    | -           | -                 | SPI2X        | 106      |

| 0x2C (0x4C)                | SPCR                 | SPIE       | SPE                              | DORD       | MSTR              | CPOL                                 | CPHA        | SPR1              | SPR0         | 105      |

| 0x2B (0x4B)                | GPIOR2               |            |                                  |            |                   | se I/O Register 2                    |             |                   |              | 24       |

| 0x2A (0x4A)<br>0x29 (0x49) | GPIOR1<br>OCR0B      |            |                                  | Ti~        |                   | se I/O Register 1<br>out Compare Reg | ister R     |                   |              | 95       |

| 0x29 (0x49)<br>0x28 (0x48) | OCR0B<br>OCR0A       |            |                                  |            | -                 | out Compare Reg                      |             |                   |              | 95<br>95 |

| 0x27 (0x47)                | TCNT0H               |            |                                  |            |                   | 0 (8 Bit) High Byte                  |             |                   |              | 95       |

| 0x26 (0x46)                | TCNT0L               |            |                                  |            |                   | 0 (8 Bit) Low Byte                   |             |                   |              | 95       |

| 0x25 (0x45)                | TCCR0B               | =          | -                                | -          | -                 | -                                    | CS02        | CS01              | CS00         | 81       |

| 0x24 (0x44)                | TCCR0A               | TCW0       | ICEN0                            | ICNC0      | ICES0             | ICS0                                 | -           | -                 | WGM00        | 94       |

| 0x23 (0x43)                | GTCCR                | TSM        | -                                | -          | -                 | =                                    | =           | -                 | PSRSYNC      |          |

| 0x22 (0x42)                | EEARH                | -          | -                                | -          | -                 | -                                    | -           | EEPRON            | /I High byte | 20       |

| 0x21 (0x41)                | EEARL                |            | EEPROM Address Register Low Byte |            |                   |                                      |             | 20                |              |          |

| 0x20 (0x40)                | EEDR                 |            | Ī                                | •          |                   | Data Register                        | i           | i                 | ,            | 20       |

| 0x1F (0x3F)                | EECR                 | -          | -                                | EEPM1      | EEPM0             | EERIE                                | EEMPE       | EEPE              | EERE         | 21       |

| 0x1E (0x3E)                | GPIOR0               |            | 1                                |            | General Purpo     | se I/O Register 0                    | INTO        | I INT             | INITO        | 24       |

| 0x1D (0x3D)                | EIMSK                | -          | _                                | _          | _                 | INT3                                 | INT2        | INT1              | INTO         | 59       |

| 0x1C (0x3C)                | EIFR                 | _          | -                                | -          | -                 | INTF3                                | INTF2       | INTF1             | INTF0        | 59       |

| Address     | Name     | Bit 7  | Bit 6  | Bit 5  | Bit 4   | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Page |

|-------------|----------|--------|--------|--------|---------|--------|--------|--------|--------|------|

| 0x1B (0x3B) | PCIFR    | -      | -      | -      | _       | -      | -      | PCIF1  | PCIF0  | 60   |

| 0x1A (0x3A) | Reserved | -      | -      | -      | _       | -      | -      | -      | -      |      |

| 0x19 (0x39) | Reserved | _      | _      | _      | _       | -      | _      | _      | _      |      |

| 0x18 (0x38) | Reserved | -      | _      | -      | -       | -      | _      | _      | _      |      |

| 0x17 (0x37) | OSICSR   | _      | _      | _      | OSISEL0 | -      | _      | OSIST  | OSIEN  | 33   |

| 0x16 (0x36) | TIFR1    | _      | _      | _      | _       | ICF1   | OCF1B  | OCF1A  | TOV1   | 96   |

| 0x15 (0x35) | TIFR0    | _      | _      | _      | _       | ICF0   | OCF0B  | OCF0A  | TOV0   | 96   |

| 0x14 (0x34) | Reserved | _      | _      | _      | _       | -      | _      | _      | -      |      |

| 0x13 (0x33) | Reserved | -      | _      | -      | -       | -      | _      | _      | _      |      |

| 0x12 (0x32) | Reserved | _      | -      | -      | _       | -      | -      | -      | _      |      |

| 0x11 (0x31) | Reserved | -      | -      | -      | _       | -      | -      | -      | -      |      |

| 0x10 (0x30) | Reserved | _      | _      | _      | _       | -      | _      | -      | _      |      |

| 0x0F (0x2F) | Reserved | _      | _      | _      | _       | -      | _      | -      | _      |      |

| 0x0E (0x2E) | Reserved | _      | _      | _      | _       | -      | _      | _      | _      |      |

| 0x0D (0x2D) | Reserved | _      | _      | _      | _       | -      | _      | -      | _      |      |

| 0x0C (0x2C) | Reserved | _      | _      | _      | _       | -      | _      | -      | _      |      |

| 0x0B (0x2B) | Reserved | _      | _      | _      | _       | -      | _      | -      | _      |      |

| 0x0A (0x2A) | Reserved | _      | _      | _      | _       | -      | _      | -      | _      |      |

| 0x09 (0x29) | Reserved | _      | -      | -      | _       | -      | -      | -      | _      |      |

| 0x08 (0x28) | PORTC    | -      | -      | PORTC5 | PORTC4  | PORTC3 | PORTC2 | PORTC1 | PORTC0 | 66   |

| 0x07 (0x27) | Reserved | _      | _      | _      | _       | -      | _      | -      | _      |      |

| 0x06 (0x26) | PINC     | _      | -      | -      | PINC4   | PINC3  | PINC2  | PINC1  | PINC0  | 66   |

| 0x05 (0x25) | PORTB    | PORTB7 | PORTB6 | PORTB5 | PORTB4  | PORTB3 | PORTB2 | PORTB1 | PORTB0 | 78   |

| 0x04 (0x24) | DDRB     | DDB7   | DDB6   | DDB5   | DDB4    | DDB3   | DDB2   | DDB1   | DDB0   | 78   |

| 0x03 (0x23) | PINB     | PINB7  | PINB6  | PINB5  | PINB4   | PINB3  | PINB2  | PINB1  | PINB0  | 78   |

| 0x02 (0x22) | PORTA    | -      | -      | -      | -       | PORTA3 | PORTA2 | PORTA1 | PORTA0 | 78   |

| 0x01 (0x21) | DDRA     | _      | _      | -      | _       | DDA3   | DDA2   | DDA1   | DDA0   | 78   |

| 0x00 (0x20) | PINA     | _      | _      | _      | _       | PINA3  | PINA2  | PINA1  | PINA0  | 78   |

Notes:

- 1. For compatibility with future devices, reserved bits should be written to zero if accessed. Reserved I/O memory addresses should never be written.

- 2. I/O registers within the address range \$00 \$1F are directly bit-accessible using the SBI and CBI instructions. In these registers, the value of single bits can be checked by using the SBIS and SBIC instructions.

- 3. Some of the status flags are cleared by writing a logical one to them. Note that the CBI and SBI instructions will operate on all bits in the I/O register, writing a one back into any flag read as set, thus clearing the flag. The CBI and SBI instructions work with registers 0x00 to 0x1F only.

- 4. When using the I/O specific commands IN and OUT, the I/O addresses \$00 \$3F must be used. When addressing I/O registers as data space using LD and ST instructions, \$20 must be added to these addresses. The Atmel ATmega16HVB/32HVB is a complex microcontroller with more peripheral units than can be supported within the 64 location reserved in Opcode for the IN and OUT instructions. For the Extended I/O space from \$60 \$FF in SRAM, only the ST/STS/STD and LD/LDS/LDD instructions can be used.

## 8. Instruction set summary

| Mnemonics      | Operands           | Description                                                            | Operation                                                                                                  | Flags                 | #Clocks    |

|----------------|--------------------|------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|-----------------------|------------|

|                | LOGIC INSTRUCTIONS | ·                                                                      | 1,1                                                                                                        |                       |            |

| ADD            | Rd, Rr             | Add two Registers                                                      | $Rd \leftarrow Rd + Rr$                                                                                    | Z, C, N, V, H         | 1          |

| ADC            | Rd, Rr             | Add with Carry two Registers                                           | $Rd \leftarrow Rd + Rr + C$                                                                                | Z, C, N, V, H         | 1          |

| ADIW           | Rdl, K             | Add Immediate to Word                                                  | Rdh:Rdl ← Rdh:Rdl + K                                                                                      | Z, C, N, V, S         | 2          |

| SUB            | Rd, Rr             | Subtract two Registers                                                 | Rd ← Rd - Rr                                                                                               | Z, C, N, V, H         | 1          |

| SUBI           | Rd, K              | Subtract Constant from Register                                        | Rd ← Rd - K                                                                                                | Z, C, N, V, H         | 1          |

| SBC            | Rd, Rr             | Subtract with Carry two Registers                                      | $Rd \leftarrow Rd - Rr - C$                                                                                | Z, C, N, V, H         | 1          |

| SBCI           | Rd, K              | Subtract with Carry Constant from Reg.                                 | $Rd \leftarrow Rd - K - C$                                                                                 | Z, C, N, V, H         | 1          |

| SBIW           | Rdl,K              | Subtract Immediate from Word                                           | Rdh:Rdl ← Rdh:Rdl - K                                                                                      | Z, C, N, V, S         | 2          |

| AND            | Rd, Rr             | Logical AND Registers                                                  | $Rd \leftarrow Rd \bullet Rr$                                                                              | Z, N, V               | 1          |

| ANDI           | Rd, K              | Logical AND Register and Constant                                      | $Rd \leftarrow Rd \bullet K$                                                                               | Z, N, V               | 1          |

| OR             | Rd, Rr             | Logical OR Registers                                                   | $Rd \leftarrow Rd v Rr$                                                                                    | Z, N, V               | 1          |

| ORI            | Rd, K              | Logical OR Register and Constant                                       | $Rd \leftarrow Rd \vee K$                                                                                  | Z, N, V               | 1          |

| EOR            | Rd, Rr             | Exclusive OR Registers                                                 | $Rd \leftarrow Rd \oplus Rr$                                                                               | Z, N, V               | 1          |

| COM            | Rd                 | One's Complement                                                       | Rd ← 0xFF – Rd                                                                                             | Z, C, N, V            | 1          |

| NEG            | Rd                 | Two's Complement                                                       | Rd ← 0x00 – Rd                                                                                             | Z, C, N, V, H         | 1          |

| SBR            | Rd, K              | Set Bit(s) in Register                                                 | Rd ← Rd v K                                                                                                | Z, N, V               | 1          |

| CBR            | Rd, K              | Clear Bit(s) in Register                                               | $Rd \leftarrow Rd \bullet (0xFF - K)$                                                                      | Z, N, V               | 1          |

| INC<br>DEC     | Rd<br>Rd           | Increment  Decrement                                                   | $Rd \leftarrow Rd + 1$ $Rd \leftarrow Rd - 1$                                                              | Z, N, V<br>Z, N, V    | 1          |

| TST            | Rd                 | Test for Zero or Minus                                                 | $Rd \leftarrow Rd \bullet Rd$ $Rd \leftarrow Rd \bullet Rd$                                                | Z, N, V               | 1          |

| CLR            | Rd                 | Clear Register                                                         | $Rd \leftarrow Rd \oplus Rd$<br>$Rd \leftarrow Rd \oplus Rd$                                               | Z, N, V               | 1          |

| SER            | Rd                 | Set Register                                                           | Rd ← 0xFF                                                                                                  | None                  | 1          |

| MUL            | Rd, Rr             | Multiply Unsigned                                                      | R1:R0 ← Rd x Rr                                                                                            | Z, C                  | 2          |

| MULS           | Rd, Rr             | Multiply Signed                                                        | R1:R0 ← Rd x Rr                                                                                            | Z, C                  | 2          |

| MULSU          | Rd, Rr             | Multiply Signed with Unsigned                                          | R1:R0 ← Rd x Rr                                                                                            | Z, C                  | 2          |

| FMUL           | Rd, Rr             | Fractional Multiply Unsigned                                           | R1:R0 ← (Rd x Rr) << 1                                                                                     | Z, C                  | 2          |

| FMULS          | Rd, Rr             | Fractional Multiply Signed                                             | R1:R0 ← (Rd x Rr) << 1                                                                                     | Z, C                  | 2          |

| FMULSU         | Rd, Rr             | Fractional Multiply Signed with Unsigned                               | $R1:R0 \leftarrow (Rd \times Rr) \ll 1$                                                                    | Z, C                  | 2          |

| BRANCH INSTRUC | TIONS              |                                                                        |                                                                                                            |                       |            |

| RJMP           | k                  | Relative Jump                                                          | PC ← PC + k + 1                                                                                            | None                  | 2          |

| IJMP           |                    | Indirect Jump to (Z)                                                   | PC ← Z                                                                                                     | None                  | 2          |

| JMP            | k                  | Direct Jump                                                            | PC ← k                                                                                                     | None                  | 3          |

| RCALL          | k                  | Relative Subroutine Call                                               | PC ← PC + k + 1                                                                                            | None                  | 3          |

| ICALL          |                    | Indirect Call to (Z)                                                   | PC ← Z                                                                                                     | None                  | 3          |

| CALL           | k                  | Direct Subroutine Call                                                 | PC ← k                                                                                                     | None                  | 4          |

| RET            |                    | Subroutine Return                                                      | PC ← STACK                                                                                                 | None                  | 4          |

| RETI           |                    | Interrupt Return                                                       | PC ← STACK                                                                                                 | I                     | 4          |

| CPSE           | Rd, Rr             | Compare, Skip if Equal                                                 | if (Rd = Rr) PC ← PC + 2 or 3                                                                              | None                  | 1/2/3      |

| CP             | Rd, Rr             | Compare                                                                | Rd – Rr                                                                                                    | Z, N, V, C, H         | 1          |

| CPC            | Rd, Rr             | Compare with Carry                                                     | Rd – Rr – C                                                                                                | Z, N, V, C, H         | 1          |

| CPI<br>SBRC    | Rd, K<br>Rr, b     | Compare Register with Immediate                                        | Rd – K<br>if $(Rr(b) = 0) PC \leftarrow PC + 2 \text{ or } 3$                                              | Z, N, V, C, H<br>None | 1/2/3      |

| SBRS           | Rr, b              | Skip if Bit in Register Cleared Skip if Bit in Register is Set         | if $(RI(b) = 0) PC \leftarrow PC + 2 \text{ or } 3$<br>if $(Rr(b) = 1) PC \leftarrow PC + 2 \text{ or } 3$ | None                  | 1/2/3      |

| SBIC           | P, b               | Skip if Bit in I/O Register Cleared                                    | if $(P(b) = 0) PC \leftarrow PC + 2 \text{ or } 3$                                                         | None                  | 1/2/3      |

| SBIS           | P, b               | Skip if Bit in I/O Register cleared Skip if Bit in I/O Register is Set | if $(P(b) = 1) PC \leftarrow PC + 2 \text{ or } 3$                                                         | None                  | 1/2/3      |

| BRBS           | s, k               | Branch if Status Flag Set                                              | if (SREG(s) = 1) then PC←PC+k + 1                                                                          | None                  | 1/2        |

| BRBC           | s, k               | Branch if Status Flag Cleared                                          | if (SREG(s) = 0) then PC←PC+k + 1                                                                          | None                  | 1/2        |

| BREQ           | k                  | Branch if Equal                                                        | if (Z = 1) then PC ← PC + k + 1                                                                            | None                  | 1/2        |

| BRNE           | k                  | Branch if Not Equal                                                    | if $(Z = 0)$ then $PC \leftarrow PC + k + 1$                                                               | None                  | 1/2        |

| BRCS           | k                  | Branch if Carry Set                                                    | if (C = 1) then PC ← PC + k + 1                                                                            | None                  | 1/2        |

| BRCC           | k                  | Branch if Carry Cleared                                                | if (C = 0) then PC ← PC + k + 1                                                                            | None                  | 1/2        |

| BRSH           | k                  | Branch if Same or Higher                                               | if (C = 0) then PC $\leftarrow$ PC + k + 1                                                                 | None                  | 1/2        |

| BRLO           | k                  | Branch if Lower                                                        | if (C = 1) then PC $\leftarrow$ PC + k + 1                                                                 | None                  | 1/2        |

| BRMI           | k                  | Branch if Minus                                                        | if (N = 1) then PC $\leftarrow$ PC + k + 1                                                                 | None                  | 1/2        |

| BRPL           | k                  | Branch if Plus                                                         | if (N = 0) then PC $\leftarrow$ PC + k + 1                                                                 | None                  | 1/2        |

| BRGE           | k                  | Branch if Greater or Equal, Signed                                     | if (N $\oplus$ V= 0) then PC $\leftarrow$ PC + k + 1                                                       | None                  | 1/2        |

| BRLT           | k                  | Branch if Less Than Zero, Signed                                       | if (N $\oplus$ V= 1) then PC $\leftarrow$ PC + k + 1                                                       | None                  | 1/2        |

| BRHS           | k                  | Branch if Half Carry Flag Set                                          | if (H = 1) then PC ← PC + k + 1                                                                            | None                  | 1/2        |

| BRHC           | k                  | Branch if Half Carry Flag Cleared                                      | if (H = 0) then PC ← PC + k + 1                                                                            | None                  | 1/2        |

| BRTS           | k                  | Branch if T Flag Set                                                   | if (T = 1) then PC $\leftarrow$ PC + k + 1                                                                 | None                  | 1/2        |

| BRTC           | k                  | Branch if T Flag Cleared                                               | if (T = 0) then PC ← PC + k + 1                                                                            | None                  | 1/2        |

|                |                    |                                                                        |                                                                                                            |                       |            |

| BRVS<br>BRVC   | k<br>k             | Branch if Overflow Flag is Set  Branch if Overflow Flag is Cleared     | if $(V = 1)$ then $PC \leftarrow PC + k + 1$<br>if $(V = 0)$ then $PC \leftarrow PC + k + 1$               | None<br>None          | 1/2<br>1/2 |

## 8. Instruction set summary (Continued)

| Mnemonics          | Operands       | Description                                               | Operation                                                                         | Flags        | #Clocks     |

|--------------------|----------------|-----------------------------------------------------------|-----------------------------------------------------------------------------------|--------------|-------------|

| BRIE               | k              | Branch if Interrupt Enabled                               | if ( I = 1) then PC ← PC + k + 1                                                  | None         | 1/2         |

| BRID               | k              | Branch if Interrupt Disabled                              | if ( I = 0) then PC ← PC + k + 1                                                  | None         | 1/2         |

| BIT AND BIT-TEST I | INSTRUCTIONS   |                                                           |                                                                                   |              |             |

| SBI                | P, b           | Set Bit in I/O Register                                   | I/O(P,b) ← 1                                                                      | None         | 2           |

| CBI                | P, b           | Clear Bit in I/O Register                                 | $I/O(P,b) \leftarrow 0$                                                           | None         | 2           |

| LSL                | Rd             | Logical Shift Left                                        | $Rd(n+1) \leftarrow Rd(n), Rd(0) \leftarrow 0$                                    | Z, C, N, V   | 1           |

| LSR                | Rd             | Logical Shift Right                                       | $Rd(n) \leftarrow Rd(n+1), Rd(7) \leftarrow 0$                                    | Z, C, N, V   | 1           |

| ROL                | Rd             | Rotate Left Through Carry                                 | $Rd(0)\leftarrow C,Rd(n+1)\leftarrow Rd(n),C\leftarrow Rd(7)$                     | Z, C, N, V   | 1           |

| ROR                | Rd             | Rotate Right Through Carry                                | $Rd(7) \leftarrow C, Rd(n) \leftarrow Rd(n+1), C \leftarrow Rd(0)$                | Z, C, N, V   | 1           |

| ASR                | Rd             | Arithmetic Shift Right                                    | $Rd(n) \leftarrow Rd(n+1), n=06$                                                  | Z, C, N, V   | 1           |

| SWAP               | Rd             | Swap Nibbles                                              | Rd(30)←Rd(74),Rd(74)←Rd(30)                                                       | None         | 1           |

| BSET               | S              | Flag Set Flag Clear                                       | SREG(s) ← 1                                                                       | SREG(s)      | 1           |

| BCLR               | S              | 9                                                         | $SREG(s) \leftarrow 0$                                                            | SREG(s)      | 1           |

| BST<br>BLD         | Rr, b<br>Rd, b | Bit Store from Register to T  Bit load from T to Register | $T \leftarrow Rr(b)$ $Rd(b) \leftarrow T$                                         | None         | 1           |

| SEC                | ixu, b         | Set Carry                                                 | C ← 1                                                                             | C            | 1           |

| CLC                |                | Clear Carry                                               | C ← 0                                                                             | C            | 1           |

| SEN                |                | Set Negative Flag                                         | N ← 1                                                                             | N            | 1           |

| CLN                |                | Clear Negative Flag                                       | N ← 0                                                                             | N            | 1           |

| SEZ                |                | Set Zero Flag                                             | Z ← 1                                                                             | Z            | 1           |

| CLZ                |                | Clear Zero Flag                                           | Z ← 0                                                                             | Z            | 1           |

| SEI                |                | Global Interrupt Enable                                   | I ← 1                                                                             | 1            | 1           |

| CLI                |                | Global Interrupt Disable                                  | 1←0                                                                               | 1            | 1           |

| SES                |                | Set Signed Test Flag                                      | S ← 1                                                                             | S            | 1           |

| CLS                |                | Clear Signed Test Flag                                    | S ← 0                                                                             | S            | 1           |

| SEV                |                | Set Twos Complement Overflow.                             | V ← 1                                                                             | V            | 1           |

| CLV                |                | Clear Twos Complement Overflow                            | V ← 0                                                                             | V            | 1           |

| SET                |                | Set T in SREG                                             | T ← 1                                                                             | T            | 1           |

| CLT                |                | Clear T in SREG                                           | T ← 0                                                                             | Т            | 1           |

| SEH                |                | Set Half Carry Flag in SREG                               | H ← 1                                                                             | Н            | 1           |

| CLH                |                | Clear Half Carry Flag in SREG                             | H ← 0                                                                             | Н            | 1           |

| DATA TRANSFER II   |                | T.,                                                       | T., .                                                                             | T.,          | <del></del> |

| MOV                | Rd, Rr         | Move Between Registers                                    | Rd ← Rr                                                                           | None         | 1           |

| MOVW               | Rd, Rr         | Copy Register Word                                        | Rd+1:Rd ← Rr+1:Rr                                                                 | None         | 1 1         |

| LDI<br>LD          | Rd, K<br>Rd, X | Load Immediate  Load Indirect                             | $Rd \leftarrow K$ $Rd \leftarrow (X)$                                             | None<br>None | 2           |

| LD                 | Rd, X+         | Load Indirect Load Indirect and Post-Inc.                 | $Rd \leftarrow (X), X \leftarrow X + 1$                                           | None         | 2           |

| LD                 | Rd, - X        | Load Indirect and Pre-Dec.                                | $X \leftarrow (X), X \leftarrow X + 1$<br>$X \leftarrow X - 1, Rd \leftarrow (X)$ | None         | 2           |

| LD                 | Rd, Y          | Load Indirect  Load Indirect                              | $Rd \leftarrow (Y)$                                                               | None         | 2           |

| LD                 | Rd, Y+         | Load Indirect and Post-Inc.                               | $Rd \leftarrow (Y), Y \leftarrow Y + 1$                                           | None         | 2           |