December 2008

# SG6510X1 — PC Power Supply Supervisors

## **Features**

- Over-Voltage Protection (OVP) for 3.3V, 5V, 12V

- Under-Voltage Sense (UVS) and Under-Voltage Protection (UVP) for 3.3V, 5V

- Open-Drain Output for PGO and FPO Pins

- 300ms Power-Good Delay

- 75ms Turn-on Delay for 3.3V and 5V

- 2.8ms PSON Control to FPO Turn-off Delay

- 38ms /38ms PSON Control Debounce

- 350µs Width Noise Deglitches

- 2ms UVP Debounce Time

- 1ms UVS Debounce Time

- No Lockup During the Fast AC Power On/Off

- Brownout Protection Function for 3.3V and 5V

- Wide Supply Voltage Range from 4V to 15V

## **Description**

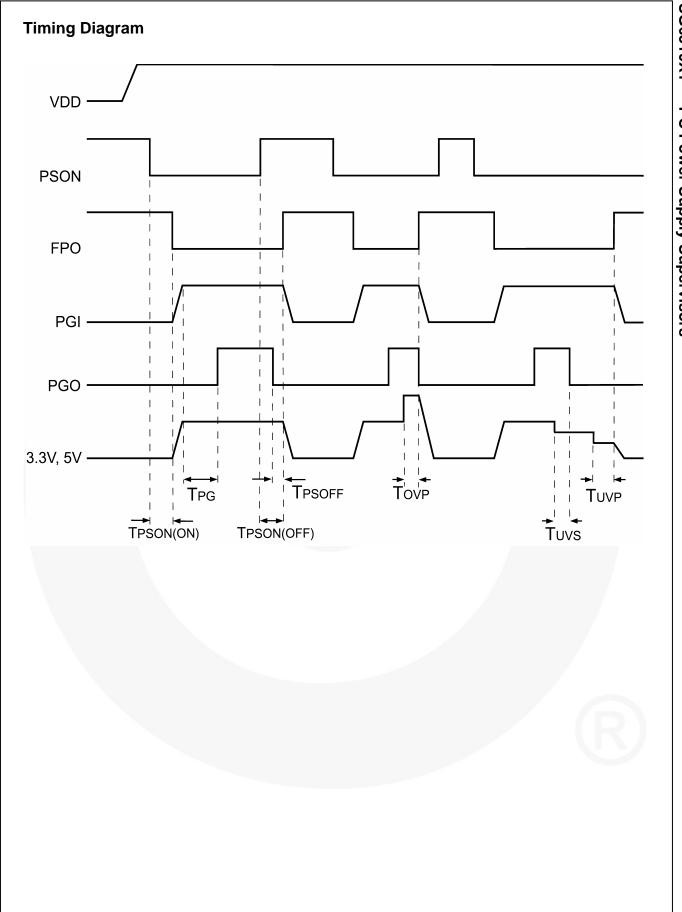

SG6510 is designed to provide the voltage supervisor function, remote on/off PSON function, power-good (PGO) indicator function, and fault protection (FPO) function for switching power systems.

For the supervisor function, it provides the over-voltage protection (OVP) monitoring for 3.3V, 5V, and 12V (12V via VDD pin); under-voltage sense (UVS) monitoring for 3.3V and 5V; and under-voltage protection (UVP) monitoring for 3.3V and 5V. When 3.3V or 5V voltage is decreasing to 2.8V and 4.2V, respectively, the undervoltage sense (UVS) function is enabled to reset the PGO signal from high to low. If 3.3V or 5V voltage is further decreasing to 2.5V and 3.6V, respectively, FPO is set high to turn off the PWM controller IC. To achieve better immunity for lighting surge glitch and to prevent accidental power shut down during dynamic loading condition, the debounce time for UVP and UVS is 2ms/1ms, respectively. The deglitch time for OVP is 75µs for better noise immunity. During an AC sag or brownout situation, UVP functions can still be enabled to protect power supply in case of output short circuit.

The power supply is turned on after 38ms debounce time when the PSON signal is set from high to low. To turn off the power supply, the PSON signal is set from low to high and the debounce time is 38ms. The PGI circuitry provides a sufficient power-down warning signal for PGO. When PGI input is lower than the internal 1.2V reference voltage, after 350µs debounce time, the PGO signal is pulled low.

## **Ordering Information**

| Part Number | Operating Temperature Range | Package | <b>Eco Status</b> | Packing Method |

|-------------|-----------------------------|---------|-------------------|----------------|

| SG6510DY1   | -40°C to +125°C             | DIP-8   | Green             | Tube           |

| SG6510DZ1   | -40°C to +125°C             | DIP-8   | RoHS              | Tube           |

| SG6510SZ1   | -40°C to +125°C             | SOP-8   | RoHS              | Tape & Reel    |

| SG6510SY1   | -40°C to +125°C             | SOP-8   | Green             | Tape & Reel    |

For Fairchild's definition of "green" please visit: <a href="http://www.fairchildsemi.com/company/green/rohs\_green.html">http://www.fairchildsemi.com/company/green/rohs\_green.html</a>.

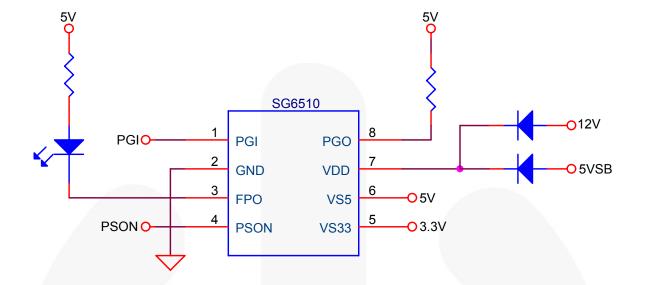

# **Application Diagram**

Figure 1. Typical Application

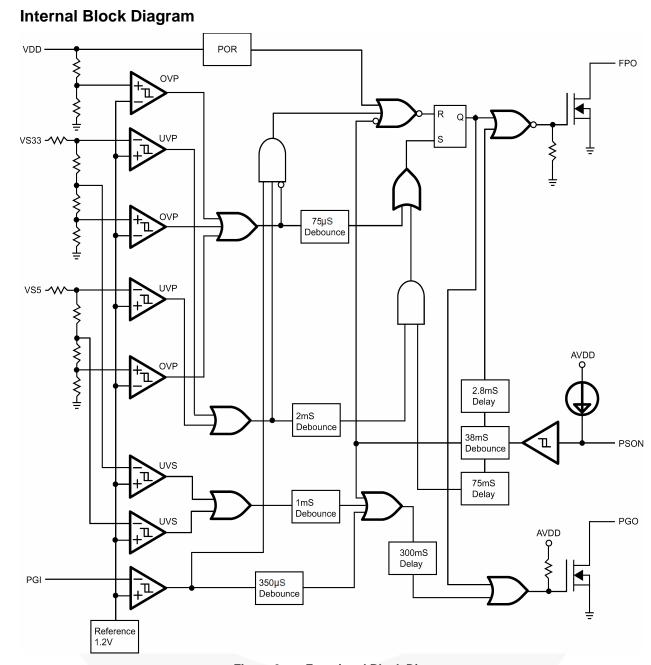

Figure 2. Functional Block Diagram

# **Marking Information**

P: Z = Lead Free

Null = regular package

XXXXXXX: Wafer Lot

YY: Year; WW: Week

V: Assembly Location

\*\* Marking for SG6510DZ1 (Pb-free) SG6510SZ1 (Pb-free)

1'st line

Z: Assembly plant code

X: Year code

Y: Week code

TT: Die run code

3'rd line

T: Package type (D = DIP, S=SOP)

P: Y=Green package

M: Manufacture flow code

Marking for SG6510DY1 (Green-compound) SG6510SY1 (Green-compound)

Figure 3. Top Mark

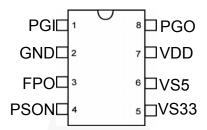

# **Pin Configurations**

Figure 4. Pin Configuration

# **Pin Definitions**

| Pin # | Name | Туре         | Description                                                                                                                                                                                       |

|-------|------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | PGI  | Analog Input | Power-good input. For ATX SMPS, it detects main AC voltage undervoltage and/or failure.                                                                                                           |

| 2     | GND  | Supply       | Ground.                                                                                                                                                                                           |

| 3     | FPO  | Logic Output | Fault protection output (invert). Output signal to control the PWM IC. For example, it controls the PWM IC of primary side through an optocoupler. When FPO is low, the main SMPS is operational. |

| 4     | PSON | Logic Input  | Remote on/off logic input from CPU or main-board. Turn on/off the PWM output after a 38ms delay.                                                                                                  |

| 5     | VS33 | Analog Input | 3.3 V over/under-voltage control sense input.                                                                                                                                                     |

| 6     | VS5  | Analog Input | 5 V over/under-voltage control sense input.                                                                                                                                                       |

| 7     | VDD  | Supply       | Supply voltage; 4V ~ 15V. For ATX SMPS, it is connected to 5V-standby and 12V through diodes, respectively.                                                                                       |

| 8     | PGO  | Logic Output | Power-good logic output, 0 or 1(open-drain). Power good = 1 means that the power is good for operation. The power-good delay is 300ms.                                                            |

# **Function Table**

| PGI      | PSON | UV Sense<br>(3.3V or 5V) | UV Protection<br>(3.3V or 5V) | OV Protection | FPO | PGO |

|----------|------|--------------------------|-------------------------------|---------------|-----|-----|

| PGI<1.2V | L    | No                       | No                            | No            | L   | L   |

| PGI<1.2V | L    | Yes                      | No                            | No            | ٦   | L   |

| PGI<1.2V | L    | No                       | Yes                           | No            | L   | L   |

| PGI<1.2V | L    | No                       | No                            | Yes           | Н   | L   |

| PGI<1.2V | L    | Yes                      | Yes                           | No            | ٦   | L   |

| PGI<1.2V | L    | Yes                      | No                            | Yes           | Н   | L   |

| PGI<1.2V | L    | No                       | Yes                           | Yes           | Н   | L   |

| PGI<1.2V | L    | Yes                      | Yes                           | Yes           | Н   | L   |

| PGI>1.2V | L    | No                       | No                            | No            | L   | Н   |

| PGI>1.2V | L    | Yes                      | No                            | No            | Г   | L   |

| PGI>1.2V | L    | No                       | Yes                           | No            | Н   | L   |

| PGI>1.2V | L    | No                       | No                            | Yes           | Н   | L   |

| PGI>1.2V | L    | Yes                      | Yes                           | No            | Н   | L   |

| PGI>1.2V | L    | Yes                      | No                            | Yes           | Н   | L   |

| PGI>1.2V | L    | No                       | Yes                           | Yes           | Н   | L   |

| PGI>1.2V | L    | Yes                      | Yes                           | Yes           | Н   | L   |

| X        | Н    | X                        | X                             | Х             | Н   | L   |

X = Don't care

FPO = L means: fault IS NOT latched FPO = H means: fault IS latched

PGO = L means: fault

PGO = H means: No fault

# **Absolute Maximum Ratings**

Stresses exceeding the absolute maximum ratings may damage the device. The device may not function or be operable above the recommended operating conditions and stressing the parts to these levels is not recommended. In addition, extended exposure to stresses above the recommended operating conditions may affect device reliability. The absolute maximum ratings are stress ratings only.

| Symbol           | Parameter                            | Min.             | Max. | Unit |    |

|------------------|--------------------------------------|------------------|------|------|----|

| V <sub>DD</sub>  | DC Supply Voltage                    |                  | -0.3 | 16   | V  |

| Vi               | Input Voltage PSON, VS33, VS5, PGI   |                  | -0.3 | 8.0  | V  |

| V <sub>out</sub> | Output Voltage                       | FPO              | -0.3 | 16   | ٧  |

| VOUT             | Output voltage                       | PGO              | -0.3 | 8.0  | V  |

| TA               | Operating Free Air Temperature Range |                  | -40  | +85  | °C |

| T <sub>STG</sub> | Storage Temperature Range            |                  | -55  | +150 | °C |

| TL               | Soldering Temperature                |                  |      | +260 | °C |

| ESD              | Electrostatic Discharge Capability   | Human Body Model |      | 2    | KV |

## Note:

1. Stresses above those listed may cause permanent damage to the device.

# **Recommended Operating Conditions**

| Symbol             | Parameter                                 |                      | Min. | Max. | Unit |  |

|--------------------|-------------------------------------------|----------------------|------|------|------|--|

| $V_{DD}$           | DC Supply Voltage                         |                      | 4    | 15   | V    |  |

| V <sub>IL</sub>    | Input Voltage                             | PSON, VS33, VS5, PGI |      | 7    | V    |  |

| \/                 | Output Voltage                            | FPO                  |      | 15   | V    |  |

| V <sub>OUT</sub>   | Output Voltage                            | PGO                  |      | 7    |      |  |

| 1                  | Output Sink Current                       | FPO                  |      | 20   | mΛ   |  |

| I <sub>oSINK</sub> |                                           | PGO                  |      | 10   | mA   |  |

| T <sub>R</sub>     | Supply Voltage Rising Time <sup>(2)</sup> |                      | 1    |      | ms   |  |

| T <sub>A</sub>     | Operating Free Air Temperature Range      |                      | -30  | 85   | °C   |  |

### Note:

2.  $V_{DD}$  rising and falling slew rate must be less than 14V/ms.

## **Electrical Characteristics**

Unless otherwise noted,  $V_{DD}$ =12V and  $T_A$ =25°C.

| Symbol                | Parameter Conditions                    |                                 | Min. | Тур. | Max. | Units |  |

|-----------------------|-----------------------------------------|---------------------------------|------|------|------|-------|--|

| Over-Vol              | tage Protection                         |                                 |      |      |      |       |  |

|                       | Over-Voltage Protection VS33            |                                 | 3.7  | 3.9  | 4.1  | V     |  |

| $V_{OVP}$             | Over-Voltage Protection VS5             | 4                               | 5.7  | 6.1  | 6.5  |       |  |

|                       | Over-Voltage Protection V <sub>DD</sub> |                                 | 13.2 | 13.8 | 14.4 |       |  |

| I <sub>LKG</sub>      | Leakage Current (FPO)                   | V <sub>FPO</sub> = 5V           |      |      | 5    | μΑ    |  |

| V <sub>OL</sub>       | Low-Level Output Voltage (FPO)          | I <sub>sink</sub> 20mA          |      |      | 0.7  | V     |  |

| t <sub>D-VDDOVP</sub> | Timing, OVP to Protection               |                                 | 33   | 75   | 110  | ms    |  |

| Under-Vo              | oltage and PGI, PGO                     |                                 |      |      |      |       |  |

| $V_{PGI}$             | Input Threshold Voltage PGI             |                                 | 1.15 | 1.20 | 1.25 | V     |  |

| \/                    | Under-Voltage Sense VS33                |                                 | 2.6  | 2.8  | 3.0  | V     |  |

| V <sub>UVS</sub>      | Under-Voltage Sense VS5                 |                                 | 4.0  | 4.2  | 4.4  | 1 V   |  |

| \/                    | Under-Voltage Protection VS33           |                                 | 2.3  | 2.5  | 2.7  | V     |  |

| $V_{UVP}$             | Under-Voltage Protection VS5            |                                 | 3.4  | 3.6  | 3.8  |       |  |

| tuvs                  | Timing UVS to Sense (PG)                |                                 | 0.6  | 1.0  | 1.5  | ms    |  |

| t <sub>UVP</sub>      | Timing UVP to Protection (FPO)          |                                 | 1.3  | 2.0  | 3.0  | ms    |  |

| I <sub>LKG</sub>      | Leakage Current (PGO)                   | PGO = 5V                        |      |      | 5    | μA    |  |

| $V_{OL}$              | Low-Level Output Voltage (PGO)          | $V_{DD}$ = 12V, $I_{SINK}$ 10mA |      |      | 0.7  | V     |  |

| t <sub>UVE</sub>      | Under-Voltage Enable Delay Time         |                                 | 49   | 75   | 114  | ms    |  |

| t                     | Timing PG Delay                         | PGI to PGO                      | 200  | 300  | 450  | ms    |  |

| t <sub>PG</sub>       | Noise Deglitch Time                     | PGI to PGO                      | 200  | 350  | 450  | μs    |  |

| PSON Co               | ontrol                                  |                                 |      |      |      |       |  |

| I <sub>PSON</sub>     | Input Pull-up Current                   | PSON = 0V                       | 100  | 160  | 220  | μΑ    |  |

| $V_{IH}$              | High-Level Input Voltage                |                                 | 2.40 | 1.85 |      | V     |  |

| $V_{IL}$              | Low-Level Input Voltage                 |                                 |      | 1.35 | 1.2  | V     |  |

|                       | Timing DCON to On/Off                   | On                              | 24   | 38   | 57   | /     |  |

| tpson                 | Timing, PSON to On/Off                  | Off                             | 24   | 38   | 57   | ms    |  |

| t <sub>PSOFF</sub>    | Timing PG Low to Power Off              |                                 | 1.6  | 2.8  | 4.5  | ms    |  |

| Total Dev             | vice                                    |                                 |      |      |      |       |  |

| I <sub>DD</sub>       | Supply Current                          | PSON = 5V/V <sub>DD</sub> = 5V  |      | 0.7  | 1.5  | mA    |  |

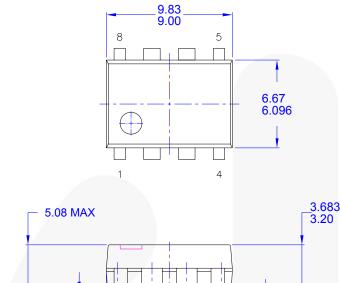

# **Physical Dimensions**

0.33 MIN

(0.56)

2.54

0.56

0.56

0.355

1.65

1.27

NOTES: UNLESS OTHERWISE SPECIFIED

- A) THIS PACKAGE CONFORMS TO JEDEC MS-001 VARIATION BA

- B) ALL DIMENSIONS ARE IN MILLIMETERS.

- C) DIMENSIONS ARE EXCLUSIVE OF BURRS, MOLD FLASH, AND TIE BAR EXTRUSIONS.

- D) DIMENSIONS AND TOLERANCES PER ASME Y14.5M-1994

- E) DRAWING FILENAME AND REVSION: MKT-N08FREV2.

Figure 5. 8-Pin, DIP-8 Package

Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or obtain the most recent revision. Package specifications do not expand the terms of Fairchild's worldwide terms and conditions, specifically the warranty therein, which covers Fairchild products.

Always visit Fairchild Semiconductor's online packaging area for the most recent package drawings: http://www.fairchildsemi.com/packaging/.

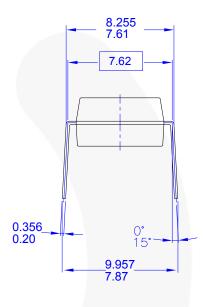

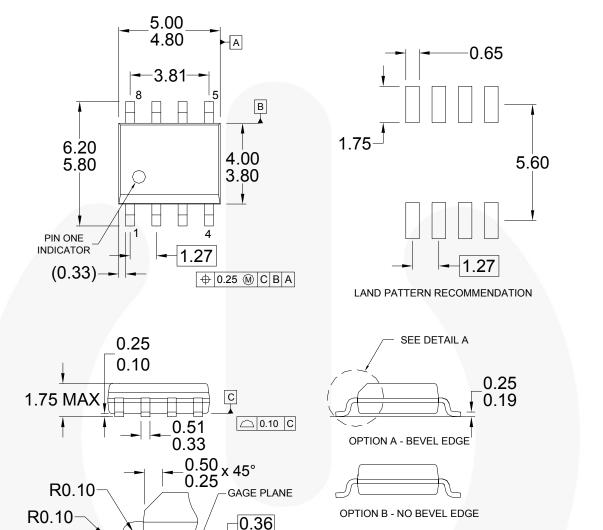

# Physical Dimensions (Continued)

## NOTES: UNLESS OTHERWISE SPECIFIED

- A) THIS PACKAGE CONFORMS TO JEDEC MS-012, VARIATION AA, ISSUE C,

- B) ALL DIMENSIONS ARE IN MILLIMETERS.

- C) DIMENSIONS DO NOT INCLUDE MOLD FLASH OR BURRS.

- D) LANDPATTERN STANDARD: SOIC127P600X175-8M.

- E) DRAWING FILENAME: M08AREV13

Figure 6. 8-Pin SOP Package

Package drawings are provided as a service to customers considering Fairchild components. Drawings may change in any manner without notice. Please note the revision and/or date on the drawing and contact a Fairchild Semiconductor representative to verify or obtain the most recent revision. Package specifications do not expand the terms of Fairchild's worldwide terms and conditions, specifically the warranty therein, which covers Fairchild products.

Always visit Fairchild Semiconductor's online packaging area for the most recent package drawings: <a href="http://www.fairchildsemi.com/packaging/">http://www.fairchildsemi.com/packaging/</a>.

SEATING PLANE

(1.04)

**DETAIL A**

8°<u>/</u>0°\

0.90

0.406

#### TRADEMARKS

The following includes registered and unregistered trademarks and service marks, owned by Fairchild Semiconductor and/or its global subsidiaries, and is not intended to be an exhaustive list of all such trademarks.

Build it Now™ CorePLUS™ CorePOWER™ CROSSVOLT™ CTL TM

Current Transfer Logic™ EcoSPARK<sup>6</sup> EfficentMa×™ EZSWITCH™ \*

Fairchild® Fairchild Semiconductor®

FACT Quiet Series™ FACT FAST® Fast∨Core™

FlashWriter® **FPSTM** E-PEST

Global Power Resource<sup>sм</sup> Green FPS™ Green FPS™ e-Series™

GTO™ IntelliMAX™ ISOPLANAR™ MegaBuck™ MIČROCOUPLER™ MicroFET™

MicroPak™ MillerDrive™ MotionMa×™ Motion-SPM™ OPTOLOGIC® OPTOPLANAR®

PDP SPM™ Power-SPM™ PowerTrench® PowerXS™

Programmable Active Droop™ **OFET**

QSTM Quiet Series™ RapidConfigure™

SYSTEM 6

The Power Franchise<sup>®</sup>

Saving our world, 1mW/W/kW at a time™

SmartMax™ SMART START™ SPM® STEALTH™ SuperFET\*\* SuperSOT\*\*-3 SuperSOT\*\*6 SuperSOT\*\*-8 SupreMOS™ SyncFET™

wer TinyBoost™ TinýBuck™ TinyLogic® TINYOPTO\*\* TinyPower™ TinyPWM™ TinyWire™ μSerDes™ ₩ SerDes UHC®

Ultra FRFET™ UniFET™  $VCX^{TM}$ VisualMax™ XSTM

\* EZSWTCH™ and FlashWriter® are trademarks of System General Corporation, used under license by Fairchild Semiconductor

#### DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION, OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS. THESE SPECIFICATIONS DO NOT EXPAND THE TERMS OF FAIRCHILD'S WORLDWIDE TERMS AND CONDITIONS, SPECIFICALLY THE WARRANTY THEREIN, WHICH COVERS THESE PRODUCTS.

## LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF FAIRCHILD SEMICONDUCTOR CORPORATION.

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user.

- 2. A critical component in any component of a life support, device, or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness

## ANTI-COUNTERFEITING POLICY

Fairchild Semiconductor Corporation's Anti-Counterfeiting Policy. Fairchild's Anti-Counterfeiting Policy is also stated on our external website, www.fairchildsemi.com, under Sales Support

Counterfeiting of semiconductor parts is a growing problem in the industry. All manufacturers of semiconductor products are experiencing counterfeiting of their parts. Customers who inadvertently purchase counterfeit parts experience many problems such as loss of brand reputation, substandard performance, failed applications, and increased cost of production and manufacturing delays. Fairchild is taking strong measures to protect ourselves and our customers from the proliferation of counterfeit parts. Fairchild strongly encourages customers to purchase Fairchild parts either directly from Fairchild or from Authorized Fairchild Distributors who are listed by country on our web page cited above. Products customers buy either from Fairchild directly or from Authorized Fairchild Distributors are genuine parts, have full traceability, meet Fairchild's quality standards for handling and storage and provide access to Fairchild's full range of up-to-date technical and product information. Fairchild and our Authorized Distributors will stand behind all warranties and will appropriately address any warranty issues that may arise. Fairchild will not provide any warranty coverage or other assistance for parts bought from Unauthorized Sources. Fairchild is committed to combat this global problem and encourage our customers to do their part in stopping this practice by buying direct or from authorized distributors.

### PRODUCT STATUS DEFINITIONS

## Definition of Terms

| Datasheet Identification   Product Status |                       | Definition                                                                                                                                                                                          |  |  |

|-------------------------------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Advance Information                       | Formative / In Design | Datasheet contains the design specifications for product development. Specifications may change in any manner without notice.                                                                       |  |  |

| Preliminary                               | First Production      | Datasheet contains preliminary data; supplementary data will be published at a later date. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve design. |  |  |

| No Identification Needed                  | Full Production       | Datasheet contains final specifications. Fairchild Semiconductor reserves the right to make changes at any time without notice to improve the design.                                               |  |  |

| Obsolete                                  | Not In Production     | Datasheet contains specifications on a product that is discontinued by Fairchild Semiconductor. The datasheet is for reference information only.                                                    |  |  |

Rev. 137