EVALUATION KIT

AVAILABLE

# 300mA LDO Linear Regulators with Internal Microprocessor Reset Circuit

## General Description

The MAX6469–MAX6484 are low-dropout linear regulators with a fully integrated microprocessor reset circuit. Each is available with preset output voltages from +1.5V to +3.3V in 100mV increments and delivers up to 300mA of load current. These devices consume only 82µA of supply current. The low supply current, low dropout voltage, and integrated reset functionality make these devices ideal for battery-powered portable equipment.

The MAX6469–MAX6484 include a reset output that indicates when the regulator output drops below standard microprocessor supply tolerances (-7.5% or -12.5% of nominal output voltage). This eliminates the need for an external microprocessor supervisor, while ensuring that supply voltages and clock oscillators have stabilized before processor activity is enabled. Push-pull and open-drain active-low reset outputs are available, with reset timeout periods of 2.5ms, 20ms, 150ms, or 1200ms (min).

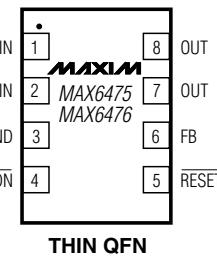

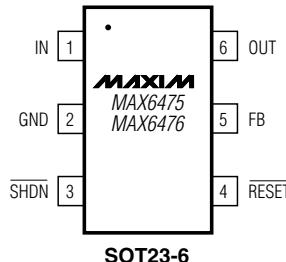

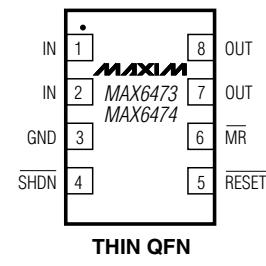

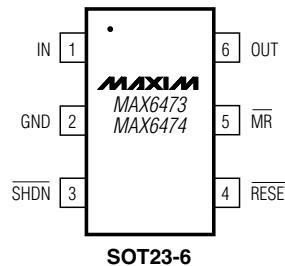

The MAX6469/MAX6470/MAX6473–MAX6478/MAX6481–MAX6484 also have a shutdown feature that reduces the supply current to 0.1µA (typ). The MAX6471–MAX6474/MAX6479–MAX6482 offer a manual reset input to assert a microprocessor reset while the regulator output is within specification. The MAX6475/MAX6476/MAX6483–MAX6484 feature a remote feedback sense pin for use with an external NPN transistor for higher-current applications. The MAX6469–MAX6476 are available in 6-pin SOT23 and 8-pin thin QFN packages. The MAX6477–MAX6484 are available in a 3 × 3 chip-scale package (UCSP™). All devices are specified for operation from -40°C to +85°C.

## Applications

- Hand-Held Instruments (PDAs, Palmtops)

- PCMCIA Cards/USB Devices

- Cellular/Cordless Telephones

- CD/DVD Drives

- Notebook Computers

- Digital Cameras

- Bluetooth Modules/Wireless LAN

UCSP is a trademark of Maxim Integrated Products, Inc.

**Pin Configurations appear at end of data sheet.**

**Typical Operating Circuits appear at end of data sheet.**

## Features

- ♦ 3 × 3 UCSP, 6-Pin SOT23, and 8-Pin QFN Packages

- ♦ Preset +1.5V to +3.3V Output (100mV Increments)

- ♦ SET Pin for Adjustable Output Voltage

- ♦ 75µVRMS LDO Output Voltage Noise (MAX6477–MAX6484)

- ♦ ±2.0% Accuracy Over Temperature

- ♦ Guaranteed 300mA Output Current

- ♦ Low Dropout Voltage

- 55mV at 150mA

- 114mV at 300mA

- ♦ 82µA Supply Current, 0.1µA Shutdown Current

- ♦ Input Reverse Current, Thermal and Short-Circuit Protection

- ♦ Microprocessor Reset with Four Timeout Options

- ♦ Push-Pull or Open-Drain RESET

- ♦ Manual Reset Input

- ♦ Remote Feedback Sense

## Ordering Information

| PART                  | TEMP RANGE     | PIN-PACKAGE |

|-----------------------|----------------|-------------|

| <b>MAX6469UT__D-T</b> | -40°C to +85°C | 6 SOT23-6   |

| MAX6469TA__D_*        | -40°C to +85°C | 8 Thin QFN  |

| <b>MAX6470UT__D-T</b> | -40°C to +85°C | 6 SOT23-6   |

| MAX6470TA__D_*        | -40°C to +85°C | 8 Thin QFN  |

\*Future product—contact factory for availability.

**Note:** The first “\_\_” are placeholders for the output voltage levels of the devices. Desired output voltages are set by the suffix found in the Output Voltage Suffix Guide (Table 1). The third “\_” is a placeholder for the reset threshold accuracy. Desired reset threshold accuracy is set by the suffix found in the Reset Threshold Accuracy Guide (Table 2). The “\_” following the D is a placeholder for the reset timeout delay time. Desired reset timeout delay time is set by the suffix found in the Reset Timeout Delay Guide (Table 3). For example, the MAX6481BL30BD4-T has a 3.0V output voltage, 12.5% reset threshold tolerance, and a 1200ms (min) reset timeout delay. Sample stock is generally available on standard versions only (Table 4). Standard versions require a minimum order increment of 2.5k units. Nonstandard versions must be ordered in 10k-unit increments. Contact factory for availability.

**Ordering Information continued at end of data sheet.**

Maxim Integrated Products 1

**For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at 1-888-629-4642, or visit Maxim's website at [www.maxim-ic.com](http://www.maxim-ic.com).**

# 300mA LDO Linear Regulators with Internal Microprocessor Reset Circuit

## ABSOLUTE MAXIMUM RATINGS

|                                                           |                        |

|-----------------------------------------------------------|------------------------|

| (All voltages referenced to GND, unless otherwise noted.) |                        |

| IN, SHDN, OUT, FB                                         | -0.3V to +7V           |

| MR, SET                                                   | -0.3V to (VIN + 0.3V)  |

| RESET (push-pull)                                         | -0.3V to (VOUT + 0.3V) |

| RESET (open drain)                                        | -0.3V to +7V           |

| OUT Short Circuit                                         | Continuous             |

| Input/Output Current (all pins except IN and OUT)         | 20mA                   |

|                                                            |

|------------------------------------------------------------|

| Continuous Power Dissipation (TA = +70°C)                  |

| 3 x 3 UCSP (derate 10.5mW/°C above +70°C) ..... 840mW      |

| 6-Pin SOT23 (derate 9.1mW/°C above +70°C) ..... 727mW      |

| 8-Pin Thin QFN (derate 24.4mW/°C above +70°C) ..... 1951mW |

| Operating Temperature Range ..... -40°C to +85°C           |

| Junction Temperature ..... +150°C                          |

| Storage Temperature Range ..... -65°C to +150°C            |

| Lead Temperature (soldering, 10s) ..... +300°C             |

**Note 1:** The MAX6477–MAX6484 are constructed using a unique set of packaging techniques that impose a limit on the thermal profile the devices can be exposed to during board-level solder attach and rework. This limit permits only the use of the solder profiles recommended in the industry-standard specification, JEDEC 020A, paragraph 7.6, Table 3 for IR/VPR and Convection reflow. Pre-heating is required. Hand or wave soldering is not allowed.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## ELECTRICAL CHARACTERISTICS

(VIN = (VOUT + 0.5V) or +2.5V, whichever is greater, COUT = 3.3µF, TA = -40°C to +85°C. Typical specifications are at TA = +25°C, unless otherwise noted.) (Note 2)

| PARAMETER                                                                         | SYMBOL            | CONDITIONS                                                   | MIN              | TYP   | MAX   | UNITS |

|-----------------------------------------------------------------------------------|-------------------|--------------------------------------------------------------|------------------|-------|-------|-------|

| Input Voltage Range                                                               | VIN               |                                                              | 2.5              | 5.5   |       | V     |

| Input Undervoltage Lockout                                                        | VUVLO             | VIN falling                                                  | 2.25             | 2.47  |       | V     |

| Supply Current (Ground Current)                                                   | I <sub>Q</sub>    | I <sub>OUT</sub> = 0                                         | 82               | 136   |       | µA    |

|                                                                                   |                   | I <sub>OUT</sub> = 300mA                                     | 96               |       |       |       |

| Shutdown Supply Current                                                           | I <sub>SHDN</sub> | TA = +25°C                                                   | 0.1              | 1     |       | µA    |

| <b>REGULATOR CIRCUIT</b>                                                          |                   |                                                              |                  |       |       |       |

| Output Current                                                                    |                   |                                                              | 300              |       |       | mA    |

| Output Voltage Accuracy (Fixed Output Voltage Operation, Table 1) MAX6469–MAX6476 |                   | 1mA ≤ I <sub>OUT</sub> ≤ 150mA, TA = +25°C                   | -1.3             | +1.3  |       | %     |

|                                                                                   |                   | 1mA ≤ I <sub>OUT</sub> ≤ 150mA, TA = -40°C to +85°C          | -2.3             | +2.3  |       |       |

|                                                                                   |                   | 1mA ≤ I <sub>OUT</sub> ≤ 300mA, TA = -40°C to +85°C          | -2.7             | +2.7  |       |       |

| Output Voltage Accuracy (Fixed Output Voltage Operation, Table 1) MAX6477–MAX6484 |                   | 2mA ≤ I <sub>OUT</sub> ≤ 100mA, TA = +25°C                   | -1.1             | +1.1  |       | %     |

|                                                                                   |                   | 2mA ≤ I <sub>OUT</sub> ≤ 100mA, TA = -40°C to +85°C          | -2.0             | +2.0  |       |       |

|                                                                                   |                   | 2mA ≤ I <sub>OUT</sub> ≤ 300mA, TA = -40°C to +85°C (Note 3) | -2.5             | +2.5  |       |       |

| Adjustable Output Voltage Range                                                   |                   |                                                              | V <sub>SET</sub> | 5.0   |       | V     |

| SET Reference Voltage                                                             | V <sub>SET</sub>  |                                                              | 1.200            | 1.229 | 1.258 | V     |

| SET Dual Mode™ Threshold                                                          |                   |                                                              |                  | 185   |       | mV    |

| SET Input Leakage Current                                                         | I <sub>SET</sub>  | V <sub>SET</sub> = 0, +1.2V (Note 3)                         | ±20              | ±100  |       | nA    |

*Dual Mode* is a trademark of Maxim Integrated Products, Inc.

# 300mA LDO Linear Regulators with Internal Microprocessor Reset Circuit

## ELECTRICAL CHARACTERISTICS (continued)

( $V_{IN} = (V_{OUT} + 0.5V)$  or  $+2.5V$ , whichever is greater,  $C_{OUT} = 3.3\mu F$ ,  $T_A = -40^\circ C$  to  $+85^\circ C$ . Typical specifications are at  $T_A = +25^\circ C$ , unless otherwise noted.) (Note 2)

| PARAMETER                                                                                              | SYMBOL            | CONDITIONS                                                                                                                              |                   | MIN                 | TYP  | MAX  | UNITS             |  |

|--------------------------------------------------------------------------------------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-------------------|---------------------|------|------|-------------------|--|

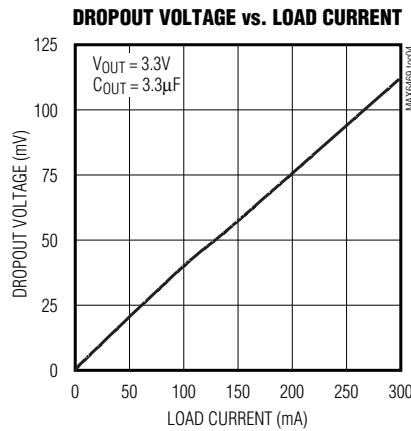

| Dropout Voltage<br>(Notes 3, 4)                                                                        | $\Delta V_{DO}$   | $V_{OUT} = +3.3V$<br>(fixed output operation)                                                                                           | $I_{OUT} = 50mA$  | 23                  | 32   |      | mV                |  |

|                                                                                                        |                   |                                                                                                                                         | $I_{OUT} = 150mA$ | 55                  | 90   |      |                   |  |

|                                                                                                        |                   |                                                                                                                                         | $I_{OUT} = 300mA$ | 114                 | 180  |      |                   |  |

|                                                                                                        |                   | $V_{OUT} = +3.0V$<br>(fixed output operation)                                                                                           | $I_{OUT} = 50mA$  | 25                  | 40   |      |                   |  |

|                                                                                                        |                   |                                                                                                                                         | $I_{OUT} = 150mA$ | 61                  | 100  |      |                   |  |

|                                                                                                        |                   |                                                                                                                                         | $I_{OUT} = 300mA$ | 114                 | 190  |      |                   |  |

|                                                                                                        |                   | $V_{OUT} = +2.8V$<br>(fixed output operation)                                                                                           | $I_{OUT} = 50mA$  | 26                  | 50   |      |                   |  |

|                                                                                                        |                   |                                                                                                                                         | $I_{OUT} = 150mA$ | 65                  | 110  |      |                   |  |

|                                                                                                        |                   |                                                                                                                                         | $I_{OUT} = 300mA$ | 137                 | 210  |      |                   |  |

|                                                                                                        |                   | $V_{OUT} = +2.5V$<br>(fixed output operation)                                                                                           | $I_{OUT} = 50mA$  | 30                  | 60   |      |                   |  |

|                                                                                                        |                   |                                                                                                                                         | $I_{OUT} = 150mA$ | 75                  | 150  |      |                   |  |

|                                                                                                        |                   |                                                                                                                                         | $I_{OUT} = 300mA$ | 158                 | 250  |      |                   |  |

| Output Current Limit                                                                                   |                   | $V_{IN} \geq 2.5V$ (Note 3)                                                                                                             |                   | 450                 |      |      | mA                |  |

| Input Reverse Leakage Current<br>(OUT to IN Leakage Current)                                           |                   | $V_{IN} = 4V$ , $V_{OUT} = 5.5V$ , $\overline{SHDN}$ deasserted                                                                         |                   | 0.01                | 1.5  |      | $\mu A$           |  |

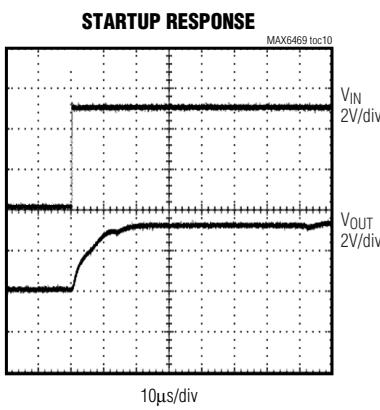

| Startup Time Response                                                                                  |                   | Rising edge of $V_{IN}$ or $\overline{SHDN}$ to $V_{OUT}$<br>within specification, $R_L = 68\Omega$ , $SET = GND$ ,<br>$I_{OUT} = 10mA$ |                   | 20                  |      |      | $\mu s$           |  |

| SHDN Input Low Voltage                                                                                 | $V_{IL}$          |                                                                                                                                         |                   | 0.3 $\times V_{IN}$ |      |      | V                 |  |

| SHDN Input High Voltage                                                                                | $V_{IH}$          |                                                                                                                                         |                   | 0.7 $\times V_{IN}$ |      |      | V                 |  |

| SHDN Input Current                                                                                     |                   | $\overline{SHDN} = V_{IN}$ or $GND$                                                                                                     |                   | -1                  | 0.1  | +1   | $\mu A$           |  |

| Thermal-Shutdown Temperature                                                                           | $T_{SHDN}$        |                                                                                                                                         |                   | 180                 |      |      | $^\circ C$        |  |

| Thermal-Shutdown Hysteresis                                                                            | $\Delta T_{SHDN}$ |                                                                                                                                         |                   | 20                  |      |      | $^\circ C$        |  |

| Line Regulation                                                                                        |                   | $V_{OUT} = 1.5V$ , $2.5V \leq V_{IN} \leq 5.5V$ ,<br>$I_{OUT} = 10mA$                                                                   |                   | 0.09                |      |      | $\%/V$            |  |

| Load Regulation                                                                                        |                   | $V_{OUT} = 1.5V$ , $V_{IN} = 2.5V$ , $1mA \leq I_{OUT} \leq$<br>$150mA$                                                                 |                   | 0.2                 |      |      | %                 |  |

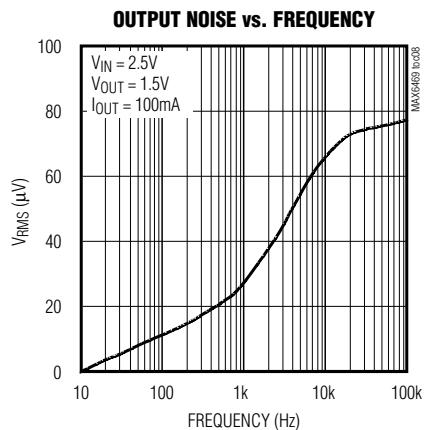

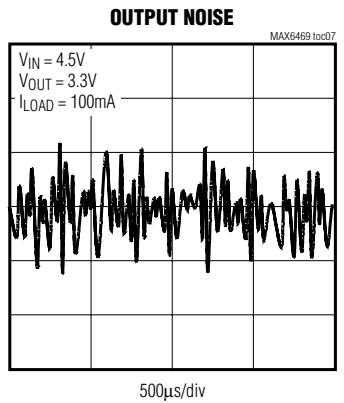

| Output Voltage Noise                                                                                   |                   | 10Hz to 100kHz,<br>$C_{IN} = 0.1\mu F$ ,<br>$I_{OUT} = 100mA$ ,<br>$V_{OUT} = 1.5V$                                                     | MAX6469–MAX6476   | 150                 |      |      | $\mu V_{RMS}$     |  |

|                                                                                                        |                   |                                                                                                                                         |                   | 75                  |      |      |                   |  |

| <b>RESET CIRCUIT</b>                                                                                   |                   |                                                                                                                                         |                   |                     |      |      |                   |  |

| V <sub>OUT</sub> Reset Threshold<br>(V <sub>FB</sub> for MAX6475/MAX6476/<br>MAX6483/MAX6484) (Note 5) | $V_{THOUT}$       | MAX64_____A                                                                                                                             |                   | 90                  | 92.5 | 95   | %V <sub>OUT</sub> |  |

|                                                                                                        |                   | MAX64_____B                                                                                                                             |                   | 85                  | 87.5 | 90   |                   |  |

| V <sub>OUT</sub> to Reset Delay<br>(V <sub>FB</sub> for MAX6475/MAX6476/<br>MAX6483/MAX6484)           |                   |                                                                                                                                         |                   | 35                  |      |      | $\mu s$           |  |

| Reset Timeout Period<br>(Note 6)                                                                       | $t_{RP}$          | D1                                                                                                                                      |                   | 2.5                 | 3.75 | 5.0  | ms                |  |

|                                                                                                        |                   | D2                                                                                                                                      |                   | 20                  | 30   | 40   |                   |  |

|                                                                                                        |                   | D3                                                                                                                                      |                   | 150                 | 225  | 300  |                   |  |

|                                                                                                        |                   | D4                                                                                                                                      |                   | 1200                | 1800 | 2400 |                   |  |

**MAX6469–MAX6484**

# 300mA LDO Linear Regulators with Internal Microprocessor Reset Circuit

## ELECTRICAL CHARACTERISTICS (continued)

( $V_{IN} = (V_{OUT} + 0.5V)$  or  $+2.5V$ , whichever is greater,  $C_{OUT} = 3.3\mu F$ ,  $T_A = -40^\circ C$  to  $+85^\circ C$ . Typical specifications are at  $T_A = +25^\circ C$ , unless otherwise noted.) (Note 2)

| PARAMETER                               | SYMBOL    | CONDITIONS                                                       | MIN                  | TYP                  | MAX                  | UNITS     |

|-----------------------------------------|-----------|------------------------------------------------------------------|----------------------|----------------------|----------------------|-----------|

| MR Input Low Voltage                    | $V_{IL}$  |                                                                  |                      |                      | $0.3 \times V_{OUT}$ | V         |

| MR Input High Voltage                   | $V_{IH}$  | (Note 3)                                                         |                      | $0.7 \times V_{OUT}$ |                      | V         |

| MR Minimum Input Pulse                  |           |                                                                  |                      | 1                    |                      | $\mu s$   |

| MR Glitch Rejection                     |           |                                                                  |                      | 120                  |                      | ns        |

| MR to Reset Delay                       |           |                                                                  |                      | 200                  |                      | ns        |

| MR Pullup Resistance                    |           | MR to OUT                                                        | 25                   | 40                   | 70                   | $k\Omega$ |

| RESET Output Voltage (Open Drain)       | $V_{OL}$  | $V_{OUT} \geq 1.0V$ , $I_{SINK} = 50\mu A$ , RESET asserted      |                      | 0.3                  |                      | V         |

|                                         |           | $V_{OUT} \geq 1.5V$ , $I_{SINK} = 3.2mA$ , RESET asserted        |                      | 0.4                  |                      |           |

| Open-Drain Reset Output Leakage Current | $I_{LKG}$ | (Note 3)                                                         |                      | 1                    |                      | $\mu A$   |

| RESET Output Voltage Push-Pull          | $V_{OL}$  | $V_{OUT} \geq 1.0V$ , $I_{SINK} = 50\mu A$ , RESET asserted      |                      | 0.3                  |                      | V         |

|                                         |           | $V_{OUT} \geq 1.5V$ , $I_{SINK} = 3.2mA$ , RESET asserted        |                      | 0.4                  |                      |           |

|                                         | $V_{OH}$  | $V_{OUT} \geq 2.0V$ , $I_{SOURCE} = 500\mu A$ , RESET deasserted | 0.8 $\times V_{OUT}$ |                      |                      |           |

**Note 2:** All devices are 100% production tested at  $+25^\circ C$  and are guaranteed by correlation for  $T_A = T_{MIN}$  to  $T_{MAX}$ .

**Note 3:** Guaranteed by design.

**Note 4:** Dropout voltage is defined as  $(V_{IN} - V_{OUT})$  when  $V_{OUT}$  is 2% below the value of  $V_{OUT}$  for  $V_{IN} = V_{OUT(NOM)} + 1V$ .

**Note 5:** MAX6473/MAX6474/MAX6481/MAX6482 are guaranteed by design for  $V_{OUT} < 2.5V$ .

**Note 6:** Select the reset timeout period using the *Reset Timeout Delay Guide* (Table 3). Insert the appropriate suffix in the part number when ordering.

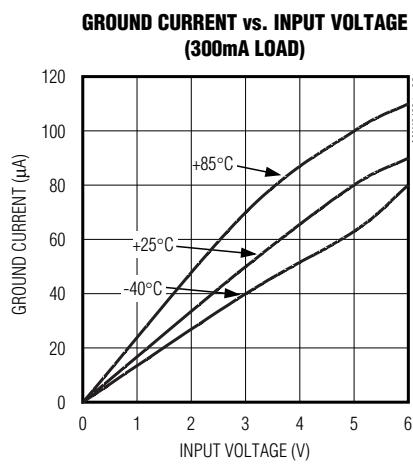

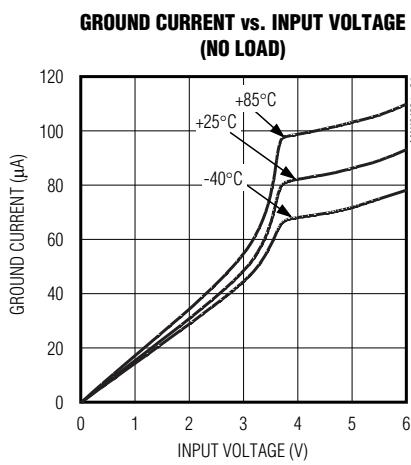

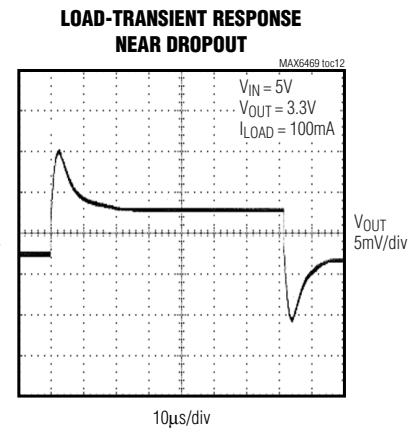

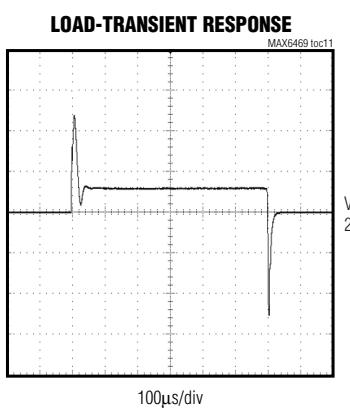

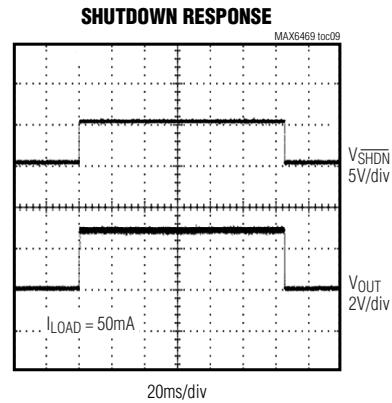

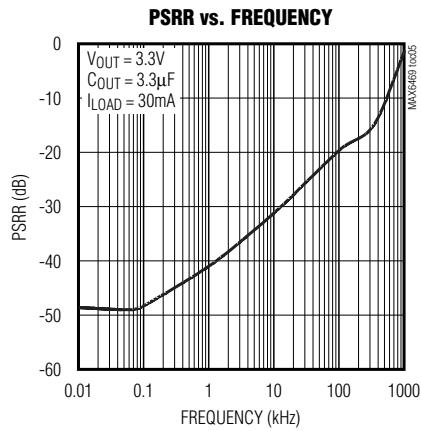

## Typical Operating Characteristics

( $V_{IN} = 5V$ ,  $V_{OUT} = 3.3V$ ,  $C_{OUT} = 3.3\mu F$ ,  $T_A = +25^\circ C$ , unless otherwise noted.)

# 300mA LDO Linear Regulators with Internal Microprocessor Reset Circuit

## Typical Operating Characteristics (continued)

( $V_{IN} = 5V$ ,  $V_{OUT} = 3.3V$ ,  $C_{OUT} = 3.3\mu F$ ,  $T_A = +25^{\circ}C$ , unless otherwise noted.)

MAX6469-MAX6484

# 300mA LDO Linear Regulators with Internal Microprocessor Reset Circuit

## Typical Operating Characteristics (continued)

( $V_{IN} = 5V$ ,  $V_{OUT} = 3.3V$ ,  $C_{OUT} = 3.3\mu F$ ,  $T_A = +25^\circ C$ , unless otherwise noted.)

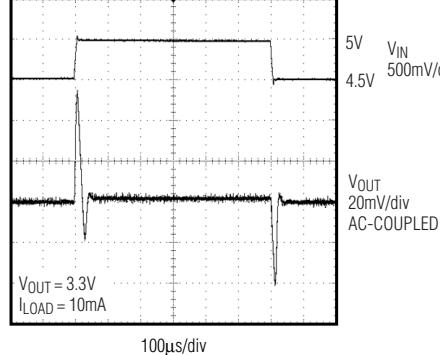

LINE TRANSIENT RESPONSE

MAX6469 toc13

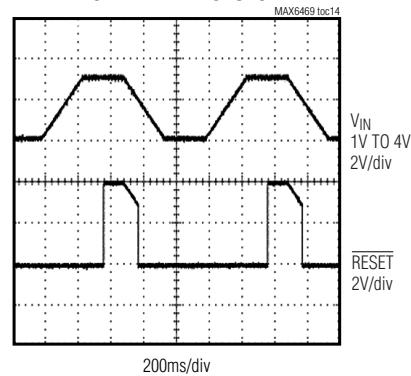

RESET DELAY RESPONSE

MAX6469 toc14

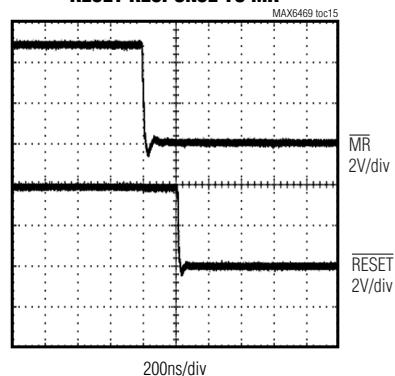

RESET RESPONSE TO MR

MAX6469 toc15

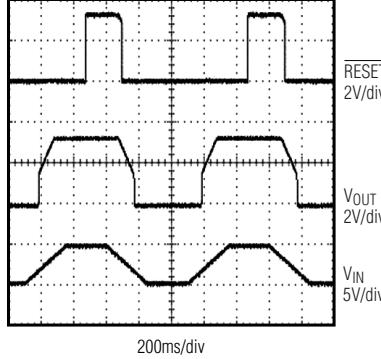

RESET RESPONSE TO  $V_{IN}$  RISING

MAX6469 toc16

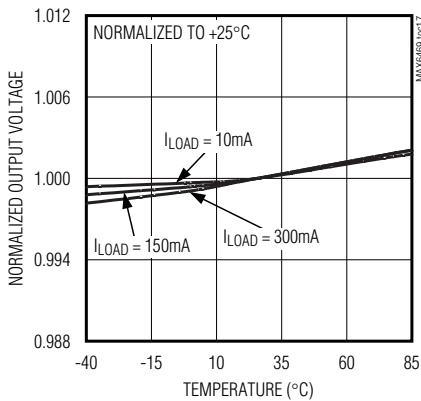

NORMALIZED OUTPUT VOLTAGE

vs. TEMPERATURE

# 300mA LDO Linear Regulators with Internal Microprocessor Reset Circuit

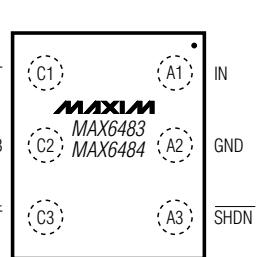

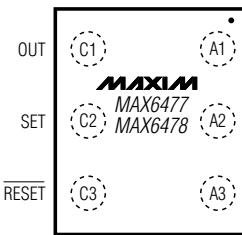

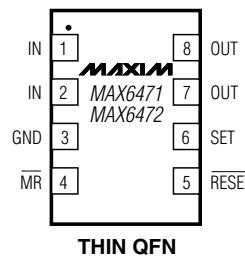

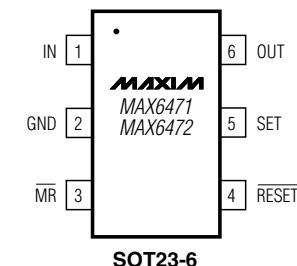

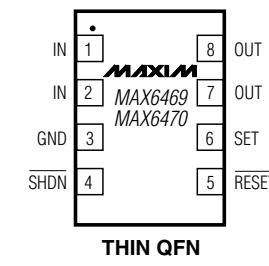

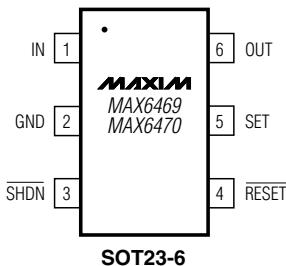

## MAX6469/MAX6470/MAX6477/MAX6478 Pin Description

| PIN             |      | BUMP            | NAME  | FUNCTION                                                                                                                                                                                                                                                                 |

|-----------------|------|-----------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAX6469/MAX6470 |      | MAX6477/MAX6478 |       |                                                                                                                                                                                                                                                                          |

| SOT23           | QFN  | UCSP            |       |                                                                                                                                                                                                                                                                          |

| 1               | 1, 2 | A1              | IN    | Regulator Input. Bypass IN to GND with a 0.1 $\mu$ F capacitor.                                                                                                                                                                                                          |

| 2               | 3    | A2              | GND   | Ground. This pin also functions as a heatsink. Solder to large pads or the circuit-board ground plane to maximize thermal dissipation.                                                                                                                                   |

| 3               | 4    | A3              | SHDN  | Active-Low Shutdown Input. Connect SHDN to V <sub>IN</sub> for normal operation.                                                                                                                                                                                         |

| 4               | 5    | C3              | RESET | Active-Low Reset Output. RESET remains low while V <sub>OUT</sub> is below the reset threshold. RESET remains low for the duration of the reset timeout period after the reset conditions are terminated. RESET is available in open-drain and push-pull configurations. |

| 5               | 6    | C2              | SET   | Feedback Input for Externally Setting the Output Voltage. Connect SET to GND to select the preset output voltage. Connect SET to an external resistor-divider network for adjustable output operation.                                                                   |

| 6               | 7, 8 | C1              | OUT   | Regulator Output. Bypass OUT to GND with a minimum 3.3 $\mu$ F low-ESR capacitor.                                                                                                                                                                                        |

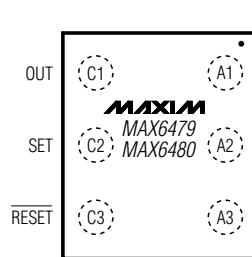

## MAX6471/MAX6472/MAX6479/MAX6480 Pin Description

| PIN             |      | BUMP            | NAME  | FUNCTION                                                                                                                                                                                                                                                                                                                                    |

|-----------------|------|-----------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MAX6471/MAX6472 |      | MAX6479/MAX6480 |       |                                                                                                                                                                                                                                                                                                                                             |

| SOT23           | QFN  | UCSP            |       |                                                                                                                                                                                                                                                                                                                                             |

| 1               | 1, 2 | A1              | IN    | Regulator Input. Bypass IN to GND with a 0.1 $\mu$ F capacitor.                                                                                                                                                                                                                                                                             |

| 2               | 3    | A2              | GND   | Ground. This pin also functions as a heatsink. Solder to large pads or the circuit-board ground plane to maximize thermal dissipation.                                                                                                                                                                                                      |

| 3               | 4    | A3              | MR    | Active-Low Manual Reset Input. The reset output is asserted while MR is pulled low and remains asserted for the duration of the reset timeout period after MR transitions from low to high. Leave MR unconnected or connect to V <sub>OUT</sub> if not used. MR has an internal pullup resistor of 40k $\Omega$ (typ) to V <sub>OUT</sub> . |

| 4               | 5    | C3              | RESET | Active-Low Reset Output. RESET remains low while V <sub>OUT</sub> is below the reset threshold or while MR is held low. RESET remains low for the duration of the reset timeout period after the reset conditions are terminated. RESET is available in open-drain and push-pull configurations.                                            |

| 5               | 6    | C2              | SET   | Feedback Input for Externally Setting the Output Voltage. Connect SET to GND to select the preset output voltage. Connect SET to an external resistor-divider network for adjustable output operation.                                                                                                                                      |

| 6               | 7, 8 | C1              | OUT   | Regulator Output. Bypass OUT to GND with a minimum 3.3 $\mu$ F low-ESR capacitor.                                                                                                                                                                                                                                                           |

MAX6469-MAX6484

## 300mA LDO Linear Regulators with Internal Microprocessor Reset Circuit

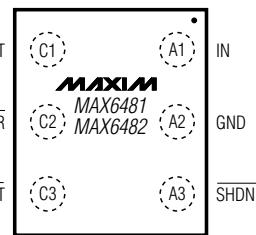

### MAX6473/MAX6474/MAX6481/MAX6482 Pin Description

| PIN   |      | BUMP | NAME  | FUNCTION                                                                                                                                                                                                                                                                                                                                    |

|-------|------|------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SOT23 | QFN  | UCSP |       |                                                                                                                                                                                                                                                                                                                                             |

| 1     | 1, 2 | A1   | IN    | Regulator Input. Bypass IN to GND with a 0.1 $\mu$ F capacitor.                                                                                                                                                                                                                                                                             |

| 2     | 3    | A2   | GND   | Ground. This pin also functions as a heatsink. Solder to large pads or the circuit-board ground plane to maximize thermal dissipation.                                                                                                                                                                                                      |

| 3     | 4    | A3   | SHDN  | Active-Low Shutdown Input. Connect SHDN to V <sub>IN</sub> for normal operation.                                                                                                                                                                                                                                                            |

| 4     | 5    | C3   | RESET | Active-Low Reset Output. RESET remains low while V <sub>OUT</sub> is below the reset threshold or while MR is held low. RESET remains low for the duration of the reset timeout period after the reset conditions are terminated. RESET is available in open-drain and push-pull configurations.                                            |

| 5     | 6    | C2   | MR    | Active-Low Manual Reset Input. The reset output is asserted while MR is pulled low and remains asserted for the duration of the reset timeout period after MR transitions from low to high. Leave MR unconnected or connect to V <sub>OUT</sub> if not used. MR has an internal pullup resistor of 40k $\Omega$ (typ) to V <sub>OUT</sub> . |

| 6     | 7, 8 | C1   | OUT   | Regulator Output. Bypass OUT to GND with a minimum 3.3 $\mu$ F (min) low-ESR capacitor.                                                                                                                                                                                                                                                     |

### MAX6475/MAX6476/MAX6483/MAX6484 Pin Description

| PIN   |      | BUMP | NAME  | FUNCTION                                                                                                                                                                                                                                                   |

|-------|------|------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SOT23 | QFN  | UCSP |       |                                                                                                                                                                                                                                                            |

| 1     | 1, 2 | A1   | IN    | Regulator Input. Bypass IN to GND with a 0.1 $\mu$ F capacitor.                                                                                                                                                                                            |

| 2     | 3    | A2   | GND   | Ground. This pin also functions as a heatsink. Solder to large pads or the circuit-board ground plane to maximize thermal dissipation.                                                                                                                     |

| 3     | 4    | A3   | SHDN  | Active-Low Shutdown Input. Connect SHDN to V <sub>IN</sub> for normal operation.                                                                                                                                                                           |

| 4     | 5    | C3   | RESET | Active-Low Reset Output. RESET remains low while FB is below the reset threshold. RESET remains low for the duration of the reset timeout period after the reset conditions are terminated. RESET is available in open-drain and push-pull configurations. |

| 5     | 6    | C2   | FB    | Feedback Input for Linear Regulator Controller or Remote Sense Applications. Connect FB to the external load (V <sub>CC</sub> ) to obtain the fixed output voltage.                                                                                        |

| 6     | 7, 8 | C1   | OUT   | Regulator Output. Bypass OUT to GND with a minimum 3.3 $\mu$ F low-ESR capacitor.                                                                                                                                                                          |

# 300mA LDO Linear Regulators with Internal Microprocessor Reset Circuit

## Detailed Description

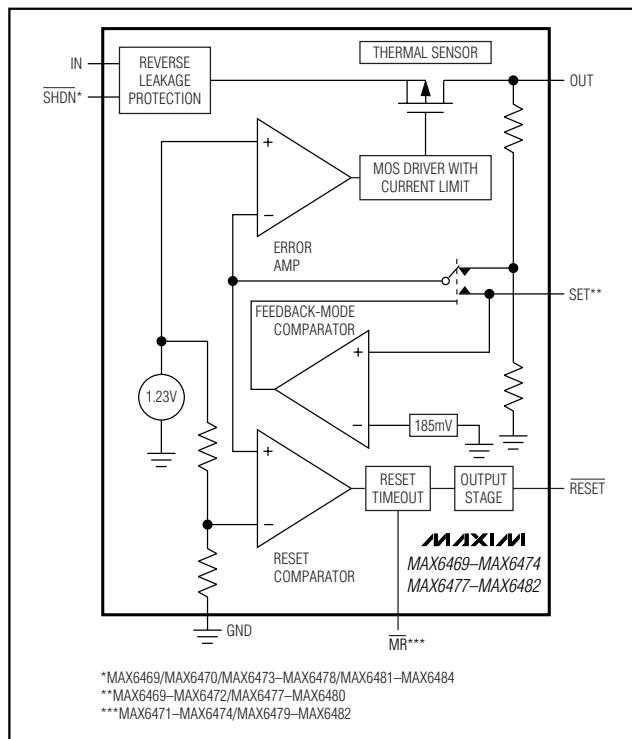

The MAX6469–MAX6484 are ultra-low, quiescent current, low-dropout linear regulators with an integrated microprocessor reset circuit. These devices guarantee 300mA (min) drive capabilities and are available with preset output voltages in 100mV increments between +1.5V and +3.3V. The internal reset circuit monitors the regulator output voltage and asserts the reset output when the regulator output is below the microprocessor supply tolerance.

### Regulator

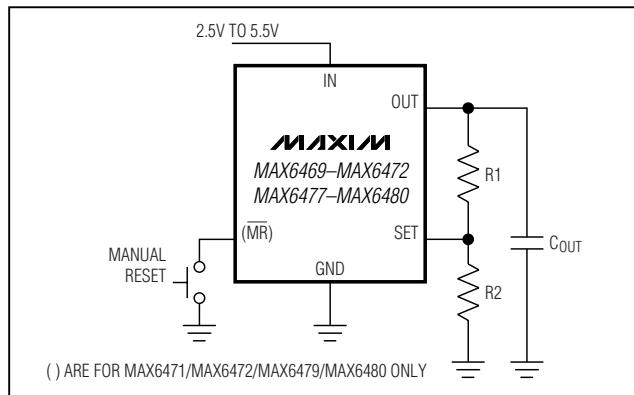

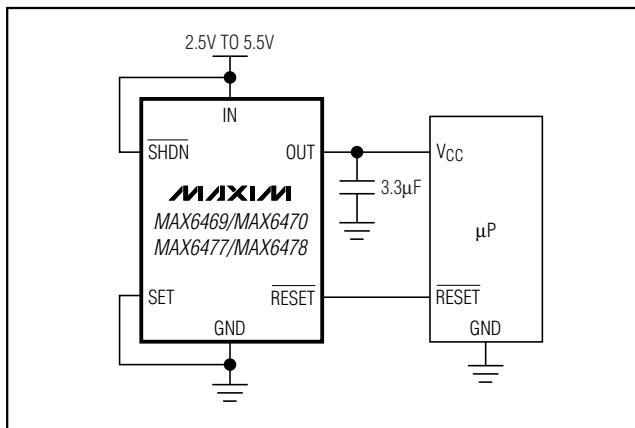

The regulator core operates with +2.5V to +5.5V input voltage range. The output voltage is offered in 100mV increments between +1.5V and +3.3V (contact factory for other output voltage options). The MAX6469–MAX6472/MAX6477–MAX6480 offer an adjustable output voltage implemented with an external resistor-divider network between OUT, SET, and GND (Figure 1). SET must be connected to either GND for fixed V<sub>OUT</sub> or to an external divider for adjustable V<sub>OUT</sub>. The MAX6469–MAX6472/MAX6477–MAX6480 automatically determine the feedback path depending on the connection of SET. The *Typical Operating Circuit* shows a typical connection for the MAX6469. OUT is an internally regulated low-dropout (LDO) linear regulator that powers a microprocessor.

### Reset Circuit

The reset supervisor circuit is fully integrated in the MAX6469–MAX6484 and uses the same reference voltage as the regulator. Two supply tolerance reset thresholds, -7.5% and -12.5%, are provided for each type of device.

**-7.5% Reset:** Reset does not assert until the regulator output voltage is at least -5% out of tolerance and always asserts before the regulator output voltage is -10% out of tolerance.

**-12.5% Reset:** Reset does not assert until the regulator output voltage is at least -10% out of tolerance and always asserts before the regulator output voltage is -15% out of tolerance.

### RESET Output

A  $\mu$ P's reset input starts the  $\mu$ P in a known state. The MAX6469–MAX6484  $\mu$ P supervisory circuits assert RESET during power-up, power-down, and brownout conditions. RESET asserts when the input voltage is below the undervoltage lockout threshold. RESET asserts when V<sub>OUT</sub> is below the reset threshold and remains asserted for at least the minimum selected reset timeout period (t<sub>RP</sub>, Table 3) after V<sub>IN</sub> rises above the undervoltage lockout threshold and V<sub>OUT</sub> rises above

Figure 1. Adjustable Output Voltage Configuration

the reset threshold. RESET asserts when  $\overline{MR}$  is pulled low (MAX6471–MAX6474/MAX6479–MAX6482). RESET asserts when SHDN is pulled low (MAX6469/MAX6470/MAX6473–MAX6478/MAX6481–MAX6484).

### Shutdown (MAX6469/MAX6470/MAX6473–MAX6478/MAX6481–MAX6484 only)

SHDN allows the regulator to shut down, thereby reducing the total I<sub>IN</sub> consumption of the device. SHDN provides a digitally controlled active-low shutdown. In shutdown mode, the pass transistor, control circuit, and reference turn off to reduce the supply current to below 0.1 $\mu$ A. Connect SHDN to IN for normal operation.

### Manual Reset Input (MAX6471–MAX6474/MAX6479–MAX6482 only)

Many  $\mu$ P-based products require manual reset capability, allowing the operator, a test technician, or external logic circuitry to initiate a reset. A logic low on  $\overline{MR}$  asserts reset while the regulator output voltage is still within tolerance.

Reset remains asserted while  $\overline{MR}$  is low and for the reset timeout period (t<sub>RP</sub>) after  $\overline{MR}$  returns high. The  $\overline{MR}$  input has an internal pullup of 40k $\Omega$  (typ) to OUT.  $\overline{MR}$  can be driven with TTL/CMOS logic levels or with open-drain/collector outputs. Connect a normally open switch from  $\overline{MR}$  to GND to create a manual reset function; external debounce circuitry is not required. If  $\overline{MR}$  is driven from long cables or the device is used in a noisy environment, connect a 0.1 $\mu$ F capacitor from  $\overline{MR}$  to GND to provide additional noise immunity.

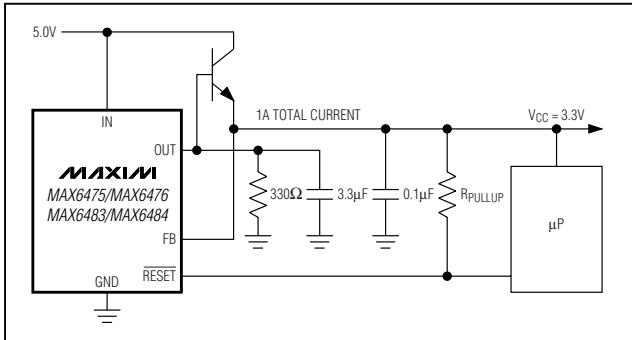

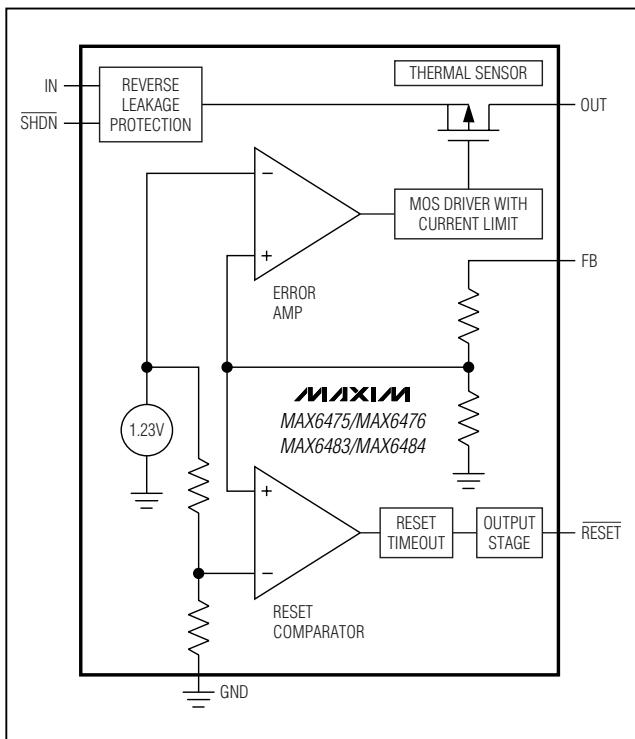

### Feedback Input (MAX6475/MAX6476/MAX6483/MAX6484 only)

The feedback input (FB) connects to an internal resistor-divider network (*Functional Diagram*). FB is not internally connected to V<sub>OUT</sub>, and as a result can be used to

**MAX6469–MAX6484**

# 300mA LDO Linear Regulators with Internal Microprocessor Reset Circuit

remotely sense the output voltage of the device. Using FB with an external NPN transistor, the current drive capability can be increased according to the following equation (Figure 2):

$$I_{OUT(TOTAL)} = I_{OUT} \times (\beta + 1)$$

The external NPN pass transistor must meet specifications for current gain, power dissipation, and collector current. The beta influences the maximum output current the circuit can deliver. The largest guaranteed output current is given by  $I_{LOAD(max)} = 300mA \times \beta(\min)$ . The transistor's rated power dissipation must exceed the actual power dissipated in the transistor. The power dissipated (PD) equals the maximum load current ( $I_{LOAD(max)}$ ) times the maximum input-to-output voltage differential:  $PD = I_{LOAD(max)} \times (V_{IN(max)} - V_{OUT})$ . The rated transistor collector current must exceed the maximum load current.

## Reverse Leakage Protection

### Reverse OUT to IN Current

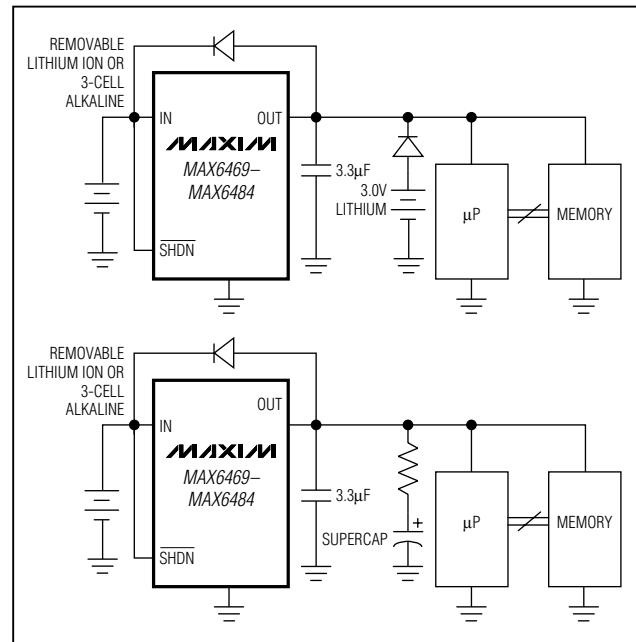

An internal circuit monitors the MAX6469–MAX6484 input and output voltages. When the output voltage is greater than the input voltage, the internal IN-to-OUT pass transistor and parasitic diode turn off. An external voltage applied to OUT does not reverse charge a battery or power source applied to IN (the leakage path from OUT to IN is  $0.01\mu A$  typ). When the output voltage exceeds the input voltage, OUT powers the device and shutdown must be logic high (greater than  $0.7 \times V_{OUT}$ ). RESET asserts until IN exceeds OUT and OUT is above the specified  $V_{THOUT}$  threshold (based on the selected or adjusted regulator OUT nominal voltage).

### Reverse OUT to Ground Current

The MAX6469–MAX6484 maintain a low OUT-to-GND reverse-current flow when the IN power source is removed. When IN floats (input battery removed) and SHDN is pulled up to  $V_{OUT}$  (by an external diode), the

Figure 2. High-Current, External Transistor Application

OUT-to-GND current through the LDO is  $40\mu A$  (typ). The regulator output can be held up with an external super capacitor or backup battery at OUT until the IN battery is replaced. The RESET output is asserted while the IN battery is removed to place the system in a low-power mode. Volatile memory content is maintained until the super capacitor or battery voltage drops below RAM standby specifications. RESET deasserts when the IN battery has been replaced and OUT exceeds the desired reset threshold. For nonrechargeable backup battery applications, place a reverse diode between OUT and the backup battery (to prevent battery charging). The external diode does not affect the regulator's dropout voltage because it is not between the LDO output and the processor/memory Vcc supply. The diode can be replaced with a current-limiting resistor for rechargeable backup battery applications.

## Current Limit

The MAX6469–MAX6484 include an internal current-limit circuit that monitors and controls the pass transistor's gate voltage, limiting the output current to  $450mA$  (min). The output can be shorted to ground indefinitely without damaging the part.

### Thermal Shutdown

When the junction temperature ( $T_J$ ) exceeds  $+180^\circ C$  (typ), the thermal sensor signals the shutdown logic, turning off the pass transistor and allowing the IC to

Figure 3. Battery Backup

# 300mA LDO Linear Regulators with Internal Microprocessor Reset Circuit

MAX6469-MAX6484

cool. The thermal sensor turns the pass transistor on again after the IC's junction temperature cools by 20°C, resulting in a pulsed output during continuous thermal overload conditions. Thermal overload protection is designed to protect the MAX6469–MAX6484 in the event of fault conditions. For continuous operation, do not exceed the absolute maximum junction temperature rating of  $T_{JMAX} = +150^\circ\text{C}$ .

## Operating Region and Power Dissipation

The MAX6469–MAX6484's maximum power dissipation depends on the thermal resistance of the case and circuit board, the temperature difference between the die junction and the ambient air, and the rate of airflow. The power dissipation across the device is:

$$P = I_{\text{OUT}} (V_{\text{IN}} - V_{\text{OUT}})$$

The maximum power dissipation is:

$$P_{\text{MAX}} = (T_J - T_A) / (\emptyset_{JB} + \emptyset_{BA})$$

where  $T_J - T_A$  is the temperature difference between the die junction and the surrounding air,  $\emptyset_{JB}$  (or  $\emptyset_{JC}$ ) is the thermal resistance of the package, and  $\emptyset_{BA}$  is the thermal resistance through the PC board, copper traces, and other materials to the surrounding air. The MAX6469–MAX6476 QFN package  $\emptyset_{JC} = 41^\circ\text{C}/\text{W}$ , and the MAX6469–MAX6476 SOT package  $\emptyset_{JC} = 110^\circ\text{C}/\text{W}$ .

The MAX6469–MAX6484's ground pin (GND) performs the dual function of providing an electrical connection to the system ground and channeling heat away. Connect GND to the system ground using a large pad or ground plane. For continuous operation, do not exceed the absolute maximum junction temperature rating of  $T_{JMAX} = +150^\circ\text{C}$ .

## Applications Information

### Output Voltage Selection

The MAX6469–MAX6484 feature dual-mode operation: they operate in either a preset output voltage mode or an adjustable mode. In preset voltage mode, internal feedback resistors set the MAX6469–MAX6484's output from +1.5V to +3.3V (Table 1). Select this mode by connecting SET to ground (MAX6469–MAX6472/MAX6477–MAX6480). In adjustable mode, select an output between 1.25V and 5.5V using two external resistors connected as a voltage-divider to SET (Figure 1). The output voltage is set by the following equation:

$$V_{\text{OUT}} = V_{\text{SET}} (1 + R_1 / R_2)$$

where  $V_{\text{SET}} = 1.23\text{V}$ . To simplify resistor selection:

$$R_1 = R_2 (V_{\text{OUT}} / V_{\text{SET}} - 1)$$

Choose  $R_2 = 50\text{k}\Omega$  to maintain stability, accuracy and high-frequency power-supply rejection. Avoid selecting

resistor values greater than  $100\text{k}\Omega$ . In preset voltage mode, the impedance between SET and ground should always be less than  $50\text{k}\Omega$ . In most applications, connect SET directly to ground.

### Low-Noise UCSP Output

MAX6477–MAX6484 UCSP products include internal filtering to yield low output noise without an additional external bypass capacitor. The devices yield  $75\text{\mu VRMS}$  (typ) output noise (for  $V_{\text{OUT}} = 3.0\text{V}$ ) and  $150\text{\mu VRMS}$  (for  $V_{\text{OUT}} = 3.3\text{V}$ ). This low-noise feature makes the MAX6477–MAX6484 ideal for audio applications.

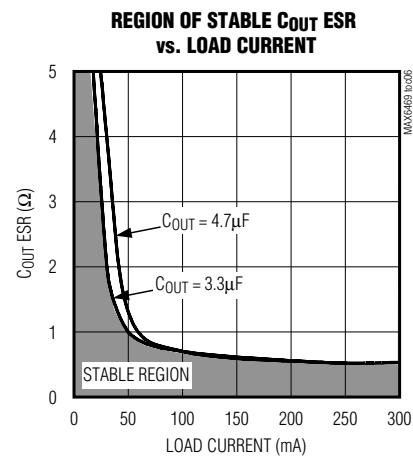

### Capacitor Selection and Regulator Stability

For stable operation over the full temperature range and with load currents up to 300mA, use a  $3.3\text{\mu F}$  (min) ceramic output capacitor with an ESR  $<0.2\Omega$ . To reduce noise and improve load transient response, stability, and power-supply rejection, use large output capacitor values such as  $10\text{\mu F}$ .

Note that some ceramic capacitors exhibit large capacitance and ESR variation with temperature. With capacitor dielectrics such as Z5U and Y5V, use  $4.7\text{\mu F}$  or more to ensure stability over temperature. With X7R or X5R capacitor dielectrics,  $3.3\text{\mu F}$  should be sufficient at all operating temperatures. Higher ESR capacitors require more capacitance to maintain stability. A graph of the Region of Stable ESR vs. Load Current is shown in the *Typical Operating Characteristics*.

To improve power-supply rejection and transient response, use a  $1\text{\mu F}$  capacitor between IN and GND.

The MAX6469–MAX6484 remain stable with purely resistive loads or current loads up to 300mA.

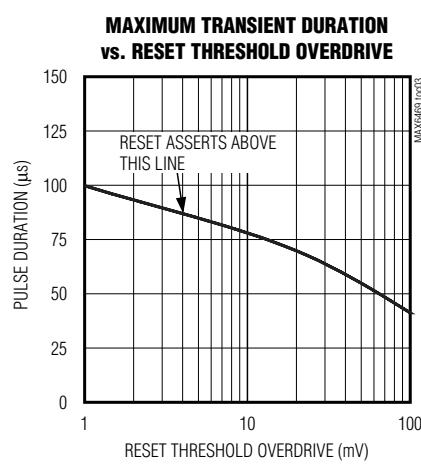

### Reset Transient Immunity

The reset circuit is relatively immune to short-duration, falling  $V_{\text{OUT}}$  transients. The *Typical Operating Characteristics* section shows a graph of the Maximum Transient Duration vs. Reset Threshold Overdrive for which reset is not asserted. The graph was produced using falling  $V_{\text{OUT}}$  transients starting at  $V_{\text{OUT}}$  and ending below the reset threshold by the magnitude indicated (reset threshold overdrive). The graph shows the maximum pulse width that a falling  $V_{\text{OUT}}$  transient can typically have without triggering a reset pulse. As the amplitude of the transient increases (i.e., goes further below the reset threshold), the maximum allowable pulse width decreases. Typically, a  $V_{\text{OUT}}$  transient that goes only 10mV below the reset threshold and lasts for  $75\text{\mu s}$  does not trigger a reset pulse.

# 300mA LDO Linear Regulators with Internal Microprocessor Reset Circuit

## Power Dissipation Consideration

For the SOT23 package, any pin except the SET pin can be used as a heatsink. If the SET pin is used as a heatsink, excessive parasitic capacitance can affect stability. For the QFN package, the exposed metal pad on the back side of a package connects to GND of the chip. This metal pad can be used as a heatsink.

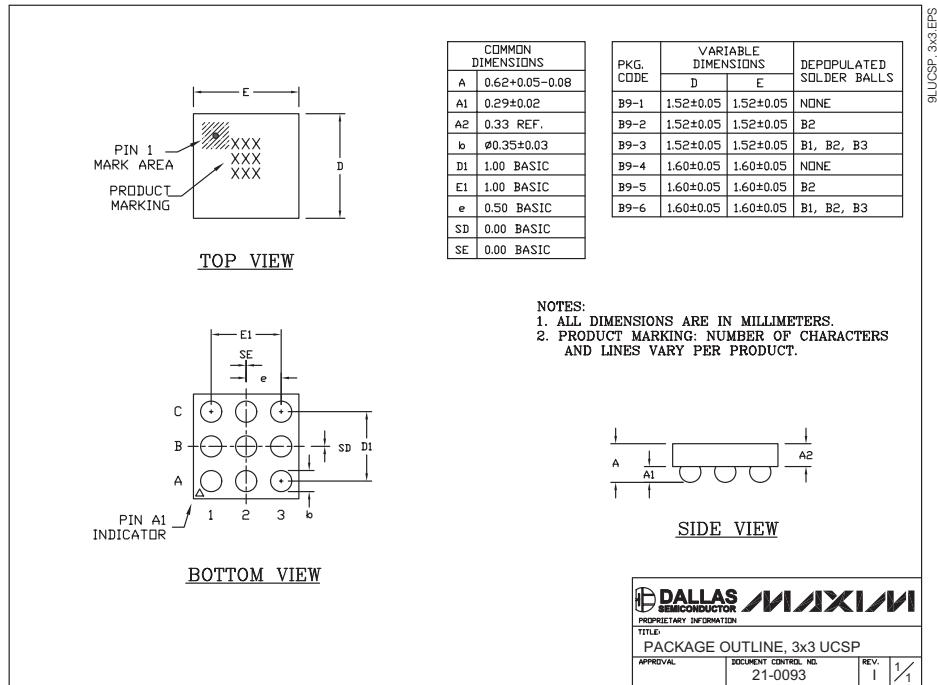

## UCSP Consideration

For general UCSP package information and PC layout considerations, refer to Maxim Application Note: *Wafer-Level Chip-Scale Package*.

## UCSP Reliability

The chip-scale package (UCSP) represents a unique packaging form factor that might not perform equally to a packaged product through traditional mechanical reliability tests. CSP reliability is integrally linked to the user's assembly methods, circuit-board material, and usage environment. The user should closely review these areas when considering a CSP package. Performance through operating life test and moisture resistance remains uncompromised, because it is primarily determined by the wafer-fabrication process.

Mechanical stress performance is a greater consideration for a CSP package. CSPs are attached through direct solder contact to the user's PC board, forgoing the inherent stress relief of a packaged product's lead frame. Solder-joint contact integrity must be considered. Information on Maxim's qualification plan, test data, and recommendations are detailed in the UCSP application note on Maxim's website at [www.maxim-ic.com](http://www.maxim-ic.com).

**Table 1. Output Voltage Suffix Guide**

| SUFFIX | OUTPUT VOLTAGE (V) |

|--------|--------------------|

| 15     | 1.5                |

| 16     | 1.6                |

| 17     | 1.7                |

| 18     | 1.8                |

| 19     | 1.9                |

| 20     | 2.0                |

| 21     | 2.1                |

| 22     | 2.2                |

| 23     | 2.3                |

| 24     | 2.4                |

| 25     | 2.5                |

| 26     | 2.6                |

| 27     | 2.7                |

| 28     | 2.8                |

| 285    | 2.85               |

| 29     | 2.9                |

| 30     | 3.0                |

| 31     | 3.1                |

| 32     | 3.2                |

| 33     | 3.3                |

**Note:** Factory-trimmed custom output voltages may be available; contact factory for availability.

**Table 2. Reset Threshold Accuracy Guide**

| SUFFIX | V <sub>OUT RESET</sub> TOLERANCE (%) |

|--------|--------------------------------------|

| A      | -7.5                                 |

| B      | -12.5                                |

**Table 3. Reset Timeout Delay Guide**

| SUFFIX | MINIMUM RESET TIMEOUT PERIOD (ms) |

|--------|-----------------------------------|

| D1     | 2.5                               |

| D2     | 20                                |

| D3     | 150                               |

| D4     | 1200                              |

# 300mA LDO Linear Regulators with Internal Microprocessor Reset Circuit

**MAX6469–MAX6484**

**Table 4. Standard Versions**

| DEVICE                | TOP MARK |

|-----------------------|----------|

| MAX6469TA15BD3        | ADO      |

| MAX6469TA18AD3        | ADP      |

| MAX6469TA25BD3        | ADQ      |

| MAX6469TA28AD3        | ACT      |

| MAX6469TA30BD3        | ADR      |

| MAX6469TA33AD3        | ADS      |

| MAX6469UT15BD3        | ABKS     |

| MAX6469UT18AD3        | ABKT     |

| MAX6469UT25BD3        | ABKU     |

| MAX6469UT28AD3        | ABFF     |

| MAX6469UT285AD3       | ABMZ     |

| MAX6469UT285BD3       | ABNA     |

| MAX6469UT30BD3        | ABKV     |

| MAX6469UT33AD3        | ABKW     |

| <b>MAX6470TA15BD3</b> | ADT      |

| MAX6470TA18AD3        | ADU      |

| MAX6470TA25BD3        | ADV      |

| MAX6470TA28AD3        | ADW      |

| MAX6470UT285AD3       | ABNB     |

| MAX6470UT285BD3       | ABNC     |

| MAX6470TA30BD3        | ADY      |

| MAX6470TA33AD3        | ACU      |

| MAX6470UT15BD3        | ABKX     |

| MAX6470UT18AD3        | ABKY     |

| MAX6470UT25BD3        | ABKZ     |

| MAX6470UT28AD3        | ABLA     |

| MAX6470UT30BD3        | ABLB     |

| MAX6470UT33AD3        | ABLC     |

| <b>MAX6471TA15AD3</b> | ADZ      |

| MAX6471TA18BD3        | AEA      |

| MAX6471TA25AD3        | AEB      |

| MAX6471TA28BD3        | AEC      |

| MAX6471TA30AD3        | AED      |

| MAX6471TA33BD3        | AEE      |

| MAX6471UT15AD3        | ABLD     |

| MAX6471UT18BD3        | ABLE     |

| MAX6471UT25AD3        | ABLF     |

| DEVICE                | TOP MARK |

|-----------------------|----------|

| MAX6471UT28BD3        | ABLG     |

| MAX6471UT30AD3        | ABLH     |

| MAX6471UT33BD3        | ABLI     |

| <b>MAX6472TA15AD3</b> | AEF      |

| MAX6472TA18BD3        | ACW      |

| MAX6472TA25AD3        | AEG      |

| MAX6472TA28BD3        | AEH      |

| MAX6472TA30AD3        | AEI      |

| MAX6472TA33BD3        | AEJ      |

| MAX6472UT15AD3        | ABLJ     |

| MAX6472UT18BD3        | ABFI     |

| MAX6472UT25AD3        | ABLK     |

| MAX6472UT28BD3        | ABLL     |

| MAX6472UT30AD3        | ABLM     |

| MAX6472UT33BD3        | ABLN     |

| <b>MAX6473TA15AD3</b> | AEK      |

| MAX6473TA18BD3        | AEL      |

| MAX6473TA25AD3        | AEM      |

| MAX6473TA28BD3        | AEN      |

| MAX6473TA30AD3        | AEO      |

| MAX6473TA33BD3        | AEP      |

| MAX6473UT15AD3        | ABLO     |

| MAX6473UT18BD3        | ABLP     |

| MAX6473UT25AD3        | ABLQ     |

| MAX6473UT28BD3        | ABLR     |

| MAX6473UT30AD3        | ABLS     |

| MAX6473UT33BD3        | ABLT     |

| <b>MAX6474TA15AD3</b> | AEQ      |

| MAX6474TA18BD3        | AER      |

| MAX6474TA25AD3        | AES      |

## 300mA LDO Linear Regulators with Internal Microprocessor Reset Circuit

Table 4. Standard Versions (continued)

| DEVICE                 | TOP MARK |

|------------------------|----------|

| MAX6474TA28BD3         | AET      |

| MAX6474TA30AD3         | AEU      |

| MAX6474TA33BD3         | AEV      |

| MAX6474UT15AD3         | ABLU     |

| MAX6474UT18BD3         | ABLV     |

| MAX6474UT25AD3         | ABLW     |

| MAX6474UT28BD3         | ABLX     |

| MAX6474UT30AD3         | ABLY     |

| MAX6474UT33BD3         | ABLZ     |

| <b>MAX6475</b> TA15BD3 | AEW      |

| MAX6475TA18AD3         | AEX      |

| MAX6475TA25BD3         | AEY      |

| MAX6475TA28AD3         | AEZ      |

| MAX6475TA30BD3         | AFA      |

| MAX6475TA33AD3         | ACZ      |

| MAX6475UT15BD3         | ABMA     |

| MAX6475UT18AD3         | ABMB     |

| MAX6475UT25BD3         | ABMC     |

| MAX6475UT28AD3         | ABMD     |

| MAX6475UT30BD3         | ABME     |

| MAX6475UT33AD3         | ABFL     |

| <b>MAX6476</b> TA15BD3 | AFB      |

| MAX6476TA18AD3         | AFC      |

| MAX6476TA25BD3         | AFD      |

| MAX6476TA28AD3         | AFE      |

| MAX6476TA30BD3         | AEF      |

| MAX6476TA33AD3         | AFG      |

| MAX6476UT15BD3         | ABMF     |

| MAX6476UT18AD3         | ABMG     |

| MAX6476UT25BD3         | ABMH     |

| MAX6476UT28AD3         | ABMI     |

| MAX6476UT30BD3         | ABMJ     |

| MAX6476UT33AD3         | ABMK     |

| <b>MAX6477</b> BL15BD3 | ABW      |

| MAX6477BL18AD3         | ABG      |

| MAX6477BL25BD3         | ABX      |

| MAX6477BL28AD3         | ABY      |

| MAX6477BL30BD3         | ABZ      |

| MAX6477BL33AD3         | ACA      |

| <b>MAX6478</b> BL15BD3 | ACB      |

| MAX6478BL18AD3         | ACC      |

| MAX6478BL25BD3         | ACD      |

| DEVICE                 | TOP MARK |

|------------------------|----------|

| MAX6478BL28AD3         | ACE      |

| MAX6478BL30BD3         | ACF      |

| MAX6478BL33AD3         | ACG      |

| <b>MAX6479</b> BL15AD3 | ACH      |

| MAX6479BL18BD3         | ACI      |

| MAX6479BL25AD3         | ACJ      |

| MAX6479BL28BD3         | ACK      |

| MAX6479BL30AD3         | ACL      |

| MAX6479BL33BD3         | ACM      |

| <b>MAX6480</b> BL15BD3 | ACN      |

| MAX6480BL18AD3         | ACO      |

| MAX6480BL25BD3         | ACP      |

| MAX6480BL28AD3         | ACQ      |

| MAX6480BL30BD3         | ACR      |

| MAX6480BL33AD3         | ABJ      |

| <b>MAX6481</b> BL15BD3 | ACS      |

| MAX6481BL18AD3         | ACT      |

| MAX6481BL25BD3         | ACU      |

| MAX6481BL28AD3         | ACV      |

| MAX6481BL30BD3         | ACW      |

| MAX6481BL33AD3         | ACX      |

| <b>MAX6482</b> BL15BD3 | ACY      |

| MAX6482BL18AD3         | ACZ      |

| MAX6482BL25BD3         | ADA      |

| MAX6482BL28AD3         | ADB      |

| MAX6482BL30BD3         | ADC      |

| MAX6482BL33AD3         | ADD      |

| <b>MAX6483</b> BL15BD3 | ADE      |

| MAX6483BL18AD3         | ADF      |

| MAX6483BL25BD3         | ADG      |

| MAX6483BL28AD3         | ADH      |

| MAX6483BL30BD3         | ADI      |

| MAX6483BL33AD3         | ADJ      |

| <b>MAX6484</b> BL15BD3 | ADK      |

| MAX6484BL18AD3         | ADL      |

| MAX6484BL25BD3         | ADM      |

| MAX6484BL28AD3         | ADN      |

| MAX6484BL30BD3         | ADO      |

| MAX6484BL33AD3         | ADP      |

Sample stock is generally available on standard versions only. Standard versions require a minimum order increment of 2.5k units. Nonstandard versions must be ordered in 10k-unit increments. Contact factory for availability.

# 300mA LDO Linear Regulators with Internal Microprocessor Reset Circuit

## Pin Configurations

**MAX6469-MAX6484**

TOP VIEW

UCSP DEVICES SHOWN AS

MOUNTED ON PC BOARD.

BALL SOLDERED DOWN.

## 300mA LDO Linear Regulators with Internal Microprocessor Reset Circuit

### Functional Diagrams

### Typical Operating Circuit

### Chip Information

TRANSISTOR COUNT: 1041

PROCESS: BiCMOS

# 300mA LDO Linear Regulators with Internal Microprocessor Reset Circuit

MAX6469–MAX6484

## **Ordering Information (continued)**

| PART                  | TEMP RANGE     | PIN-PACKAGE |

|-----------------------|----------------|-------------|

| <b>MAX6471UT__D-T</b> | -40°C to +85°C | 6 SOT23-6   |

| MAX6471TA__D*         | -40°C to +85°C | 8 Thin QFN  |

| <b>MAX6472UT__D-T</b> | -40°C to +85°C | 6 SOT23-6   |

| MAX6472TA__D*         | -40°C to +85°C | 8 Thin QFN  |

| <b>MAX6473UT__D-T</b> | -40°C to +85°C | 6 SOT23-6   |

| MAX6473TA__D*         | -40°C to +85°C | 8 Thin QFN  |

| <b>MAX6474UT__D-T</b> | -40°C to +85°C | 6 SOT23-6   |

| MAX6474TA__D*         | -40°C to +85°C | 8 Thin QFN  |

| <b>MAX6475UT__D-T</b> | -40°C to +85°C | 6 SOT23-6   |

| MAX6475TA__D*         | -40°C to +85°C | 8 Thin QFN  |

| <b>MAX6476UT__D-T</b> | -40°C to +85°C | 6 SOT23-6   |

| MAX6476TA__D*         | -40°C to +85°C | 8 Thin QFN  |

| <b>MAX6477BL__D-T</b> | -40°C to +85°C | 6 UCSP      |

| <b>MAX6478BL__D-T</b> | -40°C to +85°C | 6 UCSP      |

| <b>MAX6479BL__D-T</b> | -40°C to +85°C | 6 UCSP      |

| <b>MAX6480BL__D-T</b> | -40°C to +85°C | 6 UCSP      |

| <b>MAX6481BL__D-T</b> | -40°C to +85°C | 6 UCSP      |

| <b>MAX6482BL__D-T</b> | -40°C to +85°C | 6 UCSP      |

| <b>MAX6483BL__D-T</b> | -40°C to +85°C | 6 UCSP      |

| <b>MAX6484BL__D-T</b> | -40°C to +85°C | 6 UCSP      |

\*Future product—contact factory for availability.

**Note:** The first “\_\_” are placeholders for the output voltage levels of the devices. Desired output voltages are set by the suffix found in the Output Voltage Suffix Guide (Table 1). The third “\_” is a placeholder for the reset threshold accuracy. Desired reset threshold accuracy is set by the suffix found in the Reset Threshold Accuracy Guide (Table 2). The “\_” following the D is a placeholder for the reset timeout delay time. Desired reset timeout delay time is set by the suffix found in the Reset Timeout Delay Guide (Table 3). For example, the MAX6481BL30BD4-T has a 3.0V output voltage, 12.5% reset threshold tolerance, and a 1200ms (min) reset timeout delay. Sample stock is generally available on standard versions only (Table 4). Standard versions require a minimum order increment of 2.5k units. Nonstandard versions must be ordered in 10k-unit increments. Contact factory for availability.

## **300mA LDO Linear Regulators with Internal Microprocessor Reset Circuit**

### **Selector Guide**

| PART    | SET | SHDN | MR | FB | PUSH-PULL<br>RESET | OPEN-DRAIN<br>RESET | PACKAGE         |

|---------|-----|------|----|----|--------------------|---------------------|-----------------|

| MAX6469 | ✓   | ✓    | —  | —  | ✓                  | —                   | SOT23-6/8-QFN   |

| MAX6470 | ✓   | ✓    | —  | —  | —                  | ✓                   | SOT23-6/8-QFN   |

| MAX6471 | ✓   | —    | ✓  | —  | ✓                  | —                   | SOT23-6/8-QFN   |

| MAX6472 | ✓   | —    | ✓  | —  | —                  | ✓                   | SOT23-6/8-QFN   |

| MAX6473 | —   | ✓    | ✓  | —  | ✓                  | —                   | SOT23-6/8-QFN   |

| MAX6474 | —   | ✓    | ✓  | —  | —                  | ✓                   | SOT23-6/8-QFN   |

| MAX6475 | —   | ✓    | —  | ✓  | ✓                  | —                   | SOT23-6/8-QFN   |

| MAX6476 | —   | ✓    | —  | ✓  | —                  | ✓                   | SOT23-6/8-QFN   |

| MAX6477 | ✓   | ✓    | —  | —  | ✓                  | —                   | 3 x 3 UCSP B9-3 |

| MAX6478 | ✓   | ✓    | —  | —  | —                  | ✓                   | 3 x 3 UCSP B9-3 |

| MAX6479 | ✓   | —    | ✓  | —  | ✓                  | —                   | 3 x 3 UCSP B9-3 |

| MAX6480 | ✓   | —    | ✓  | —  | —                  | ✓                   | 3 x 3 UCSP B9-3 |

| MAX6481 | —   | ✓    | ✓  | —  | ✓                  | —                   | 3 x 3 UCSP B9-3 |

| MAX6482 | —   | ✓    | ✓  | —  | —                  | ✓                   | 3 x 3 UCSP B9-3 |

| MAX6483 | —   | ✓    | —  | ✓  | ✓                  | —                   | 3 x 3 UCSP B9-3 |

| MAX6484 | —   | ✓    | —  | ✓  | —                  | ✓                   | 3 x 3 UCSP B9-3 |

# 300mA LDO Linear Regulators with Internal Microprocessor Reset Circuit

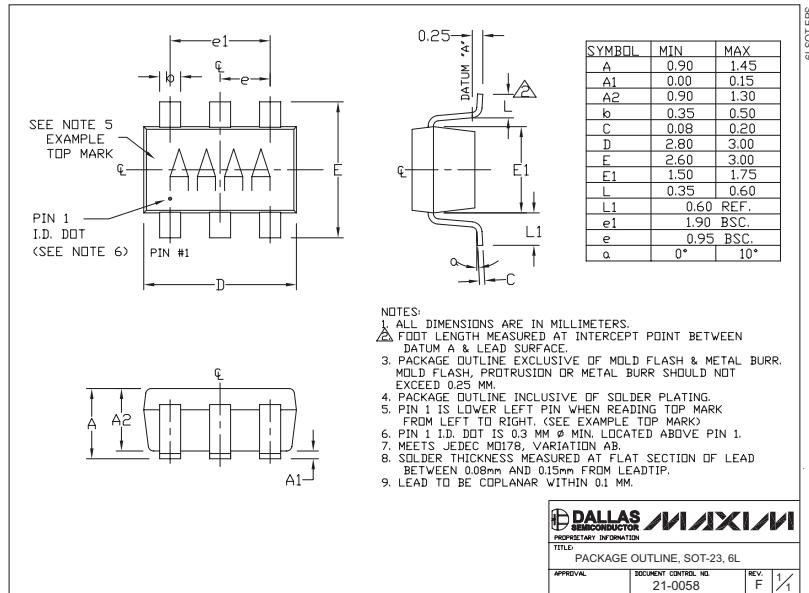

## Package Information

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to [www.maxim-ic.com/packages](http://www.maxim-ic.com/packages).)

**MAX6469-MAX6484**

# 300mA LDO Linear Regulators with Internal Microprocessor Reset Circuit

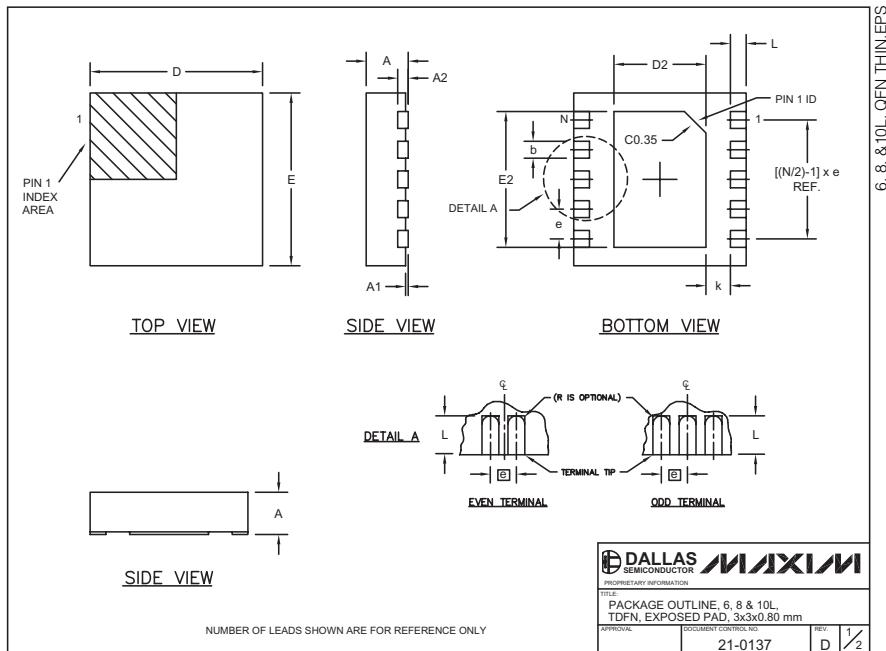

## Package Information (continued)

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information, go to [www.maxim-ic.com/packages](http://www.maxim-ic.com/packages).)

| COMMON DIMENSIONS |           |      |

|-------------------|-----------|------|

| SYMBOL            | MIN.      | MAX. |

| A                 | 0.70      | 0.80 |

| D                 | 2.90      | 3.10 |

| E                 | 2.90      | 3.10 |

| A1                | 0.00      | 0.05 |

| L                 | 0.20      | 0.40 |

| k                 | 0.25 MIN. |      |

| A2                | 0.20 REF. |      |

| PACKAGE VARIATIONS |    |           |           |          |                |           |

|--------------------|----|-----------|-----------|----------|----------------|-----------|

| PKG. CODE          | N  | D2        | E2        | e        | JEDEC SPEC     | b         |

| T633-1             | 6  | 1.50-0.10 | 2.30-0.10 | 0.95 BSC | MO229 / WEEA   | 0.40-0.05 |

| T833-1             | 8  | 1.50-0.10 | 2.30-0.10 | 0.65 BSC | MO229 / WEEC   | 0.30-0.05 |

| T1033-1            | 10 | 1.50-0.10 | 2.30-0.10 | 0.50 BSC | MO229 / WEED-3 | 0.25-0.05 |

NOTES:

1. ALL DIMENSIONS ARE IN mm. ANGLES IN DEGREES.

2. COPLANARITY SHALL NOT EXCEED 0.08 mm.

3. WARPAGE SHALL NOT EXCEED 0.10 mm.

4. PACKAGE LENGTH/PACKAGE WIDTH ARE CONSIDERED AS SPECIAL CHARACTERISTIC(S).

5. DRAWING CONFORMS TO JEDEC MO229, EXCEPT DIMENSIONS "D2" AND "E2".

6. "N" IS THE TOTAL NUMBER OF LEADS.

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

20 **Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600**