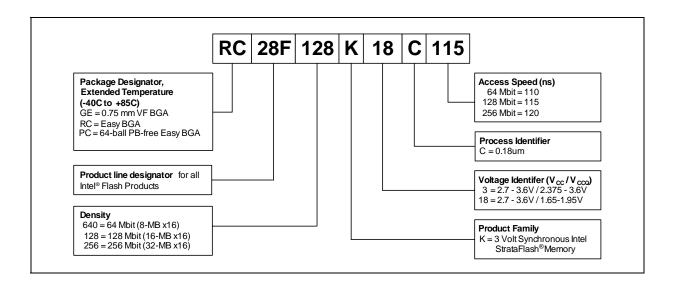

# Intel StrataFlash® Synchronous Memory (K3/K18)

28F640K3, 28F640K18, 28F128K3, 28F128K18, 28F256K3, 28F256K18 (x16)

#### **Datasheet**

### **Product Features**

#### Performance

- -110/115/120 ns Initial Access Speed for 64/128/256 Mbit Densities

- —25 ns Asynchronous Page-Mode Reads, 8 Words Wide

- —13 ns Synchronous Burst-Mode Reads, 8 or 16 Words Wide

- —32-Word Write Buffer

- -Buffered Enhanced Factory Programming

#### Software

- -25 μs (typ.) Program and Erase Suspend Latency Time

- —Flash Data Integrator (FDI), Common Flash Interface (CFI) Compatible

- —Programmable WAIT Signal Polarity

#### Ouality and Reliability

- -Operating Temperature:

- -40 °C to +85 °C

- —100K Minimum Erase Cycles per Block

- —0.18 μm ETOX™ VII Process

#### Architecture

- -Multi-Level Cell Technology: High Density at Low Cost

- —Symmetrical 64 K-Word Blocks

- —256 Mbit (256 Blocks)

- —128 Mbit (128 Blocks)

- —64 Mbit (64 Blocks)

- —Ideal for "CODE + DATA" applications

#### Security

- -2-Kbit Protection Register

- —Unique 64-bit Device Identifier

- —Absolute Data Protection with V<sub>PEN</sub> and

- -Individual and Instantaneous Block Locking, Unlocking and Lock-Down Capability

#### Packaging and Voltage

- —64-Ball Intel<sup>®</sup> Easy BGA Package (128-Mbit is also offered in a lead-free package)

- 56-and 79-Ball Intel® VF BGA Package

- $-V_{CC} = 2.70 \text{ V to } 3.60 \text{ V}$  $-V_{CCQ} = 1.65 \text{ to } 1.95 \text{ V}/2.375 \text{ to } 3.60 \text{ V}$

The Intel StrataFlash® Synchronous Memory (K3/K18) product line adds a high performance burst-mode interface and other additional features to the Intel StrataFlash® memory family of products. Just like its J3 counterpart, the K3/K18 device utilizes reliable and proven two-bit-percell technology to deliver 2x the memory in 1x the space, offering high density flash at low cost. This is Intel's third generation MLC technology, manufactured on 0.18 µm lithography, making it the most widely used and proven MLC product family on the market.

K3/K18 is a 3-volt device (core), but it is available with 3-volt (K3) or 1.8-volt (K18) I/O voltages. These devices are ideal for mainstream applications requiring large storage space for both code and data storage. Advanced system designs will benefit from the high performance page and burst modes for direct execution from the flash memory. Available in densities from 64 Mbit to 256 Mbit (32 Mbyte), the K3/K18 device is the highest density NOR-based flash component available today, just as it was when Intel introduced the original device in 1997.

Notice: This document contains information on new products in production. The specifications are subject to change without notice. Verify with your local Intel sales office that you have the latest datasheet before finalizing a design.

> Order Number: 290737-009 February 2005

Information in this document is provided in connection with Intel® products. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document. Except as provided in Intel's Terms and Conditions of Sale for such products, Intel assumes no liability whatsoever, and Intel disclaims any express or implied warranty, relating to sale and/or use of Intel products including liability or warranties relating to fitness for a particular purpose, merchantability, or infringement of any patent, copyright or other intellectual property right. Intel products are not intended for use in medical, life saving, or life sustaining applications.

Intel may make changes to specifications and product descriptions at any time, without notice.

Designers must not rely on the absence or characteristics of any features or instructions marked "reserved" or "undefined." Intel reserves these for future definition and shall have no responsibility whatsoever for conflicts or incompatibilities arising from future changes to them.

The 3 Volt Synchronous Intel StrataFlash® Memory may contain design defects or errors known as errata which may cause the product to deviate from published specifications. Current characterized errata are available on request.

Contact your local Intel sales office or your distributor to obtain the latest specifications and before placing your product order.

Copies of documents which have an ordering number and are referenced in this document, or other Intel literature may be obtained by calling 1-800-548-4725 or by visiting Intel's website at http://www.intel.com.

Copyright © Intel Corporation, 2005.

\*Other names and brands may be claimed as the property of others.

| 1.0          | Introduction                                                                          | 7             |

|--------------|---------------------------------------------------------------------------------------|---------------|

|              | 1.1 Nomenclature                                                                      |               |

| 2.0          | Functional Overview                                                                   |               |

|              | 2.1 High Performance Page/Burst Modes                                                 | 9<br>10<br>11 |

| 3.0          | Package Information                                                                   | 13            |

|              | 3.1 Easy BGA Package                                                                  | 14            |

| 4.0          | Ballout and Signal Description                                                        | 17            |

|              | <ul> <li>4.1 64-Ball Easy BGA Package for All Densities (1.0 mm Ball Pitch)</li></ul> | 18<br>19      |

| 5.0          | Maximum Ratings and Operating Conditions                                              | 21            |

|              | 5.1 Absolute Maximum Ratings                                                          |               |

| 6.0          | Electrical Specifications                                                             | 22            |

|              | 6.1 DC Current Characteristics                                                        | 22            |

| 7.0          | AC Characteristics                                                                    | 24            |

|              | 7.1 Read Operations                                                                   | 29<br>31      |

|              | 7.4 AC Test Conditions                                                                |               |

| 8.0          | Power and Reset                                                                       |               |

|              | 8.1 Power-Up/Down Characteristics                                                     |               |

|              | 8.2 Power Supply Decoupling                                                           | 33            |

|              | 8.3 Reset Characteristics                                                             |               |

| 9.0          | Bus Operations                                                                        |               |

| <del>-</del> | 9.1 Bus Operations Overview                                                           |               |

|              | 9.1.1 Read Mode                                                                       | 35            |

|              | 9.1.2 Write/Program                                                                   | 36            |

|      | 9.2                                  | 9.1.3 Output Disable                                                                                                                                                                                                                                                                          | 36<br>36                   |

|------|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

| 10.0 | Read                                 | d Modes                                                                                                                                                                                                                                                                                       | 39                         |

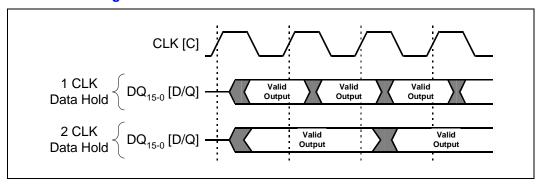

|      | 10.1<br>10.2<br>10.3                 | Asynchronous Page-Mode Read Synchronous Burst-Mode Read Read Configuration Register  10.3.1 Read Mode  10.3.2 Latency Count  10.3.3 WAIT Polarity  10.3.4 Data Hold  10.3.5 WAIT Delay  10.3.6 Burst Sequence  10.3.7 Clock Edge  10.3.8 Burst Length                                         |                            |

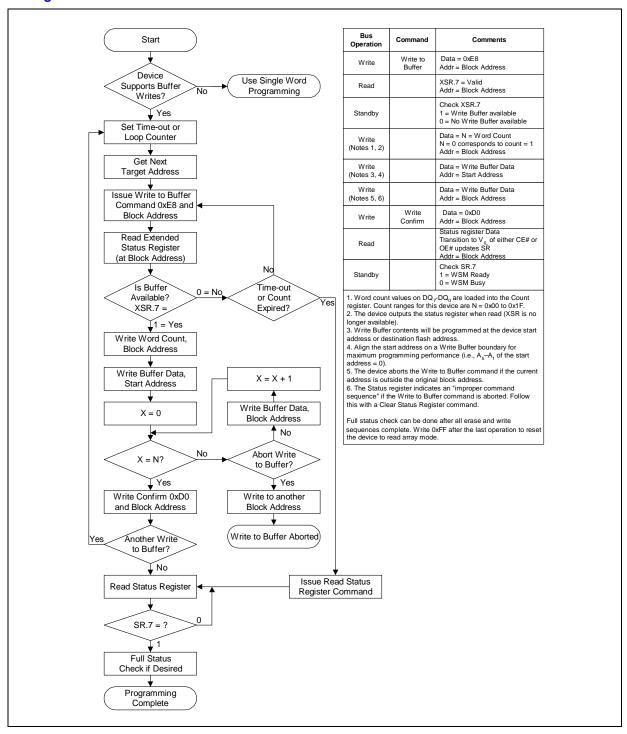

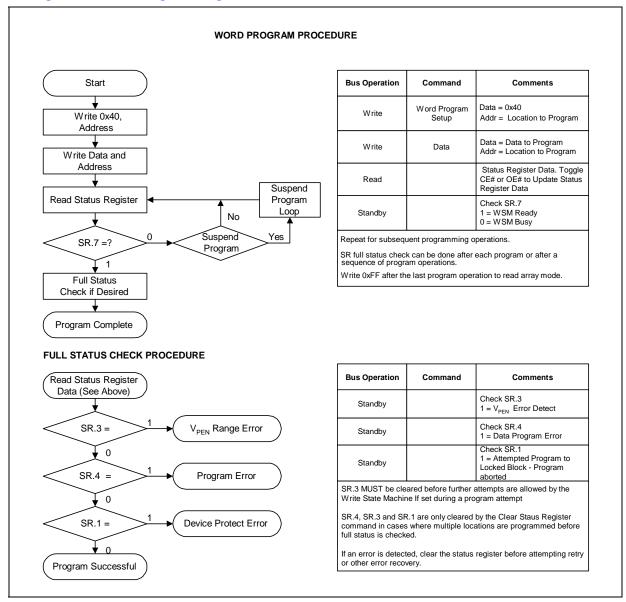

| 11.0 | Prog                                 | gram Modes                                                                                                                                                                                                                                                                                    | 4                          |

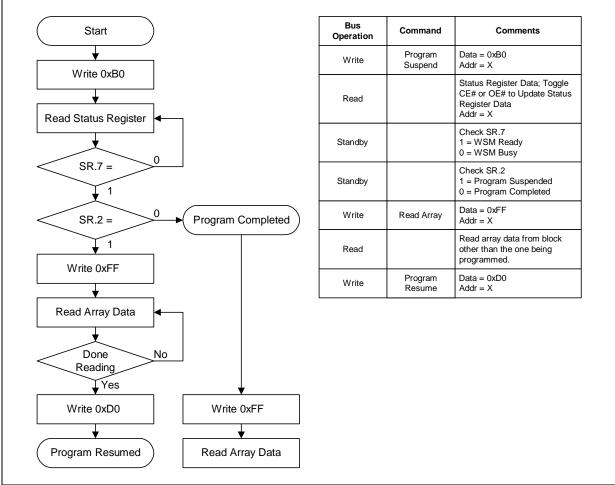

|      | 11.1<br>11.2<br>11.3<br>11.4<br>11.5 | Word Programming Write-Buffer Programming Program Suspend Program Resume Buffered Enhanced Factory Programming (Buffered-EFP) 11.5.1 Buffered-EFP Requirements and Considerations 11.5.2 Buffered-EFP Setup Phase 11.5.3 Buffered-EFP Program and Verify Phase 11.5.4 Buffered-EFP Exit Phase | 45<br>47<br>47<br>47<br>48 |

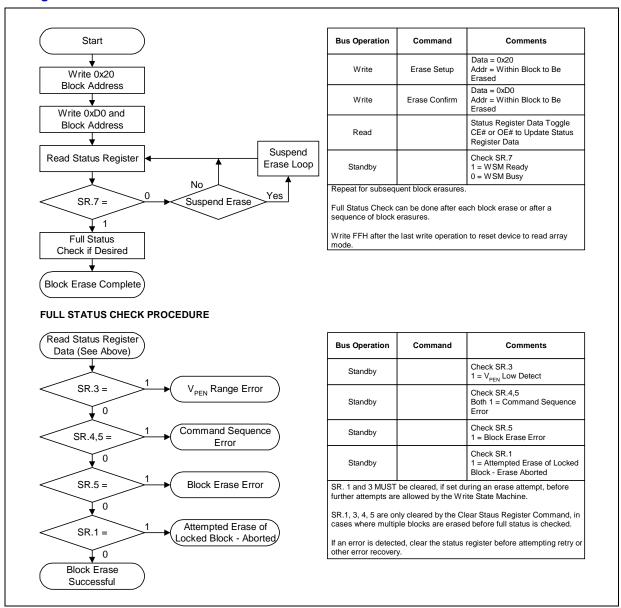

| 12.0 | Erase                                | se Mode                                                                                                                                                                                                                                                                                       | 50                         |

|      | 12.1<br>12.2<br>12.3                 | Block Erase<br>Erase Suspend<br>Erase Resume                                                                                                                                                                                                                                                  | 50                         |

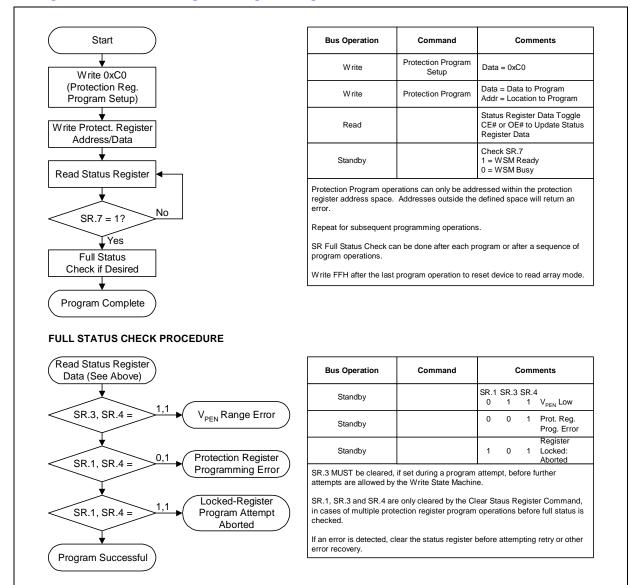

| 13.0 | Secu                                 | urity Modes                                                                                                                                                                                                                                                                                   | 52                         |

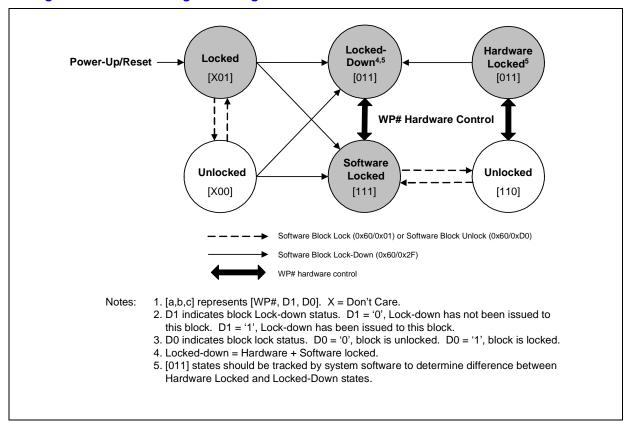

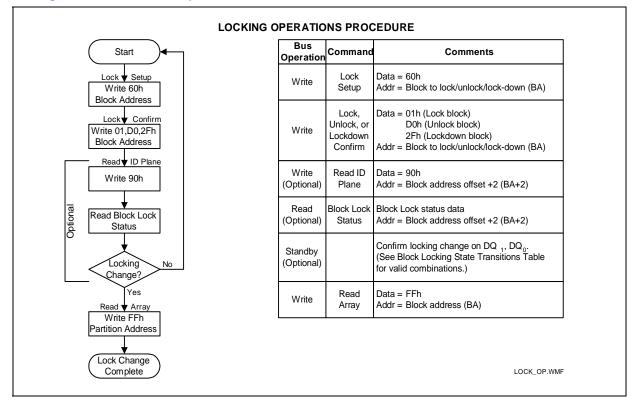

|      | 13.1                                 | Block Locking Operations                                                                                                                                                                                                                                                                      | 53<br>53<br>53             |

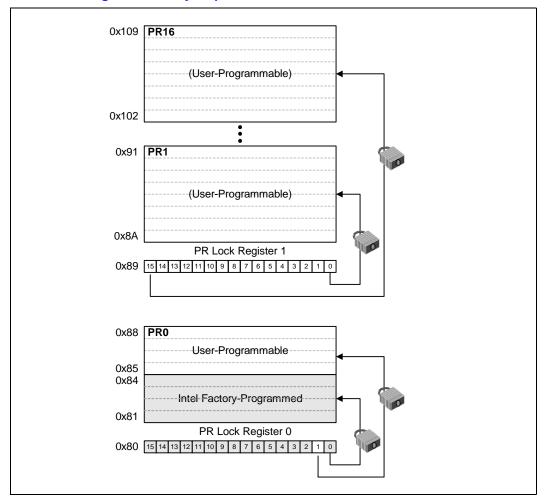

|      | 13.2                                 | Protection Registers                                                                                                                                                                                                                                                                          | 54<br>55<br>55             |

| 14.0 | 13.3                                 | Array Protection                                                                                                                                                                                                                                                                              |                            |

| 14.0 | <b>Spec</b><br>14.1                  | Read Status Register                                                                                                                                                                                                                                                                          |                            |

|      | 14.2                                 | 14.1.1 Clear Status Register                                                                                                                                                                                                                                                                  | 57                         |

|      |                                      |                                                                                                                                                                                                                                                                                               |                            |

### 28F640K3, 28F640K18, 28F128K3, 28F128K18, 28F256K3, 28F256K18

| 14         | 4.3 Read Query/CFI                     | 58 |

|------------|----------------------------------------|----|

|            | 4.4 STS Configuration (Easy BGA packag |    |

| Appendix A | Write State Machine (WSM)              | 59 |

| • •        | Common Flash Interface                 |    |

|            | Flowcharts                             |    |

|            | Additional Information                 |    |

| Appendix E | Ordering Information                   | 79 |

# **Revision History**

| Date of Revision | Revision | Description                                                                                                                                  |

|------------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------|

| 08/22/01         | -001     | Original Version                                                                                                                             |

| 09/24/01         | -002     | Corrected Typographical Errors in 11.0 AC Characteristics section.                                                                           |

| 09/27/01         | -003     | Change VFBGA Package from 64 to 56 ball package. Add ordering info in Appendix E.                                                            |

| 02/22/02         | -004     | Changes to ballouts per engineering review and editing/formatting updates.                                                                   |

| 06/17/02         | -005     | Changes to Iccr, elimination of Speed Bin 2, expansion of Vccq range.                                                                        |

| 06/11/03         | -006     | Corrections to Ordering Information, typcs, added Next-State Table, Appendix A info. Added table of Latency Count settings to Section 4.3.2. |

| 12/01/03         | -007     | Update PDF presentation.                                                                                                                     |

| 5/19/04          | -008     | Reformatted the document layout.                                                                                                             |

| 2/1/05           | -009     | Added lead-free information.                                                                                                                 |

### 1.0 Introduction

This document contains information pertaining to the Intel StrataFlash® Synchronous Memory (K3/K18) device. The purpose of this document is to describe the features, operations and specifications of these devices.

#### 1.1 Nomenclature

**3 Volt core:**  $V_{CC}$  range of 2.7 V - 3.6 V  $V_{CCQ}$  range of 2.375 V - 3.6 V  $V_{CCQ}$  range of 2.375 V - 3.6 V  $V_{CCQ}$  range of 1.65 V - 1.95 V For Easy BGA packages:  $A_{MIN} = A1$

For VF BGA packages:  $A_{MIN} = A0$

$A_{MAX}$ : For Easy BGA packages:

$\begin{array}{lll} 64 \ Mbit & A_{MAX} = A22 \\ 128 \ Mbit & A_{MAX} = A23 \\ 256 \ Mbit & A_{MAX} = A24 \\ For \ VF \ BGA \ packages: \\ 64 \ Mbit & A_{MAX} = A21 \\ 128 \ Mbit & A_{MAX} = A22 \\ 256 \ Mbit & A_{MAX} = A23 \end{array}$

**Block:** A group of flash cells that share common erase circuitry and erase simultaneously

**Program:** To write data to the flash array

**VPEN:** Refers to a signal or package connection name

$V_{PEN}$ : Refers to timing or voltage levels

CUI: Command User Interface

OTP: One Time Programmable

PR: Protection Register

PLR: Protection Lock Register

RFU: Reserved for Future Use

SR: Status Register

**RCR:** Read Configuration Register

WSM: Write State Machine

MLC: Multi-Level Cell

Set: Indicates a logic one (1)

Clear: Indicates a logic zero (0)

### 1.2 Conventions

0x: Hexadecimal prefix0b: Binary prefix

k (noun): 1,000 M (noun): 1,000,000 Byte: 8 bits Word: 16 bits Kword: 1,024 words Kb: 1,024 bits 1,024 bytes KB: Mb: 1,048,576 bits MB: 1,048,576 bytes

**Brackets:** Square brackets ([]) will be used to designate group membership or to define a

group of signals with similar function (i.e. A[21:1], SR[4,1] and D[15:0]).

### 2.0 Functional Overview

This section provides an overview of the K3/K18 device features and architecture.

The K3/K18 device product line adds a high performance burst-mode interface and other additional features to the Intel StrataFlash memory family of products. Just like its J3 counterpart, the K3/K18 utilizes reliable and proven two-bit-per-cell technology to deliver 2x the memory in 1x the space, offering high density flash at low cost. This is the third generation of Intel's multi-level cell (MLC) technology, manufactured on 0.18  $\mu$ m lithography, making it the most widely used and proven MLC product family on the market.

K3/K18 is a 3-volt device (core), but it is available with 3-volt (K3) or 1.8-volt (K18) I/O voltages. These devices are ideal for mainstream applications requiring large storage space for both code and data storage. Advanced system designs will benefit from the high performance page and burst modes for direct execution from the flash memory. Available in densities from 64 Mb to 256 Mbit (32 Mbyte), the K3/K18 device is the highest density NOR-based flash component available today, just as it was when Intel introduced the original device in 1997.

### 2.1 High Performance Page/Burst Modes

NOR-based flash is generally preferred over other architectures for its reliability and fast read speeds. Fast reads allow the application to execute code directly out of flash, rather than downloading to RAM for execution, saving the costs of redundant system memory and board space. The K3/K18 device sets the standard for fast read speeds by adding burst mode and utilizing an 8 word page mode. Burst mode increases throughput up to 76MB/s, effectively five times faster than asynchronous reads on standard flash memory, and supports performance up to 66 Mhz with zero wait states. Both page and burst modes also provide a high performance glueless interface to the Intel® StrongARM\* SA-1110 CPU (and future Intel® XScale processors) and many other microprocessors.

### 2.2 Single Chip Solution

In addition to code execution, many applications also have data storage needs. K3/K18 memory provides a single-chip solution for combined code execution and data storage. A single-chip solution is easy to implement by utilizing a unique hardware and software combination: the K3/K18 device and Intel<sup>®</sup> Persistent Storage Manager (Intel<sup>®</sup> PSM). Intel<sup>®</sup> PSM is royalty free when used with Intel<sup>®</sup> Flash, is an installable file system and block device driver for Microsoft Windows\* CE OS version 2.1 and later.

The Intel<sup>®</sup> PSM software is appropriate for any application using the Microsoft Windows CE operating system, including PC Companions, Set-Top Boxes, and other connected appliances and hand-held devices. Other operating system ports are also available. Intel<sup>®</sup> PSM is optimized for the Intel StrataFlash<sup>®</sup> Memory product line.

For wireless applications, Intel<sup>®</sup> Flash Data Integrator (Intel<sup>®</sup> FDI) Version 4 software provides the ability to manage data and files in Intel StrataFlash<sup>®</sup> Memory in an open architecture, including support for downloaded Java\* applets, Bluetooth\* file transfers, and voice recognition tags.

### 2.3 Packaging Options

The K3/K18 device is available in multiple packages: lead and lead-free Easy BGA and VF BGA, and Stacked Chip Scale Package (SCSP, stacking with SRAM or flash + flash). The 64-ball Easy BGA package provides SOP reliability and long-term footprint compatibility and cost in a chip scale package size. The VF BGA and SCSP offer small footprints for wireless applications.

Manufactured on the Intel 0.18-micron process technology, Intel StrataFlash® Memory offers unprecedented value and performance and reliability.

### 2.4 Product Highlights

High performance read modes: 8 or 16-word synchronous burst, 8-word page:

- 64 Mb: 110/25/13 ns (async/page/burst)

- 128 Mb: 115/25/13 ns (Offered in both lead and lead-free Easy BGA packages)

- 256 Mb:120/25/13 ns

- 2.7 V to 3.6 V Vcc operation

- 64-ball Easy BGA

- VF BGA packages and Stacked Chip Scale Package (SCSP)

- I/O V<sub>CCO</sub>: 2.375 V to 3.6 V (K3); 1.65 V to 1.95 V (K18)

- One-time-programmable protection registers (2Kbits)

- Program and Erase suspend capability

- Cost-effective multi-level cell architecture

- Royalty-free software support for most applications with Intel<sup>®</sup> PSM, Intel<sup>®</sup> FDI Version 4, or VFM

- Full extended operating temperature: -40° C to +85° C

- Proven reliability: 100,000 cycles, up to 20 years data retention

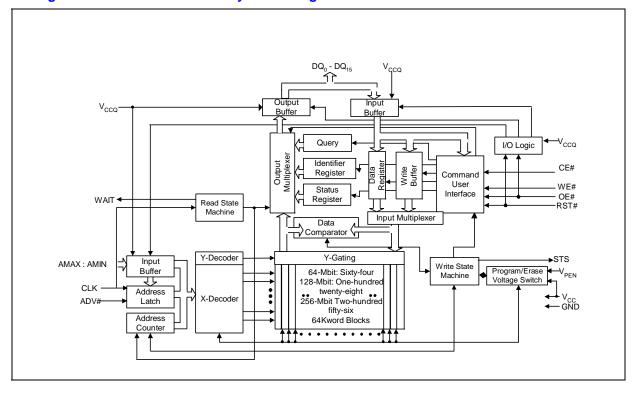

## 2.5 K3/K18 Block Diagram

Figure 1. K3/K18 Device Memory Block Diagram

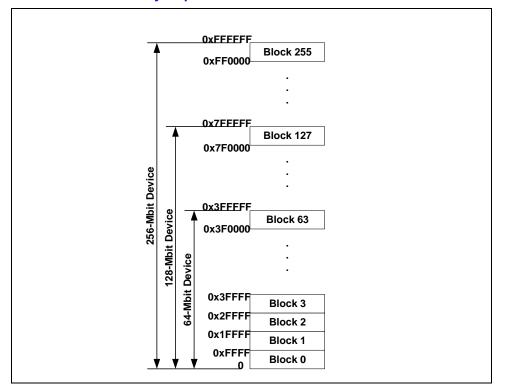

### 2.6 Memory Map

The K3/K18 device array is divided into symmetrical blocks that are 64-Kword in size. A 64 Mbit device contains 64 blocks, a 128 Mbit device contains 128 blocks and a 256 Mbit device contains 256 blocks. Flash cells within a block are organized by rows and columns. A block contains 512 rows by 128 words. The words on a row are divided into 16 eight-word groups. (See Figure 2.)

Figure 2. K3/K18 Device Memory Map

## 3.0 Package Information

### 3.1 Easy BGA Package

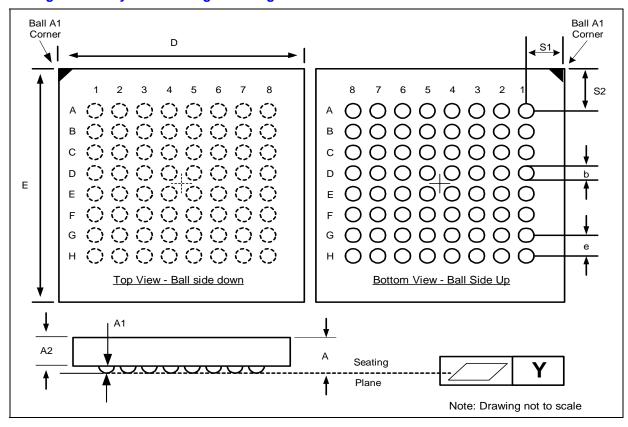

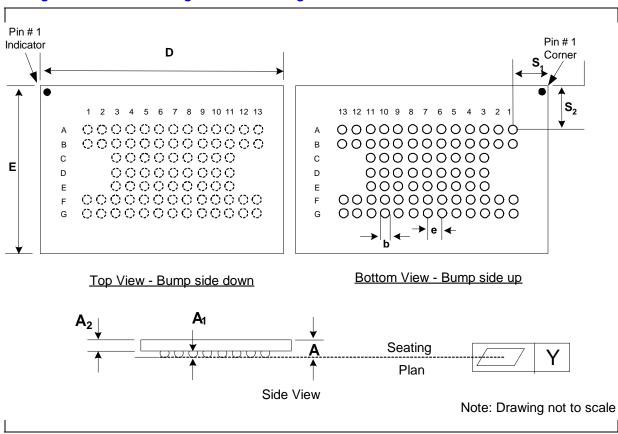

Figure 3. Easy BGA Package Drawing

Table 1. Easy BGA Package Dimensions (Sheet 1 of 2)

|                                            |        | Millimeters |        |        | Inches |        |        |        |

|--------------------------------------------|--------|-------------|--------|--------|--------|--------|--------|--------|

|                                            | Symbol | Min         | Nom    | Max    | Notes  | Min    | Nom    | Max    |

| Package Height                             | А      |             |        | 1.200  |        |        |        | 0.0472 |

| Ball Height                                | A1     | 0.250       |        |        |        | 0.0098 |        |        |

| Package Body Thickness                     | A2     |             | 0.780  |        |        |        | 0.0307 |        |

| Ball Width                                 | b      | 0.330       | 0.430  | 0.530  |        | 0.0130 | 0.0169 | 0.0209 |

| Package Body Width (64 Mb, 128 Mb, 256 Mb) | D      | 9.900       | 10.000 | 10.100 | 1      | 0.3898 | 0.3937 | 0.3976 |

| Package Body Length (64 Mb, 128 Mb)        | E      | 12.900      | 13.000 | 13.100 | 1      | 0.5079 | 0.5118 | 0.5157 |

| Package Body Length (256 Mb)               | E      | 14.900      | 15.000 | 15.100 | 1      | 0.5866 | 0.5906 | 0.5945 |

| Pitch                                      | [e]    |             | 1.000  |        |        |        | 0.0394 |        |

| Ball Count                                 | N      |             | 64     |        |        |        | 64     |        |

Table 1. Easy BGA Package Dimensions (Sheet 2 of 2)

|                                                    |        | Millimeters |       |       |       | Inches |        |        |

|----------------------------------------------------|--------|-------------|-------|-------|-------|--------|--------|--------|

|                                                    | Symbol | Min         | Nom   | Max   | Notes | Min    | Nom    | Max    |

| Seating Plane Coplanarity                          | Υ      |             |       | 0.100 |       |        |        | 0.0039 |

| Corner to Ball A1 Distance Along D (64/128/256 Mb) | S1     | 1.400       | 1.500 | 1.600 | 1     | 0.0551 | 0.0591 | 0.0630 |

| Corner to Ball A1 Distance Along E (64/128 Mb)     | S2     | 2.900       | 3.000 | 3.100 | 1     | 0.1142 | 0.1181 | 0.1220 |

| Corner to Ball A1 Distance Along E (256 Mb)        | S2     | 3.900       | 4.000 | 4.100 | 1     | 0.1535 | 0.1575 | 0.1614 |

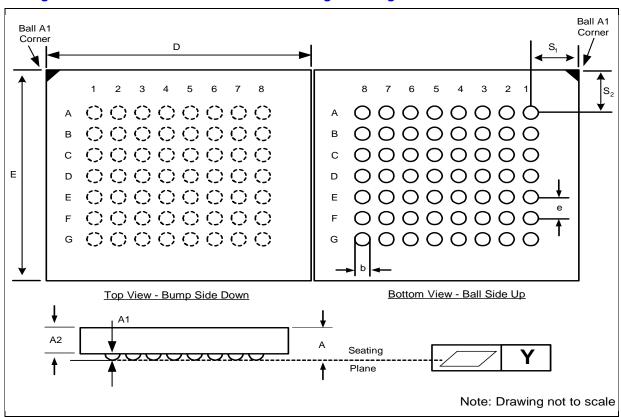

### 3.2 VF BGA for 64 Mbit and 128 Mbit Package

Figure 4. VF BGA for 64 Mb and 128 Mb Package Drawing

Table 2. VF BGA Package (64 Mb and 128 Mb) Dimensions (Sheet 1 of 2)

|                        |        | Millimeters |       |       |       | Inches |        |        |

|------------------------|--------|-------------|-------|-------|-------|--------|--------|--------|

|                        | Symbol | Min         | Nom   | Max   | Notes | Min    | Nom    | Max    |

| Package Height         | Α      |             |       | 1.000 |       |        |        | 0.0394 |

| Ball Height            | A1     | 0.150       |       |       |       | 0.0059 |        |        |

| Package Body Thickness | A2     |             | 0.665 |       |       |        | 0.0262 |        |

Table 2. VF BGA Package (64 Mb and 128 Mb) Dimensions (Sheet 2 of 2)

|                                                    | Millimeters |        |        |        | Inches |        |        |        |

|----------------------------------------------------|-------------|--------|--------|--------|--------|--------|--------|--------|

|                                                    | Symbol      | Min    | Nom    | Max    | Notes  | Min    | Nom    | Max    |

| Ball (Lead) Width                                  | b           | 0.325  | 0.375  | 0.425  |        | 0.0128 | 0.0148 | 0.0167 |

| Package Body Width (64 Mb)                         | D           | 7.600  | 7.700  | 7.800  | 1      | 0.2992 | 0.3031 | 0.3071 |

| Package Body Width (128 Mb)                        | D           | 10.900 | 11.000 | 11.100 | 1      | 0.4291 | 0.4331 | 0.4370 |

| Package Body Length (64 Mb, 128 Mb)                | E           | 8.900  | 9.000  | 9.100  | 1      | 0.3504 | 0.3543 | 0.3583 |

| Pitch                                              | [e]         |        | 0.750  |        |        |        | 0.0295 |        |

| Ball (Lead) Count                                  | N           |        | 56     |        |        |        | 56     |        |

| Seating Plane Coplanarity                          | Υ           |        |        | 0.100  |        |        |        | 0.0039 |

| Corner to Ball A1 Distance Along D (64 Mb)         | S1          | 1.125  | 1.225  | 1.325  | 1      | 0.0443 | 0.0482 | 0.0522 |

| Corner to Ball A1 Distance Along E (128 Mb)        | S1          | 2.775  | 2.875  | 2.975  | 1      | 0.1093 | 0.1132 | 0.1171 |

| Corner to Ball A1 Distance Along E (64 Mb, 128 Mb) | S2          | 2.150  | 2.250  | 2.350  | 1      | 0.0846 | 0.0886 | 0.0925 |

### 3.3 VF BGA for 256 Mbit Package

Figure 5. VF BGA Package 256 Mb Drawing

### 28F640K3, 28F640K18, 28F128K3, 28F128K18, 28F256K3, 28F256K18

Table 3. VF BGA (256 Mb) Dimensions

|                                    |        |        | Millimeters |        |       | Inches |        |        |

|------------------------------------|--------|--------|-------------|--------|-------|--------|--------|--------|

|                                    | Symbol | Min    | Nom         | Max    | Notes | Min    | Nom    | Max    |

| Package Height                     | А      |        |             | 1.000  |       |        |        | 0.0394 |

| Ball Height                        | A1     | 0.150  |             |        |       | 0.0059 |        |        |

| Package Body Thickness             | A2     |        | 0.665       |        |       |        | 0.0262 |        |

| Ball (Lead) Width                  | b      | 0.325  | 0.375       | 0.425  |       | 0.0128 | 0.0148 | 0.0167 |

| Package Body Width                 | D      | 14.400 | 14.500      | 14.600 | 1     | 0.5669 | 0.5709 | 0.5748 |

| Package Body Length                | Е      | 8.900  | 9.000       | 9.100  | 1     | 0.3504 | 0.3543 | 0.3583 |

| Pitch                              | [e]    |        | 0.750       |        |       |        | 0.0295 |        |

| Ball (Lead) Count                  | N      |        | 79          |        |       |        | 79     |        |

| Seating Plane Coplanarity          | Υ      |        |             | 0.100  |       |        |        | 0.0039 |

| Corner to Ball A1 Distance Along D | S1     | 2.650  | 2.750       | 2.850  | 1     | 0.1043 | 0.1083 | 0.1122 |

| Corner to Ball A1 Distance Along E | S2     | 2.150  | 2.250       | 2.350  | 1     | 0.0846 | 0.0886 | 0.0925 |

### 4.0 Ballout and Signal Description

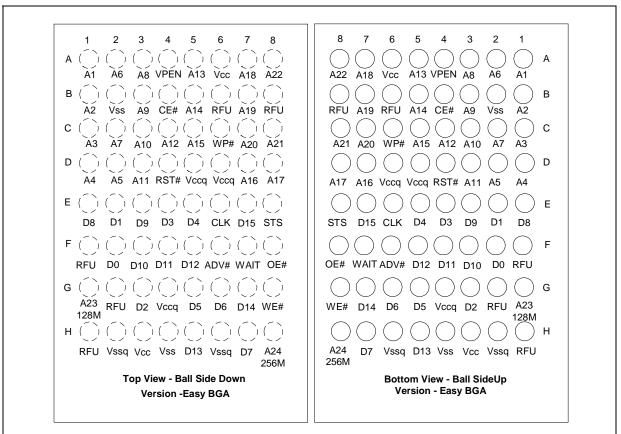

The K3/K18 device is available in a 64-ball Easy BGA package for the 64-, 128-, and 256 Mbit densities. See Figure 6.

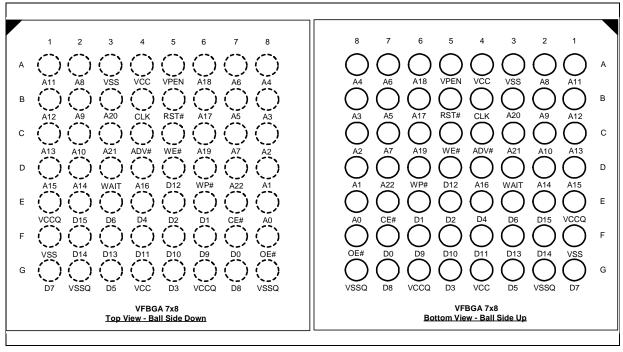

This device is also available in a 56-ball VF BGA package for the 64- and 128-Mbit densities and a 79-ball VF BGA package for the 256-Mbit density. See Figure 7 on page 18 and Figure 8 on page 19.

# 4.1 64-Ball Easy BGA Package for All Densities (1.0 mm Ball Pitch)

Figure 6. 64-Ball Easy BGA Package for All Available Densities (1.0 mm Ball Pitch)

#### NOTES:

- 1. Address A23 is valid only on 128-Mbit densities and above; otherwise, it is a no connect (NC).

- 2. Address A24 is valid only on 256-Mbit density; otherwise, it is a no connect (NC).

# 4.2 56-Ball VF BGA Package for 64- and 128-Mbit Density (0.75 mm Ball Pitch)

Figure 7. 56-Ball VF BGA Package 0.75 mm Ball Pitch (for 64- and 128-Mb Densities ONLY)

NOTE: Address A22 is only valid on 128-Mbit density; otherwise, it is a no connect (NC).

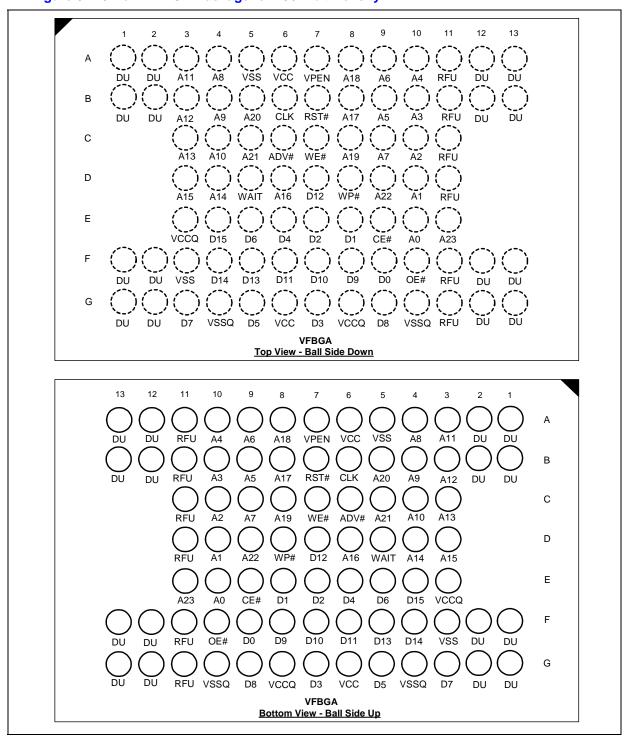

### 4.3 79-Ball VF BGA for 256-Mbit Density Package

Figure 8. 79-Ball VF BGA Package for 256-Mbit Density

# 4.4 Signal Descriptions

Table 4 describes the active signals used.

**Table 4. Signal Descriptions**

| Sym                                    | Type                 | Name and Function                                                                                                                                                                                                                                                                                                                                                             |

|----------------------------------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A[A <sub>MAX</sub> :A <sub>MIN</sub> ] | Input                | ADDRESS: Device address. Address internally latched during read/write operations. See nomenclature Section 1.2 for A <sub>MAX</sub> and A <sub>MIN</sub> values.                                                                                                                                                                                                              |

| D[15:0]                                | Input/<br>Output     | <b>DATA I/O:</b> Inputs data and commands during write operations, outputs data during read operations. Float when CE# or OE# are de-asserted. Data is internally latched during write operations.                                                                                                                                                                            |

| CE#                                    | Input                | <b>CHIP ENABLE:</b> Active-low; CE#-low selects the device. CE#-high deselects the device, places it in standby mode, and places data and WAIT outputs in a High-Z state.                                                                                                                                                                                                     |

| OE#                                    | Input                | <b>OUTPUT ENABLE:</b> Active-low; OE#-low enables the device's output data drivers during read cycles. OE#-high places the data outputs in a High-Z state.                                                                                                                                                                                                                    |

| WE#                                    | Input                | WRITE ENABLE: Active-low; WE# controls writes to the flash device. Address and data are latched on the rising edge of WE#.                                                                                                                                                                                                                                                    |

| RST#                                   | Input                | <b>RESET:</b> Active-low; resets internal circuitry and inhibits write operations. This provides data protection during power transitions. RST#-high enables normal operation. Exit from reset places the device in asynchronous read-array mode.                                                                                                                             |

| WP#                                    | Input                | WRITE PROTECT: Active-low; WP#-low enables the lock-down mechanism. Blocks locked down cannot be unlocked with the unlock command. WP#-high overrides the lock-down function enabling blocks to be erased or programmed through software.                                                                                                                                     |

| ADV#                                   | Input                | ADDRESS VALID: Active-low; during synchronous read operations, addresses are latched on the rising edge of ADV# or on the rising (or falling) edge of CLK, whichever occurs first.                                                                                                                                                                                            |

| VPEN                                   | Input                |                                                                                                                                                                                                                                                                                                                                                                               |

| CLK                                    | Input                | <b>CLOCK:</b> Synchronizes the device to the system's bus frequency in synchronous-read mode, and increments the internal address generator. During synchronous read operations, addresses are latched on ADV#'s rising edge or CLK's rising (or falling) edge, whichever occurs first. Connect this signal to VCC if the device will not be used in synchronous-read mode.   |

| STS                                    | Open Drain<br>Output | STATUS: Indicates the status of the internal state machine. When configured in level mode (default mode), it acts as a RY/BY# pin. When configured in one of its pulse modes, it can indicate program and/or erase completion. For alternate configurations of the STATUS pin, see the configuration commands. STS is to be tied to V <sub>CCQ</sub> with a pull-up resistor. |

| WAIT                                   | Output               | <b>WAIT:</b> Indicates invalid data in synchronous-read (burst) modes. WAIT is High-Z whenever CE# is de-asserted. WAIT is not gated by OE#.                                                                                                                                                                                                                                  |

| vcc                                    | Power                | <b>CORE POWER SUPPLY:</b> Core (logic) source voltage. Writes to the flash array are inhibited when $V_{CC} \le V_{LKO}$ . Device operation at invalid $V_{CC}$ voltages should not be attempted.                                                                                                                                                                             |

| VCCQ                                   | Power                | I/O POWER SUPPLY: I/O Output-driver source voltage.                                                                                                                                                                                                                                                                                                                           |

| VSS                                    | Power                | GROUND: Ground reference for device core power supply. Connect to system ground.                                                                                                                                                                                                                                                                                              |

| VSSQ                                   | Power                | I/O GROUND: I/O Ground reference for device I/O power supply. Connect to system ground.                                                                                                                                                                                                                                                                                       |

| DU                                     | _                    | <b>DO NOT USE:</b> Do not use this ball. This ball should not be connected to any power supplies, signals or other balls and must be left floating.                                                                                                                                                                                                                           |

| NC                                     | _                    | NO CONNECT: No internal connection; can be driven or floated.                                                                                                                                                                                                                                                                                                                 |

| RFU                                    | _                    | <b>RESERVED for FUTURE USE:</b> Balls designated as RFU are reserved by Intel for future device functionality and enhancement.                                                                                                                                                                                                                                                |

#### 5.0 **Maximum Ratings and Operating Conditions**

#### **Absolute Maximum Ratings** 5.1

The absolute maximum ratings are shown in Table 5.

Warning:

Stressing the device beyond the "Absolute Maximum Ratings" may cause permanent damage. These are stress ratings only. Operation beyond the "Operating Conditions" is not recommended and extended exposure beyond the "Operating Conditions" may affect device reliability.

#### **Table 5. Absolute Maximum Ratings**

| Parameter                                   | Maximum Rating                    | Notes |

|---------------------------------------------|-----------------------------------|-------|

| Temperature under bias                      | −40 °C to +85 °C                  |       |

| Storage temperature                         | −65 °C to +125 °C                 |       |

| Voltage on any signal (except VCC and VCCQ) | -0.5 V to V <sub>CCQ</sub> +0.5 V | 1,2   |

| VCC1 (K3) voltage                           | -0.2 V to +4.1 V                  | 1     |

| VCC2 (K18) voltage                          | -0.2 V to +3.8 V                  |       |

| VCCQ1 (K3) voltage                          | -0.2 V to +4.1 V                  | 1     |

| VCCQ2 (K18) voltage                         | -0.2 V to +2.45 V                 | 1     |

| Output short circuit current                | 100 mA                            | 3     |

#### **Operating Conditions 5.2**

| Symbol             | Parameter                         | Min     | Max  | Units  |

|--------------------|-----------------------------------|---------|------|--------|

| T <sub>A</sub>     | Operating Temperature             | -40     | +85  | °C     |

| V <sub>CC1</sub>   | Core Voltage (K3)                 | 2.70    | 3.60 | V      |

| V <sub>CC2</sub>   | Core Voltage (K18)                | 2.70    | 3.30 | V      |

| V <sub>CCQ1</sub>  | Vccq I/O Supply voltage (K3)      | 2.375   | 3.60 | V      |

| $V_{CCQ2}$         | Vccq I/O Supply voltage (K18)     | 1.65    | 1.95 | V      |

| Block Erase Cycles | All Blocks, V <sub>CC</sub> = 3 V | 100,000 |      | Cycles |

<sup>1.</sup> Specified voltages are with respect to V<sub>SS</sub>. Minimum DC voltage is -0.5 V on input/output signals and -0.2 V on V<sub>CC</sub> and V<sub>CCQ</sub>. During transitions, this level may undershoot to -2.0 V for periods <20 ns. Maximum DC voltage on V<sub>CC</sub> is V<sub>CC</sub> +0.5 V, which, during transitions, may overshoot to V<sub>CC</sub> +2.0 V for periods <20 ns. Maximum DC voltage on input/output signals and V<sub>CCQ</sub> is V<sub>CCQ</sub> +0.5 V, which, during transitions, may overshoot to  $V_{CCQ}$  +2.0 V for periods <20 ns. 2. Program/erase voltage is normally 2.7 V-3.6 V.

<sup>3.</sup> Output shorted for no more than one second. No more than one output shorted at a time.

#### **Electrical Specifications** 6.0

#### 6.1 **DC Current Characteristics**

Table 6. DC Current Characteristics

|                                          |                                                 | V <sub>CC</sub>            |                        | 2.7 V   | - 3.3 V  | 2.7 V - | - 3.6 V |      |                                                                                                                                                                                                     |  |

|------------------------------------------|-------------------------------------------------|----------------------------|------------------------|---------|----------|---------|---------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                          |                                                 | V <sub>CCQ</sub>           |                        | 1.65 V- | - 1.95 V | 2.375 V | - 3.6 V |      |                                                                                                                                                                                                     |  |

| Sym                                      | Pa                                              | rameter                    | Notes                  | Тур     | Max      | Тур     | Max     | Unit | Test Condition                                                                                                                                                                                      |  |

| I <sub>LI</sub>                          | Input Load Current                              |                            | 1                      |         | ±1       |         | ±1      | μΑ   | $\begin{aligned} & V_{CC} = V_{CCMAX}, \\ & V_{CCQ} = V_{CCQMAX}, \\ & V_{IN} = V_{CCQ} \text{ or GND} \end{aligned}$                                                                               |  |

| I <sub>LO</sub>                          | Output Lea                                      | kage Current               | 1                      |         | ±10      |         | ±10     | μΑ   | V <sub>CC</sub> = V <sub>CCMAX</sub> ,<br>V <sub>CCQ</sub> = V <sub>CCQMAX</sub> ,<br>V <sub>IN</sub> = V <sub>CCQ</sub> or GND                                                                     |  |

|                                          | V <sub>CC</sub>                                 | 64 Mbit,<br>128 Mbit       | 1, 2, 3,               | 30      | 55       | 30      | 55      | μΑ   | CMOS Inputs,<br>V <sub>CC</sub> = V <sub>CCMAX</sub> ,                                                                                                                                              |  |

| I <sub>ccs</sub>                         | Standby                                         | 256 Mbit                   | 4                      | 45      | 80       | 45      | 80      | μΑ   | V <sub>CCQ</sub> = V <sub>CCQMAX</sub> ,<br>Device is Disabled<br>RST# = V <sub>CCQ</sub> ±0.2V/GND±0.2V                                                                                            |  |

|                                          |                                                 | Single Word<br>Read        | onous<br>ode<br>1,3,4, | 10      | 73       | 10      | 78      | mA   | $V_{CC} = V_{CCMAX},$<br>$t_{ACC} = t_{AVQV}$                                                                                                                                                       |  |

|                                          | Average                                         | Asynchronous<br>Page Mode  |                        | 16      | 28       | 18      | 30      | mA   | $ \begin{array}{c} \text{8 Word} \\ \text{Read} \end{array} \begin{array}{c} t_{\text{ACC}} = t_{\text{AVQV}}, \\ t_{\text{APA}} = 25 \text{ ns}, \\ v_{\text{CC}} = v_{\text{CCMAX}} \end{array} $ |  |

| I <sub>CCR</sub>                         | V <sub>CC</sub> Read<br>Current                 | Synchronous                |                        | 24      | 38       | 32      | 46      | mA   | Burst   f = 66 MHz(K3),   50 MHz(K18)   V <sub>CC</sub> = V <sub>CCMAX</sub>   CE# = V <sub>IL</sub> ,                                                                                              |  |

|                                          |                                                 | Burst                      |                        | 28      | 40       | 36      | 48      | mA   | Burst $CE\# = V_{IL}$ , $OE\# = V_{IH}$ , $Inputs = V_{IH}$ or $V_{IL}$                                                                                                                             |  |

| I <sub>CCW</sub>                         | V <sub>CC</sub> Progra                          | am Current                 | 1, 4, 6,<br>7          | 50      | 80       | 40      | 70      | mA   | CMOS Inputs,<br>V <sub>PEN</sub> = V <sub>CC</sub>                                                                                                                                                  |  |

| I <sub>CCE</sub>                         | V <sub>CC</sub> Block Erase Current             |                            | 1, 4, 6,<br>7          | 50      | 80       | 40      | 70      | mA   | CMOS Inputs,<br>V <sub>PEN</sub> = V <sub>CC</sub>                                                                                                                                                  |  |

| I <sub>CCWS</sub> ,<br>I <sub>CCES</sub> | V <sub>CC</sub> Progra<br>Block Eras<br>Current | am Suspend or<br>e Suspend | 1, 4, 6,<br>7          |         | 20       |         | 10      | mA   | Device is enabled                                                                                                                                                                                   |  |

- All currents are RMS unless noted. Typical values at V<sub>CC</sub> = 3 V, T<sub>A</sub> = +25°C, best-case address pattern. Maximum values at V<sub>CC</sub> = 3.6 V, worst-case address pattern.

Includes STS.

- 3. CMOS inputs/outputs are either  $V_{CC} \pm 0.2 \text{ V}$  or  $V_{SS} \pm 0.2 \text{ V}$ . 4. Current values are specified over a specific temperature range (-40°C to +85°C).

- Current values are specified over a specific temperature range (~40 °C to 405 °C).

Sampled, not 100% tested.

I<sub>CCES</sub>, I<sub>CCWS</sub> are specified with device deselected. If device is read while in erase suspend/program suspend, current is I<sub>CCES</sub> plus I<sub>CCR</sub> or I<sub>CCWS</sub> plus I<sub>CCR</sub>.

V<sub>PEN</sub> < V<sub>PENLK</sub> inhibits block erase, program and lock-bit operations. Don't use V<sub>PEN</sub> outside its valid ranges.

#### Table 7. DC Voltage Characteristics

|                     | V <sub>CC</sub>                                                            |                   |      | 2.7 V – 3.3 V                   |                  | 2.7 V                    | 2.7 V – 3.6 V    |      |                                                                       |

|---------------------|----------------------------------------------------------------------------|-------------------|------|---------------------------------|------------------|--------------------------|------------------|------|-----------------------------------------------------------------------|

|                     | V <sub>CCQ</sub>                                                           |                   |      | 1.65 V – 1.95 V 2.375 V – 3.6 V |                  |                          |                  |      |                                                                       |

| Sym                 | Paramet                                                                    | er <sup>(1)</sup> | Note | Min                             | Max              | Min                      | Max              | Unit | Test Condition                                                        |

| V <sub>IL</sub>     | Input Low<br>Voltage                                                       | CMOS              | 7    | 0                               | 0.4              | 0                        | 0.4              | V    |                                                                       |

| V <sub>IH</sub>     | Input High<br>Voltage                                                      | CMOS              | 7    | V <sub>CCQ</sub><br>-0.4        | V <sub>CCQ</sub> | 2.3                      | V <sub>CCQ</sub> | V    |                                                                       |

| V <sub>OL</sub>     | Output Low<br>Voltage                                                      | CMOS              | 2, 4 |                                 | 0.2              |                          | 0.2              | V    | $V_{CC} = V_{CCMIN},$ $V_{CCQ} = V_{CCQMIN},$ $I_{OH} = 100 \mu A$    |

| V <sub>OH</sub>     | Output High<br>Voltage                                                     | CMOS              | 2, 4 | V <sub>CCQ</sub><br>-0.2        |                  | V <sub>CCQ</sub><br>-0.2 |                  | V    | $V_{CC} = V_{CCMIN},$ $V_{CCQ} = V_{CCQMIN},$ $I_{OH} = -100 \ \mu A$ |

| V <sub>PENLK</sub>  | V <sub>PEN</sub> Lock-Out                                                  |                   | 3, 5 |                                 | 1.0              |                          | 1.0              | V    |                                                                       |

| V <sub>PENH</sub>   | V <sub>PEN</sub> during Block<br>Erase, Program or Lock-<br>Bit operations |                   | 3, 5 | 1.65                            | 1.95             | 2.7                      | 3.6              | V    |                                                                       |

| $V_{LKO}$           | V <sub>CC</sub> Lockout Voltage                                            |                   | 3, 6 | 1.8                             |                  | 1.8                      |                  | V    |                                                                       |

| V <sub>CCQLKO</sub> | V <sub>CCQ</sub> Lockout                                                   | Voltage           | 3    | 1.0                             |                  | 1.0                      |                  | V    |                                                                       |

- 1. All currents are RMS unless noted. Typical values at typical  $V_{CC}$ ,  $T_A$  = +25°C.

- 2. Includes STS.

- 3. Sampled, not 100% tested.

- I<sub>CCES</sub>, I<sub>CCWS</sub> are specified with device deselected. If device is read while in erase suspend/program suspend, current is I<sub>CCES</sub> plus I<sub>CCR</sub> or I<sub>CCWS</sub> plus I<sub>CCR</sub>.

V<sub>PEN</sub> < V<sub>PENLK</sub> inhibits block erase, program and lock-bit operations. Don't use V<sub>PEN</sub> outside its valid

- 6. Block erases, programming and lock-bit configurations are inhibited when  $V_{CC}$ < $V_{LKO}$ , and not guaranteed in the range between  $V_{LKOMIN}$  and  $V_{CCMIN}$ , and above  $V_{CCMAX}$ .

7.  $V_{IL}$  can undershoot to -0.4V and  $V_{IH}$  can overshoot to  $V_{CCQ}$  +0.4V for durations of 20 ns or less.

# 7.0 AC Characteristics

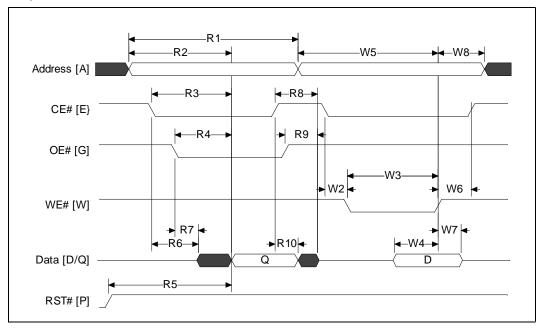

### **7.1** Read Operations

Table 8. AC Read Characteristics (Sheet 1 of 2)

|         |                     | vcc                                                         |          |      | 2.7 V  | - 3.3 V | 2.7 V   | - 3.6 V   |      |

|---------|---------------------|-------------------------------------------------------------|----------|------|--------|---------|---------|-----------|------|

|         |                     | VCCQ                                                        |          |      | 1.65 V | - 1.95V | 2.375 \ | / - 3.6 V |      |

| Num     | Sym                 | Parameter <sup>(3)</sup>                                    | Density  | Note | Min    | Max     | Min     | Max       | Unit |

| Asynch  | ronous S            | pecifications                                               |          |      | l      |         |         |           |      |

|         |                     |                                                             | 64 Mbit  |      | 110    |         | 110     |           | ns   |

| R1      | t <sub>AVAV</sub>   | Read cycle time                                             | 128 Mbit |      | 115    |         | 115     |           | ns   |

|         |                     |                                                             | 256 Mbit |      | 120    |         | 120     |           | ns   |

|         |                     |                                                             | 64 Mbit  |      |        | 110     |         | 110       | ns   |

| R2      | t <sub>AVQV</sub>   | Address to output delay                                     | 128 Mbit | 6    |        | 115     |         | 115       | ns   |

|         |                     |                                                             | 256 Mbit |      |        | 120     |         | 120       | ns   |

|         |                     |                                                             | 64 Mbit  |      |        | 110     |         | 110       | ns   |

| R3      | t <sub>ELQV</sub>   | CE# low to output delay                                     | 128 Mbit | 3    |        | 115     |         | 115       | ns   |

|         |                     |                                                             | 256 Mbit |      |        | 120     |         | 120       | ns   |

| R4      | t <sub>GLQV</sub>   | OE# low to output delay                                     |          | 3    |        | 30      |         | 25        | ns   |

|         |                     |                                                             | 64 Mbit  |      |        | 190     |         | 180       | ns   |

| R5      | t <sub>PHQV</sub>   | RST# high to output delay                                   | 128 Mbit |      |        | 220     |         | 210       | ns   |

|         |                     |                                                             | 256 Mbit |      |        | 220     |         | 210       | ns   |

| R6      | t <sub>ELQX</sub>   | CE# low to output in Low-Z                                  |          |      | 0      |         | 0       |           | ns   |

| R7      | t <sub>GLQX</sub>   | OE# low to output in Low-Z                                  |          | 3    | 0      |         | 0       |           | ns   |

| R8      | t <sub>EHQZ</sub>   | CE# high to output in High-Z                                |          | 5    |        | 25      |         | 25        | ns   |

| R9      | t <sub>GHQZ</sub>   | OE# high to output in High-Z                                |          | 5    |        | 25      |         | 25        | ns   |

| R10     | t <sub>OH</sub>     | Output hold from first occurring address, CE# or OE# change |          | 5    | 0      |         | 0       |           | ns   |

| R11     | t <sub>EHEL</sub>   | CE# high to CE# low                                         |          | 1    | 0      |         | 0       |           | ns   |

| R12     | t <sub>ELTL/H</sub> | CE# low to WAIT low                                         |          |      |        | 30      |         | 25        | ns   |

| R13     | t <sub>EHTZ</sub>   | CE# high to WAIT High-Z                                     |          |      |        | 30      |         | 25        | ns   |

| Latchin | g Specific          | cations                                                     |          |      | l.     |         |         |           |      |

| R101    | t <sub>AVVH</sub>   | Address setup to ADV# high                                  |          |      | 9      |         | 7       |           | ns   |

| R102    | t <sub>ELVH</sub>   | CE# low to ADV# high                                        |          |      | 9      |         | 7       |           | ns   |

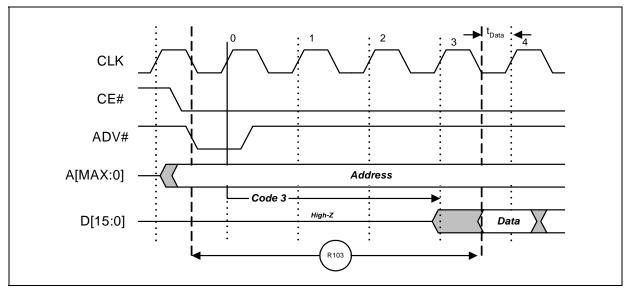

|         |                     |                                                             | 64 Mbit  |      |        | 110     |         | 110       | ns   |

| R103    | $t_{VLQV}$          | ADV# low to output delay                                    | 128 Mbit |      |        | 115     |         | 115       | ns   |

|         |                     |                                                             | 256 Mbit |      |        | 120     |         | 120       | ns   |

#### Table 8. AC Read Characteristics (Sheet 2 of 2)

|         |                     | vcc                            |         |      | 2.7 V  | - 3.3 V | 2.7 V   | - 3.6 V   |      |

|---------|---------------------|--------------------------------|---------|------|--------|---------|---------|-----------|------|

|         |                     | VCCQ                           |         |      | 1.65 V | - 1.95V | 2.375 \ | / - 3.6 V |      |

| Num     | Sym                 | Parameter <sup>(3)</sup>       | Density | Note | Min    | Max     | Min     | Max       | Unit |

| R104    | t <sub>VLVH</sub>   | ADV# pulse width low           |         |      | 12     |         | 10      |           | ns   |

| R105    | $t_{VHVL}$          | ADV# pulse width high          |         |      | 12     |         | 10      |           | ns   |

| R106    | t <sub>VHAX</sub>   | Address hold from ADV#<br>high |         | 4    | 10     |         | 8       |           | ns   |

| R108    | t <sub>APA</sub>    | Page address access            |         | 6    |        | 30      |         | 25        | ns   |

| Clock S | pecificati          | ons                            |         |      |        |         |         |           |      |

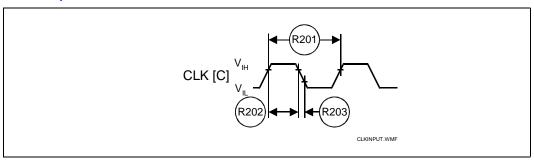

| R200    | f <sub>CLK</sub>    | CLK frequency                  |         |      |        | 50      |         | 66        | MHz  |

| R201    | t <sub>CLK</sub>    | CLK period                     |         | 7    | 20     |         | 15      |           | ns   |

| R202    | t <sub>CH/L</sub>   | CLK high/low time              |         | 7    | 7      |         | 4.5     |           | ns   |

| R203    | t <sub>CHCL</sub>   | CLK fall/rise time             |         | 7    |        | 3       |         | 3         | ns   |

| Synchro | onous Sp            | ecifications                   |         |      |        |         |         |           |      |

| R301    | t <sub>AVCH</sub>   | Address valid setup to CLK     |         |      | 9      |         | 7       |           | ns   |

| R302    | t <sub>VLCH</sub>   | ADV# low setup to CLK          |         |      | 9      |         | 7       |           | ns   |

| R303    | t <sub>ELCH</sub>   | CE# low setup to CLK           |         |      | 9      |         | 7       |           | ns   |

| R304    | t <sub>CHQV</sub>   | CLK to output delay            |         | 7    |        | 15      |         | 13        | ns   |

| R305    | t <sub>CHQX</sub>   | Output hold from CLK           |         |      | 3      |         | 3       |           | ns   |

| R306    | t <sub>CHAX</sub>   | Address hold from CLK          |         | 4    | 10     |         | 8       |           | ns   |

| R307    | t <sub>CHTL/H</sub> | CLK to WAIT delay              |         | 7, 8 |        | 15      |         | 13        | ns   |

| R312    | t <sub>CHVL</sub>   | CLK to ADV# low                |         |      | 3      |         | 3       |           | ns   |

#### NOTES:

- CE# high between synchronous reads = 15 ns. Data bus read voltage is ≤ V<sub>CCQ1</sub>.

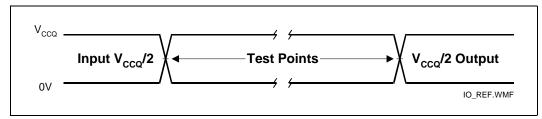

See Figure 17, "AC Input/Output Reference Waveform" on page 32 for timing measurements and maximum allowable input slew rate.

- 3. OE# may be delayed up to  $t_{\text{ELQV}} t_{\text{GLQV}}$  after CE# low without impact on  $t_{\text{ELQV}}$ .

4. Address hold in synchronous burst-mode is  $t_{\text{CHAX}}$  or  $t_{\text{VHAX}}$ , whichever timing specification is satisfied first.

- 5. Sampled, not 100% tested.

- 6. For devices configured to standard word read mode, R108(t<sub>APA</sub>) will equal R2(t<sub>AVQV</sub>).

- 7. The clock duty cycle should be 50% (approx.).

- 8. Applies only to subsequent synchronous reads.

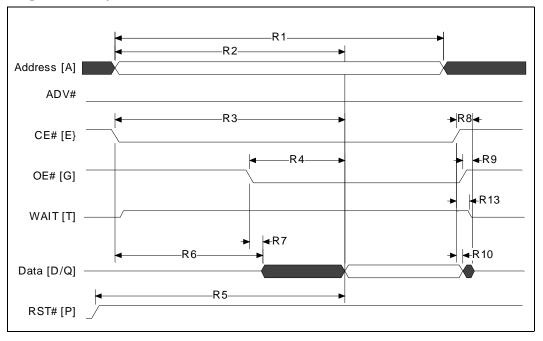

Figure 9. Single Word Asynchronous Read Waveform

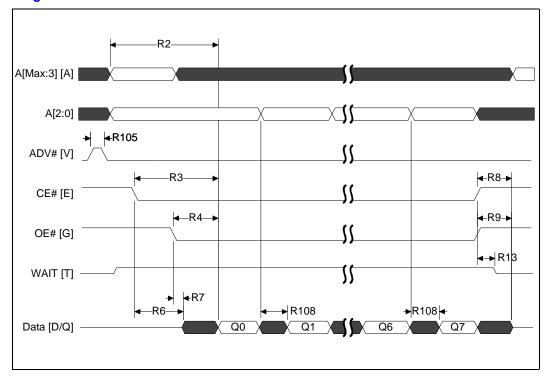

Figure 10. Page Mode Read Waveform

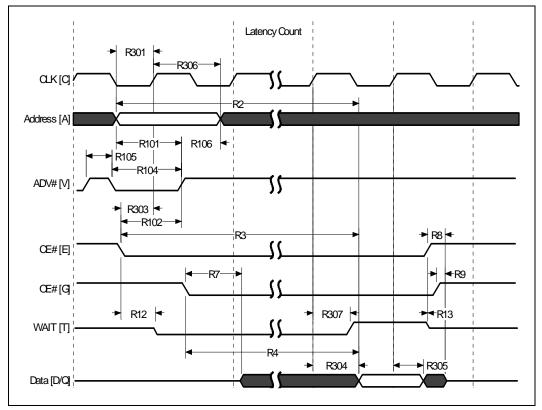

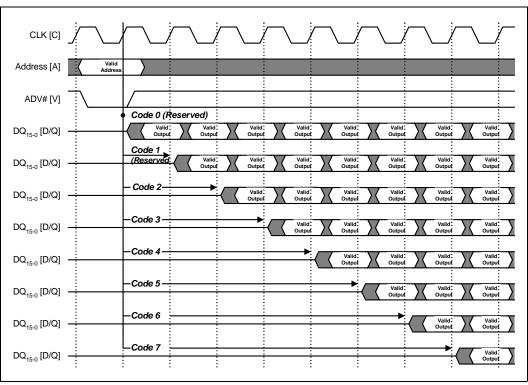

Figure 11. Single Word Burst Read Waveform

**NOTE:** WAIT (shown active low) can be configured to assert either during, or one clock before, valid data.

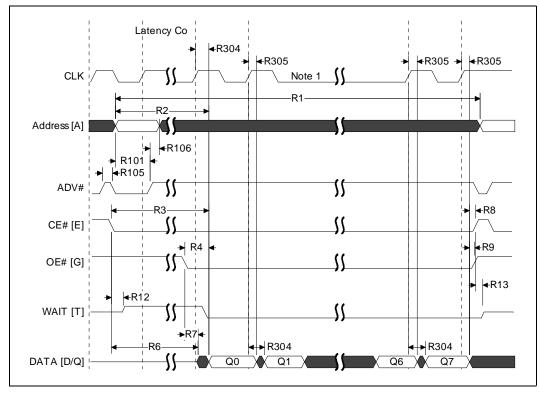

Figure 12. 8 Word Synchronous Burst Read Waveform

### NOTES:

- Section 4.9.13, "First Access Latency Count (CR.11-13)" on page 38 describes how to insert clock cycles during the initial access.

- 2. WAIT (shown active high) can be configured to assert either during or one clock before valid data.

Figure 13. Clock Input AC Waveform

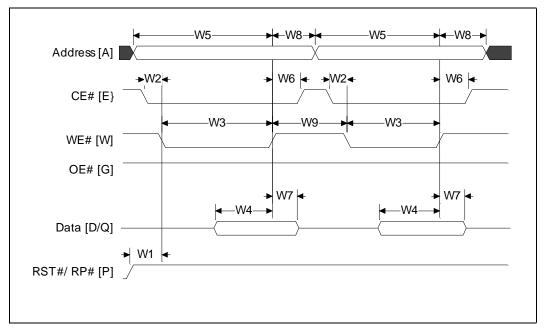

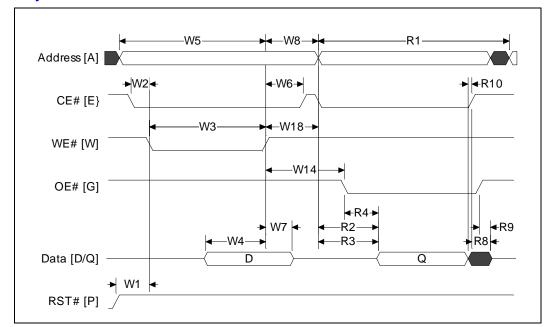

#### **Write Operation** 7.2

Table 9. Write Characteristics

|     |                                        | vcc                                                     |          |         | 2.7 - 3.3 V              | 2.7 - 3.6 V              |      |

|-----|----------------------------------------|---------------------------------------------------------|----------|---------|--------------------------|--------------------------|------|

|     |                                        | VCCQ                                                    |          |         | 1.65 - 1.95 V            | 2.375 - 3.6 V            |      |

| Num | Sym                                    | Parameter (1)                                           | Density  | Notes   | Min                      | Min                      | Unit |

|     |                                        |                                                         | 64 Mbit  |         | 190                      | 180                      | ns   |

| W1  | t <sub>PHWL</sub>                      | RST# high recovery to WE# low                           | 128 Mbit |         | 220                      | 210                      | ns   |

|     |                                        |                                                         | 256 Mbit | 2       | 220                      | 210                      | ns   |

| W2  | t <sub>ELWL</sub>                      | CE# setup to WE# low                                    |          |         | 0                        | 0                        | ns   |

| W3  | t <sub>WLWH</sub>                      | WE# write pulse width low                               |          | 3       | 60                       | 60                       | ns   |

| W4  | t <sub>DVWH</sub>                      | Data setup to WE# high                                  |          |         | 60                       | 60                       | ns   |

| W5  | t <sub>AVWH</sub>                      | Address setup to WE# high                               |          |         | 55                       | 55                       | ns   |

| W6  | t <sub>WHEH</sub>                      | CE# hold from WE# high                                  |          |         | 0                        | 0                        | ns   |

| W7  | t <sub>WHDX</sub>                      | Data hold from WE# high                                 |          |         | 0                        | 0                        | ns   |

| W8  | t <sub>WHAX</sub>                      | Address hold from WE# high                              |          |         | 0                        | 0                        | ns   |

| W9  | t <sub>WHWL</sub>                      | WE# pulse width high                                    |          | 4, 5    | 35                       | 30                       | ns   |

| W10 | t <sub>VPWH</sub> (t <sub>VPEH</sub> ) | V <sub>PEN</sub> Setup to WE# (CE#)<br>Going High       |          |         | 0                        | 0                        | ns   |

| W11 | t <sub>QVVL</sub>                      | V <sub>PEN</sub> Hold from Valid SRD,<br>STS Going High |          | 3, 7    | 0                        | 0                        |      |

| W12 | t <sub>QVBL</sub>                      | WP# hold from Status read                               |          | 2, 3, 6 | 0                        | 0                        | ns   |

| W13 | t <sub>BHWH</sub>                      | WP# setup to WE# high                                   |          | 2       | 200                      | 200                      | ns   |

| W14 | t <sub>WHGL</sub>                      | Write recovery before read                              |          |         | 35                       | 35                       | ns   |

| W16 | t <sub>WHQV</sub>                      | WE# high to data valid                                  |          | 2       | t <sub>AVQV</sub><br>+40 | t <sub>AVQV</sub><br>+40 | ns   |

#### NOTES:

- Read timing characteristics during block erase, program and lock-bit operations are the same as during read-only operations. Refer to AC Characteristics Read-Only Operations.

- 2. A write operation can be initiated or terminated with either CE# or WE#.

- 3. Sampled, not 100% tested.

- Sampled, not 100% tested.

Write pulse width low (t<sub>WLWH</sub>) is defined from CE# or WE# going low (whichever goes low last) to CE# or WE# going high (whichever goes high first). Hence, t<sub>WLWH</sub> = t<sub>ELEH</sub> = t<sub>WLEH</sub> = t<sub>ELWH</sub>.

Write pulse width high (t<sub>WHWL</sub>) is defined from CE# or WE# going high (whichever goes high first) to CE# or WE# going low (whichever goes low last). Hence, t<sub>WHWL</sub> = t<sub>EHEL</sub> = t<sub>WHEL</sub> = t<sub>EHWL</sub>.

For array access, t<sub>AVQV</sub> is required in addition to t<sub>WHGL</sub> for any accesses after a write.

STS timings are based on STS configured in its RY/BY# default mode.

Figure 14. Write to Write Waveform

Figure 15. Asynchronous Read to Write Waveform

Figure 16. Asynchronous Write to Read Waveform

#### 7.3 **Block Erase and Program Operation Performance**

**Table 10. Block Erase and Program Operation Performance**

| #  | Sym                                     | Parameter                                                     | Notes   | Min | Тур  | Max | Unit |

|----|-----------------------------------------|---------------------------------------------------------------|---------|-----|------|-----|------|

|    | t <sub>WHQV1</sub> , t <sub>EHQV1</sub> | Write Buffer Program Time (Time to program 64 bytes/32 words) | 4, 5, 6 |     | 320  | 960 | μs   |

|    | t <sub>WHQV2</sub> , t <sub>EHQV2</sub> | Word Program Time (Using Word Program Command)                | 4       |     | 150  | 450 | μs   |

|    | t <sub>WHQV3</sub> , t <sub>EHQV3</sub> | Block Program Time (Using Write-to- Buffer Command)           | 4       |     | 0.7  | 2.1 | sec  |

|    | t <sub>BBWB</sub>                       | Buffered-EFP Buffer Write Time                                | 1, 3, 4 |     | 288  | 864 | μs   |

| Wo | t <sub>BWB</sub>                        | Buffered-EFP Block Write Time                                 | 1, 3, 4 |     | 0.58 | 1.7 | sec  |

|    | t <sub>BEFP-SETUP</sub>                 | Buffered-EFP Set-up Time                                      | 1, 3, 4 |     | N/A  | 5.0 | μs   |

|    | t <sub>WHQV4</sub> , t <sub>EHQV4</sub> | Block Erase Time                                              | 4       |     | 1.0  | 4.0 | sec  |

|    | t <sub>WHRH1</sub> , t <sub>EHRH1</sub> | Program Suspend Latency Time to Read                          |         |     | 20   | 25  | μs   |

|    | t <sub>WHRH</sub> , t <sub>EHRH</sub>   | Erase Suspend Latency Time to Read                            |         |     | 20   | 25  | μs   |

| WY | t <sub>STS</sub>                        | STS Pulse Width Low Time                                      | 4       |     | 250  |     | ns   |

#### NOTES:

- 1. Typical values measured at T<sub>A</sub>= +25°C and nominal voltages. Assumes corresponding lock-bits are not set. Subject to change based on device characterization.

2. These performance numbers are valid for all speed versions.

- These performance numbers are valid for all speed versions.

Sampled but not 100% tested.

Excludes system level overhead.

These values are valid when the buffer is full, and the start address is aligned on 32-bit boundary.

Effective word program time (t<sub>WHQV1</sub>, t<sub>EHQV1</sub>) is 10.0 µs/word (typ).

### 7.4 AC Test Conditions

Figure 17. AC Input/Output Reference Waveform

**NOTE:** AC test inputs are driven at  $V_{CCQ}$  for Logic "1" and 0.0 V for Logic "0." Input/output timing begins or ends at  $V_{CCQ}/2$ . Input rise and fall times (10% to 90%) < 5 ns. Worst case speed occurs at  $V_{CC} = V_{CCMIN}$ .

**Figure 18. Transient Equivalent Testing Load Circuit**

**NOTE:**  $C_L$  included jig capacitance.

**Table 11. Test Configuration Component Value for Worst Case Speed Conditions**

| Test Configuration                | C <sub>L</sub> (pF) | R <sub>1</sub> | R <sub>2</sub> |

|-----------------------------------|---------------------|----------------|----------------|

| V <sub>CCQMIN</sub> Standard Test | 30                  | 25K            | 25K            |

**NOTE:** C<sub>L</sub> includes jig capacitance.

### 7.5 Capacitance

**Table 12. Capacitance**

| Sym              | Parameter <sup>(1)</sup> | Тур | Max | Unit | Condition                |

|------------------|--------------------------|-----|-----|------|--------------------------|

| C <sub>IN</sub>  | Input Capacitance        | 6   | 8   | pF   | V <sub>IN</sub> = 0.0 V  |

| C <sub>OUT</sub> | Output Capacitance       | 8   | 12  | pF   | V <sub>OUT</sub> = 0.0 V |

NOTES:

- 1.  $T_A = +25$ °C, f = 1 MHz.

- 2. Sampled, not 100% tested.

### 8.0 Power and Reset

This section provides an overview of some system level considerations in regards to the flash device. This section provides a brief description of power-up, power-down, decoupling and reset design considerations.

### 8.1 Power-Up/Down Characteristics

In order to prevent any condition that may result in a spurious write or erase operation, it is recommended to power-up and power-down  $V_{CC}$  and  $V_{CCQ}$  together. It is also recommended to power-up  $V_{PEN}$  with or slightly after  $V_{CC}$ . Conversely,  $V_{PEN}$  must power down with or slightly before  $V_{CC}$ .

### 8.2 Power Supply Decoupling

When the device is enabled, many internal conditions change. Circuits are energized, charge pumps are switched on, and internal voltage nodes are ramped. All of this internal activities produce transient signals. The magnitude of the transient signals depends on the device and system loading. To minimize the effect of these transient signals, a 0.1  $\mu F$  ceramic capacitor is required across each  $V_{CC}/V_{SS}$  and  $V_{CCQ}/V_{SSQ}$  signal. Capacitors should be placed as close as possible to device connections.

Additionally, for every eight flash devices, a 4.7  $\mu$ F electrolytic capacitor should be placed between  $V_{CC}$  and  $V_{SS}$  at the power supply connection. This 4.7  $\mu$ F capacitor should help overcome voltage slumps caused by PCB (print circuit board) trace inductance.

### 8.3 Reset Characteristics

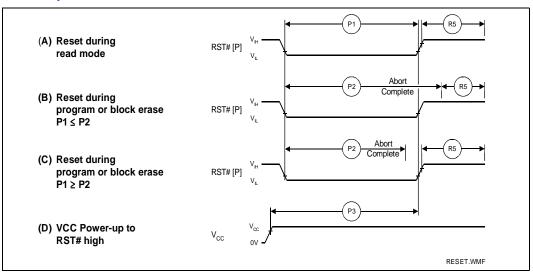

By holding the flash device in reset during power-up and power-down transitions, invalid bus conditions may be masked. The flash device enters reset mode when RST# is driven low. In reset, internal flash circuitry is disabled and outputs are placed in a high-impedance state. After return from reset, a certain amount of time is required before the flash device is able to perform normal operations. After return from reset, the flash device defaults to asynchronous page mode. If RST# is driven low during a program or erase operation, the program or erase operation will be aborted and the memory contents at the aborted block or address are no longer valid. See Figure 19, "Reset Operation Waveforms" on page 34 for detailed information regarding reset timings.

#### **Reset Operation** 8.4

**Figure 19. Reset Operation Waveforms**

**Table 13. Reset Specifications**

| Num | Symbol             | Parameter                                               | Notes   | Min | Max | Unit |

|-----|--------------------|---------------------------------------------------------|---------|-----|-----|------|

| P1  | t <sub>PLPH</sub>  | RST# pulse width low                                    | 1,2,3,4 | 100 |     | ns   |

| P2  | DO 4               | RST# low to device reset during erase                   | 1,3,4,7 |     | 20  |      |

| F 2 | <sup>T</sup> PLRH  | RST# low to device reset during program                 | 1,3,4,7 |     | 10  | μs   |

| P3  | t <sub>VCCPH</sub> | V <sub>CC</sub> Power Valid to RST# de-assertion (high) | 1,4,5,6 | 60  |     |      |

- 1. These specifications are valid for all product versions (packages and speeds).

- 2. The device may reset if t<sub>PLPH</sub> is <t<sub>PLPH</sub> MIN, but this is not guaranteed.

- 3. Not applicable if RST# is tied to Vcc.

- 4. Sampled, but not 100% tested.

- 5. If RST# is tied to the  $V_{CC}$  supply, device will not be ready until  $t_{VCCPH}$  after  $V_{CC} \ge V_{CC}$  min. 6. If RST# tied to any supply/signal with  $V_{CCQ}$  voltage levels, the RST# input voltage must not exceed  $V_{CC}$  until  $V_{CC} \ge V_{CC}(min)$ .

- 7. Reset completes within t<sub>PLPH</sub> if RST# is asserted while no erase or program operation is executing.

### 9.0 Bus Operations

This section provides an overview of device bus operations. The on-chip Write State Machine (WSM) manages all block-erase and word-program algorithms. The system CPU provides control of all in-system read, write, and erase operations of the device via the system bus.

Device commands are written to the Command User Interface (CUI) to control all of the flash memory device's operations. The CUI does not occupy an addressable memory location; it is the mechanism through which the flash device is controlled.

### 9.1 Bus Operations Overview

Bus cycles to and from the device conform to standard microprocessor bus operations. Table 14 summarizes the bus operations and the voltage levels that must be applied to the device control signals when operating within each device mode. Whenever CE# is asserted, the device is in an active state; it is selected and its internal circuits are active. OE# and WE# determine whether D[15:0] are outputs or inputs, respectively.