# **P89LPC938**

8-bit microcontroller with accelerated two-clock 80C51 core 8 kB 3 V byte-erasable Flash with 10-bit A/D converter

Rev. 01 — 25 February 2005

**Product data sheet**

# 1. General description

The P89LPC938 is a single-chip microcontroller, available in low cost packages, based on a high performance processor architecture that executes instructions in two to four clocks, six times the rate of standard 80C51 devices. Many system-level functions have been incorporated into the P89LPC938 in order to reduce component count, board space, and system cost.

#### 2. Features

# 2.1 Principal features

- 8 kB byte-erasable Flash code memory organized into 1 kB sectors and 64-byte pages. Single-byte erasing allows any byte(s) to be used as non-volatile data storage.

- 256-byte RAM data memory and a 512-byte auxiliary on-chip RAM.

- 512-byte customer Data EEPROM on chip allows serialization of devices, storage of set-up parameters, etc.

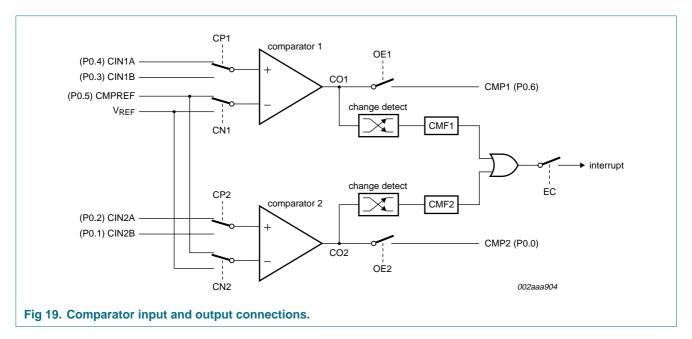

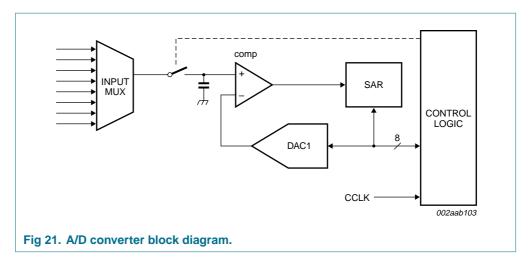

- 8-input multiplexed 10-bit A/D converter. Two analog comparators with selectable inputs and reference source.

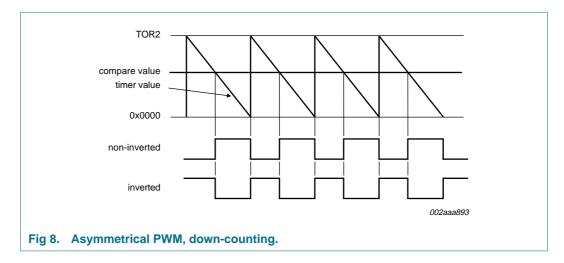

- Two 16-bit counter/timers (each may be configured to toggle a port output upon timer overflow or to become a PWM output) and a 23-bit system timer that can also be used as a RTC.

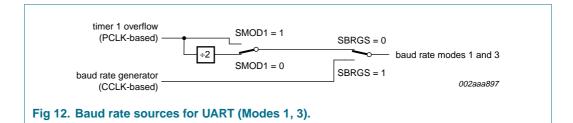

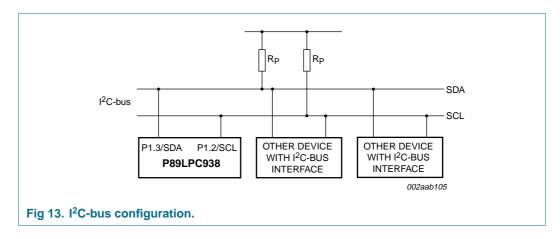

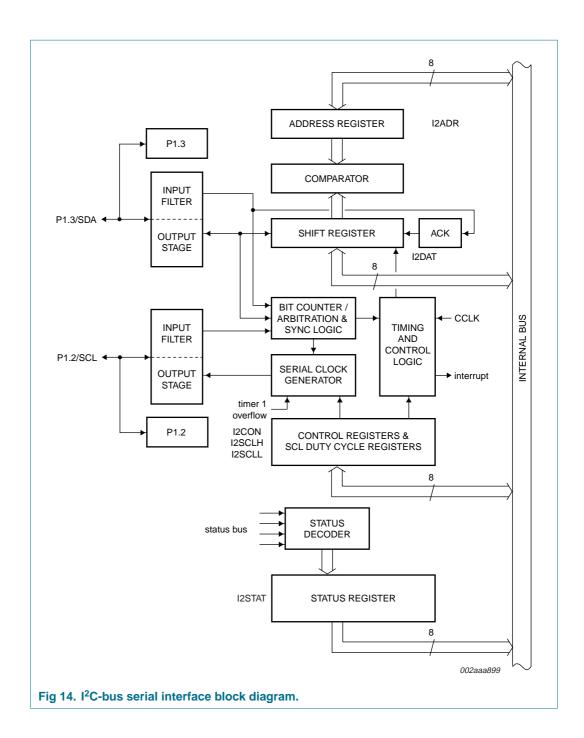

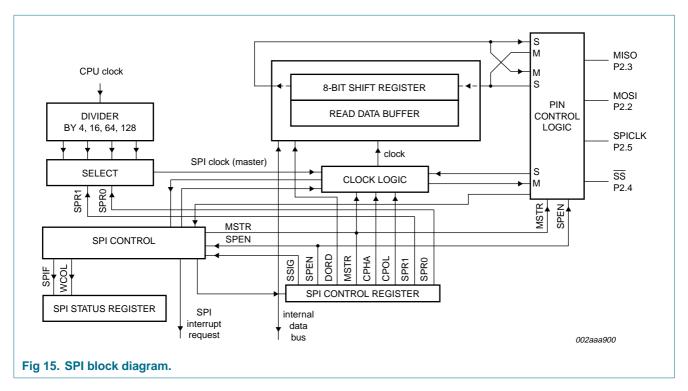

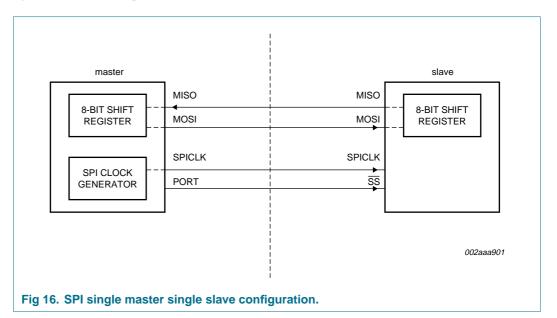

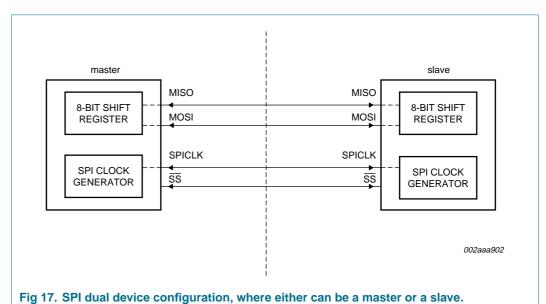

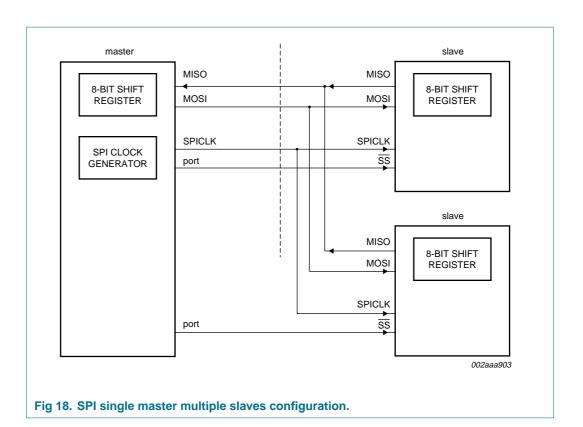

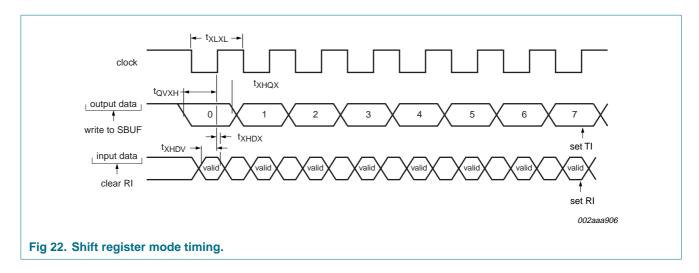

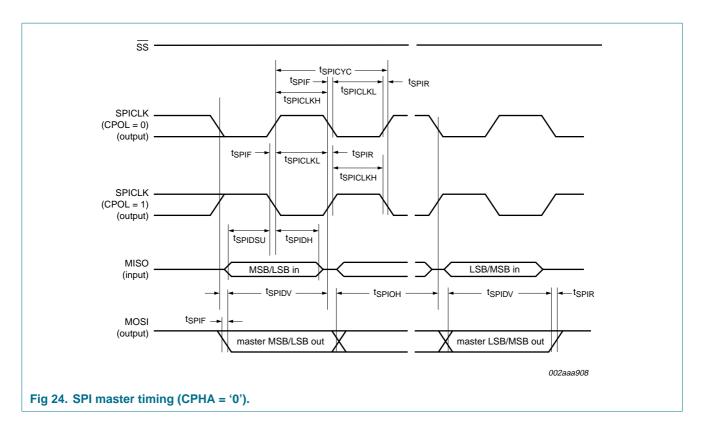

- Enhanced UART with fractional baud rate generator, break detect, framing error detection, and automatic address detection; 400 kHz byte-wide I<sup>2</sup>C-bus communication port and SPI communication port.

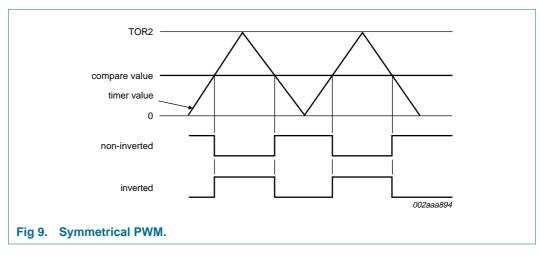

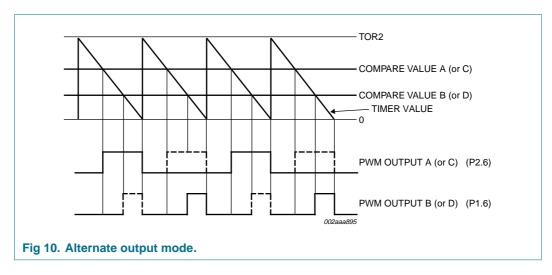

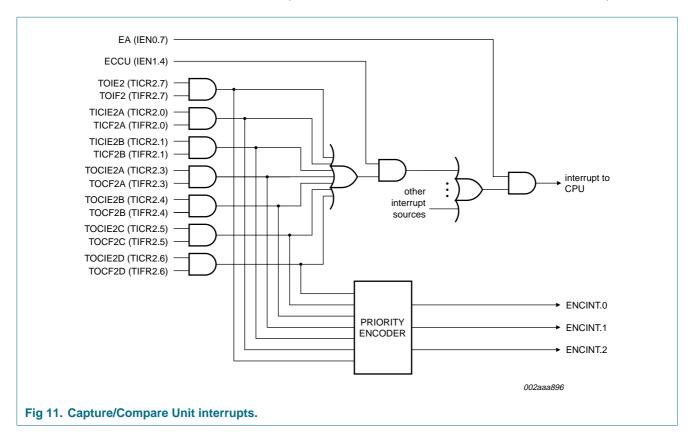

- CCU provides PWM, input capture, and output compare functions.

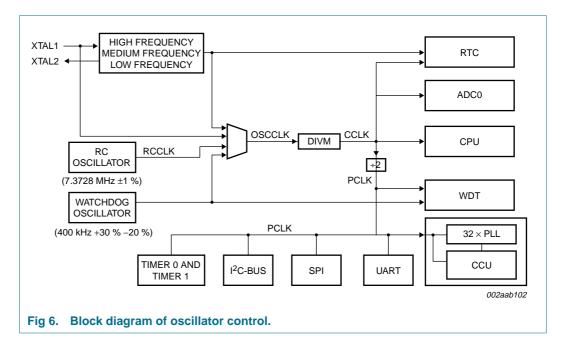

- High-accuracy internal RC oscillator option allows operation without external oscillator components. The RC oscillator option is selectable and fine tunable.

- 2.4 V to 3.6 V V<sub>DD</sub> operating range. I/O pins are 5 V tolerant (may be pulled up or driven to 5.5 V).

- 28-pin TSSOP, PLCC, and HVQFN packages with 23 I/O pins minimum and up to 26 I/O pins while using on-chip oscillator and reset options.

#### 2.2 Additional features

- A high performance 80C51 CPU provides instruction cycle times of 111 ns to 222 ns for all instructions except multiply and divide when executing at 18 MHz. This is six times the performance of the standard 80C51 running at the same clock frequency. A lower clock frequency for the same performance results in power savings and reduced EMI.

- Serial Flash ICP allows simple production coding with commercial EPROM programmers. Flash security bits prevent reading of sensitive application programs.

- Serial Flash ISP allows coding while the device is mounted in the end application.

- In-Application Programming of the Flash code memory. This allows changing the code in a running application.

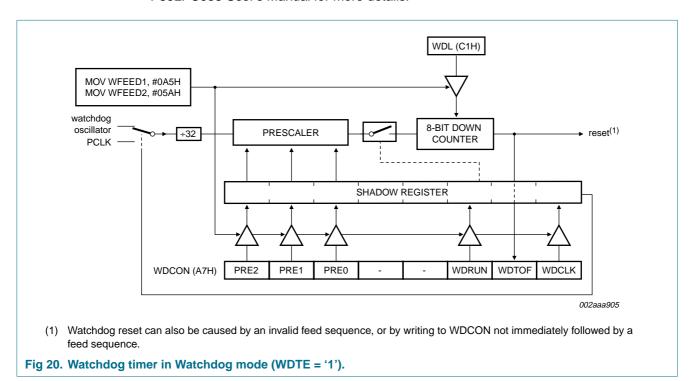

- Watchdog timer with separate on-chip oscillator, requiring no external components. The watchdog prescaler is selectable from eight values.

- Low voltage reset (brownout detect) allows a graceful system shutdown when power fails. May optionally be configured as an interrupt.

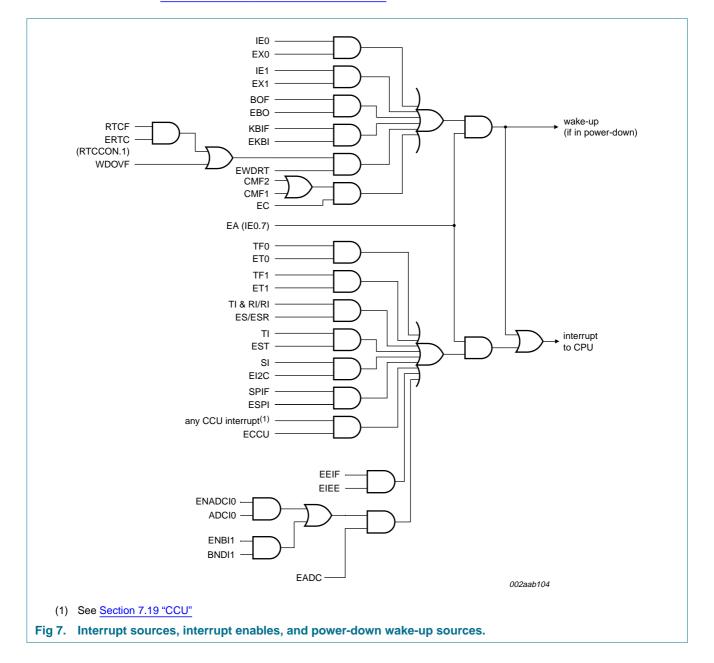

- Idle and two different power-down reduced power modes. Improved wake-up from Power-down mode (a LOW interrupt input starts execution). Typical power-down current is 1 μA (total power-down with voltage comparators disabled).

- Active-LOW reset. On-chip power-on reset allows operation without external reset components. A reset counter and reset glitch suppression circuitry prevent spurious and incomplete resets. A software reset function is also available.

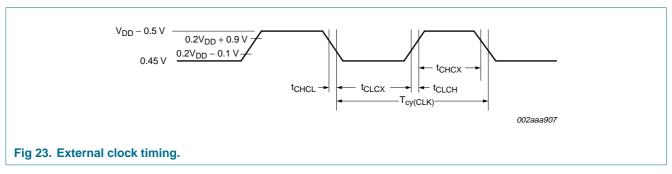

- Configurable on-chip oscillator with frequency range options selected by user programmed Flash configuration bits. Oscillator options support frequencies from 20 kHz to the maximum operating frequency of 18 MHz.

- Oscillator fail detect. The watchdog timer has a separate fully on-chip oscillator allowing it to perform an oscillator fail detect function.

- Programmable port output configuration options: quasi-bidirectional, open drain, push-pull, input-only.

- Port 'input pattern match' detect. Port 0 may generate an interrupt when the value of the pins match or do not match a programmable pattern.

- LED drive capability (20 mA) on all port pins. A maximum limit is specified for the entire chip.

- Controlled slew rate port outputs to reduce EMI. Outputs have approximately 10 ns minimum ramp times.

- Only power and ground connections are required to operate the P89LPC938 when internal reset option is selected.

- Four interrupt priority levels.

- Eight keypad interrupt inputs, plus two additional external interrupt inputs.

- Schmitt trigger port inputs.

- Second data pointer.

- Emulation support.

# 3. Ordering information

Table 1: Ordering information

| Type number  | Package |                                                                                                            |          |  |  |  |  |  |  |  |

|--------------|---------|------------------------------------------------------------------------------------------------------------|----------|--|--|--|--|--|--|--|

|              | Name    | Description                                                                                                | Version  |  |  |  |  |  |  |  |

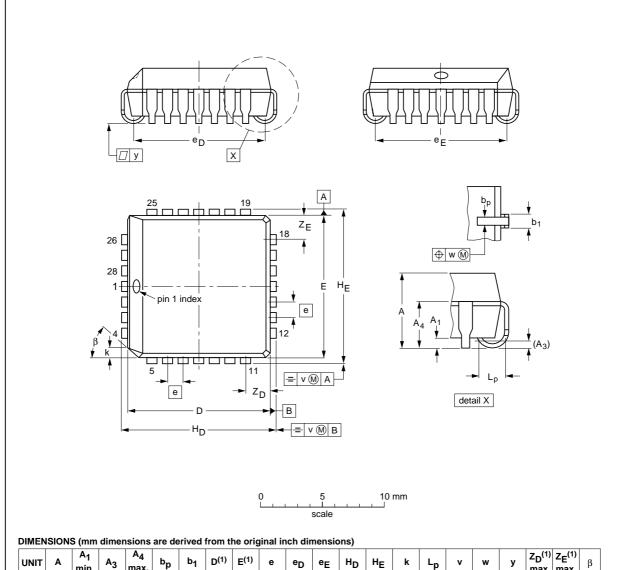

| P89LPC938FA  | PLCC28  | plastic leaded chip carrier; 28 leads                                                                      | SOT261-2 |  |  |  |  |  |  |  |

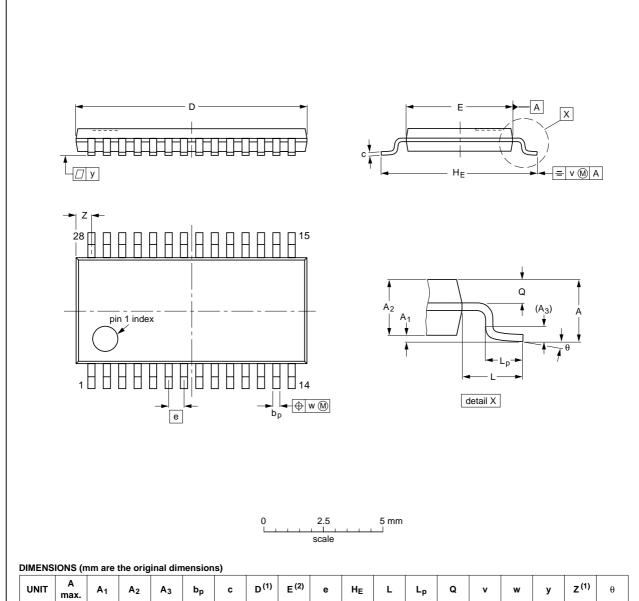

| P89LPC938FDH | TSSOP28 | plastic thin shrink small outline package;<br>28 leads; body width 4.4 mm                                  | SOT361-1 |  |  |  |  |  |  |  |

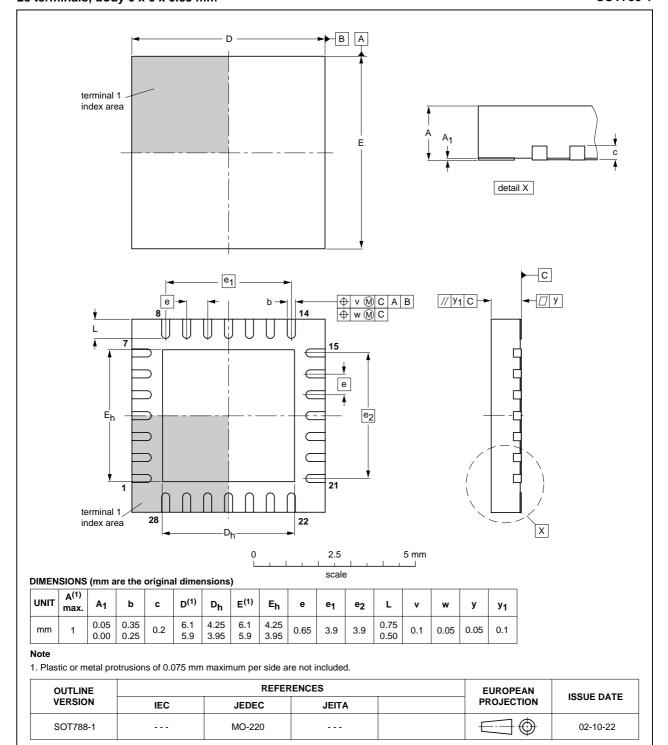

| P89LPC938FHN | HVQFN28 | plastic thermal enhanced very thin quad flat package; no leads; 28 terminals; body $6\times6\times0.85$ mm | SOT788-1 |  |  |  |  |  |  |  |

# 3.1 Ordering options

Table 2: Ordering options

| Type number  | Flash memory | Temperature range | Frequency       |

|--------------|--------------|-------------------|-----------------|

| P89LPC938FA  | 8 kB         | –40 °C to +85 °C  | 0 MHz to 18 MHz |

| P89LPC938FDH | 8 kB         | –40 °C to +85 °C  | 0 MHz to 18 MHz |

| P89LPC938FHN | 8 kB         | –40 °C to +85 °C  | 0 MHz to 18 MHz |

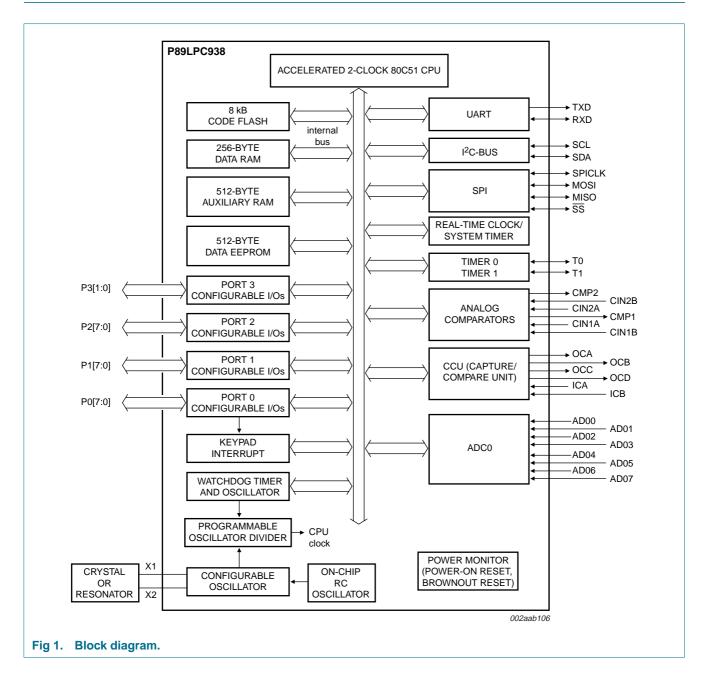

# 4. Block diagram

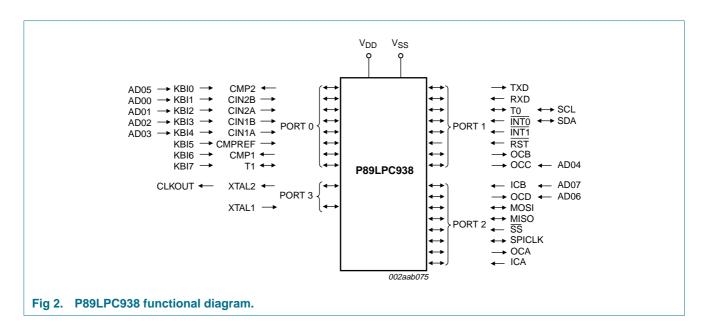

# 5. Functional diagram

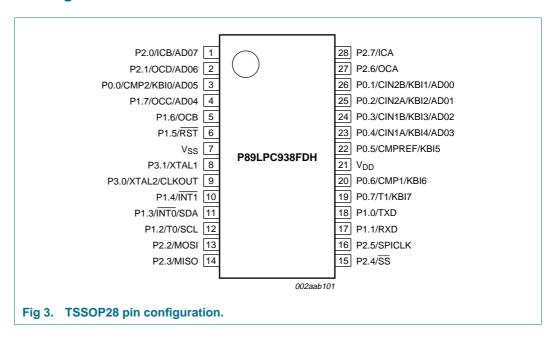

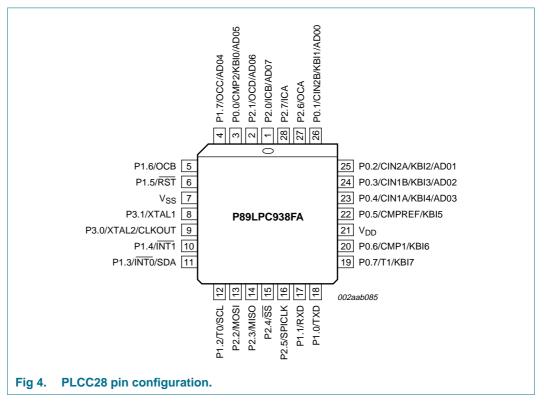

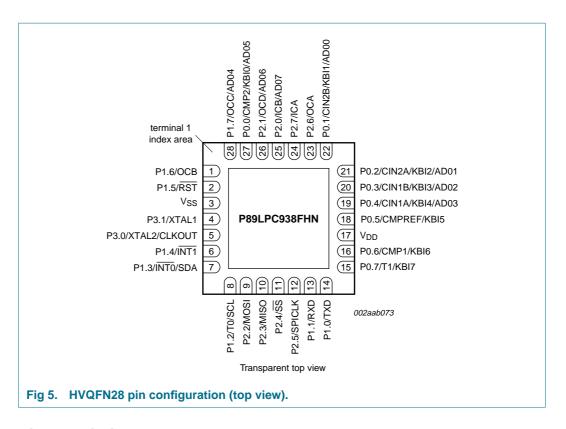

# 6. Pinning information

# 6.1 Pinning

# 6.2 Pin description

Table 3: Pin description

| Symbol       | Pin                |         | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                |

|--------------|--------------------|---------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|              | TSSOP28,<br>PLCC28 | HVQFN28 |      |                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| P0.0 to P0.7 |                    |         | I/O  | <b>Port 0:</b> Port 0 is an 8-bit I/O port with a user-configurable output type. During reset Port 0 latches are configured in the input only mode with the internal pull-up disabled. The operation of Port 0 pins as inputs and outputs depends upon the port configuration selected. Each port pin is configured independently. Refer to Section 7.13.1 "Port configurations" and Table 10 "DC electrical characteristics" for details. |

|              |                    |         |      | The Keypad Interrupt feature operates with Port 0 pins.                                                                                                                                                                                                                                                                                                                                                                                    |

|              |                    |         |      | All pins have Schmitt triggered inputs.                                                                                                                                                                                                                                                                                                                                                                                                    |

|              |                    |         |      | Port 0 also provides various special functions as described below:                                                                                                                                                                                                                                                                                                                                                                         |

| P0.0/CMP2/   | 3                  | 27      | I/O  | <b>P0.0</b> — Port 0 bit 0.                                                                                                                                                                                                                                                                                                                                                                                                                |

| KBI0/AD05    |                    |         | 0    | CMP2 — Comparator 2 output.                                                                                                                                                                                                                                                                                                                                                                                                                |

|              |                    |         | I    | KBI0 — Keyboard input 0.                                                                                                                                                                                                                                                                                                                                                                                                                   |

|              |                    |         | I    | AD05 — ADC0 channel 5 analog input.                                                                                                                                                                                                                                                                                                                                                                                                        |

| P0.1/CIN2B/  | 26                 | 22      | I/O  | <b>P0.1</b> — Port 0 bit 1.                                                                                                                                                                                                                                                                                                                                                                                                                |

| KBI1/AD00    |                    |         | I    | CIN2B — Comparator 2 positive input B.                                                                                                                                                                                                                                                                                                                                                                                                     |

|              |                    |         | I    | KBI1 — Keyboard input 1.                                                                                                                                                                                                                                                                                                                                                                                                                   |

|              |                    |         | I    | AD00 — ADC0 channel 0 analog input.                                                                                                                                                                                                                                                                                                                                                                                                        |

Table 3:

Pin description ...continued

| Symbol           | Pin                |         | Туре          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------------------|--------------------|---------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                  | TSSOP28,<br>PLCC28 | HVQFN28 |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| P0.2/CIN2A/      | 25                 | 21      | I/O           | <b>P0.2</b> — Port 0 bit 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| KBI2/AD01        |                    |         | I             | CIN2A — Comparator 2 positive input A.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                  |                    |         | I             | KBI2 — Keyboard input 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                  |                    |         | I             | AD01 — ADC0 channel 1 analog input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| P0.3/CIN1B/      | 24                 | 20      | I/O           | <b>P0.3</b> — Port 0 bit 3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| KBI3/AD02        |                    |         | I             | CIN1B — Comparator 1 positive input B.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                  |                    |         | I             | KBI3 — Keyboard input 3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                  |                    |         | I             | AD02 — ADC0 channel 2 analog input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| P0.4/CIN1A/      | 23                 | 19      | I/O           | <b>P0.4</b> — Port 0 bit 4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| KBI4/AD03        |                    |         | I             | CIN1A — Comparator 1 positive input A.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                  |                    |         | I             | KBI4 — Keyboard input 4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                  |                    |         | I             | AD03 — ADC0 channel 3 analog input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| P0.5/CMPREF/     | 22                 | 18      | I/O           | <b>P0.5</b> — Port 0 bit 5.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| KBI5             |                    |         | I             | CMPREF — Comparator reference (negative) input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                  |                    |         | I             | KBI5 — Keyboard input 5.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| P0.6/CMP1/ 20 16 |                    | 16      | I/O           | <b>P0.6</b> — Port 0 bit 6.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| KBI6             |                    |         | 0             | CMP1 — Comparator 1 output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                  |                    |         | I             | KBI6 — Keyboard input 6.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| P0.7/T1/KBI7     | 19                 | 15      | I/O           | <b>P0.7</b> — Port 0 bit 7.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                  |                    |         | I/O           | T1 — Timer/counter 1 external count input or overflow output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                  |                    |         | I             | KBI7 — Keyboard input 7.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| P1.0 to P1.7     |                    |         | I/O, I<br>[1] | Port 1: Port 1 is an 8-bit I/O port with a user-configurable output type, except for three pins as noted below. During reset Port 1 latches are configured in the input only mode with the internal pull-up disabled. The operation of the configurable Port 1 pins as inputs and outputs depends upon the port configuration selected. Each of the configurable port pins are programmed independently. Refer to Section 7.13.1 "Port configurations" and Table 10 "DC electrical characteristics" for details. P1.2 to P1.3 are open drain when used as outputs. P1.5 is input only. All pins have Schmitt triggered inputs. |

| P1.0/TXD         | 18                 | 14      | I/O           | <b>P1.0</b> — Port 1 bit 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                  |                    |         | 0             | <b>TXD</b> — Transmitter output for the serial port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| P1.1/RXD         | 17                 | 13      | I/O           | <b>P1.1</b> — Port 1 bit 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                  |                    |         | 1             | RXD — Receiver input for the serial port.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| P1.2/T0/SCL      | 12                 | 8       | I/O           | P1.2 — Port 1 bit 2 (open-drain when used as output).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                  |                    |         | I/O           | <b>T0</b> — Timer/counter 0 external count input or overflow output (open-drain when used as output).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                  |                    |         | I/O           | SCL — I <sup>2</sup> C serial clock input/output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

Table 3:

Pin description ...continued

| Symbol                | Pin                |         | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-----------------------|--------------------|---------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                       | TSSOP28,<br>PLCC28 | HVQFN28 |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| P1.3/INTO/SDA         | 11                 | 7       | I/O  | P1.3 — Port 1 bit 3 (open-drain when used as output).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                       |                    |         | I    | INT0 — External interrupt 0 input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                       |                    |         | I/O  | SDA — I <sup>2</sup> C serial data input/output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| P1.4/ <del>INT1</del> | 10                 | 6       | I    | <b>P1.4</b> — Port 1 bit 4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                       |                    |         | I    | INT1 — External interrupt 1 input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| P1.5/RST              | 6                  | 2       | I    | P1.5 — Port 1 bit 5 (input only).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                       |                    |         | I    | $\overline{\textbf{RST}}$ — External Reset input during power-on or if selected via UCFG1. When functioning as a reset input, a LOW on this pin resets the microcontroller, causing I/O ports and peripherals to take on their default states, and the processor begins execution at address 0. Also used during a power-on sequence to force In-System Programming mode. When using an oscillator frequency above 12 MHz, the reset input function of P1.5 must be enabled. An external circuit is required to hold the device in reset at power-up until $V_{DD}$ has reached its specified level. When system power is removed $V_{DD}$ will fall below the minimum specified operating voltage. When using an oscillator frequency above 12 MHz, in some applications, an external brownout detect circuit may be required to hold the device in reset when $V_{DD}$ falls below the minimum specified operating range. |

| P1.6/OCB              | 5                  | 1       | I/O  | <b>P1.6</b> — Port 1 bit 6.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                       |                    |         | 0    | OCB — Output Compare B.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| P1.7/OCC/             | 4                  | 28      | I/O  | <b>P1.7</b> — Port 1 bit 7.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| AD04                  |                    |         | 0    | OCC — Output Compare C.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                       |                    |         | I    | AD04 — ADC0 channel 4 analog input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| P2.0 to P2.7          |                    |         | I/O  | Port 2: Port 2 is an 8-bit I/O port with a user-configurable output type. During reset Port 2 latches are configured in the input only mode with the internal pull-up disabled. The operation of Port 2 pins as inputs and outputs depends upon the port configuration selected. Each port pin is configured independently. Refer to Section 7.13.1 "Port configurations" and Table 10 "DC electrical characteristics" for details.  All pins have Schmitt triggered inputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                       |                    |         |      | Port 2 also provides various special functions as described below:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| P2.0/ICB/AD07         | 1                  | 25      | I/O  | <b>P2.0</b> — Port 2 bit 0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                       |                    |         | l    | ICB — Input Capture B.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                       |                    |         | l    | AD07 — ADC0 channel 7 analog input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| P2.1/OCD/             | 2                  | 26      | I/O  | <b>P2.1</b> — Port 2 bit 1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| AD06                  |                    |         | 0    | OCD — Output Compare D.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                       |                    |         | I    | AD06 — ADC0 channel 6 analog input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| P2.2/MOSI             | 13                 | 9       | I/O  | <b>P2.2</b> — Port 2 bit 2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                       |                    |         | I/O  | <b>MOSI</b> — SPI master out slave in. When configured as master, this pin is output; when configured as slave, this pin is input.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| P2.3/MISO             | 14                 | 10      | I/O  | <b>P2.3</b> — Port 2 bit 3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                       |                    |         | I/O  | $\mbox{\bf MISO}$ — When configured as master, this pin is input, when configured as slave, this pin is output.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

Table 3:

Pin description ...continued

| Symbol              | Pin                |         | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                        |

|---------------------|--------------------|---------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                     | TSSOP28,<br>PLCC28 | HVQFN28 |      |                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| P2.4/ <del>SS</del> | 15                 | 11      | I/O  | <b>P2.4</b> — Port 2 bit 4.                                                                                                                                                                                                                                                                                                                                                                                                        |

|                     |                    |         | I    | SS — SPI Slave select.                                                                                                                                                                                                                                                                                                                                                                                                             |

| P2.5/SPICLK         | 16                 | 12      | I/O  | <b>P2.5</b> — Port 2 bit 5.                                                                                                                                                                                                                                                                                                                                                                                                        |

|                     |                    |         | I/O  | <b>SPICLK</b> — SPI clock. When configured as master, this pin is output; when configured as slave, this pin is input.                                                                                                                                                                                                                                                                                                             |

| P2.6/OCA            | 27                 | 23      | I/O  | <b>P2.6</b> — Port 2 bit 6.                                                                                                                                                                                                                                                                                                                                                                                                        |

|                     |                    |         | 0    | OCA — Output Compare A.                                                                                                                                                                                                                                                                                                                                                                                                            |

| P2.7/ICA            | 28                 | 24      | I/O  | <b>P2.7</b> — Port 2 bit 7.                                                                                                                                                                                                                                                                                                                                                                                                        |

|                     |                    |         | I    | ICA — Input Capture A.                                                                                                                                                                                                                                                                                                                                                                                                             |

| P3.0 to P3.1        |                    |         | I/O  | Port 3: Port 3 is a 2-bit I/O port with a user-configurable output type. During reset Port 3 latches are configured in the input only mode with the internal pull-up disabled. The operation of Port 3 pins as inputs and outputs depends upon the port configuration selected. Each port pin is configured independently. Refer to Section 7.13.1 "Port configurations" and Table 10 "DC electrical characteristics" for details. |

|                     |                    |         |      | All pins have Schmitt triggered inputs.                                                                                                                                                                                                                                                                                                                                                                                            |

|                     |                    |         |      | Port 3 also provides various special functions as described below:                                                                                                                                                                                                                                                                                                                                                                 |

| P3.0/XTAL2/         | 9                  | 5       | I/O  | <b>P3.0</b> — Port 3 bit 0.                                                                                                                                                                                                                                                                                                                                                                                                        |

| CLKOUT              |                    |         | 0    | <b>XTAL2</b> — Output from the oscillator amplifier (when a crystal oscillator option is selected via the Flash configuration.                                                                                                                                                                                                                                                                                                     |

|                     |                    |         | 0    | <b>CLKOUT</b> — CPU clock divided by 2 when enabled via SFR bit (ENCLK -TRIM.6). It can be used if the CPU clock is the internal RC oscillator, watchdog oscillator or external clock input, except when XTAL1/XTAL2 are used to generate clock source for the RTC/system timer.                                                                                                                                                   |

| P3.1/XTAL1          | 8                  | 4       | I/O  | <b>P3.1</b> — Port 3 bit 1.                                                                                                                                                                                                                                                                                                                                                                                                        |

|                     |                    |         | I    | XTAL1 — Input to the oscillator circuit and internal clock generator circuits (when selected via the Flash configuration). It can be a port pin if internal RC oscillator or watchdog oscillator is used as the CPU clock source, and if XTAL1/XTAL2 are not used to generate the clock for the RTC/system timer.                                                                                                                  |

| V <sub>SS</sub>     | 7                  | 3       | I    | Ground: 0 V reference.                                                                                                                                                                                                                                                                                                                                                                                                             |

| $V_{DD}$            | 21                 | 17      | I    | <b>Power Supply:</b> This is the power supply voltage for normal operation as well as Idle and Power-down modes.                                                                                                                                                                                                                                                                                                                   |

<sup>[1]</sup> Input/Output for P1.0 to P1.4, P1.6, P1.7. Input for P1.5.

# 7. Functional description

**Remark:** Please refer to the *P89LPC938 User's Manual* for a more detailed functional description.

# 7.1 Special function registers

Remark: SFR accesses are restricted in the following ways:

- User must **not** attempt to access any SFR locations not defined.

- Accesses to any defined SFR locations must be strictly for the functions for the SFRs.

- SFR bits labeled '-', '0' or '1' can **only** be written and read as follows:

- '-' Unless otherwise specified, must be written with '0', but can return any value when read (even if it was written with '0'). It is a reserved bit and may be used in future derivatives.

- '0' must be written with '0', and will return a '0' when read.

- '1' must be written with '1', and will return a '1' when read.

**Philips**

Semiconductors

**Table 4: P89LPC938 Special function registers** \* indicates SFRs that are bit addressable.

| Name        | Description                        | SFR     | Bit functi | ons and ad  | dresses |       |       |        |        |        | Reset  | value    |

|-------------|------------------------------------|---------|------------|-------------|---------|-------|-------|--------|--------|--------|--------|----------|

|             |                                    | addr.   | MSB        |             |         |       |       |        |        | LSB    | Hex    | Binary   |

|             | Bit                                | address | E7         | <b>E</b> 6  | E5      | E4    | E3    | E2     | E1     | E0     |        | '        |

| ACC*        | Accumulator                        | E0H     |            |             |         |       |       |        |        |        | 00     | 00000000 |

| AD0CON      | ADC0 control register              | 97H     | ENBI0      | ENADCI<br>0 | TMM0    | EDGE0 | ADCI0 | ENADC0 | ADCS01 | ADCS00 | 00     | 00000000 |

| AD0INS      | ADC0 input select                  | АЗН     | ADI07      | ADI06       | ADI05   | ADI04 | ADI03 | ADI02  | ADI01  | ADI00  | 00     | 00000000 |

| AD0MOE<br>A | ADC0 mode register A               | C0H     | BNDI0      | BURST0      | SCC0    | SCAN0 | -     | -      | -      | -      | 00     | 00000000 |

| AD0MOE<br>B | ADC0 mode register B               | A1H     | CLK2       | CLK1        | CLK0    | -     | -     | -      | -      | -      | 00     | 000x0000 |

| AUXR1       | Auxiliary function register        | A2H     | CLKLP      | EBRR        | ENT1    | ENT0  | SRST  | 0      | -      | DPS    | 00     | 000000x0 |

|             | Bit                                | address | F7         | F6          | F5      | F4    | F3    | F2     | F1     | F0     |        |          |

| B*          | B register                         | F0H     |            |             |         |       |       |        |        |        | 00     | 00000000 |

| BRGR0       | Baud rate generator rate low       | v BEH   |            |             |         |       |       |        |        |        | 00     | 00000000 |

| BRGR1       | Baud rate generator rate hig       | ıh BFH  |            |             |         |       |       |        |        |        | 00     | 00000000 |

| BRGCO       | N Baud rate generator control      | BDH     | -          | -           | -       | -     | -     | -      | SBRGS  | BRGEN  | 00 [1] | xxxxxx00 |

| CCCRA       | Capture compare A control register | EAH     | ICECA2     | ICECA1      | ICECA0  | ICESA | ICNFA | FCOA   | OCMA1  | OCMA0  | 00     | 0000000  |

| CCCRB       | Capture compare B control register | EBH     | ICECB2     | ICECB1      | ICECB0  | ICESB | ICNFB | FCOB   | OCMB1  | OCMB0  | 00     | 0000000  |

| CCCRC       | Capture compare C control register | ECH     | -          | -           | -       | -     | -     | FCOC   | OCMC1  | OCMC0  | 00     | xxxxx000 |

| CCCRD       | Capture compare D control register | EDH     | -          | -           | -       | -     | -     | FCOD   | OCMD1  | OCMD0  | 00     | xxxxx000 |

| CMP1        | Comparator 1 control registe       | er ACH  | -          | -           | CE1     | CP1   | CN1   | OE1    | CO1    | CMF1   | 00 [2] | xx000000 |

| CMP2        | Comparator 2 control registe       | er ADH  | -          | -           | CE2     | CP2   | CN2   | OE2    | CO2    | CMF2   | 00 [2] | xx000000 |

| DEECON      | I Data EEPROM control register     | F1H     | EEIF       | HVERR       | ECTL1   | ECTL0 | -     | -      | -      | EADR8  | 0E     | 00001110 |

| DEEDAT      | Data EEPROM data register          | r F2H   |            |             |         |       |       |        |        |        | 00     | 00000000 |

| DEEADR      | Data EEPROM address register       | F3H     |            |             |         |       |       |        |        |        | 00     | 00000000 |

| DIVM        | CPU clock divide-by-M control      | 95H     |            |             |         |       |       |        |        |        | 00     | 0000000  |

8-bit microcontroller with 10-bit A/D converter

**Philips**

Semiconductors

**Table 4: P89LPC938 Special function registers** ...continued \* indicates SFRs that are bit addressable.

| Name   | Description                                         | SFR    | Bit function | ons and ad  | dresses     |             |         |             |             |             | Reset value |          |

|--------|-----------------------------------------------------|--------|--------------|-------------|-------------|-------------|---------|-------------|-------------|-------------|-------------|----------|

|        |                                                     | addr.  | MSB          |             |             |             |         |             |             | LSB         | Hex         | Binary   |

| DPTR   | Data pointer (2 bytes)                              |        |              |             |             |             |         |             |             |             |             |          |

| DPH    | Data pointer high                                   | 83H    |              |             |             |             |         |             |             |             | 00          | 00000000 |

| DPL    | Data pointer low                                    | 82H    |              |             |             |             |         |             |             |             | 00          | 00000000 |

| FMADRH | Program Flash address high                          | E7H    |              |             |             |             |         |             |             |             | 00          | 00000000 |

| FMADRL | Program Flash address low                           | E6H    |              |             |             |             |         |             |             |             | 00          | 00000000 |

| FMCON  | Program Flash control (Read)                        | E4H    | BUSY         | -           | -           | -           | HVA     | HVE         | SV          | OI          | 70          | 01110000 |

|        | Program Flash control (Write)                       | E4H    | FMCMD.       | FMCMD.<br>6 | FMCMD.<br>5 | FMCMD.<br>4 | FMCMD.  | FMCMD.<br>2 | FMCMD.<br>1 | FMCMD.<br>0 |             |          |

| FMDATA | Program Flash data                                  | E5H    |              |             |             |             |         |             |             |             | 00          | 00000000 |