# LB11693JH

## Monolithic Digital IC 24V Fan Motor Driver IC

ON Semiconductor®

http://onsemi.com

### Overview

The LB11693JH is a three-phase brushless motor driver IC that uses a direct PWM drive technique to achieve highly efficient drive. It is optimal for driving fuel pump motors and other miniature motors.

### Functions

- Soft phase switching + Direct PWM drive

- PWM control based on both a DC voltage input (the CTL voltage) and a pulse input

- Provides a 5V regulator output

- One Hall-effect sensor FG output

- Built-in integrating amplifier

- Automatic recovery constraint protection circuit (on/off = 1/14), RD output

- Built-in current limiter circuit

- Built-in LVSD circuit

- Built-in thermal protection circuit

### Specifications

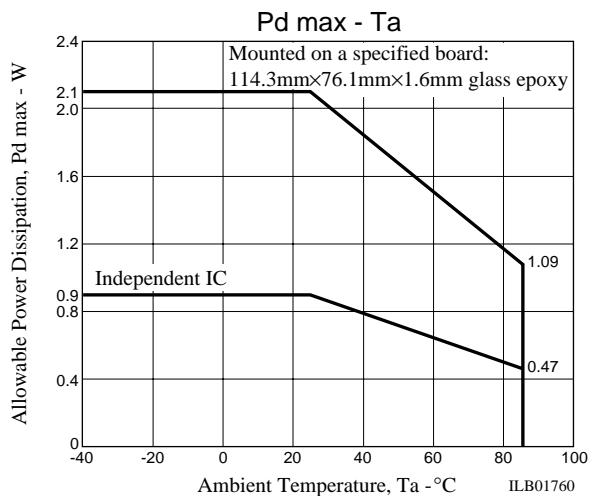

#### Absolute Maximum Ratings at Ta = 25°C

| Parameter                     | Symbol              | Conditions                    | Ratings     | Unit |

|-------------------------------|---------------------|-------------------------------|-------------|------|

| Supply voltage range          | V <sub>CC</sub> max |                               | 30          | V    |

| Output current                | I <sub>O</sub> max  | T ≤ 500ms                     | 1.8         | A    |

| Allowable power dissipation 1 | P <sub>d</sub> max1 | Independent IC                | 0.9         | W    |

| Allowable power dissipation 2 | P <sub>d</sub> max2 | Mounted on a specified board* | 2.1         | W    |

| Operating temperature         | T <sub>opr</sub>    |                               | -40 to +85  | °C   |

| Storage temperature           | T <sub>stg</sub>    |                               | -55 to +150 | °C   |

\* Mounted on a specified board: 114.3mm×76.1mm×1.6mm, glass epoxy

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

# LB11693JH

## Allowable Operating Ranges at $T_a = 25^\circ\text{C}$

| Parameter                       | Symbol    | Conditions | Ratings |          | Unit |

|---------------------------------|-----------|------------|---------|----------|------|

| Supply voltage range            | $V_{CC}$  |            |         | 8 to 28  | V    |

| Constant voltage output current | $I_{REG}$ |            |         | 0 to -30 | mA   |

| RD output current               | $I_{RD}$  |            |         | 0 to 10  | mA   |

| FG output current               | $I_{FG}$  |            |         | 0 to 10  | mA   |

## Electrical Characteristics at $T_a = 25^\circ\text{C}$ , $V_{CC} = VM = 24\text{V}$

| Parameter                                          | Symbol               | Conditions                                               | Ratings       |               |               | unit             |

|----------------------------------------------------|----------------------|----------------------------------------------------------|---------------|---------------|---------------|------------------|

|                                                    |                      |                                                          | min           | typ           | max           |                  |

| Current drain 1                                    | $I_{CC1}$            |                                                          |               | 10            | 13.5          | mA               |

| Current drain 2                                    | $I_{CC2}$            | When STOP                                                |               | 4.0           | 5.5           | mA               |

| <b>[Output Block]</b>                              |                      |                                                          |               |               |               |                  |

| Output saturation voltage 1                        | $V_{O\text{sat}1}$   | $I_O = 0.7\text{A}, V_O(\text{SINK})+V_O(\text{SOURCE})$ |               | 1.5           | 2.05          | V                |

| Output saturation voltage 2                        | $V_{O\text{sat}2}$   | $I_O = 1.5\text{A}, V_O(\text{SINK})+V_O(\text{SOURCE})$ |               | 2.2           | 2.9           | V                |

| Output leakage current                             | $I_{O\text{leak}}$   |                                                          |               |               | 100           | $\mu\text{A}$    |

| High side diode forward voltage 1                  | $V_{D1}$             | $I_D = 0.7\text{A}$                                      |               | 1.25          | 1.65          | V                |

| High side diode forward voltage 2                  | $V_{D2}$             | $I_D = 1.5\text{A}$                                      |               | 1.9           | 2.5           | V                |

| <b>[5V Constant Voltage Output]</b>                |                      |                                                          |               |               |               |                  |

| Output voltage                                     | $V_{REG}$            | $I_O = -5\text{mA}$                                      | 4.7           | 5.0           | 5.3           | V                |

| Line regulation                                    | $\Delta V_{REG1}$    | $V_{CC} = 9.5 \text{ to } 28\text{V}$                    |               | 30            | 100           | $\text{mV}$      |

| Load regulation                                    | $\Delta V_{REG2}$    | $I_O = -5 \text{ to } -20\text{mA}$                      |               | 20            | 100           | $\text{mV}$      |

| <b>[Hall Amplifier]</b>                            |                      |                                                          |               |               |               |                  |

| Input bias current                                 | $I_{B(\text{HA})}$   |                                                          |               | 2             | 10            | $\mu\text{A}$    |

| Hall sensor input sensitivity                      | $V_{HIN}$            | Sine wave input                                          | 50            |               | 350           | $\text{mVp-p}$   |

| Common-mode input voltage range                    | $V_{ICM}$            | Differential input 50mVp-p                               | 1.5           |               | $V_{REG-1.0}$ | V                |

| Input offset voltage                               | $V_{IOH}$            | Design target value*                                     | -20           |               | +20           | $\text{mV}$      |

| <b>[CSD Pin]</b>                                   |                      |                                                          |               |               |               |                  |

| High-level output voltage                          | $V_{OH(\text{CSD})}$ |                                                          | 2.75          | 3.0           | 3.25          | V                |

| Low-level output voltage                           | $V_{OL(\text{CSD})}$ |                                                          | 0.85          | 1.0           | 1.15          | V                |

| External capacitor charge current                  | $I_{CSD1}$           |                                                          | -3.3          | -2.4          | -1.4          | $\mu\text{A}$    |

| External capacitor discharge current               | $I_{CSD2}$           |                                                          | 0.09          | 0.17          | 0.23          | $\mu\text{A}$    |

| Charge/discharge current ratio                     | $R_{CSD}$            | Charge current/discharge current                         |               | 14            |               | Times            |

| <b>[Undervoltage Protection Circuit (LVS Pin)]</b> |                      |                                                          |               |               |               |                  |

| Operating voltage                                  | $V_{SDL}$            |                                                          | 3.6           | 3.8           | 4.0           | V                |

| Release voltage                                    | $V_{SDH}$            |                                                          | 4.1           | 4.3           | 4.5           | V                |

| Hysteresis                                         | $\Delta V_{SD}$      |                                                          | 0.35          | 0.5           | 0.65          | V                |

| <b>[Current Limiter Circuit]</b>                   |                      |                                                          |               |               |               |                  |

| Limiter voltage                                    | $V_{RF}$             | $V_{CC}-VM$                                              | 0.45          | 0.5           | 0.55          | V                |

| <b>[Thermal Shutdown Operation]</b>                |                      |                                                          |               |               |               |                  |

| Thermal shutdown operating temperature             | $T_{SD}$             | Design target value*<br>(junction temperature)           | 150           | 170           |               | $^\circ\text{C}$ |

| Hysteresis                                         | $\Delta T_{SD}$      | Design target value*<br>(junction temperature)           |               | 40            |               | $^\circ\text{C}$ |

| <b>[CTL Amplifier]</b>                             |                      |                                                          |               |               |               |                  |

| Input offset voltage                               | $V_{IO(\text{CTL})}$ |                                                          | -10           |               | 10            | $\text{mV}$      |

| Input bias current                                 | $I_{B(\text{CTL})}$  |                                                          | -1            |               | 1             | $\mu\text{A}$    |

| Common-mode input voltage range                    | $V_{ICM}$            |                                                          | 0             |               | $V_{REG-1.7}$ | V                |

| High-level output voltage                          | $V_{OH(\text{CTL})}$ | $I_{TOC} = -0.2\text{mA}$                                | $V_{REG-1.2}$ | $V_{REG-0.8}$ |               | V                |

| Low-level output voltage                           | $V_{OL(\text{CTL})}$ | $I_{TOC} = 0.2\text{mA}$                                 |               | 0.8           | 1.05          | V                |

| Open-loop gain                                     | $G(\text{CTL})$      | $f(\text{CTL}) = 1\text{kHz}$                            | 45            | 51            |               | $\text{dB}$      |

\*: Design target value and no measurement was made.

Continued on next page.

# LB11693JH

Continued from preceding page.

| Parameter                                 | Symbol        | Conditions                                       | Ratings       |      |           | unit             |

|-------------------------------------------|---------------|--------------------------------------------------|---------------|------|-----------|------------------|

|                                           |               |                                                  | min           | typ  | max       |                  |

| <b>[PWM Oscillator Circuit]</b>           |               |                                                  |               |      |           |                  |

| High-level output voltage                 | $V_{OH(PWM)}$ |                                                  | 2.75          | 3.0  | 3.25      | V                |

| Low-level output voltage                  | $V_{OL(PWM)}$ |                                                  | 1.1           | 1.3  | 1.4       | V                |

| Amplitude                                 | $V(PWM)$      |                                                  | 1.5           | 1.7  | 2.0       | V <sub>p-p</sub> |

| External capacitor charge current         | $I_{CHG}$     | $VPWM = 2.1V$                                    | -125          | -90  | -70       | $\mu A$          |

| Oscillator frequency                      | $f(PWM)$      | $C = 2200pF$                                     | 15.5          | 19.5 | 27.0      | kHz              |

| <b>[TOC Pin]</b>                          |               |                                                  |               |      |           |                  |

| Input voltage 1                           | $V_{TOC1}$    | Output duty: 100%                                | 2.72          | 3.0  | 3.30      | V                |

| Input voltage 2                           | $V_{TOC2}$    | Output duty: 0%                                  | 1.07          | 1.3  | 1.45      | V                |

| Input voltage 1L                          | $V_{TOC1L}$   | Design target value*. 100% when $V_{REG} = 4.7V$ | 2.72          | 2.80 | 2.90      | V                |

| Input voltage 2L                          | $V_{TOC2L}$   | Design target value*. 0% when $V_{REG} = 4.7V$   | 1.07          | 1.17 | 1.27      | V                |

| Input voltage 1H                          | $V_{TOC1H}$   | Design target value*. 100% when $V_{REG} = 5.3V$ | 3.08          | 3.20 | 3.30      | V                |

| Input voltage 2H                          | $V_{TOC2H}$   | Design target value*. 0% when $V_{REG} = 5.3V$   | 1.21          | 1.33 | 1.45      | V                |

| <b>[RD Pin]</b>                           |               |                                                  |               |      |           |                  |

| Low-level output voltage                  | $V_{OL(RD)}$  | $IRD = 5mA$                                      |               | 0.1  | 0.3       | V                |

| Output leakage current                    | $IL(RD)$      | $VRD = 28V$                                      |               |      | 10        | $\mu A$          |

| <b>[FG Pin]</b>                           |               |                                                  |               |      |           |                  |

| Low-level output voltage                  | $V_{OL(FG)}$  | $IFG = 5mA$                                      |               | 0.1  | 0.3       | V                |

| Output leakage current                    | $IL(FG)$      | $VFG = 28V$                                      |               |      | 10        | $\mu A$          |

| <b>[IFGFI1 Pin]</b>                       |               |                                                  |               |      |           |                  |

| Charge current                            | $IFGFI1$      |                                                  | -7            | -5   | -3        | $\mu A$          |

| Discharge current                         | $IFGFI2$      |                                                  | 3             | 5    | 7         | $\mu A$          |

| <b>[FG Amplifier Schmitt Block (IN1)]</b> |               |                                                  |               |      |           |                  |

| Amplifier gain                            | $G(FG)$       | Design target value*.                            |               | 7    |           | Times            |

| Hysteresis                                | $V_{IS}(FG)$  | Design target value*. Input equivalent           |               | 8    |           | mV               |

| <b>[S/S Pin]</b>                          |               |                                                  |               |      |           |                  |

| High-level input voltage                  | $V_{IH(SS)}$  |                                                  | 2.0           |      | $V_{REG}$ | V                |

| Low-level input voltage                   | $V_{IL(SS)}$  |                                                  | 0             |      | 1.0       | V                |

| Input open voltage                        | $V_{IO(SS)}$  |                                                  | 2.6           | 2.9  | 3.2       | V                |

| Hysteresis                                | $V_{IS(SS)}$  |                                                  | 0.16          | 0.25 | 0.34      | V                |

| High-level input current                  | $I_{IH(SS)}$  | $VS/S = V_{REG}$                                 |               | 100  | 130       | $\mu A$          |

| Low-level input current                   | $I_{IL(SS)}$  | $VS/S = 0V$                                      | -170          | -130 |           | $\mu A$          |

| <b>[P威MIN Pin]</b>                        |               |                                                  |               |      |           |                  |

| Input frequency range                     | $f(PI)$       |                                                  |               |      | 50        | kHz              |

| High-level input voltage range            | $V_{IH(PI)}$  |                                                  | 2.0           |      | $V_{REG}$ | V                |

| Low-level input voltage range             | $V_{IL(PI)}$  |                                                  | 0             |      | 1.0       | V                |

| Input open voltage                        | $V_{IO(PI)}$  |                                                  | 2.6           | 2.9  | 3.2       | V                |

| Hysteresis                                | $V_{IS(PI)}$  |                                                  | 0.16          | 0.25 | 0.34      | V                |

| High-level input current                  | $I_{IH(PI)}$  | $VPWMIN = V_{REG}$                               |               | 100  | 130       | $\mu A$          |

| Low-level input current                   | $I_{IL(PI)}$  | $VPWMIN = 0V$                                    | -170          | -130 |           | $\mu A$          |

| <b>[F/R Pin]</b>                          |               |                                                  |               |      |           |                  |

| High-level input voltage                  | $V_{IH(FR)}$  |                                                  | 2.0           |      | $V_{REG}$ | V                |

| Low-level input voltage                   | $V_{IL(FR)}$  |                                                  | 0             |      | 1.0       | V                |

| Input open voltage                        | $V_{IO(FR)}$  |                                                  | $V_{REG}-0.5$ |      | $V_{REG}$ | V                |

| Hysteresis                                | $V_{IS(FR)}$  |                                                  | 0.16          | 0.25 | 0.34      | V                |

| High-level input current                  | $I_{IH(FR)}$  | $VF/R = V_{REG}$                                 | -10           | 0    | 10        | $\mu A$          |

| Low-level input current                   | $I_{IL(FR)}$  | $VF/R = 0V$                                      | -165          | -115 |           | $\mu A$          |

\*: Design target value and no measurement was made.

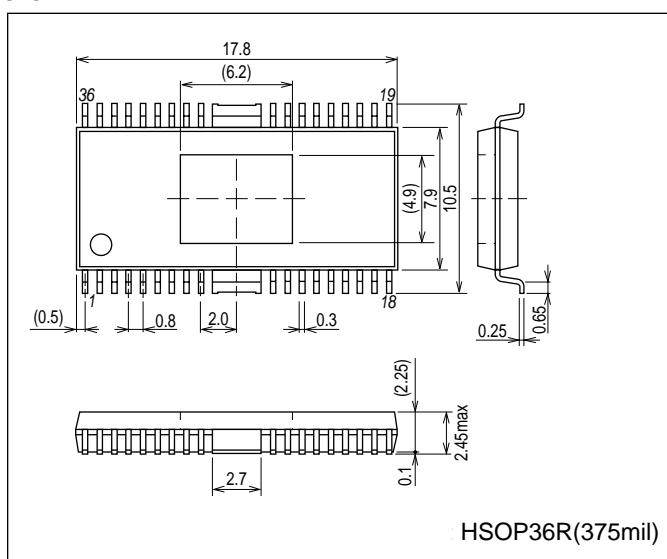

## Package Dimensions

unit : mm (typ)

3251

## Truth Table

|   | Source→Sink | F/R = "L" |     |     | F/R = "H" |     |     |

|---|-------------|-----------|-----|-----|-----------|-----|-----|

|   |             | IN1       | IN2 | IN3 | IN1       | IN2 | IN3 |

| 1 | OUT2→OUT1   | H         | L   | H   | L         | H   | L   |

| 2 | OUT3→OUT1   | H         | L   | L   | L         | H   | H   |

| 3 | OUT3→OUT2   | H         | H   | L   | L         | L   | H   |

| 4 | OUT1→OUT2   | L         | H   | L   | H         | L   | H   |

| 5 | OUT1→OUT3   | L         | H   | H   | H         | L   | L   |

| 6 | OUT2→OUT3   | L         | L   | H   | H         | H   | L   |

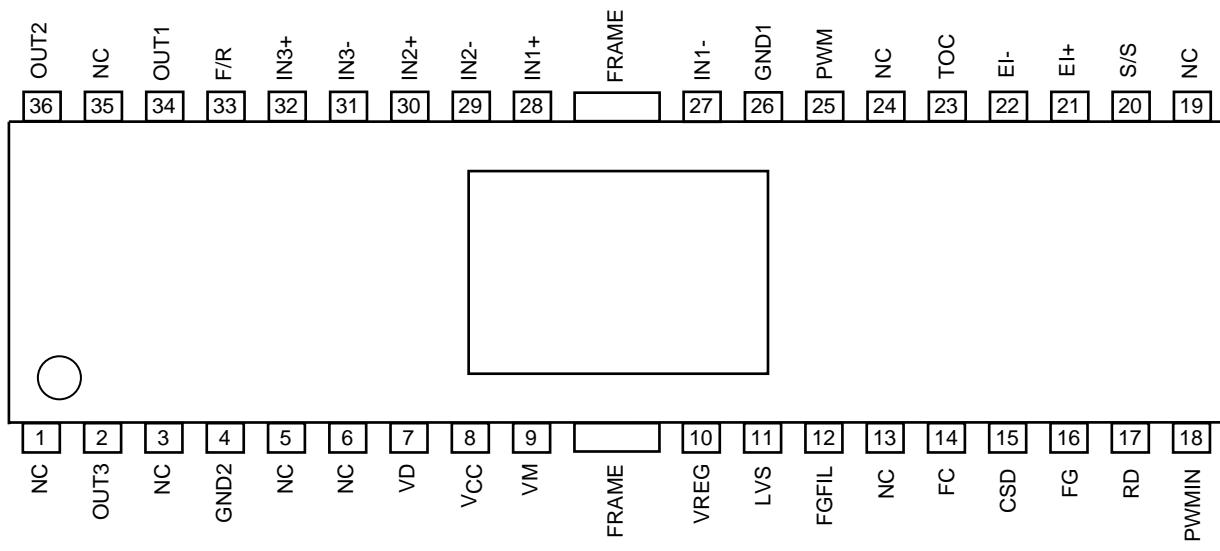

## Pin Assignment

Top view

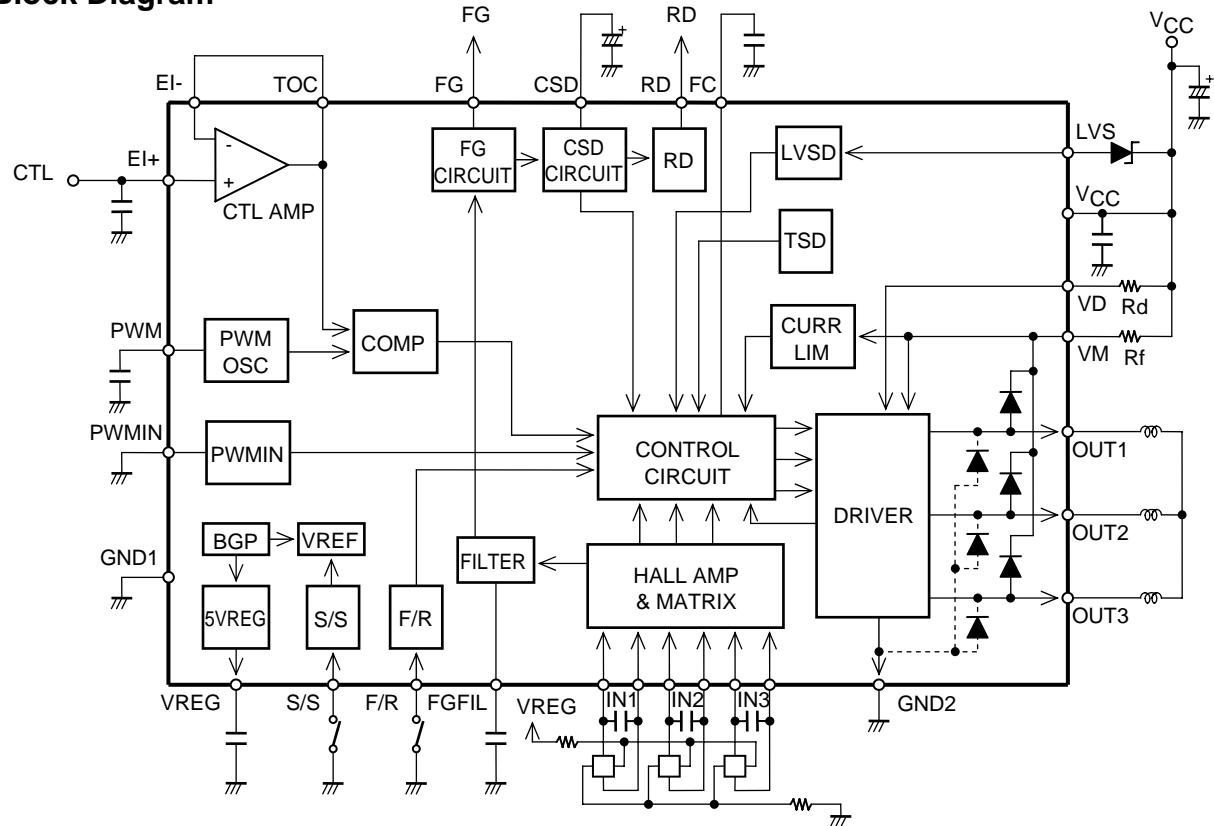

**Block Diagram**

**Pin Functions**

| Pin No. | Symbol | Pin Description                                                                                                                                                                                                | Equivalent Circuit |

|---------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| 34      | OUT1   | Motor drive output                                                                                                                                                                                             |                    |

| 36      | OUT2   |                                                                                                                                                                                                                |                    |

| 2       |        |                                                                                                                                                                                                                |                    |

| 4       | GND2   | Motor drive output system ground                                                                                                                                                                               |                    |

| 7       | VD     | Low side output transistor drive current supply                                                                                                                                                                |                    |

| 9       | VM     | Motor drive output power supply and output current detection.<br>Connect a resistor (Rf) between this pin and VCC.<br>The output current is limited to a value determined by the equation $I_{OUT} = VRF/Rf$ . |                    |

| 8       | VCC    | Power supply<br>(Systems other than the motor drive output)                                                                                                                                                    |                    |

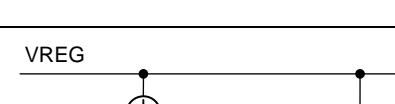

| 10      | VREG   | 5V regulator output<br>Connect a capacitor (about 0.1μF) between this pin and ground for stabilization.                                                                                                        |                    |

Continued on next page.

# LB11693JH

Continued from preceding page.

| Pin No. | Symbol | Pin Description                                                                                                                                                                                                    | Equivalent Circuit |

|---------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

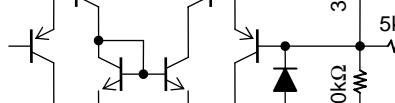

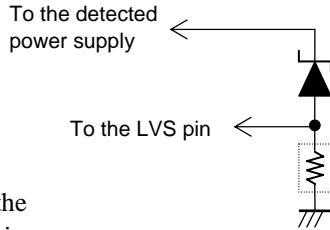

| 11      | LVS    | Undervoltage protection voltage detection.<br>Connect this pin to VREG if the VREG level is to be detected.<br>If the $V_{CC}$ level is to be detected, insert a zener diode in series to set the detection level. |                    |

| 12      | FGFIL  | FG filter.<br>Normally, this IC will be used with this pin open.<br>Connect a capacitor between this pin and ground if noise on the FG signal becomes a problem.                                                   |                    |

| 14      | FC     | Control loop frequency characteristics correction.<br>Connect a capacitor between this pin and ground.                                                                                                             |                    |

| 15      | CSD    | Constraint protection circuit operating time setting.                                                                                                                                                              |                    |

| 16      | FG     | One hall-effect sensor FG output.<br>(This is an open-collector output.)                                                                                                                                           |                    |

Continued on next page.

**LB11693JH**

Continued from preceding page.

| Pin No.  | Symbol     | Pin Description                                                                                                                                                                 | Equivalent Circuit                                                                 |

|----------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|

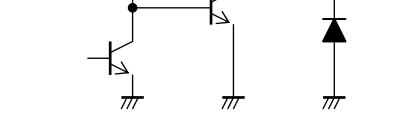

| 17       | RD         | Motor constrained state detection output<br>(This is an open-collector output.)<br>When the motor is constrained: high, when the motor is turning: low.                         |  |

| 18       | PWM IN     | PWM pulse input.<br>When low the output will be on and when high the outputs will be off. If this pin is used to control this IC, connect EI- to ground and connect EI+ to TOC. |  |

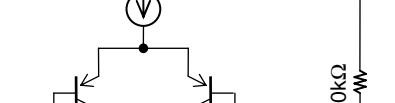

| 20       | S/S        | Start/stop control. Low: start, high or open: stop.                                                                                                                             |  |

| 21<br>22 | EI+<br>EI- | CTL amplifier noninverting input<br>CTL amplifier inverting input                                                                                                               |  |

| 23       | TOC        | PWM waveform comparator (CTL amplifier output)                                                                                                                                  |  |

---

Continued on next page.

# LB11693JH

Continued from preceding page.

| Pin No.                          | Symbol                                       | Pin Description                                                                                                                                                                                                                                                    | Equivalent Circuit |

|----------------------------------|----------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| 25                               | PWM                                          | PWM oscillator frequency setting.<br>Connect a capacitor between this pin and ground.<br>A frequency of about 20kHz can be set by using a 2200pF capacitor.                                                                                                        |                    |

| 26                               | GND1                                         | Ground<br>(For circuits other than the motor drive output system)                                                                                                                                                                                                  |                    |

| 28<br>27<br>30<br>29<br>32<br>31 | IN1+<br>IN1-<br>IN2+<br>IN2-<br>IN3+<br>IN3- | Hall effect sensor inputs<br>High when IN+ > IN-, low for the reverse state.<br>Signal inputs with an amplitude (differential) of at least 50mVp-p are desirable for the Hall inputs.<br>If noise is a problem, connect capacitors between the IN+ and IN- inputs. |                    |

| 33                               | F/R                                          | Forward/reverse control<br>Low: forward, high or open: reverse.                                                                                                                                                                                                    |                    |

| 1,3<br>5,6<br>13,19<br>24,35     | NC                                           | No connection.<br>The NC pins may be used for wiring connections.                                                                                                                                                                                                  |                    |

|                                  | FRAME                                        | Frame connection<br>The FRAME pin is connected internally to the IC surface metal parts. Both must be used in the electrically open state.                                                                                                                         |                    |

## LB11693JH Overview

### 1. Output Drive Circuit

The LB11693JH reduces motor vibration and noise by switching the output current smoothly when switching phases. Since the Hall input waveform is used for the change in (slope of) the output current during phase switching, if the slope of the Hall input waveform is too steep, the change in the output current during phase switching will also be too steep and the effectiveness of this technique at lowering vibration and noise effect will be reduced. Thus the slope of the Hall input waveform requires attention during application design.

Low side output transistor PWM switching is used for motor speed control. The drive output is adjusted by changing the duty. The diodes between the outputs and VM used for the regenerative current when the PWM signal is in the off state are built in.

If the slope (amplitude) of the Hall input waveform is large, and if used with a high current, the parasitic diodes between the outputs and ground will operate due to the low side kickback during phase switching. If problems such as disruption of the waveforms occur, connect either rectifying diodes or Schottky diodes between the outputs and ground.

### 2. Power Supply Stabilization

Since the LB11693JH uses a control method based on PWM switching, the power supply lines are susceptible to disruption. Electrolytic capacitors with an adequate capacitance for stabilization must be connected between VCC and ground. If diodes are inserted in the power supply lines to prevent destruction of the equipment if the power supply is connected in reverse, the power supply lines will be particularly susceptible to disruption. In this case, even larger capacitors must be used. The connected electrolytic capacitors must be located as close as possible to the IC pins (VCC, VM, and GND2). If the electrolytic capacitors cannot be attached close to the pins due to problems with the heat sink or other issues, ceramic capacitors of about  $0.1\mu\text{F}$  must be attached close to the pins.

### 3. VREG Pin

At the same time as being the 5V regulator output, the VREG pin is also the power supply for the IC internal control circuits. Therefore, a capacitor of at least  $0.1\mu\text{F}$  must be connected between the VREG pin and ground to stabilize the control circuit power supply. The ground side of the connected capacitor must be connected to the GND1 pin with as short a line as possible.

### 4. FC Pin

The capacitor connected to the FC pin is required to correct the control loop's frequency characteristics. (It should be about  $0.1\mu\text{F}$ .)

### 5. VD Pin

The VD pin supplies the low side output transistor drive current (a maximum of about 0.1A).

The IC internal power consumption is suppressed by connecting a resistor between the VCC and VD pins and dividing power consumption due to the low side output transistor drive current with that resistor. Although the IC internal power consumption due to the drive current can be reduced by lowering the VD pin voltage, a voltage of at least 4V must be assured at the VD pin. Use a resistor in the range from about  $50\Omega$  (0.5W) to about  $100\Omega$  (1W) between the VCC and VD pins when the LB11693JH is used with  $\text{VCC} = 24\text{V}$ .

### 6. Hall Effect Sensor Input Signals

Signal inputs with an amplitude (differential) of at least  $50\text{mVp-p}$  are required for the Hall inputs. If the output waveforms are disrupted by noise, capacitors must be connected between the Hall input pins (the + and - sides).

### 7. Current Limiter Circuit

The current limiter circuit limits the peak value of the output current to a current determined by the equation  $I = VRF/Rf$  (where  $VRF = 0.5\text{V}$  (typical),  $Rf$  = current detection resistor value). When the limiter operates, it suppresses the current by PWM control of the low side output transistor at the PWM frequency determined by the external capacitor connected to the PWM pin, in particular, by reducing the on duty.

## 8. Forward/Reverse Switching

The LB11693JH was designed assuming that forward/reverse switching would not be performed while the motor is operating. We recommend that the F/R pin be held fixed at either the low (forward) or high (reverse) level when the motor is turning. Although it will be pulled up to the high level by an internal pull-up resistor (about  $40\text{k}\Omega$ ) when left open, this must be strengthened by an external resistor if fluctuations are large.

If the direction is switched while the motor is turning, large currents will flow due to the braking operation. The LB11693JH's current limiter circuit, however, cannot limit this braking current. Therefore, forward/reverse switching during motor rotation is only possible if the braking current is limited to a value under  $I_{Q\text{ max}}$  (1.8A) by the motor coil resistance or other circuit or phenomenon. Furthermore, since through current will flow in the high and low side transistors at the instant the switch occurs with switching that only uses the F/R pin, applications must provide a rive off period for switching directions. A drive off period must be provided by either setting the IC to the stopped state with the S/S pin or setting the PWM signal to the 0% duty state with the TOC and PWMIN pins, and the F/R pin must only be switched during that period to prevent through current.

## 9. Power Saving Circuit

This IC can be set to a power saving state in which current consumption is reduced by setting it to the stopped state with the S/S pin. The bias current to most of the circuits in the IC is cut off in this power saving state. Note, however, that the 5V regulator output is still provided in the power saving state.

## 10. Notes on the PWM Frequency

The PWM frequency is determined by the capacitance (F) of the capacitor connected to the PWM pin.

$$f_{\text{PWM}} \approx 1 / (23400 \times C)$$

A frequency in the range 15 to 25kHz is desirable for the PWM frequency. The ground side of the connected capacitor must be connected to the GND1 pin by as short a line as possible.

## 11. Control Methods

The output duty can be controlled by either of the following methods.

- Comparison of the TOC pin voltage with the PWM oscillator waveform

This method determines the low side output transistor duty according to the result of comparing the TOC pin voltage with the PWM oscillator waveform. The PWM duty will be 0% when the TOC pin voltage is under about 1.3V and will be 100% when that voltage is over about 3.0V.

Since the TOC pin is the output of the CTL amplifier, a control voltage cannot be directly input to the TOC pin. Accordingly, the CTL amplifier is normally used as a full feedback amplifier (by connecting the EI- pin to the TOC pin) and inputting a DC voltage to the EI pin (here the TOC voltage will be equal to the EI+ pin voltage). When the EI+ pin voltage increases, the output duty will increase as well. Since the motor will be driven if the EI+ pin is in the open state, a pull-down resistor should be connected to the EI+ pin in applications where this is not desirable.

A low level must be input to the PWMIN pin (or it must be connected to ground) if the TOC pin voltage control system is used.

- PWMIN pulse input

A 15 to 25kHz frequency pulse signal can be input to the PWMIN pin and the low side output transistor duty can be controlled based on the duty of that input signal. When the PWMIN pin is low, the output will be on, and when high, the output will be off. When the PWMIN pin is open, the input will go to the high level and the output will be off.

If PWMIN pin control is used, the EI- pin must be connected to ground and the EI+ pin must be connected to the TOC pin.

## 12. Undervoltage Protection Circuit

The undervoltage protection circuit turns off the low side output transistor if the LVS pin voltage falls below the circuit's operating voltage (about 3.8V). This operating voltage is the detection level for a 5V system. The detection level can be increased by connecting a zener diode in series with the LVS pin to apply a level shift to the detection level. The current flowing into the LVS pin during detection is about 65 $\mu$ A.

To suppress variations in the zener voltage, it is necessary to stabilize the rise of the zener diode voltage by increasing the current that flows in the zener diode. If this is necessary, insert a resistor between the LVS pin and ground.

When the LVS pin is open, it will be pulled to the ground level by the built-in pull-down resistor and the output will be turned off. Thus if the undervoltage protection circuit is not used, a voltage in excess of the release voltage (about 4.3V) must be applied to the LVS pin. Note that the maximum rating for the LVS pin voltage is 30V.

### 13. Motor Constraint Protection Circuit

When motor motion is constrained, the external capacitor connected to the CSD pin will be alternately charged (up to about 3.0V) with a constant current of about  $2.4\mu\text{A}$  and discharged with a constant current of about  $0.17\mu\text{A}$  (to about 1.0V). Thus the CSD pin voltage will have a sawtooth waveform. The motor constraint protection circuit turns the motor (the low side output transistor) on or off repeatedly based on this sawtooth waveform. Motor drive will be on during the period the CSD pin external capacitor is being charged from about 1.0V to about 3.0V and will be off when it is being discharged from about 3.0V to about 1.0V. The drive on/off operation protects the IC and the motor when the motor is physically constrained from moving. If a  $0.47\mu\text{F}$  capacitor is connected to the CSD pin, the IC will iterate an on/off cycle in which drive is on for about 0.4 seconds and off for about 5.5 seconds.

While the motor is turning, the CSD pin voltage will be held at a certain voltage (that depends on the motor speed) by (a) a CSD pin external capacitor discharge operation based on about  $10\mu\text{s}$  discharge pulses generated internally in the IC when the Hall input IN1 switches (that is, on rising and falling edges on the FG output) and (b) a charge operation on that capacitor by a constant current of about  $2.4\mu\text{A}$ .

Since the Hall input IN1 does not switch when the motor is physically constrained, the discharge pulses are not generated and the CSD pin external capacitor will be charged to about 3.0V by the constant current of about  $2.4\mu\text{A}$ . The motor constraint protection circuit operates when the capacitor reaches about 3.0V. The constraint protection operation will be released when the motor constraint is released.

If the motor speed is extremely low, the CSD pin voltage during that motor rotation will be held at a comparatively high voltage, and if that voltage reaches about 3.0V, the constraint protection function will operate. Since the constraint protection function will operate if the Hall input IN1 frequency falls below about 10Hz, caution is required when using the motor constraint protection circuit with motors that will operate at low speeds.

Connect the CSD pin to ground if the motor constraint protection circuit is not used.

ON Semiconductor and the ON logo are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of SCILLC's product/patent coverage may be accessed at [www.onsemi.com/site/pdf/Patent-Marking.pdf](http://www.onsemi.com/site/pdf/Patent-Marking.pdf). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

# Mouser Electronics

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

[ON Semiconductor](#):

[LB11693JH-TLM-E](#) [LB11693JH-MPB-E](#)