ADS4222, ADS4225, ADS4226, ADS4242, ADS4245, ADS4246 SBAS533E - MARCH 2011 - REVISED FEBRUARY 2023

# ADS42xx Dual-Channel, 14-Bit, 12-Bit, 160, 125, 65 MSPS Ultralow-Power ADC

#### 1 Features

- Ultralow power with single 1.8-V Supply, CMOS

- 183 mW Total power at 65 MSPS

- 277 mW Total power at 125 MSPS

- 332 mW Total power at 160 MSPS

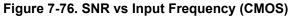

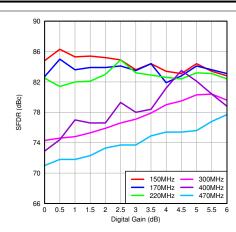

- High dynamic performance:

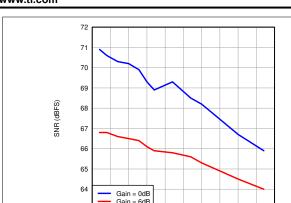

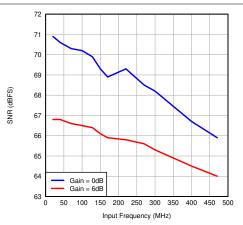

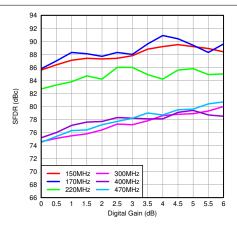

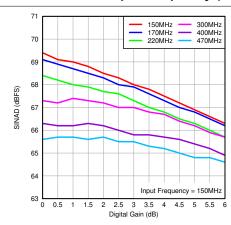

- 88-dBc SFDR at 170 MHz

- 71.4-dBFS SNR at 170 MHz

- Crosstalk: > 90 dB at 185 MHz

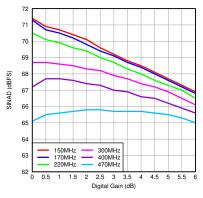

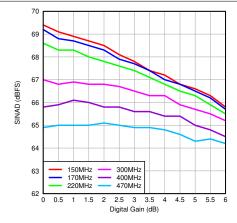

- Programmable gain up to 6 dB for SNR/SFDR trade-off

- · DC offset correction

- Output interface options:

- 1.8-V parallel CMOS interface

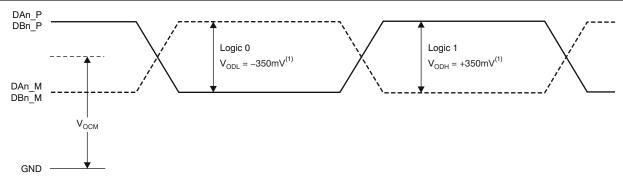

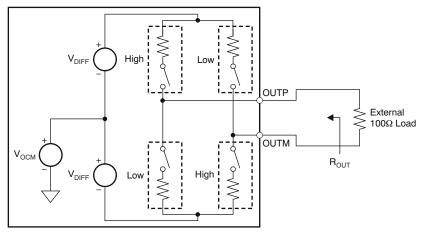

- Double data rate (DDR) LVDS with programmable swing:

- Standard swing: 350 mV

- Low swing: 200 mV

- Supports low input clock amplitude down to  $200 \text{ mV}_{PP}$

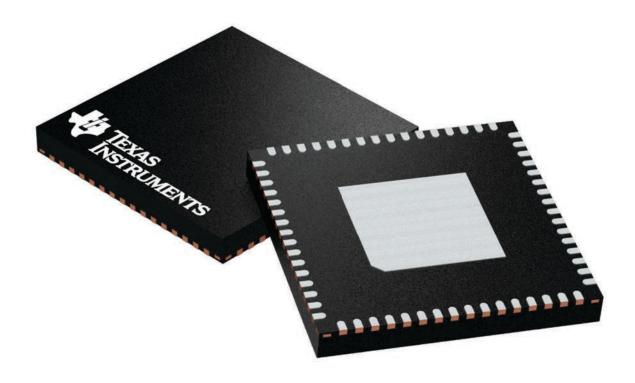

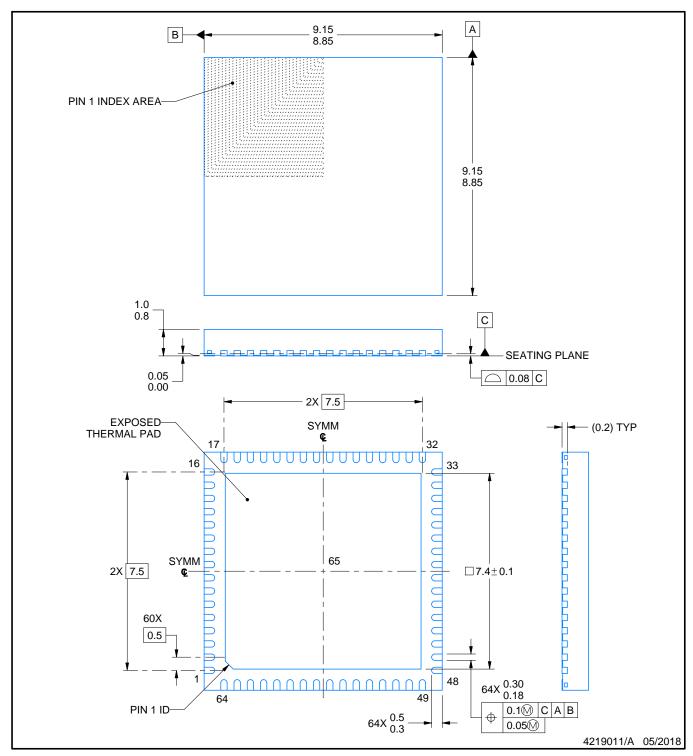

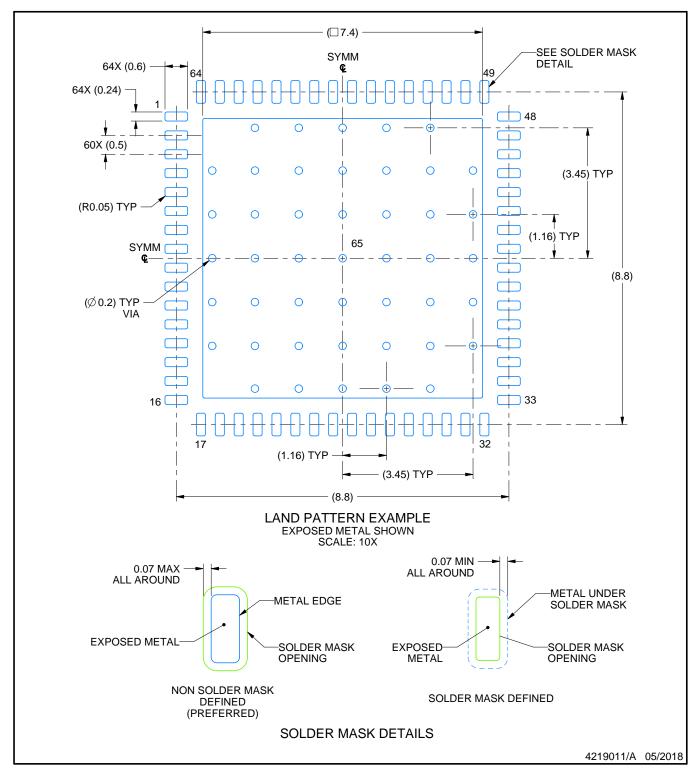

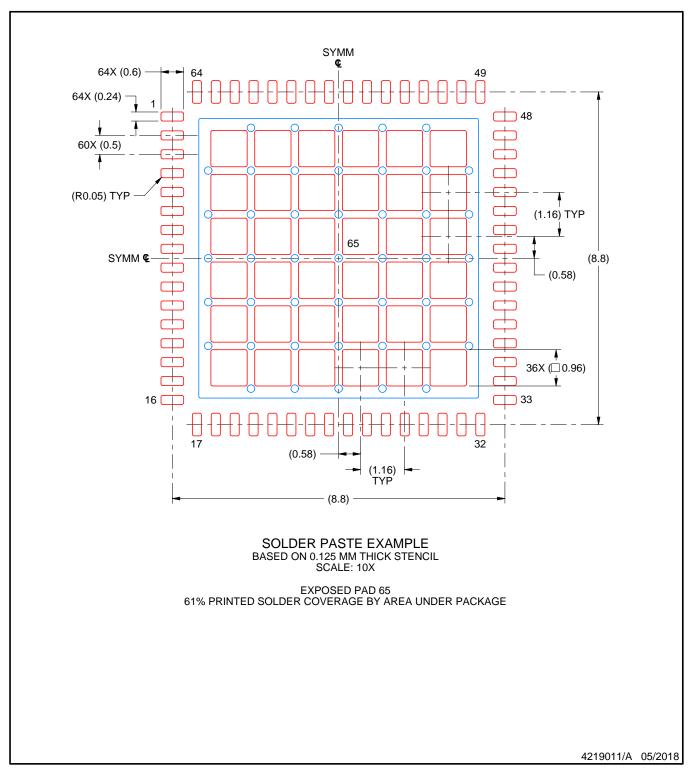

- Package: VQFN-64 (9.00 mm × 9.00 mm)

# 2 Applications

- Wireless communications infrastructure

- Software-defined radio

- Power amplifier linearization

### 3 Description

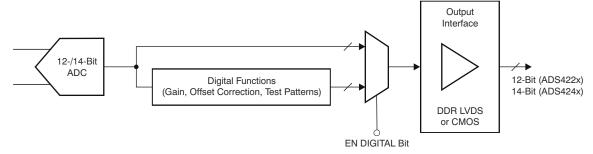

The ADS424x and ADS422x family of devices are low-speed variants of the ADS42xx ultralowpower family of dual-channel, 14-bit or 12-bit analog-to-digital converters (ADCs). Innovative design techniques are used to achieve high-dynamic performance, while consuming extremely low power with 1.8-V supply. This topology makes the ADS424x/ 422x well-suited for multi-carrier, wide-bandwidth communications applications.

#### Package Information

| PART NUMBER | PACKAGE <sup>(1)</sup> | BODY SIZE (NOM)         |

|-------------|------------------------|-------------------------|

| ADS4222     |                        |                         |

| ADS4225     |                        |                         |

| ADS4226     | VQFN (64)              | 9.00 mm × 9.00 mm       |

| ADS4242     | VQFN (04)              | 9.00 11111 ^ 9.00 11111 |

| ADS4245     |                        |                         |

| ADS4246     |                        |                         |

For all available packages, see the orderable addendum at the end of the data sheet.

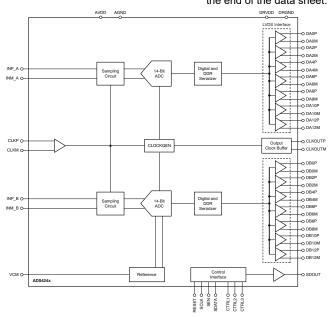

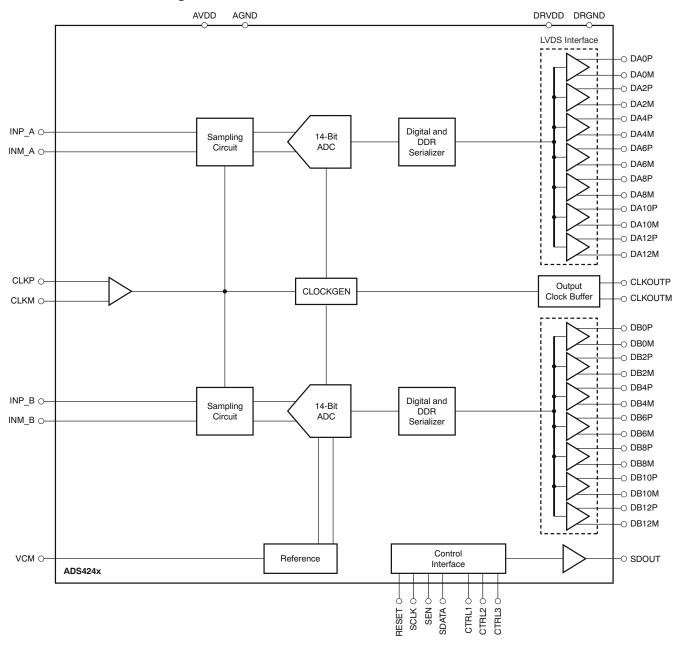

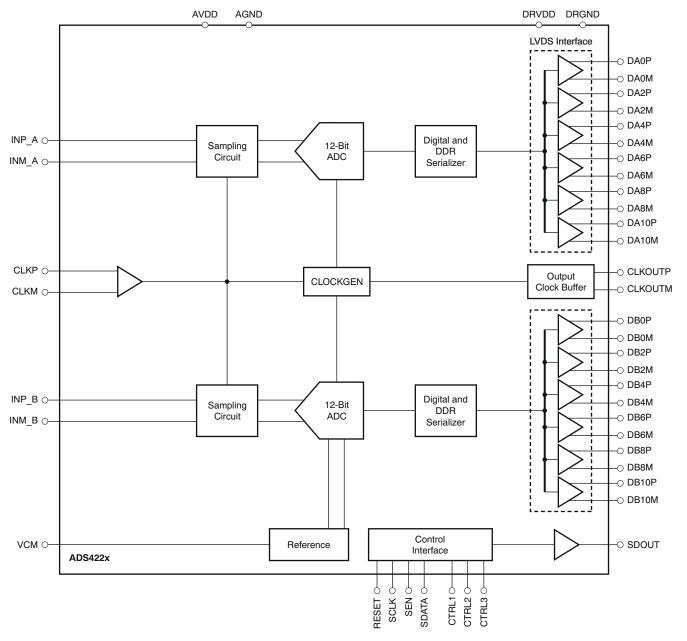

ADS4222, 25, 26, 42, 45, 46 Block Diagram

#### **Table of Contents**

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 7.12 Typical Characteristics                                                                                                                                                                               |                  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| 2 Applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 8 Detailed Description                                                                                                                                                                                     | <mark>50</mark>  |

| 3 Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 8.1 Overview                                                                                                                                                                                               | 50               |

| 4 Revision History                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 8.2 Functional Block Diagrams                                                                                                                                                                              |                  |

| 5 Description (continued)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 8.3 Feature Description                                                                                                                                                                                    |                  |

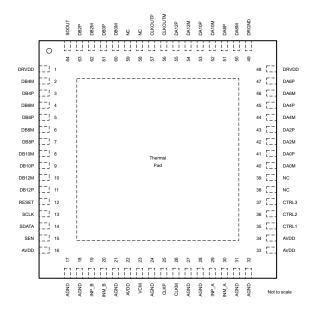

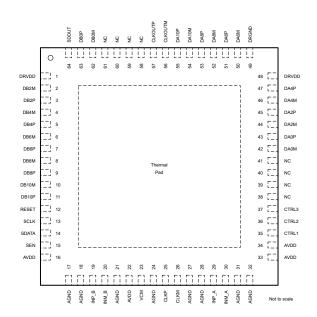

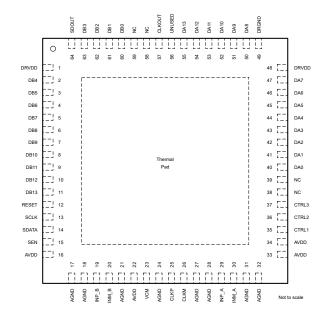

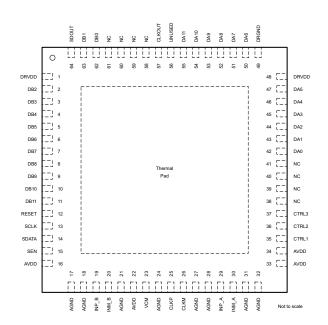

| 6 Pin Configuration and Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 8.4 Device Functional Modes                                                                                                                                                                                |                  |

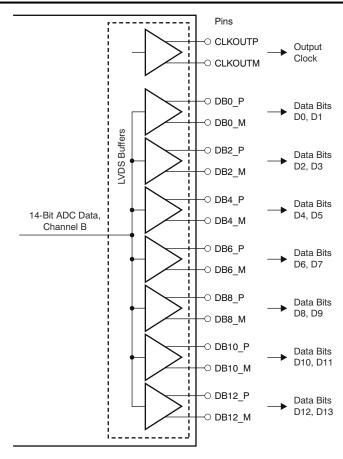

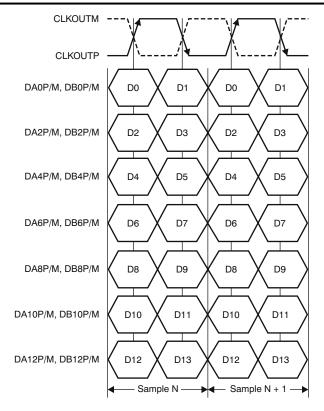

| Pin Functions – LVDS Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 8.5 Programming                                                                                                                                                                                            | 59               |

| Pin Functions – CMOS Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 8.6 Register Maps                                                                                                                                                                                          |                  |

| 7 Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 9 Application and Implementation                                                                                                                                                                           |                  |

| 7.1 Absolute Maximum Ratings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 9.1 Application Information                                                                                                                                                                                |                  |

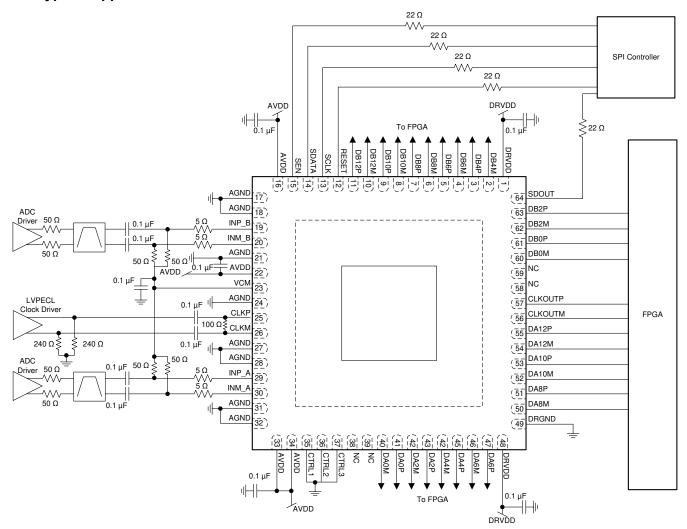

| 7.2 ESD Ratings                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 9.2 Typical Application                                                                                                                                                                                    |                  |

| 7.3 Recommended Operating Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 9.3 Power Supply Recommendations                                                                                                                                                                           |                  |

| 7.4 Thermal Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 9.4 Layout                                                                                                                                                                                                 | 85               |

| 7.5 Electrical Characteristics: ADS4246, ADS4245,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 10 Device and Documentation Support                                                                                                                                                                        | 87               |

| ADS4242                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 10.1 Device Support                                                                                                                                                                                        |                  |

| 7.6 Electrical Characteristics: ADS4226, ADS4225,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 10.2 Documentation Support                                                                                                                                                                                 | 89               |

| ADS4222                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 10.3 Support Resources                                                                                                                                                                                     | 89               |

| 7.7 Electrical Characteristics: General                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 10.4 Trademarks                                                                                                                                                                                            | 8 <mark>9</mark> |

| 7.8 Digital Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 10.5 Electrostatic Discharge Caution                                                                                                                                                                       | <mark>89</mark>  |

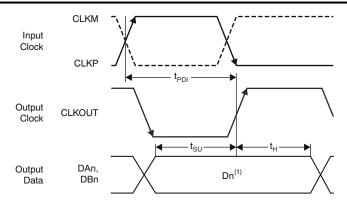

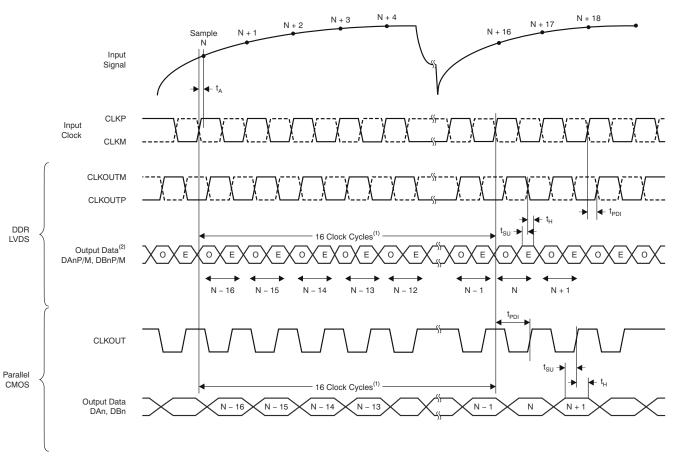

| 7.9 Timing Requirements: LVDS and CMOS Modes <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 10.6 Glossary                                                                                                                                                                                              | <mark>89</mark>  |

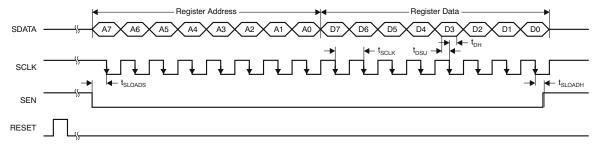

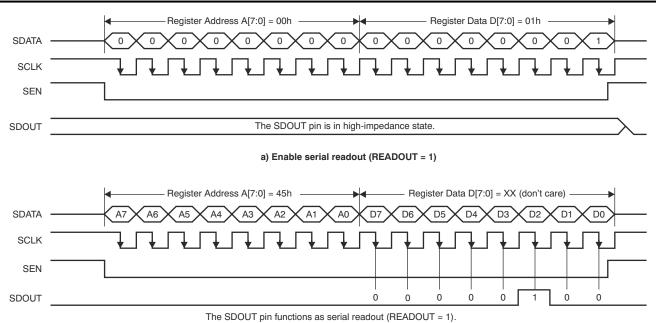

| 7.10 Serial Interface Timing Characteristics <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 19                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 11 Mechanical, Packaging, and Orderable                                                                                                                                                                    |                  |

| 7.11 Reset Timing (Only When Serial Interface Is                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Information                                                                                                                                                                                                | 89               |

| Used)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                            |                  |

| <ul> <li>Changes from Revision D (December 2015) to R</li> <li>Changed the Device Information table to the Pa</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | ion E (February 2023)  e Information table                                                                                                                                                                 | Page<br>1        |

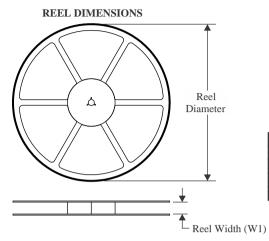

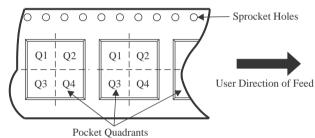

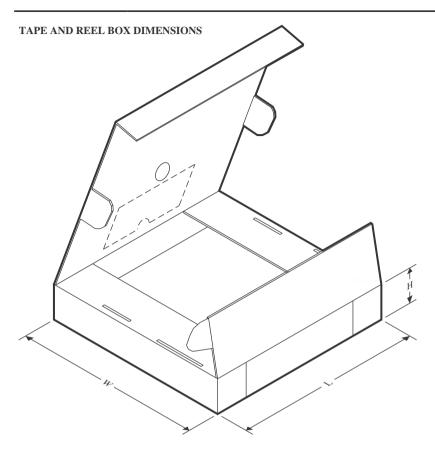

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | nformation table                                                                                                                                                                                           |                  |