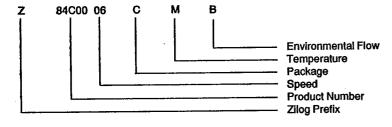

03E 08442 [

Zilog

**April 1988**

T-49-17-07

# Z84C00 CMOS Z80® CPU Central Processing Unit

### **FEATURES**

- The CMOS Z80 combines the high performance of the Z80 CPU with extremely low power consumption which results in increased reliability and very low system power requirements. This dramatic power savings makes the CMOS Z80 a natural choice for both hand-held and battery back-up operations.

- Pin compatible with Z80 CPUs.

- Software compatible with Z80 CPUs. The extensive instruction set contains 158 instructions, including the 8080A instruction set as a subset.

- Single 5 volt power supply (± 10%).

- The CMOS Z80 microprocessors and associated family of peripherals can be linked by a vectored interrupt system. This system can be daisy-chained to allow implementation of a priority interrupt scheme.

- Duplicate set of both general-purpose and flag registers.

- Two sixteen bit index registers.

- Three modes of maskable interrupts:

Mode 0—8080A similar;

Mode 1—Non-Z80 environment, location 38H;

Mode 2—Z80 family peripherals, vectored interrupts.

- Low Power Consumption

15 mA typical Icc

Standby current less than 100 μA @ 5V

- On-chip dynamic memory refresh counter.

- Can be operated at 6.144MHz clock.

# **GENERAL DESCRIPTION**

The CPUs are fourth-generation enhanced microprocessors with exceptional computational power. They offer higher system throughput and more efficient memory utilization than comparable second- and third-generation microprocessors. The internal registers contain 208 bits of read/write memory that are accessible to the programmer. These registers include two sets of six general-purpose registers which may be used individually as either 8-bit registers or as 16-bit register pairs. In addition, there are two sets of accumulator and flag registers. A group of "Exchange" instructions makes either set of main or alternate registers accessible to the programmer. The alternate set allows operation in foreground-background mode or it may be reserved for very fast interrupt response.

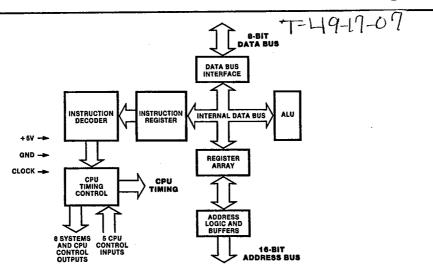

The CPU also contains a Stack Pointer, Program Counter, two index registers, a Refresh register (counter), and an Interrupt register. The CPU is easy to incorporate into a system since it requires only a single +5V power source. All output signals are fully decoded and timed to control standard memory or peripheral circuits; the CPU is supported by an extensive family of peripheral controllers. The internal block diagram (Figure 1) shows the primary functions of the processors. Subsequent text provides more detail on the I/O controller family, registers, instruction set, interrupts and daisy chaining, and CPU timing.

Figure 1. Z80C CPU Block Diagram

# **CMOS Z80 MICROPROCESSOR FAMILY**

The Zilog CMOS Z80 microprocessor is the central element of a comprehensive microprocessor product family. This family works together in most applications with minimum requirements for additional logic, facilitating the design of efficient and cost-effective microcomputer-based systems.

Zilog has designed five components to provide extensive support for the microprocessor. These are:

- The PIO (Parallel Input/Output) operates in both data-byte I/O transfer mode (with handshaking) and in bit mode (without handshaking). The PIO may be configured to interface with standard parallel peripheral devices such as printers, tape punches, and keyboards.

- The CTC (Counter/Timer Circuit) features four programmable 8-bit counter/timers, each of which has an 8-bit prescaler. Each of the four channels may be configured to operate in either counter or timer mode.

- The DMA (Direct Memory Access) controller provides dual port data transfer operations and the ability to terminate data transfer as a result of a pattern match.

- The SIO (Serial Input/Output) controller offers two channels. It is capable of operating in a variety of programmable modes for both synchronous and asynchronous communication, including Bi-Synch and SDLC.

- The DART (Dual Asynchronous Receiver/Transmitter) device provides low cost asynchronous serial communication. It has two channels and a full modem control interface.

- The above peripherals are compatible with the CPU; in addition, the PIO, CTC, and SIO devices are available in CMOS versions.

#### **CPU TIMING**

The CPU executes instructions by proceeding through a specific sequence of operations:

- Memory read or write

- I/O device read or write

- Interrupt acknowledge

The basic clock period is referred to as a T time or cycle, and three or more T cycles make up a machine cycle (M1, M2 or M3 for instance). Machine cycles can be extended either by the CPU automatically inserting one or more Wait states or by the insertion of one or more Wait states by the user.

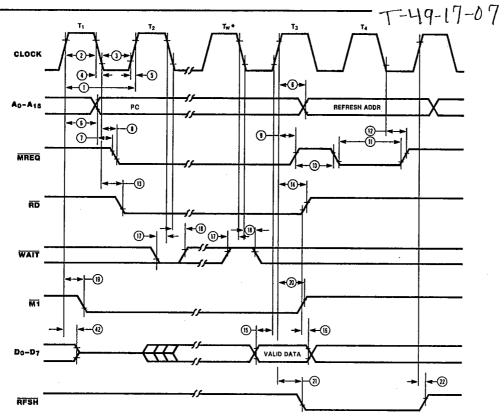

Instruction Opcode Fetch. The CPU places the contents of the Program Counter (PC) on the address bus at the start of the cycle (Figure 2). Approximately one-half clock cycle later, MREQ goes active. When active, RD indicates that the memory data can be enabled onto the CPU data bus.

The CPU samples the WAIT input with the falling edge of clock state T<sub>2</sub>. During clock states T<sub>3</sub> and T<sub>4</sub> of an M1 cycle dynamic RAM refresh can occur while the CPU starts decoding and executing the instruction. When the Refresh Control signal becomes active, refreshing of dynamic memory can take place.

\*Tw = Wait cycle added when necessary for slow ancilliary devices

Figure 2. Instruction Opcode Fetch

03E 08445 D

「一般のできないという」とは、「一般のないとなる」という。 「ないことは、「ないことは、「ないない」となってきないできない。 「ないないない」という。

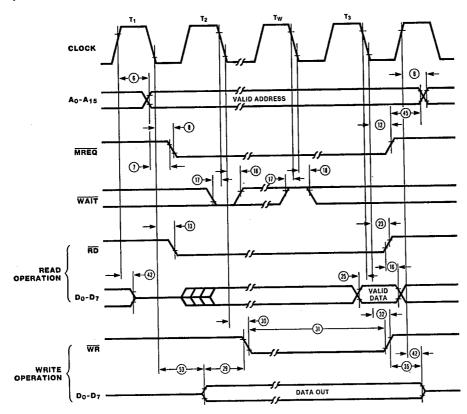

Memory Read or Write Cycles. Figure 3 shows the timing of memory read or write cycles other than an opcode fetch (M1) cycle. The MREQ and RD signals function exactly as in the fetch cycle. In a memory write cycle, MREQ also

becomes active when the address bus is stable. The WR line is active when the data bus is stable, so that it can be used directly as an R/W pulse to most semiconductor memories.

Figure 3. Memory Read or Write Cycles

D

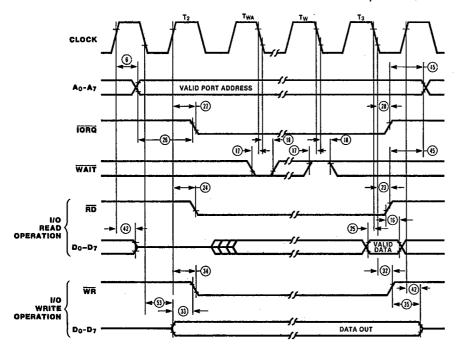

**input or Output Cycles.** Figure 4 shows the timing for an I/O read or I/O write operation. During I/O operations, the CPU automatically inserts a single Wait state  $(T_{WA})$ . This

extra Wait state allows sufficient time for an I/O port to decode the address from the port address lines.

T<sub>MA</sub> = One wait cycle automatically inserted by CPU.

Figure 4. Input or Output Cycles

03E 08447

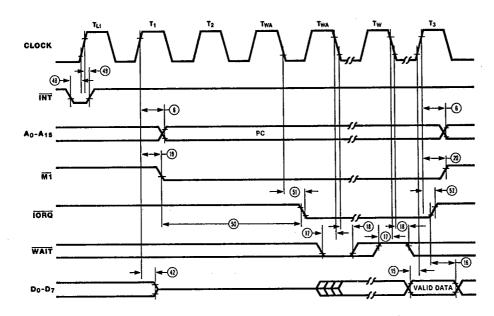

**Interrupt Request/Acknowledge Cycle.** The CPU samples the interrupt signal with the rising edge of the last clock cycle at the end of any instruction (Figure 5). When an interrupt is accepted, a special M1 cycle is generated.

During this M1 cycle, IORQ becomes active (instead of MREQ) to indicate that the interrupting device can place an 8-bit vector on the data bus. The CPU automatically adds two Wait states to this cycle.

NOTES: 1)  $T_{ij}$  = Last state of any instruction cycle. 2)  $T_{min}$  = Walt cycle automatically inserted by CPU.

Figure 5. Interrupt Request/Acknowledge Cycle

京大学者の意大学ないというない これにあせいませんしゃ ちゅうというけんかい

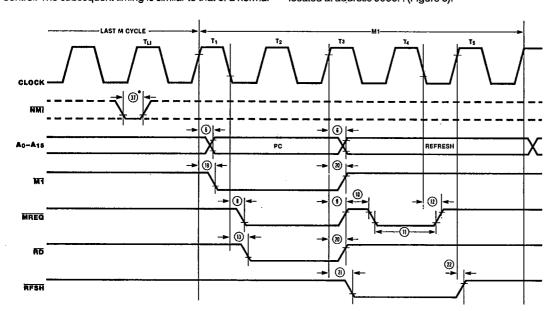

Non-Maskable Interrupt Request Cycle. NMI is sampled at the same time as the maskable interrupt input INT but has higher priority and cannot be disabled under software control. The subsequent timing is similar to that of a normal

instruction fetch except that data put on the bus by the memory is ignored. The CPU instead executes a restart (RST) operation and jumps to the NMI service routine located at address 0066H (Figure 6).

<sup>\*</sup>Although NMI is an asynchronous input, to guarantee its being recognized on the following machine cycle, NMI's falling edge must occur no late than the rising edge of the clock cycle preceding the last state of any instruction cycle (T<sub>L</sub>).

Figure 6. Non-Maskable Interrupt Request Operation

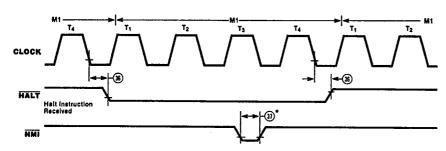

Halt Acknowledge Cycle. When the CPU receives a Halt instruction, it executes NOP states until either an INT or NMI input is received. When in the Halt state, the HALT output is

active and remains so until an interrupt is received (Figure 7). INT will also force a Halt exit.

<sup>\*</sup>Although NMI is an asynchronous input, to guarantee its being recognized on the following machine cycle, NMI's falling edge must occur no later than the rising edge of the clock cycle praceding the last state of any instruction cycle (T<sub>L</sub>).

Figure 7. Halt Acknowledge Cycle

03E 08449 D

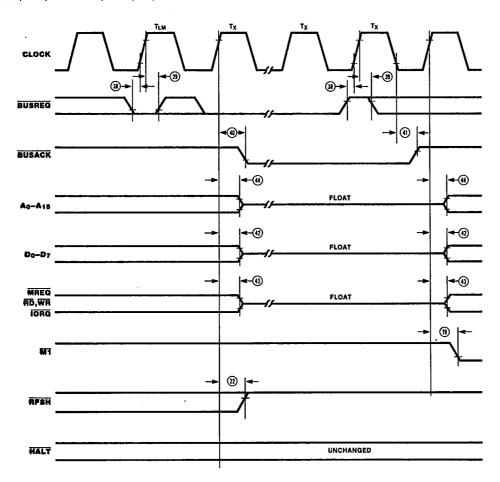

Bus Request/Acknowledge Cycle. The CPU samples BUSREQ with the rising edge of the last clock period of any machine cycle (Figure 8). If BUSREQ is active, the CPU sets its address, data, and MREQ, IORQ, RD, and WR lines to a

high-impedance state with the rising edge of the next clock pulse. At that time, any external device can take control of these lines, usually to transfer data between memory and I/O devices.

NOTES: 1)  $T_{LM}$  = Last state of any M cycle. 2)  $T_{\chi}$  = An arbitrary clock cycle used by requesting device.

Figure 8. Z-BUS Request/Acknowledge Cycle

是我们的时候,他们就是一个时间,他们也是一个时间,我们也没有一个时间,他们也是一个时间,他们也是一个时间,他们也是一个时间,他们也是一个时间,他们也是一个时间, 第一天,一个时间,他们就是一个时间,他们就是一个时间,他们就是一个时间,他们就是一个时间,他们就是一个时间,他们就是一个时间,他们就是一个时间,他们也是一个时间

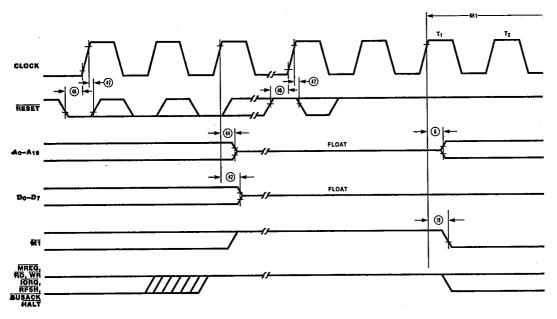

Reset Cycle. RESET must be active for at least three clock cycles for the CPU to properly accept it. As long as RESET remains active, the address and data buses float, and the control outputs are inactive. Once RESET goes inactive,

three internal T cycles are consumed before the CPU resumes normal processing operation. RESET clears the PC register, so the first opcode fetch will be to location 0000H (Figure 9).

Figure 9. Reset Cycle

03E 08451

# **AC CHARACTERISTICS**†

T-49-17-07

|    |              |                                                            | Z840            | 0006             |

|----|--------------|------------------------------------------------------------|-----------------|------------------|

| N  | umber Symbol | Parameter                                                  | Min             | Max              |

| 1  | TcC          | Clock Cycle Time                                           | 162**           | DCc              |

| !  | TwCh         | Clock Pulse Width (High)                                   | 65 <sup>c</sup> | DC°              |

| ;  | TwCl         | Clock Pulse Width (Low)                                    | 65°             | DC°              |

| ļ  | TfC          | Clock Fall Time                                            |                 | 20°              |

| ;  | TrC          | Clock Rise Time                                            |                 | 20°              |

| 5  | TdCr(A)      | Clock to Address Valid Delay                               |                 | 90ª              |

| 7  | TdA(MREQf)   | Address Valid to MREQ Delay                                | . 35*°          |                  |

| }  | TdCf(MREQf)  | Clock to MREQ Delay                                        |                 | 70ª              |

| )  | TdCr(MREQr)  | Clock to MREQ Delay                                        |                 | 70 <b>°</b>      |

| lO | TwMREQh      | MREQ Pulse Width (High)                                    | 65 <b>*</b> °   |                  |

| 11 | TwMREQI      | MREQ Pulse Width (Low)                                     | 135*c           |                  |

| 2  | TdCf(MREQr)  | Clock to MREQ Delay                                        | •               | 70 <b>ª</b>      |

| 3  | TdCf(RDf)    | Clock to RD Delay                                          |                 | 80ª              |

| 4  | TdCr(RDr)    | Clock to RD Delay                                          |                 | 70 <sup>a</sup>  |

| 15 | TsD(Cr)      | Data Setup Time to Clock                                   | 30ª             |                  |

| 16 | ThD(RDr)     | Data Hold Time to RD                                       | <del></del>     | 0°               |

| 17 | TsWAIT(Cf)   | WAIT Setup Time to Clock                                   | 60ª             |                  |

| 8  | ThWAIT (Cf)  | WAIT Hold Time after Clock                                 | 10°             |                  |

| 9  | TdCr(M1f)    | Clock to M1 Delay                                          |                 | 80 <sup>a</sup>  |

| 20 | TdCr(M1r)    | Clock to M1 Delay                                          |                 | 80°              |

| 21 | TdCr(RRSHf)  | Clock to RFSH Delay                                        |                 | 110ª             |

| 22 | TdCr(RFSHr)  | Clock to RFSH Delay                                        |                 | 100 <sup>8</sup> |

| 13 | TdCf(RDr)    | Clock to RD Delay                                          |                 | 70ª              |

| 24 | TdCr(RDf)    | Clock to RD Delay                                          | _               | 70ª              |

| 25 | TsD(Cf)      | Data Setup to Clock during M <sub>2</sub> ,                | 40°             |                  |

|    |              | M <sub>3</sub> , M <sub>4</sub> , or M <sub>5</sub> Cycles |                 | <u></u>          |

| 26 | TdA(lORQf)   | Address Stable prior to IORQ                               | 110*c           |                  |

| 27 | TdCr(IORQf)  | Clock to IORQ Delay                                        |                 | 65 <b>4</b>      |

| 28 | TdCf(lORQr)  | Clock to IORQ Delay                                        |                 | 70 <sup>a</sup>  |

| 29 | TdD(WRf)Mw   | Data Stable prior to WR                                    | 25*°            |                  |

<sup>\*</sup>For clock periods other than the minimums shown, calculate parameters using the table on the following page.

Calculated values above assumed TrC = TfC = 20 ns.

†Units in nanoseconds (ns).

†TFor loading ≤ 50 pf. Decrease width by 10 ns for each additional 50 pf.

03E 08452

# AC CHARACTERISTICS† (Continued)

T-49-17-07

|    |               |                              | Z840              | 0006                                   |

|----|---------------|------------------------------|-------------------|----------------------------------------|

| Nu | mber Symbol   | General Parameter            | Min               | Max                                    |

| 30 | TdCf(WRf)     | Clock to WR Delay            |                   | 70ª                                    |

| 31 | T₩WR          | WR Pulse Width               | 135 <sup>40</sup> |                                        |

| 32 | TdCf(WRr)     | Clock to WR Delay            |                   | 70°                                    |

| 33 | TdD(WRI)IO    | Data Stable prior to WR      | −55 <sup>¢°</sup> |                                        |

| 34 | TdCr(WRf)     | Clock to WR Delay            |                   | 60ª                                    |

| 35 | TdWRr(D)      | Data Stable from WR          | 30*°              | ······································ |

| 36 | TdCf(HALT)    | Clock to HALT or             |                   | 260ª                                   |

| 37 | TWNMI         | NMI Pulse Width              | 70°               |                                        |

| 38 | TsBUSREQ(Cr)  | BUSREQ Setup Time to Clock   | 50ª               |                                        |

| 39 | ThBUSREQ(Cr)  | BUSREQ Hold Time after Clock | 25°               |                                        |

| 40 | TdCr(BUSACKf) | Clock to BUSACK Delay        |                   | 90ª                                    |

| 41 | TdCf(BUSACKr) | Clock to BUSACK Delay        |                   | 90 <b>4</b>                            |

| 42 | TdCr(Dz)      | Clock to Data Float Delay    |                   | 80 <sup>c</sup>                        |

| 43 | TdCr(CTz)     | Clock to Control Outputs     |                   | 70°                                    |

|    | , ,           | Float Delay(MREQ, IORQ,      |                   |                                        |

|    |               | RD, and WR)                  |                   |                                        |

| 44 | TdCr(Az)      | Clock to Address Float Delay |                   | 80°                                    |

| 45 | TdCTr(A)      | MREQ , IORQ , RD , and       | 35*°              | ····                                   |

|    |               | WR to Address Hold Time      |                   |                                        |

| 46 | TsRESET(Cr)   | RESET to Clock Setup Time    | 60ª               |                                        |

| 47 | ThRESET(Cr)   | RESET to Clock Hold Time     | 10°               |                                        |

| 48 | TsINT((Cr)    | INT to Clock Setup Time      | 70°               |                                        |

| 49 | ThINTr(Cr)    | NT to Clock Hold Time        | 10°               |                                        |

| 50 | TdM1f(lORQf)  | M1 to IORQ Delay             | 365°°             | _                                      |

| 51 | TdCf(lORQf)   | Clock to IORQ Delay          |                   | 70 <sup>8</sup> -                      |

| 52 | TdCf(IORQr)   | Clock to IORQ Delay          |                   | 70 <sup>9</sup>                        |

| 53 | TdCf(D)       | Clock to Data Valid Delay    |                   | 130 <sup>8</sup>                       |

<sup>\*</sup>For clock periods other than the minimums shown, calculate parameters using the following table. Calculated values above assumed TrC = TrC = 20 ns.

# **FOOTNOTES TO AC CHARACTERISTICS**

| Number          | Symbol:                                                                | General Paramete           | er .                                                                   | Z84C0006       |  |

|-----------------|------------------------------------------------------------------------|----------------------------|------------------------------------------------------------------------|----------------|--|

| 1               | TcC                                                                    | TwCh + TwCl + TrC          | + TſC                                                                  |                |  |

| 7               | TdA(MREQf)                                                             | TwCh + TfC                 |                                                                        | -50            |  |

| 10              | TwMREQh                                                                | TwCh + TfC                 |                                                                        | -20            |  |

| 11              | TwMREQI                                                                | TcC                        |                                                                        | 30             |  |

| 26              | TdA(IORQf)                                                             | TcC                        |                                                                        | <b>-55</b>     |  |

| 29              | TdD(WRf)                                                               | TcC                        |                                                                        | -140           |  |

| 31              | TwWR                                                                   | TcC                        |                                                                        | -30            |  |

| 33              | TdD(WRf)                                                               | TwCl + TrC                 |                                                                        | -140           |  |

| 35              | TdWRr(D)                                                               | TwCl + TrC                 |                                                                        | <b>–55</b>     |  |

| 45              | TdCTr(A)                                                               | TwCl + TrC                 |                                                                        | 50             |  |

| 50              | TdM1f(lORQf)                                                           | 2TcC + TwCh + TfC          |                                                                        | <b>–50</b>     |  |

| Test Conditions | : V <sub>IH</sub> = V <sub>CC'</sub> -1.00V<br>V <sub>IL</sub> = 0.8 V | VoH = Vcc/2<br>VoL = Vcc/2 | V <sub>IHC</sub> = V <sub>CC</sub> -0.6 V<br>V <sub>H.C</sub> = 0.45 V | FLOAT = ±0.5 V |  |

<sup>†</sup>Units in nanoseconds (ns).

幸養所以 教養養者者有不養者不敢 日本道人人為此為此人之是是其一人人為此之

#### **ABSOLUTE MAXIMUM RATINGS**

Voltages on all pins with respect to V<sub>SS</sub>. . . . . . . . . . . . . -0.3V to V<sub>CC</sub> + 0.3V Voltage on all pins with respect to ground.....-0.3V to +7V Operating Case Temperature . . . . . . - 55°C to +125°C Storage Temperature Range . . . . . . . . - 65°C to +150°C

T-49-17-07

Absolute Maximum Power Dissipation . . . . . . . . 1W Stresses greater than those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; operation of the device at any condition above those indicated in the operational sections of these specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### STANDARD TEST CONDITIONS

The DC Characteristics and Capacitance sections below apply for the following standard test conditions, unless otherwise noted.

Military Operating Temperature Range (T<sub>C</sub>) -55°C to +125°C

Standard Military Test Condition +4.5V ≤ V<sub>CC</sub> ≤ +5.5V

All voltages are referenced to GND (0V). Positive current flows into the referenced pin.

All AC parameters assume a load capacitance of 100 pf. Add 15 ns delay for each 50 pf increase in load up to a maximum of 200 pf for the data bus. AC timing measurements are referenced to V<sub>CC</sub>/2 Volts.

<sup>C</sup> Guaranteed by Characterization/Design

## DC CHARACTERISTICS

| Symbol           | Parameter                               | Min                                | Max                               | Unit | Condition                                                                       |

|------------------|-----------------------------------------|------------------------------------|-----------------------------------|------|---------------------------------------------------------------------------------|

| VILC             | Clock Input Low Voltage                 | -0.3°                              | 0.45 <sup>a</sup>                 | v    |                                                                                 |

| VIHC             | Clock Input High Voltage                | V <sub>CC</sub> 6 <sup>a</sup>     | V <sub>CC</sub> + .3 <sup>c</sup> | ٧    |                                                                                 |

| VIL              | Input Low Voltage                       | -0.3 <sup>c</sup>                  | 0.8ª                              | ٧    |                                                                                 |

| V <sub>IH</sub>  | Input High Voltage                      | 2.2°                               | V <sub>CC</sub> c                 | ٧    |                                                                                 |

| VOL              | Output Low Voltage                      |                                    | 0.4ª                              | ٧    | $I_{OL} = 2.0  \text{mA}$                                                       |

| V <sub>OH1</sub> | Output High Voltage                     | 2.4ª                               |                                   | ٧    | $I_{OH} = -1.6  \text{mA}$                                                      |

| V <sub>OH2</sub> | Output High Voltage                     | V <sub>CC</sub> - 0.8 <sup>a</sup> |                                   | ٧    | I <sub>OH</sub> = -250 µA                                                       |

| ICC <sub>1</sub> | Power Supply Current                    |                                    |                                   |      | $V_{CC} = 5V$                                                                   |

| ·                | 6 MHz                                   |                                    | 35°                               | mA   | $V_{IH} = V_{CC} - 0.2V$<br>$V_{IL} = 0.2V$                                     |

| Icc <sub>2</sub> | Standby Supply Current                  |                                    | 100ª                              | μΑ   | V <sub>CC</sub> = 5V                                                            |

|                  |                                         |                                    |                                   |      | CLK = (0)<br>V <sub>IH</sub> = V <sub>CC</sub> - 0.2V<br>V <sub>IL</sub> = 0.2V |

| (L)              | laput Leakage Current                   |                                    | 10 <sup>a</sup>                   | μΑ   | $V_{IN} = 0.4 \text{ to } V_{CC}$                                               |

| lίO              | 3-State Output Leakage Current in Float | - 10 <sup>8</sup>                  | 10 <sup>28</sup>                  | μΑ   | V <sub>OUT</sub> = 0.4 to V <sub>CC</sub>                                       |

Measurements made with outputs floating.

A<sub>15</sub>-A<sub>0</sub>, D<sub>7</sub>-D<sub>0</sub>, MREQ, IORQ, RD, and WR.

Unmeasured pins returned to ground.

### **CAPACITANCE**

| Symbol .                    | Parameter          |                        | Min      | Max                 | Unit         |

|-----------------------------|--------------------|------------------------|----------|---------------------|--------------|

| C <sub>IN</sub>             | Input Capacitance  |                        |          | 10°                 | pf           |

| C <sub>OUT</sub>            | Output Capacitance |                        |          | 15°                 | pf           |

| OTES:                       |                    | Parameter Test Status: |          |                     | ·            |

| $I_A = 25$ °C, $f = 1$ MHz. |                    | 8 Tested               | C Guaran | teed by Characteriz | ation/Decian |

a Tested

b Guaranteed

lCO2 standby supply current is guaranteed only when the supplied clock is stopped at a low level during T4 of the machine cycle immediately following the execution of a HALT instruction.

<sup>4.</sup> Icc, is measured with 100pF capacitive only test load.

你是是是是是不完全人 医大龙 不意 多语语言不不

# 03E 08454

#### **PIN DESCRIPTIONS**

7-49-17-07le One (output, active Low).  $\overline{M1}$ , toge

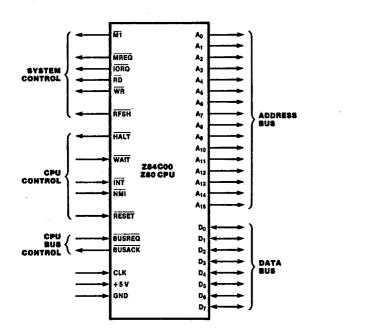

**A<sub>0</sub>-A<sub>15</sub>.** Address Bus (output, active High, 3-state). A<sub>0</sub>-A<sub>15</sub> form a 16-bit address bus. The Address Bus provides the address for memory data bus exchanges (up to 64K bytes) and for I/O device exchanges.

**BUSACK.** Bus Acknowledge (output, active Low). Bus Acknowledge indicates to the requesting device that the CPU address bus, data bus, and control signals MREQ, IORQ, RD, and WR have entered their high-impedance states. The external circuitry can now control these lines.

BUSREQ. Bus Request (input, active Low). Bus Request has a higher priority than \$\overline{NMI}\$ and is always recognized at the end of the current machine cycle. \$\overline{BUSREQ}\$ forces the CPU address bus, data bus, and control signals \$\overline{MREQ}\$, \$\overline{IORQ}\$, \$\overline{RD}\$, and \$\overline{WR}\$ to go to a high-impedance state so that other devices can control these lines. \$\overline{BUSREQ}\$ is normally wired-OR and requires an external pullup for these applications. Extended \$\overline{BUSREQ}\$ periods due to extensive DMA operations can prevent the CPU from properly refreshing dynamic RAMs.

**D<sub>0</sub>-D<sub>7</sub>.** Data Bus (input/output, active High, 3-state). D<sub>0</sub>-D<sub>7</sub> constitute an 8-bit bidirectional data bus, used for data exchanges with memory and I/O.

Halt. Halt State (output, active Low). HALT indicates that the CPU has executed a Halt instruction and is awaiting either a nonmaskable or a maskable interrupt (with the mask enabled) before operation can resume. While halted, the CPU executes NOPs to maintain memory refresh.

**INT.** Interrupt Request (input, active Low). Interrupt Request is generated by I/O devices. The CPU honors a request at the end of the current instruction if the internal software-controlled interrupt enable flip-flop (IFF) is enabled. INT is normally wired-OR and requires an external pullup for these applications.

IORQ. Input/Output Request (output, active Low, 3-state). IORQ indicates that the lower half of the address bus holds a valid I/O address for an I/O read or write operation. IORQ is also generated concurrently with M1 during an interrupt acknowledge cycle to indicate that an interrupt response vector can be placed on the data bus.

M1. Machine Cycle One (output, active Low). M1, together with MREQ, indicates that the current machine cycle is the opcode fetch cycle of an instruction execution. M1, together with IORQ, indicates an interrupt acknowledge cycle.

MREQ. Memory Request (output, active Low, 3-state). MREQ indicates that the address bus holds a valid address for a memory read or memory write operation.

NMI. Non-Maskable Interrupt (input, negative edge-triggered). NMI has a higher priority than INT. NMI is always recognized at the end of the current instruction, independent of the status of the interrupt enable flip-flop, and automatically forces the CPU to restart at location 0066H.

**RD.** Read (output, active Low, 3-state). RD indicates that the CPU wants to read data from memory or an I/O device. The addressed I/O device or memory should use this signal to gate data onto the CPU data bus.

**RESET.** Reset (input, active Low). RESET initializes the CPU as follows: it resets the interrupt enable flip-flop, clears the PC and Registers I and R, and sets the interrupt status to Mode 0. During reset time, the address and data bus go to a high-impedance state, and all control output signals go to the inactive state. Note that RESET must be active for a minimum of three full clock cycles before the reset operation is complete.

**RFSH.** Refresh (output, active Low). RFSH, together with MREQ, indicates that the lower seven bits of the system's address bus can be used as a refresh address to the system's dynamic memories.

WAIT. Wait (input, active Low). WAIT indicates to the CPU that the addressed memory or I/O devices are not ready for a data transfer. The CPU continues to enter a Wait state as long as this signal is active. Extended WAIT periods can prevent the CPU from refreshing dynamic memory properly.

WR. Write (output, active Low, 3-state). WR indicates that the CPU data bus holds valid data to be stored at the addressed memory or I/O location.

03E 08455

D

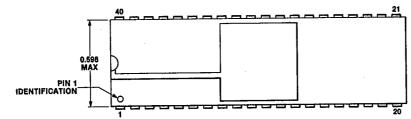

**PACKAGE PIN OUTS**

T-49-17-07

40 A10 39 A2 38 A3 37 A7 38 A6 35 A6 24 WAIT

23 BUSACK

22 WR

21 RD

**DIP and LCC Pin Functions**

40-Pin Dual-in-Line Package (DIP), Pin Assignments, Top View

03E 08456

D

# **MIL-STD-883 MILITARY PROCESSED PRODUCT**

T-49-17-07

- Mil-Std-883 establishes uniform methods and procedures for testing microelectronic devices to insure the electrical, mechanical, and environmental integrity and reliability that is required for military applications.

- Mil-Std-883 Class B is the industry standard product assurance level for military ground and aircraft application.

- The total reliability of a system depends upon tests that are designed to stress specific quality and reliability concerns that affect microelectronic products.

- The following tables detail the 100% screening and electrical tests, sample electrical tests, and Qualification/Quality Conformance testing required.

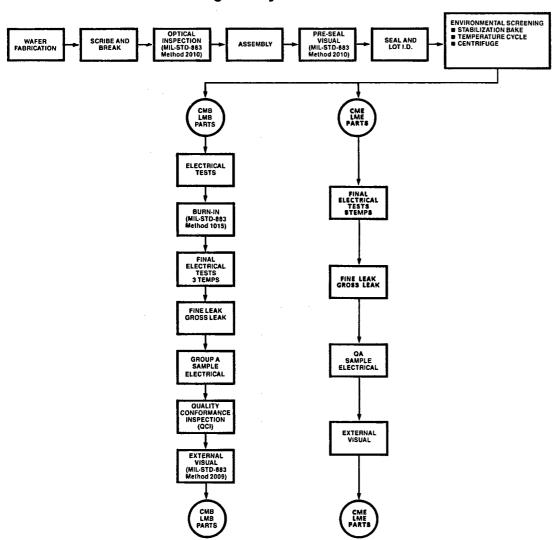

# **Zilog Military Product Flow**

Method 5004

9984043 ZILOG INC

03E 08457

T-49-17-07-Table I MIL-STD-883 Class B Screening Requirements

| 2010 | <del></del>                                                                                                                            | Requiremen                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------|----------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|      | Condition B                                                                                                                            | 100%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 1008 | Condition C                                                                                                                            | 100%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 1010 | Condition C                                                                                                                            | 100%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 2001 | Condition E or D <sup>(Note 1)</sup> , Y <sub>1</sub> Axis Only                                                                        | 100%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|      | Zilog Military Electrical Specification<br>Static/DC T <sub>C</sub> = +25°C                                                            | 100%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 1015 | Condition D <sup>(Note 2)</sup> , 160 hours,<br>$T_A = +125$ °C                                                                        | 100%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|      | Zilog Military Electrical Specification<br>Static/DC T <sub>C</sub> = +25°C                                                            | 100%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|      | PDA = 5%                                                                                                                               | 100%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|      | Zilog Military Electrical Specification<br>Static/DC T <sub>C</sub> = +125°C, -55°C<br>Functional, Switching/AC T <sub>C</sub> = +25°C | 100%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 1014 | Condition B                                                                                                                            | 100%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 1014 | Condition C                                                                                                                            | 100%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|      | ·                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 5005 | (See Table II)                                                                                                                         | Sample                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|      |                                                                                                                                        | Sample                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|      | •                                                                                                                                      | Sample                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 5005 | (See Table V)                                                                                                                          | Sample                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 2009 |                                                                                                                                        | 100%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|      |                                                                                                                                        | 100%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|      | 1008<br>1010<br>2001<br>1015<br>1015<br>1014<br>1014<br>5005<br>5005<br>5005<br>5                                                      | 1008 Condition C  1010 Condition C  2001 Condition E or D(Note 1), Y1 Axis Only  Zilog Military Electrical Specification Static/DC TC = +25°C  1015 Condition D(Note 2), 160 hours, TA = +125°C  Zilog Military Electrical Specification Static/DC TC = +25°C  PDA = 5%  Zilog Military Electrical Specification Static/DC TC = +125°C, -55°C Functional, Switching/AC TC = +25°C  1014 Condition B 1014 Condition C  5005 (See Table II) 5005 (See Table IV) 5005 (See Table IV) 5005 (See Table V) |

# NOTES:

mass of >5 grams.

2. In process of fully implementing of Condition D Burn-In Circuits. Contact factory for copy of specific burn-in circuit available.

3. Performed periodically as required by Mil-Std-883, paragraph 1.2.1 b(17).

<sup>1.</sup> Applies to larger packages which have an inner seal or cavity perimeter of two inches or more in total length or have a package

03E 08458

00436

# Table II Group A Sample Electrical Tests MIL-STD-883 Method 5005

T-49-17-07

| Subgroup    | Tests        | Temperature (T <sub>C</sub> ) | LTPD<br>Max Accept = 2 |

|-------------|--------------|-------------------------------|------------------------|

| Subgroup 1  | Static/DC    | +25°C                         | 2                      |

| Subgroup 2  | Static/DC    | +125°C                        | 3                      |

| Subgroup 3  | Static/DC    | -55°C                         | 5                      |

| Subgroup 7  | Functional   | +25°C                         | 2                      |

| Subgroup 8  | Functional   | -55°C and +125°C              | 5                      |

| Subgroup 9  | Switching/AC | +25°C                         | 2                      |

| Subgroup 10 | Switching/AC | +125°C                        | 3                      |

| Subgroup 11 | Switching/AC | −55°C                         | 5                      |

### NOTES:

A single sample may be used for all subgroup testing. Where required size exceeds the lot size, 100% inspection shall be allowed.

Group A testing by subgroup or within subgroups may be performed in any sequence unless otherwise specified.

<sup>•</sup> The specific parameters to be included for tests in each subgroup shall be as specified in the applicable detail electrical specification. Where no parameters have been identified in a particular subgroup or test within a subgroup, no Group A testing is required for that subgroup or test.

T-49-17-07

# Table III Group B

Sample Test Performed Every Week to

Test Construction and insure integrity of Assembly Process. MIL-STD-883 Method 5005

| Subgroup                                                           | Mil-Std-883<br>Method | Test Condition                                                                                                                                                            | Quantity or<br>LTPD/Max Accept |

|--------------------------------------------------------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|

| Subgroup 1 Physical Dimensions                                     | 2016                  |                                                                                                                                                                           | 2/0                            |

| Subgroup 2 Resistance to Solvents                                  | 2015                  |                                                                                                                                                                           | 4/0                            |

| Subgroup 3<br>Solderability                                        | 2003                  | Solder Temperature<br>+245°C ± 5°C                                                                                                                                        | 15(Note 1)                     |

| Subgroup 4 Internal Visual and Mechanical                          | 2014                  |                                                                                                                                                                           | 1/0                            |

| Subgroup 5<br>Bond Strength                                        | 2011                  | С                                                                                                                                                                         | 15 <sup>(Note 2)</sup>         |

| Subgroup 6(Note 3) Internal Water Vapor Content                    | 1018                  | 1000 ppm.<br>maximum at +100°C                                                                                                                                            | 3/0 or 5/1                     |

| Subgroup 7 <sup>(Note 4)</sup> Seal 7a) Fine Leak 7b) Gross Leak   | 1014                  | 7a) <b>B</b><br>7b) C                                                                                                                                                     | 5                              |

| Subgroup 8 <sup>(Note 5)</sup> Electrostatic Discharge Sensitivity | 3015                  | Zilog Military Electrical Specification Static/DC T <sub>C</sub> = +25°C A = 20-2000V B = >2000V Zilog Military Electrical Specification Static/DC T <sub>C</sub> = +25°C | 15/0                           |

# NOTES:

- Number of leads inspected selected from a minimum of 3 devices.

Number of bond pulls selected from a minimum of 4 devices.

Test applicable only if the package contains a dessicant.

Test not required if either 100% or sample seal test is performed between final electrical tests and external visual during Class B screening.

Test required for initial qualification and product redesign.

03E 08460

T-49-17-07 Table IV Group C

Sample Test Performed Periodically to Verify Integrity of the Die.

MIL-STD-883 Method 5005

| Subgroup                           | Mil-Std-883<br>Method | Test Condition                                                                   | Quantity or<br>LTPD/Max Accept |

|------------------------------------|-----------------------|----------------------------------------------------------------------------------|--------------------------------|

| Subgroup 1                         |                       |                                                                                  | ·····                          |

| Steady State Operating Life        | 1005                  | Condition D <sup>(Note 1)</sup> , 1000 hours at<br>+ 125°C                       | 5                              |

| End Point Electrical Tests         |                       | Zilog Military Electrical Specification<br>T <sub>C</sub> = +25°C, +125°C, -55°C |                                |

| Subgroup 2                         |                       |                                                                                  |                                |

| Temperature Cycle                  | 1010                  | Condition C                                                                      |                                |

| Constant Acceleration (Centrifuge) | 2001                  | Condition E or D(Note 2), Y1 Axis Only                                           |                                |

| Seal                               | 1014                  |                                                                                  | 15                             |

| 2a) Fine Leak                      |                       | 2a) Condition B                                                                  |                                |

| 2b) Gross Leak                     |                       | 2b) Condition C                                                                  |                                |

| Visual Examination                 | 1010 or 1011          |                                                                                  |                                |

| End Point Electrical Tests         |                       | Zilog Military Electrical Specification<br>T <sub>C</sub> = +25°C, +125°C, -55°C |                                |

#### NOTE:

NOTE:

1. In process of fully implementing Condition D Burn-In Circuits. Contact factory for copy of specific burn-in circuit available.

2. Applies to larger packages which have an inner seal or cavity perimeter of two inches or more in total length or have a package mass of ≥5 grams.

03E 08461

T-49-17-07

Table V Group D

Sample Test Performed Periodically to Insure Integrity of the Package.

MiL-STD-883 Method 5005

| Subgroup                                      | Mil-Std-883<br>Method | Test Condition                                                                   | Quantity or<br>LTPD/Max Accep         |

|-----------------------------------------------|-----------------------|----------------------------------------------------------------------------------|---------------------------------------|

| Subgroup 1                                    |                       |                                                                                  | · · · · · · · · · · · · · · · · · · · |

| Physical Dimensions                           | 2016                  |                                                                                  | 15                                    |

| Subgroup 2<br>Lead Integrity                  | 2004                  | Condition B <sub>2</sub> or D <sup>(Note 1)</sup>                                | 15                                    |

| Subgroup 3<br>Thermal Shock                   | 1011                  | Condition B minimum,<br>15 cycles minimum                                        |                                       |

| Temperature Cycling                           | 1010                  | Condition C, 100 cycles minimum                                                  | 15                                    |

| Moisture Resistance                           | 1004                  |                                                                                  |                                       |

| Seal<br>3a) Fine Leak<br>3b) Gross Leak       | 1014                  | 3a) Condition B 3b) Condition C                                                  |                                       |

| Visual Examination End Point Electrical Tests | 1004 or 1010          | Zilog Military Electrical Specification<br>T <sub>C</sub> = +25°C, +125°C, -55°C |                                       |

| Subgroup 4<br>Mechanical Shock                | 2002                  | Condition B minimum                                                              |                                       |

| Vibration Variable Frequency                  | 2007                  | Condition A minimum                                                              |                                       |

| Constant Acceleration (Centrifuge)            | 2001                  | Condition E or D <sup>(Note 2)</sup> , Y <sub>1</sub> Axis Only                  | 15                                    |

| Seal<br>4a) Fine Leak<br>4b) Gross Leak       | 1014                  | 4a) Condition B 4b) Condition C                                                  |                                       |

| Visual Examination                            | 1010 or 1011          |                                                                                  |                                       |

| End Point Electrical Tests                    | •                     | Zilog Military Electrical Specification<br>T <sub>C</sub> = +25°C, +125°C, -55°C |                                       |

| Subgroup 5 Salt Atmosphere                    | 1009                  | Condition A minimum                                                              |                                       |

| Seal<br>5a) Fine Leak<br>5b) Gross Leak       | 1014                  | 5a) Condition B 5b) Condition C                                                  | 15                                    |

| Visual Examination                            | 1009                  |                                                                                  |                                       |

| Subgroup 6 Internal Water Vapor Content       | 1018                  | 5,000 ppm. maximum water content at +100°C                                       | 3/0 or 5/1                            |

| Subgroup 7(Note 3) Adhesion of Lead Finish    | 2025                  |                                                                                  | 15(Note 4)                            |

| Subgroup 8 <sup>(Note 5)</sup><br>Lid Torque  | 2024                  |                                                                                  | 5/0                                   |

- Lead Integrity Condition D for leadless chip carriers.

Applies to larger packages which have an inner seal or cavity perimeter of two inches or more in total length or have a package mass of ≥5 grams.

- 3. Not applicable to leadless chip carriers.

- 4. LTPD based on number of leads.

- 5. Not applicable for solder seal packages.

03E 08462

T-49-17-07

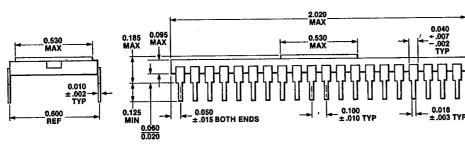

# PACKAGE INFORMATION

40-Pin Ceramic Dual In-line Package (DIP)

The way of the transfer of the second of the

D

9984043 ZILOG INC

03E 08463

ORDERING INFORMATION

T-49-17-07

CMOS Z80 CPU, 6.0 MHz

40-pin DIP Z84C0006CME Z84C0006CMB

Codes

**PACKAGE** C = Ceramic

TEMPERATURE  $M = -55^{\circ}C$  to  $+125^{\circ}C$  **ENVIRONMENTAL** E = Hermetic Standard

Longer Lead Time B = 833 Class B Military

Example: Z84C0006CMB is a CMOS 8400, 6MHz, Ceramic, -55 C to 125 C 883C Standard Flow.