# 20 characters × 2 lines COG module RCM2072R

The RCM2072R is a reflective TN type liquid crystal module with a built-in controller/driver LSI and a display capacity of 20 characters × 2 lines.

### Applications

Printers, copiers, facsimiles, etc.

### Features

- 1) Wide viewing angle and high contrast.

- 2) 5×7 dot character matrix with cursor.

- 3) Interfaces with 4-bit or 8-bit MPUs.

- 4) Displays up to 237 characters and special symbols

- Custom character patterns are displayed with the character RAM.

- Abundant instruction set including clear display, cursor on/off, and character blinking.

- Compact and lightweight for easy assembly to the host instrument.

- 8) Operable on single 5V power supply.

- 9) Low power consumption.

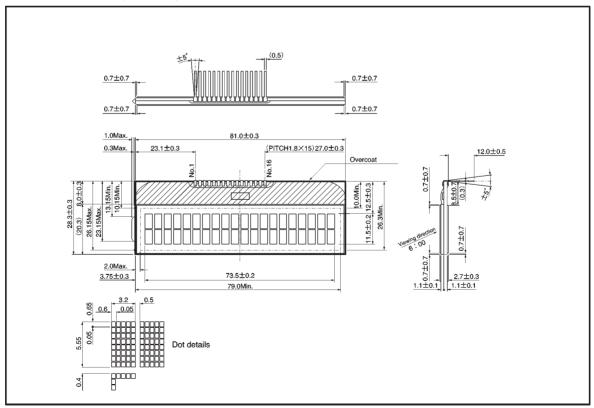

### External dimensions (Units: mm)

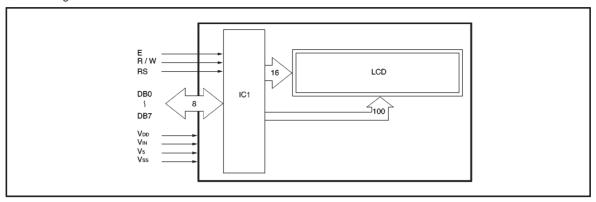

# ■Block diagram

# Pin assignments

| Pin No. | Signal | Pin No. | Signal          |

|---------|--------|---------|-----------------|

| 1       | RS     | 9       | DB5             |

| 2       | R/W    | 10      | DB6             |

| 3       | E      | 11      | DB7             |

| 4       | DB0    | 12      | Vss             |

| 5       | DB1    | 13      | V <sub>DD</sub> |

| 6       | DB2    | 14      | Vin             |

| 7       | DB3    | 15      | <b>V</b> 5      |

| 8       | DB4    | 16      | GND             |

Vss and GND are separate.

Vss is the earth for the IC.

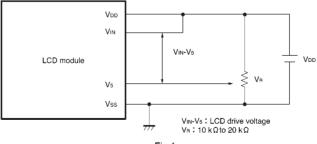

### Power supply example

# ●Absolute maximum ratings (Ta = 25°C)

| Parameter                  | Symbol                           | Min. | Max.    | Unit |

|----------------------------|----------------------------------|------|---------|------|

| Logic power supply voltage | V <sub>DD</sub> -V <sub>SS</sub> | -0.3 | 6.0     | V    |

| LCD drive voltage          | V <sub>DD</sub> -V <sub>5</sub>  | -0.3 | 6.0     | V    |

| Input voltage              | Vı                               | -0.3 | Vpp+0.3 | V    |

| Operating temperature      | Topr                             | 0    | 50      | Ç    |

| Storage temperature        | Tstg                             | -20  | 70      | Ç    |

# • Electrical characteristics ( $V_{DD} = 5.0 \pm 5\%$ , Ta = $25^{\circ}$ C)

| Parameter                 | Symbol | Min.    | Тур. | Max.               | Unit | Conditions              |

|---------------------------|--------|---------|------|--------------------|------|-------------------------|

| High level input voltage  | Vıн    | 0.7Vdd  | _    | _                  | V    | _                       |

| Low level input voltage   | VIL    | _       | _    | 0.2V <sub>DD</sub> | V    | _                       |

| High level output voltage | Vон    | 0.75Vpb | _    | _                  | V    | I <sub>ОН</sub> =-0.1mA |

| Low level output voltage  | Vol    | _       | _    | 0.2V <sub>DD</sub> | V    | IoL=0.1mA               |

| Operating voltage         | VLCD   | 3.0     | _    | 5.0                | V    | 1 / 4Bias               |

| Power supply current      | loo    | _       | 1.5  | 2.5                | mA   | V <sub>DD</sub> =5.0V   |

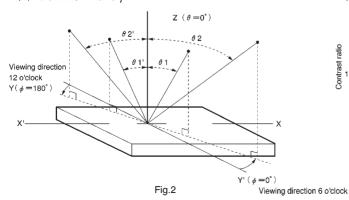

# ●Optical characteristics (Ta = 25°C)

When viewing from below

| Parameter      | Symbol | Min. | Тур. | Max. | Unit | Conditions                               |

|----------------|--------|------|------|------|------|------------------------------------------|

| Rise time      | Tr     | _    | 100  | 250  | ms   | $\theta = 10^{\circ},  \phi = 0^{\circ}$ |

| Fall time      | Td     | _    | 150  | 250  | ms   | $\theta = 10^{\circ},  \phi = 0^{\circ}$ |

| Contrast ratio | К      | _    | 3    | _    | _    | $\theta = 10^{\circ},  \phi = 0^{\circ}$ |

|                | θ 1    | _    | _    | 10   | deg  | K≧1.4                                    |

| Viouring angle | θ2     | 40   | _    | _    | deg  | φ=0°                                     |

| Viewing angle  | ,      | ±30  |      |      | dos  | K≧1.4                                    |

|                | φ      |      | _    | _    | deg  | θ=20°                                    |

# (1) Definition $\theta$ and $\phi$

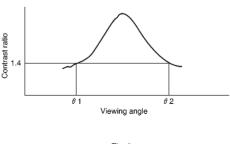

# (2) Definition of viewing angles

Fig.3

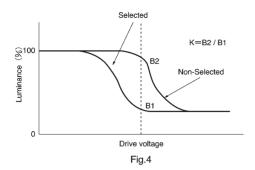

### (3) Definition of contrast ratio "K"

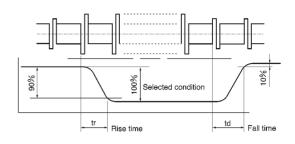

### (4) Definition of optical response

Fig.5

### Pin functions

| Symbol                            | Level    | IN / OUT |                                                                                                                                          | Function                                                                                             |  |  |  |

|-----------------------------------|----------|----------|------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|--|--|--|

| Vss                               | _        | _        | 0V                                                                                                                                       | Earth                                                                                                |  |  |  |

| V <sub>DD</sub>                   | _        | _        | 5.0V                                                                                                                                     | Power supply voltage                                                                                 |  |  |  |

| V <sub>IN</sub><br>V <sub>5</sub> | 1        |          | 3.0~5.0V<br>(V <sub>DD</sub> -V <sub>5</sub> )                                                                                           | The V₅ pin is for the liquid crystal contrast adjustment should be kept within the range Vɒp≧V₅≧Vss. |  |  |  |

| GND                               | 1        | _        | F                                                                                                                                        | rame GND                                                                                             |  |  |  |

| RS                                | H/L      | IN       | Register selection signal.  0: Instruction register (writing) Busy flag, address counter (reading)  1: Data register (reading / writing) |                                                                                                      |  |  |  |

| R/W                               | H/L      | IN       | Reading (R) and writing<br>0: Writing MPU→LCD n<br>1: Reading MPU←LCD                                                                    | nodule                                                                                               |  |  |  |

| E                                 | H, H / L | IN       | Data reading and writin                                                                                                                  | g start signal.                                                                                      |  |  |  |

| DB0                               | H/L      | IN / OUT | The lower 4 line data buses are 3-state bi-directional. They are not used during 4-bit operation and must be fixed to GND.               |                                                                                                      |  |  |  |

| DB4                               | H/L      | IN / OUT | The upper 4 line data buses are 3-state bi-directional. DB7 can also be used as a busy flag.                                             |                                                                                                      |  |  |  |

Note: In order to be able to interface with 4-bit or 8-bit MPUs, the module supports data transfer with two transmissions of 4 bits at a time or one transmission of 8 bits at once.

- (1) When the interface data length is 4 bits, data is transferred between the MPU along DB4 through DB7 buses and DB0 through DB3 buses are not used. Data transferral is completed after two transfers of 4 bit data. First the upper nibble (contents of DB4 through DB7 during 8-bit interfacing) is transferred and then the lower nibble (contents of DB0 through DB3 during 8-bit interfacing) is transferred. Check for busy flag occurs after the second 4-bit data (one instruction) is transferred. At that time, the busy flag and address counter data is also output in two 4-bit increments.

- (2) When the interface data length is 8 bits, the data DB0 through DB7 is transferred along the eight data buses.

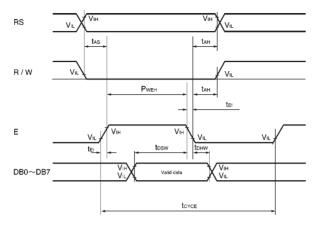

# ●Timing chart

# (1) Writing

Fig.6

| Parameter                 | Symbol    | Min. | Тур. | Max. | Unit | Conditions |

|---------------------------|-----------|------|------|------|------|------------|

| Enable cycle time         | tcyce     | 500  | _    | _    | ns   |            |

| Enable pulse time         | Pweh      | 250  | _    | _    | ns   |            |

| Enable rise and fall time | ter / tef | _    | _    | 20   | ns   |            |

| Address setup time        | tas       | 40   | _    | _    | ns   | Fig.6      |

| Address hold time         | tан       | 10   | _    | _    | ns   |            |

| Data setup time           | tosw      | 60   | _    | _    | ns   |            |

| Data hold time            | tohw      | 10   | _    | _    | ns   |            |

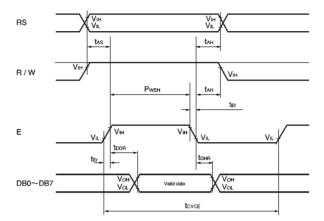

# (2) Reading

Fig.7

| Parameter                 | Symbol    | Min. | Тур. | Max. | Unit | Conditions |

|---------------------------|-----------|------|------|------|------|------------|

| Enable cycle time         | tcyce     | 500  | _    | _    | ns   |            |

| Enable pulse time         | Pweh      | 250  | _    | _    | ns   |            |

| Enable rise and fall time | ter / ter | _    | _    | 20   | ns   |            |

| Address setup time        | tas       | 40   | _    | _    | ns   | Fig.7      |

| Address hold time         | tah       | 10   | _    | _    | ns   |            |

| Data delay time           | toda      | _    | _    | 250  | ns   |            |

| Data hold time            | tohr      | 20   | _    | _    | ns   |            |

### Instructions

| Instruction                    |                                                                             |                                                                                                   |                                                                                                                         |                                                                                    | Co    | ode   |      |     |     |                      | Description                                                                                                                                                                       | Execution time<br>Max.                            |

|--------------------------------|-----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|-------|-------|------|-----|-----|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|

| mstruction                     | RS                                                                          | R/W                                                                                               | DB7                                                                                                                     | DB6                                                                                | DB5   | DB4   | DB3  | DB2 | DB1 | DB0                  | Description                                                                                                                                                                       | fosc=250kHz                                       |

| Clear display                  | 0                                                                           | 0                                                                                                 | 0                                                                                                                       | 0                                                                                  | 0     | 0     | 0    | 0   | 0   | 1                    | Clears display and sets address 0 of DD RAM to address counter.                                                                                                                   | 1.64ms                                            |

| Home cursor                    | 0                                                                           | 0                                                                                                 | 0                                                                                                                       | 0                                                                                  | 0     | 0     | 0    | 0   | 1   | *                    | Sets address 0 of DD RAM to address counter and returns a shifted display to original position. The contents of DD RAM are unchanged.                                             | 1.64ms                                            |

| Entry mode set                 | 0                                                                           | 0                                                                                                 | 0                                                                                                                       | 0                                                                                  | 0     | 0     | 0    | 1   | I/D | s                    | Sets the cursor move direction and specifies whether or not to shift display. This operation occurs when reading or writing data.                                                 | 40 μs                                             |

| Display on / off control       | 0                                                                           | 0                                                                                                 | 0                                                                                                                       | 0                                                                                  | 0     | 0     | 1    | D   | С   | В                    | Turns display on or off (D), turns cursor on or off (C), or blinks the character at the cursor position (B).                                                                      | 40 μs                                             |

| Cursor / display shift         | 0                                                                           | 0                                                                                                 | 0                                                                                                                       | 0                                                                                  | 0     | 1     | S/C  | R/L | *   | *                    | Moves cursor or shifts display without changing the DD RAM.                                                                                                                       | 40 μs                                             |

| Function set                   | 0                                                                           | 0                                                                                                 | 0                                                                                                                       | 0                                                                                  | 1     | DL    | N    | SD1 | SD2 | CD                   | Sets the interface data length (DL),<br>SEG data transfer direction (SD1,SD2),<br>and COM data transfer direction(CD).                                                            | 40 μs                                             |

| CG RAM address set             | 0                                                                           | 0                                                                                                 | 0                                                                                                                       | 1                                                                                  | 1 Aca |       |      |     |     |                      | Sets the CG RAM address.<br>Data received after this is CG RAM data.                                                                                                              | 40 μs                                             |

| DD RAM address set             | 0                                                                           | 0                                                                                                 | 1                                                                                                                       |                                                                                    |       |       | Add  |     |     |                      | Sets the DD RAM address.<br>Data received after this is DD RAM data.                                                                                                              | 40 μs                                             |

| Read busy flag address         | 0                                                                           | 1                                                                                                 | BF                                                                                                                      |                                                                                    |       |       | AC   |     |     |                      | Reads the busy flag signifying internal operations<br>in progress and reads the contents of the address<br>counter.                                                               | 0μs                                               |

| Write data to CG or DD RAM     | 1                                                                           | 0                                                                                                 |                                                                                                                         |                                                                                    | ,     | Write | Data | a   |     |                      | Data is written from the DD RAM or CG RAM.                                                                                                                                        | 40 μs<br>tadd=6 μs                                |

| Read data from CG or DD<br>RAM | 1                                                                           | 1                                                                                                 |                                                                                                                         |                                                                                    | 1     | Read  | Data | а   |     |                      | Data is read to DD RAM or CG RAM.                                                                                                                                                 | 40 μs<br>tadd=6 μs                                |

|                                | S=-<br>S/C:<br>R/L=<br>DL=<br>CD=<br>CD=<br>SD1<br>SD1<br>SD1<br>SD1<br>BF= | 1: Acc<br>=1: D<br>=1: R<br>=1: 8 l<br>1: 2 lir<br>=0: C<br>=1: C<br>=0,S<br>=1,S<br>=0,S<br>=1,S | compa<br>pisplay<br>ight s<br>bit, DI<br>nes, N<br>OM1-<br>OM16<br>D2=<br>D2=<br>D2=<br>D2=<br>D2=<br>D2=<br>D2=<br>D2= | nies c<br>/ shift, F<br>=0:<br>+CON<br>3→CO<br>0: SEO<br>0: SEO<br>1: SEO<br>opera | OM16  |       |      |     |     | 3100<br>:G51<br>:EG1 | DD RAM: Display data RAM CG RAM: Character generator RAM Acs: CG RAM address Add: DD RAM address (corresponds to cursor address) AC: Address counter used for both DD and CG RAM. | Execution<br>times will<br>vary with<br>frequency |

(Example) When fosc = 270kHz

$$40\mu s \times \frac{250}{270} = 37\mu s$$

● Character code and corresponding character pattern

| Character | 1    | and c | 1    | Jonain | g cha    | actor | patter      |              |              | 1        |      |      | 1    | I         |             |          |

|-----------|------|-------|------|--------|----------|-------|-------------|--------------|--------------|----------|------|------|------|-----------|-------------|----------|

| Upper     | 0000 | 0001  | 0010 | 0011   | 0100     | 0101  | 0110        | 0111         | 1000         | 1001     | 1010 | 1011 | 1100 | 1101      | 1110        | 1111     |

| 0000      | *1   |       |      |        |          |       | *•          | <b></b> .    |              |          |      |      | -::: | <b></b> . |             | <b>!</b> |

| 0001      | *2   |       |      | 1      |          |       | -:::        |              |              |          |      |      | -    | i;        |             | :::      |

| 0010      | *3   |       | ***  |        |          |       |             | ļ            |              |          | :"   | ·    | :::  | .::¹      |             |          |

| 0011      | *4   | 1     | -    | .:     |          | :;    | :           | <u>:::</u> . |              |          |      | :::  | :    | ===       | <u>::</u> . | :::      |

| 0100      | *5   |       | :::  |        |          | i     | :::         | ÷            | -==          |          | ٠.   |      | ŀ    | •         | <b></b>     | :::      |

| 0101      | *6   |       | :::: |        |          | 1!    |             | 11           |              |          | ::   | .:   |      |           | :::         |          |

| 0110      | *7   |       |      |        | <b>!</b> | Ļ     | •           | i.,.:        | -==          |          |      |      | •••• |           | <u> </u>    |          |

| 0111      | *8   |       | :    | :      |          |       | :           | ļ.,i         | : <u>.</u> . |          | ·;;: |      | ;::° |           | ::::        |          |

| 1000      | *1   |       | 1    |        | -        | ×     | -           | $\times$     |              | •        | ·4.  | •::: | :::: | Ņ         | .;:"        | ×        |

| 1001      | *2   |       | )    | •      | I        | ¥     |             | •!           |              |          | *::  | •    |      | 11.       | 1           | •        |

| 1010      | *3   | ֥     | :4:  | ::     |          | ::::  | :           | :::          |              |          |      |      | 1    | <u></u>   |             |          |

| 1011      | *4   |       |      | ::     | K.       |       |             | -{           |              | <b>:</b> | :#   | ;    |      |           | ∷           |          |

| 1100      | *5   |       | :    | ∹.     |          | #     | i.          |              | 1            |          | †:   | ::   | :    | :::I      |             |          |

| 1101      | *6   | i     |      | *****  | H        |       | <b>!</b> :: | <b>}</b>     |              |          |      |      | •••  | :         |             |          |

| 1110      | *7   | 400   | ::   | ÷      | N        | ۰۰.   | <b>!</b> ": |              |              |          |      | 111  |      | •••       | i"i         |          |

| 1111      | *8   | *     |      | •      |          | ••••  | :::         | <b></b>      |              |          | •::  | ••   | **   | :::       |             |          |

### Reset function

When you turn on the power supply, the module automatically returns to its initial (reset) settings. At the initial settings, the busy flag (BF) becomes "1." The busy status last 10 ms from when V<sub>DD</sub> reaches 4.5V. At the initial settings, following instructions are carried out.

- (1) Clear display

- (2) Function set

| 8-bit interface data length                           | (DL = 1)           |

|-------------------------------------------------------|--------------------|

| Two line display                                      | (N = 1)            |

| SEG signal transfer direction SEG1→SEG50→SEG51→SEG100 | (SD1 = 0, SD2 = 0) |

(CD = 0)

COM signal transfer direction COM1→COM16

(3) Display on/off control

| Display off  | (D = 0) |

|--------------|---------|

| Cursor off   | (C = 0) |

| Blinking off | (B = 0) |

(4) Entry mode set

+1 (increment) (I/D = 1)(S = 0)

No shift

\* The internal reset circuit may not operate properly due to conditions with the power supply. If this is the case, use the appropriate instruction to reset the settings.

### Operation notes

- (1) Handling precautions

- Protect the module from strong shocks as they can cause damage or defective operation.

- The polarizing plate on the surface of the module is soft and can easily be scratched. Wipe away dirt and dust using an alcohol-based cleanser.

- If the liquid crystal panel is damaged and liquid crystal contacts your clothing or body, wash immediately with soap and water.

- If the module is to be used for long periods subjected to direct sunlight, employ a filter to block the ultraviolet

- Do not use the module in areas of high temperature or high humidity. Do not use the module in locations exposed to direct sunlight or fluorescent light.

- A protective film (polyethylene) is pasted over ROHM liquid crystal modules to protect the panel surfaces. When peeling this film off, be sure to peel as slow as possible in order to minimize the generation of static electricity.

- (2) Precautions during operation

- Do not connect or disconnect the module while the power supply is turned on.

- Input the input signal after the module power supply is turned on. When turning it off, turn off the input signal first. Otherwise the IC may be damaged by the latch-up phenomenon.