### General Description

The MAX281 is a 5th-order all-pole instrumentation lowpass filter with no DC error. The filter uses an external resistor and capacitor to isolate the integrated circuit from the DC signal path, thus providing DC accuracy.

The external resistor and capacitor together with the on-chip 4th-order switched capacitor filter form a 5th-order Bessel lowpass filter. Bessel lowpass filters provide linear phase (constant group delay) response from DC to beyond the filter cutoff frequency, with some reduction in stopband attenuation.

The filter cutoff frequency is set by a clock which can be either internally generated or externally provided. The clock to cutoff frequency ratio of 101 allows easy removal of clock ripple.

MAX281A provides tighter specfications than the MAX281B for internal clock oscillator frequency and buffer amplifier offset voltage.

MAX280 is available for applications requiring a maximally flat (Butterworth) amplitude response.

### **Applications**

Anti-Aliasing Filters

Data Loggers

Digital Voltmeters

Weigh Scales

Strain Gauges

### \_\_\_\_ Features

- Bessel Lowpass Filter with No DC Error

- Low Passband Noise

- DC to 20kHz Cutoff Frequency

- ♦ 5th-Order All-Pole Bessel Response

- Internal or External Clock

- Cascadable for Higher Order Rolloff

- **♦ Buffered Output Available**

- ♦ 8-Pin DIP or 16-Pin Wide SO Packages

### **Ordering Information**

| PART       | TEMP. RANGE     | PIN-PACKAGE   |

|------------|-----------------|---------------|

| MAX281ACPA | 0°C to +70°C    | 8 Plastic DIP |

| MAX281BCPA | 0°C to +70°C    | 8 Plastic DIP |

| MAX281ACWE | 0°C to +70°C    | 16 Wide SO    |

| MAX281BCWE | 0°C to +70°C    | 16 Wide SO    |

| MAX281C/D  | 0°C to +70°C    | Dice          |

| MAX281AEPA | -40°C to +85°C  | 8 Plastic DIP |

| MAX281BEPA | -40°C to +85°C  | 8 Plastic DIP |

| MAX281AEWE | -40°C to +85°C  | 16 Wide SO    |

| MAX281BEWE | -40°C to +85°C  | 16 Wide SO    |

| MAX281AMJA | -55°C to +125°C | 8 CERDIP      |

| MAX281BMJA | -55°C to +125°C | 8 CERDIP      |

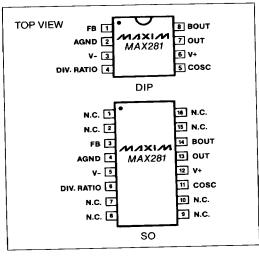

### Pin Configurations

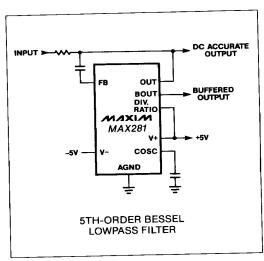

# Typical Operating Circuit

Maxim Integrated Products 6-91

### **ABSOLUTE MAXIMUM RATINGS**

| Total Supply Voltage (V+ to V-)                              | 17V       |

|--------------------------------------------------------------|-----------|

| Input Voltage at Any Pin $V_{-}(-0.3V) \le V_{IN} \le V_{+}$ | + (+0.3V) |

| Power Dissipation                                            | ( 0.04)   |

| Plastic DIP (derate at 6.25mW/°C above 70°C)                 | 500mW     |

| CERDIP (derate at 8.00mW/°C above 70°C)                      | 640mW     |

| SO (derate at 9.52mW/°C above 70°C)                          | 762mW     |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **ELECTRICAL CHARACTERISTICS**

(V+ = +5V, V- = -5V, T<sub>A</sub> = +25°C, unless otherwise noted, AC output measured at OUT pin, Figure 1.)

| PARAMETER                                                                            | CONDITIONS                                                                                                 |                                                                                     | MIN                | TYP                | MAX        | UNITS             |

|--------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|--------------------|--------------------|------------|-------------------|

| Operating Supply Voltage<br>Dual Supply<br>Single Supply                             |                                                                                                            |                                                                                     | ±2.375<br>4.75     |                    | ±8<br>16   | v                 |

| Power-Supply Current                                                                 |                                                                                                            | COSC (Pin 5 to V-) = 100pF<br>T <sub>A</sub> = T <sub>MIN</sub> to T <sub>MAX</sub> |                    | 5                  | 10         | mA                |

| Input Frequency Range                                                                |                                                                                                            |                                                                                     |                    | 0-20               |            | kHz               |

| Filter Gain at  f <sub>IN</sub> = 0  f <sub>IN</sub> = 0.5f <sub>C</sub> (Note 1)    | f <sub>CLK</sub> = 100kHz<br>Pin 4 at V+                                                                   | T <sub>A</sub> = +25°C                                                              | :                  | 0<br>-0.9          | -1.2       | KI IZ             |

| $f_{IN} = f_{C}$ $f_{IN} = 2f_{C}$ $f_{IN} = 4f_{C}$                                 | C = 0.01μF<br>R = 18.61kΩ                                                                                  | T <sub>A</sub> = T <sub>MIN</sub> to T <sub>MAX</sub>                               | -2.5<br>-12<br>-35 | -3.5<br>-14<br>-39 |            | dB                |

| Clock to Cutoff Frequency Ratio fclk/fc                                              | f <sub>CLK</sub> = 100kHz, Pin 4 at V+<br>C = 0.01μF, R = 25.78kΩ                                          |                                                                                     |                    | 101                |            |                   |

| Filter Gain at f <sub>IN</sub> = 4fc                                                 | $f_{CLK} = 400$ kHz, Pin 4 at V+<br>C = $0.01\mu$ F, R = $4.65$ k $\Omega$<br>$T_A = T_{MIN}$ to $T_{MAX}$ |                                                                                     | -32                | -37                |            | dB                |

| f <sub>CLK</sub> /f <sub>C</sub> Tempco                                              | Same as above                                                                                              |                                                                                     |                    | 10                 |            | ppm/°C            |

| Filter Output (Pin 7) DC Swing                                                       | Pin 7 buffered with an ext op amp T <sub>A</sub> = T <sub>MIN</sub> to T <sub>MAX</sub>                    |                                                                                     | ±3.5               | ±3.8               |            | V                 |

| Clock Feedthrough                                                                    |                                                                                                            |                                                                                     |                    | 10                 |            | mV <sub>p-p</sub> |

| INTERNAL BUFFER                                                                      |                                                                                                            |                                                                                     |                    |                    |            | 1 · P · P         |

| Bias Current                                                                         | T <sub>A</sub> = +25°C<br>T <sub>A</sub> = T <sub>MIN</sub> to T <sub>MAX</sub>                            |                                                                                     |                    | 2<br>170           | 50<br>1000 | pA                |

| Offset Voltage                                                                       | MAX281A<br>MAX281B                                                                                         |                                                                                     |                    | 0.2<br>2           | 2<br>20    | mV                |

| Voltage Swing                                                                        | 20kΩ; T <sub>A</sub> = T <sub>MIN</sub> to T <sub>MAX</sub>                                                |                                                                                     | ±3.5               | ±3.8               |            | V                 |

| Short-Circuit Current Source/Sink                                                    |                                                                                                            |                                                                                     |                    | 30/2               |            | mA                |

| CLOCK (NOTE 2)                                                                       |                                                                                                            |                                                                                     |                    |                    |            |                   |

| Internal Oscillator Frequency                                                        | COSC (Pin 5 to<br>V-) = 100pF                                                                              | MAX281A<br>MAX281B                                                                  | 31<br>25           | 35<br>35           | 39<br>50   |                   |

|                                                                                      | $T_A = T_{MIN}$ to $T_{MA}$ ;<br>COSC (Pin 5 to<br>V-) = 100pF                                             | MAX281A<br>MAX281B                                                                  | 29<br>15           | 35<br>35           | 43<br>65   | kHz               |

| Max Clock Frequency                                                                  |                                                                                                            |                                                                                     |                    | 4                  |            | MHz               |

| COSC Input Sink/Source Current T <sub>A</sub> = T <sub>MIN</sub> to T <sub>MAX</sub> |                                                                                                            |                                                                                     | 25                 | 80                 | μΑ         |                   |

Note 1: f<sub>C</sub> is the corner frequency of the filter.

Note 2: The external or driven clock frequency is divided by either 1, 2, or 4 depending upon the voltage at pin 4. When pin 4 = V+, fclk/fc = 101; when pin 4 = GND, fclk/fc = 202 when pin 4 = V-, fclk/fc = 404.

| NAME             | FUNCTION                                                                                                                                                                             |                   |                |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|----------------|

| FB               | External capacitor couples to the chip through this pin.                                                                                                                             |                   |                |

| AGND             | Ground. Connect to system ground for dual-supply operation or mid-supply for single operation. This pin should be well bypassed using a large capacitor for single-supply operation. |                   |                |

| V-               | Negative Supply Voltage                                                                                                                                                              |                   |                |

| DIVIDER<br>RATIO | Strapped to select clock to cutoff ratio (external clock), or internal divider ratio (internal oscillator).                                                                          |                   |                |

| •                | Voltage<br>at pin 4                                                                                                                                                                  | EXT<br>fosc/fc    | INT<br>divisor |

|                  | V+<br>GND<br>V-                                                                                                                                                                      | 101<br>202<br>404 | 1<br>2<br>4    |

| NAME | FUNCTION                                                                                                                            |  |  |

|------|-------------------------------------------------------------------------------------------------------------------------------------|--|--|

| cosc | Clock input pin for external clock applications. For internal clock operation, connect an external capacitor between this pin and V |  |  |

| V+   | Positive Supply Voltage                                                                                                             |  |  |

| OUT  | Input to on-chip buffer amplifier                                                                                                   |  |  |

| BOUT | Output of buffer amplifier                                                                                                          |  |  |

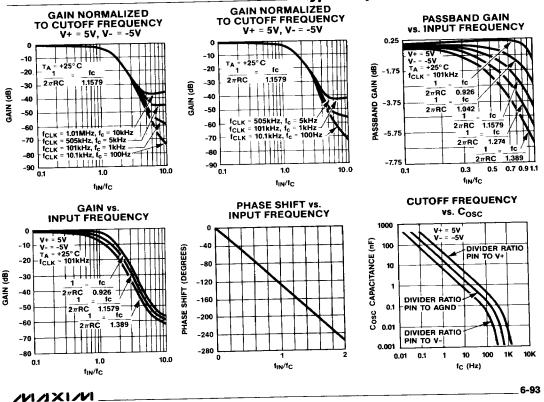

# **Typical Operating Characteristics**

6-94

# 5th-Order, Zero-Error, Bessel Lowpass Filter

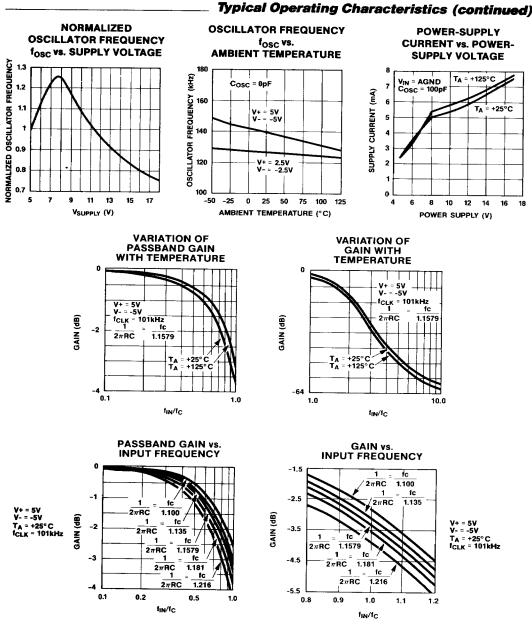

# Typical Operating Characteristics (continued)

NINXIN

#### Introduction

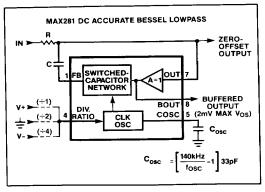

Figure 1 illustrates the architecture of the circuit. The output voltage is sensed through an internal buffer, then applied to an internal switched capacitor network which drives the bottom plate of an external capacitor to form a 5th-order, lowpass filter. The input and output appear across an external resistor, and the IC part of the overall filter handles only the AC path of the signal. The DC offsets of the buffer and the switched-capacitor network are blocked by the capacitor and do not appear at the zero-offset output pin.

Use of this external resistor and capacitor also automatically provides the required anti-aliasing filtering for the sampled filter. Further, low-frequency noise in the filter IC.is attenuated by the external capacitor since any noise at the FB pin goes through a highpass path to the filter output. The filter output pin is unbuffered. This signal can be buffered by the on-chip buffer or by a high-accuracy op amp (such as a chopper stabilized op amp) to obtain a buffered DC accurate system. The on-chip buffer has an offset voltage of 2mV for the MAX281A and 20mV for the MAX281B. The offset voltage for both devices have a typical tempco of 1 \( \pu \mu \mathbb{V}^{\circ} \mathbb{C}.

### **Detailed Description**

#### **Clock Requirements**

The MAX281 operates either on its internal oscillator or an externally supplied clock.

#### Using an Internal Oscillator

The MAX281 contains an internal 140kHz (nominal) oscillator. This frequency can be modified by connecting an external capacitor in parallel with the on-chip 3pF capacitor; from the COSC pin to GND (or to V- if the capacitor is polarized).

When using the internal oscillator, connect the DIVIDER RATIO pin to V+ for 1/1, to GND for a 2/1, and to V- for a 4/1 fosc/fclk ratio.

The oscillator frequency can be calculated by:

$$f_{OSC} = 140kHz (33pF/(33pF+C_{OSC})) (1)$$

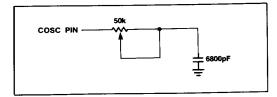

Due to process tolerances,  $f_{\rm OSC}$  can vary by  $\pm 62.5\%$  in the MAX281B. In the MAX281A, on-chip trimming reduces the  $f_{\rm OSC}$  tolerance to  $\pm 19.5\%$ . The oscillator frequency can be adjusted by adding a series potentiometer between the capacitor and the COSC pin (Figure 2). The new frequency can be computed as:

$$f'_{OSC} = f_{OSC}/(1-4RC_{OSC} f_{OSC})$$

(2)

where  $f_{OSC}$  is the value of the oscillator frequency when R = 0. When an external potentiometer is used, the new value of the oscillator frequency is always higher than the one calculated in (equation 1). To achieve a wide tuning range, calculate (equation 1) the ideal fosc,  $C_{OSC}$  pair, then double the value of  $C_{OSC}$  and use a 50k potentiometer to adjust  $f'_{OSC}$ . For example, to obtain a 1kHz oscillator frequency,  $C_{OSC}$  is 3900pF. By using 6800pF for  $C_{OSC}$  and a 50k $\Omega$  potentiometer, the clock

Figure 1. Block Diagram

Figure 2. External Oscillator Trim

frequency can be adjusted from 500Hz to 1.56kHz. The internal oscillation frequency can be measured directly at the COSC pin using a low-capacitance probe.

#### Using an External Clock

Depending upon the connection of the DIVIDER RATIO pin, the internal switched capacitor filter requires a clock 101, 202, or 404 times higher than the desired cutoff frequency. If an external clock is used, the input on the COSC pin must swing close to the power rails (V+,V-). Although standard 74HC00 series CMOS gates do not guarantee CMOS levels with the source and sink currents of the COSC pin, they will in reality drive the COSC pin. CMOS gates conforming to standard B series output drive have the appropriate voltage levels and current to simultaneously drive several chips. The typical trip levels of the internal Schmitt trigger sensing COSC pin are:

| POWER SUPPLY | TRIP LEVEL                                           |  |

|--------------|------------------------------------------------------|--|

| V+ = +2.5V   | $\begin{array}{cccccccccccccccccccccccccccccccccccc$ |  |

/VIXI/VI

6-95

#### Choosing External Resistor and Capacitor Values

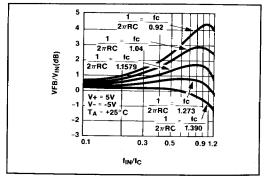

The external resistor and capacitor are used as part of a feedback loop for the filter and also forms one pole. The internal 4-pole switched-capacitor filter is driven by a clock which also determines the filter cutoff frequency. For a proper Bessel response, the clock and DIVIDER RATIO pin should be set to provide the desired cutoff frequency. Additionally, the resistor and capacitor should be chosen such that:

$$\frac{f_C}{1.1579} = \frac{1}{2\pi BC}$$

where f<sub>C</sub> = filter cutoff frequency.

For example to implement a 10Hz cutoff filter, set:

$$1/2\pi RC = 10Hz/1.1579 = 8.6363Hz$$

R is typically  $\approx 20 k \Omega$ . The minimum value of R depends upon the maximum input signal, and the current sinking capability of the FB pin (typically 1mA). So for a  $1V_{p-p}$  signal, the minimum value of the resistor is  $1k\Omega$ .

The passband response for values of  $1/(2\pi RC)$  around  $(f_C/1.1579)$  can be seen on the Passband Gain vs. Input Frequency plots (see Typical Operating Characteristics). For optimum Bessel response, the RC product should be well controlled. Note that an inaccurate RC product can cause excessive peaking at the FB pin (Figure 3), which results in clipping and distortion of the output waveform.

For wide temperature range applications, NPO ceramic capacitors are recommended. Their tempcos are around  $\pm 20$  ppm and values are available to  $0.1\mu$ F. Other ceramic capacitors are not recommended due to their large tempcos. Mylar, polystyrene and polypropylene capacitors all provide acceptable performance. Solid tantalum capacitors connected back-to-back and disc ceramic capacitors introduce additional passband errors (0.05-0.1dB).

## \_ Applications Information

#### Filter Input Voltage Range

Every node of the filter typically swings within 1V of both supplies. With the appropriate external resistor and capacitor values, the amplitude response of all the internal and external nodes should not exceed a gain of OdB with the exception of the FB pin. The amplitude response of the FB pin, where some peaking may occur, is shown in Figure 3.

With ±5V supplies, the peak-to-peak input voltage should not exceed 6.5V. If the input voltage goes beyond this value, clipping and distortion of the output waveform may occur; however, the filter will not be damaged. The absolute maximum input voltage to any pin should not exceed the power supplies.

#### Internal Buffer

The internal output buffer of the FB pin and the OUT pin is part of the AC signal path. Hence, capacitive loading greater than 30pF can cause gain errors in the passband around the cutoff frequency. The internal buffer can also be used as the filter output, however, there will be a few millivolts of output offset.

#### Filter Attenuation

The rolloff is 30dB/octave. When the clock rate is increased and hence the cutoff frequency is increased, the filter's maximum attenuation decreases as shown in the Typical Operating Characteristics. This decrease is caused by rolloff at higher frequencies of the loop gains of the various internal feedback paths and is not due to any increase in noise floor.

Figure 3. Amplitude Response of FB Pin

#### Filter Noise

The filter wideband noise is typically  $90\mu V_{RMS}$  with  $\pm 5V$  supplies and typically  $80\mu V_{RMS}$  for  $\pm 2.5V$  supplies or a +5V single supply. This value is nearly independent of the cutoff frequency. The noise spectral density, unlike conventional active filters, is nearly zero for frequencies below  $0.1f_C$ . Roughly 2/3 of the entire wideband noise is in the band DC to  $f_C$ .

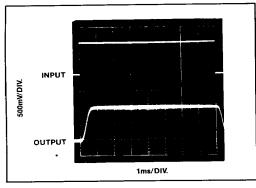

#### Transient Response

Figure 4 shows the step response of the filter where  $f_{\rm C}=1$  kHz. This response approximates an ideal 5th-order Bessel filter. The absence of overshoot is characteristic of the Bessel response.

#### Anti-Aliasing

The internal 4th-order switched-capacitor filter is a sampled device, and as such will alias unless preceded by a band limited signal or a continuous non-sampled filter. The external resistor and capacitor used to form the 5th filter pole also automatically provides this function. Attenuation is greater than 35dB at the Nyquist frequency.

Figure 4. Step Response of MAX281 for f<sub>C</sub> = 1kHz

#### Single-Supply Operation

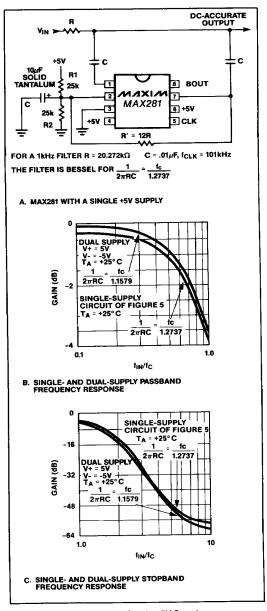

Figure 5A shows a schematic for single-supply operation. The AGND pin and the OUT pin should be biased at 1/2 supply. The value of the resistors, R1 and R2, should be chosen to conduct  $100\mu\text{A}$  or more. R' DC biases the buffer and C' isolates the buffer from the DC value of the output. Under these conditions, the external resistor and capacitor should be adjusted such that  $(1/2\pi\text{RC})=1.2737$ . This accounts for the extra loading of the R',C' combination. R' and C' are not required if the input voltage has a DC value around 1/2 supply. If an external capacitor is used to activate the internal oscillator, its bottom plate should be tied to system ground. The AGND pin should also be bypassed by a decoupling capacitor.

Figures 5B and 5C illustrate the passband and stopband frequency response for both single- and dual-supply operation.

#### Clock Feedthrough

Clock feedthrough can be reduced by using a resistor and capacitor at the buffered output pin provided that this pin is used as an output. An active filter at the DC accurate output can act as a buffer and provide clock feedthrough filtering.

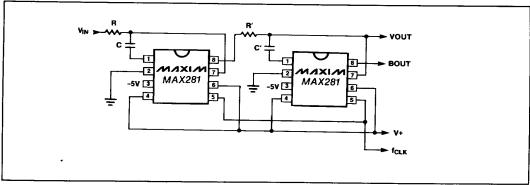

#### Cascading for Higher Order Filters

Two chips can be cascaded with or without intermediate buffers. Figure 6 shows a buffered arrangement which corrects for loading of the output when the first stage is used to drive the input of the next stage. This introduces a maximum DC error of 2mV over temperature at VOUT.

Figure 5. Operation from a Single +5V Supply

MIXIM.

6-97

Figure 6. Cascading Two MAX281 filters. The 2nd Stage is Driven by the Buffered Output of the First Stage

### **Application Circuits**

## DC OUTPUT 0.01µF, 0.014F. HIGH DC MAX281 INPUT = 100V = 220k = 101kHz fc = 1kHz INPUT 20V 200µs 100V DC + 5V<sub>р-р</sub> @ 10kHz OUTPUT 20V

Figure 7. Filtering AC Signals from High DC Voltages

### Filtering High DC Voltages

In Figure 7, a MAX281 removes undesired AC components from a DC voltage much higher than the operating voltage of the filter IC. This is possible due to the shunt architecture of these filters and is not generally possible with conventional active filter structures.

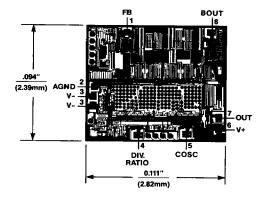

#### \_ Chip Topography

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.