Issue Date: January 7, 2010

# ML610Q340/ML610340

8-bit Microcontroller with Voice Output Function

#### **GENERAL DESCRIPTION**

Equipped with an LAPIS Semiconductor original 8-bit CPU nX-U8/100, the ML610Q340/ML610340 is a high-performance 8-bit CMOS microcontroller that integrates a wide variety of peripherals such as a timer, synchronous serial port, and voice output function. The nX-U8/100 CPU is capable of executing instructions efficiently on a one-instruction-per-clock-pulse basis through parallel processing by the 3-stage pipelined architecture. The microcontroller is also equipped with a flash memory that has achieved low voltage and low power consumption (at read) equivalent to mask ROMs, so it is best suited to battery-driven applications such as cellular phones. In addition, it has an on-chip debugging function, which allows software debugging/rewriting with the LSI mounted on the board.

#### **FEATURES**

#### • CPU

- 8-bit RISC CPU (CPU name: nX-U8/100)

- Instruction repertoire: 16-bit length instructions

- Instruction set: Transfer, arithmetic operations, comparison, logical operations, multiply/divide operations, bit manipulation, bit logical operations, jump, conditional jump, call return stack manipulation, and arithmetic shift instructions.

- Built-in on-chip debugging function

- Minimum instruction execution time:

0.244 μs (@ 4.096 MHz system clock)

#### Internal memory

- ML610O340

- Has 96-Kbyte flash memory (48K × 16-bit) built in. (including unusable 1KByte TEST area)

- ML610340

- Has 96-Kbyte mask memory (48K × 16-bit) built in. (including unusable 1KByte TEST area)

- Has 512-byte RAM (512  $\times$  8-bit) built in.

### • Interrupt controller

- Non-maskable interrupt: 2 sources (1 internal source and 1 external sources)

- Maskable interrupt: 12 sources (8 internal sources and 4 external sources)

### • Time-base counter

- Low-speed side time-base counter × 1ch

- High-speed side time-base counter × 1ch

#### • Watchdog timer

- Generates a non-maskable interrupt upon the first overflow and a system reset occurs upon the second

- Free-running

- Selectable overflow period: 4 types (125 ms, 500 ms, 2 sec, 8 sec)

#### • Timer

- 8-bit × 2ch (16-bit configuration also enabled)

#### Voice output function

- Voice synthesis method: 4-bit ADPCM2 / 8-bit non-linear PCM / 8-bit PCM / 16-bit PCM

- Sampling frequency: 6.4/8/10.7/12.8/16/21.3/25.6/32 kHz

#### • Speaker amplifier output power

-1 W(at 5 $\dot{V}$ )

#### • Synchronous serial port

- Master/slave selectable

- LSB/MSB-first selectable

- 8-bit/16-bit length selectable

#### • General-purpose port

- Input-only port  $\times$  4ch

- Output-only port × 4ch (those as secondary functions are also included)

- Input-output port × 4ch (those as secondary functions are also included)

#### • Reset

- Resetting by the RESET\_N pin

- Resetting upon power-on detection

- Resetting upon WDT overflow detection

#### • Clock

Low-speed side clock

Internal frequency division (1/128 of the high-speed side clock)

High-speed side clock

Crystal/ceramic oscillation (4.096 MHz), external clock

#### • Power management

- HALT mode: Halts the execution of instructions issued by the CPU (the peripheral circuits continue operating)

- STOP mode: Stops low-speed and high-speed oscillation (the CPU and the peripheral circuits stop operating)

- Clock gear: Allows changing the frequency of the high-speed system clock by software (oscillator clock divided by 1, 2, 4, or 8)

- Block Control Function: Power down (reset registers and stop clock supply) the circuits of unused peripherals.

### • Shipment

- 30-pin SSOP

- High-speed side clock : Crystal/ceramic oscillation (4.096 MHz)

Flash Memory : ML610Q340-xxxMB (blank product: ML610Q340-NNNMB)

Mask Memory : ML610340-xxxMB

- High-speed side clock : external clock

Flash Memory : ML610Q340J-xxxMB (blank product: ML610Q340J-NNNMB)

Mask Memory : ML610340J-xxxMB

xxx: ROM code number

#### • Guaranteed operating range

Operating temperature: −40°C to +85°C

- Operating voltage:  $V_{DD} = 2.2$  to 5.5 V,  $SPV_{DD} = 2.3$  to 5.5 V (Be sure to apply the same voltage to all the power supplies.)

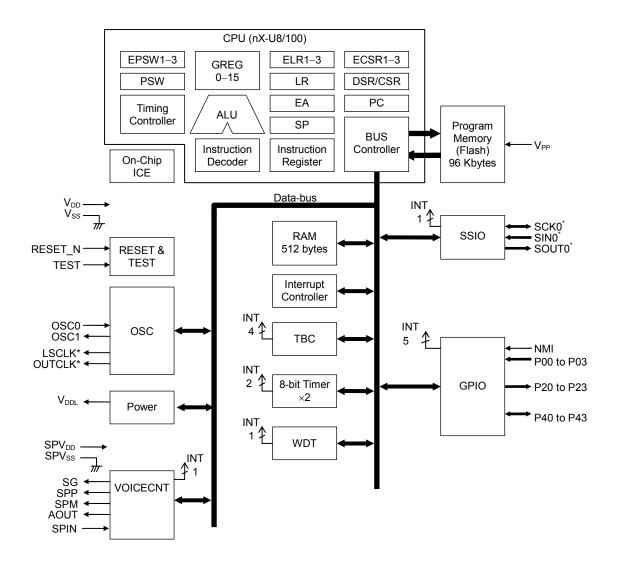

### **BLOCK DIAGRAM**

### ML610Q340

Figure 1 is a block diagram of the ML610Q340.

Symbols with an asterisk "\*" indicate that each of them is the secondary or tertiary function of the corresponding port.

Figure 1 Block Diagram of ML610Q340

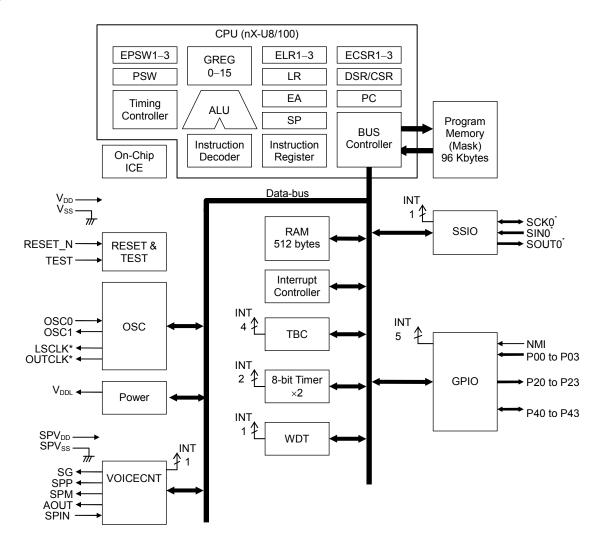

### ML610340

Figure 2 is a block diagram of the ML610340.

Symbols with an asterisk "\*" indicate that each of them is the secondary or tertiary function of the corresponding port.

Figure 2 Block Diagram of ML610340

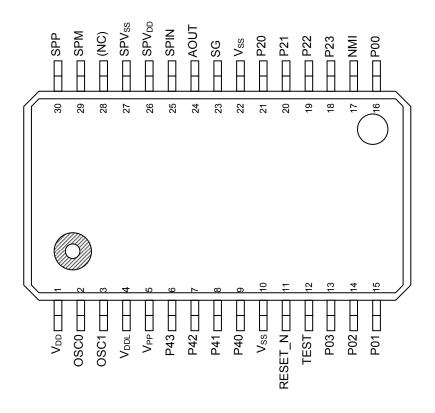

# PIN CONFIGURATION

# ML610Q340 SSOP package product

NC: No Connection

Figure 3 Pin Configuration of ML610Q340 Package Product

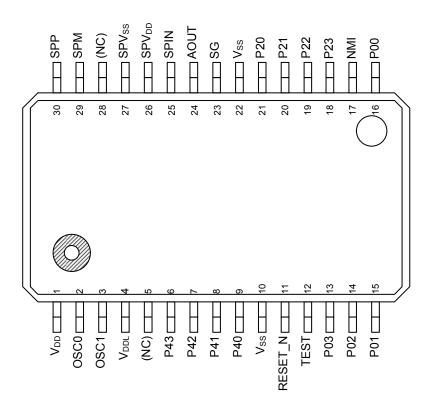

# ML610340 SSOP package product

NC: No Connection

Figure 4 Pin Configuration of ML610340 Package Product

# LIST OF PINS

| PAD   |                     | Prima | ary function                                                          | Sec      | condary | function                   | Te       | rtiary fu | unction     |

|-------|---------------------|-------|-----------------------------------------------------------------------|----------|---------|----------------------------|----------|-----------|-------------|

| No    | Pin name            | I/O   | Description                                                           | Pin name | I/O     | Description                | Pin name | I/O       | Description |

| 10,22 | Vss                 |       | Negative power supply pin                                             | _        | _       | _                          |          |           |             |

| 1     | $V_{DD}$            | _     | Positive power supply pin                                             | _        | _       | _                          |          |           |             |

| 4     | $V_{DDL}$           | _     | Power supply for internal logic (internally generated)                | _        | _       | _                          | _        | _         | _           |

| 27    | SPV <sub>ss</sub>   | —     | Negative power supply pin for built-in speaker amplifier              | _        | _       | _                          | _        |           |             |

| 26    | SPV <sub>DD</sub>   | _     | Positive power supply<br>pin for built-in speaker<br>amplifier        | _        | _       | _                          | _        |           | _           |

| 5     | V <sub>PP</sub> (*) | _     | Power supply pin for flash memory                                     | _        | _       | _                          | _        | _         | _           |

| 12    | TEST                | I/O   | Input/output pin for testing                                          | _        | _       | _                          | _        | _         | _           |

| 11    | RESET_N             | I     | Reset input pin                                                       | _        | _       | _                          | _        | _         | _           |

| 2     | OSC0                | I     | Connection pin for high-speed clock oscillation                       | _        | —       | _                          | _        | _         | _           |

| 3     | OSC1                | 0     | Connection pin for high-speed clock oscillation                       | P11      | 1       | Input port                 | _        |           | _           |

| 24    | AOUT                | 0     | LINE output                                                           | _        | _       | _                          |          | _         | _           |

| 25    | SPIN                | I     | Analog input to the built-in speaker amplifier                        | _        |         | _                          |          |           | 1           |

| 23    | SG                  | 0     | Reference power<br>supply pin of the<br>built-in speaker<br>amplifier |          |         | _                          | _        |           | _           |

| 30    | SPP                 | 0     | Positive output pin of the built-in speaker amplifier                 | _        | _       | _                          | _        |           | _           |

| 29    | SPM                 | 0     | Negative output pin of the built-in speaker amplifier                 | _        | _       | _                          | _        |           | _           |

| 17    | NMI                 | I     | Input port,<br>non-maskable<br>interrupt                              | _        | _       | _                          | _        |           | _           |

| 16    | P00/EXI0            | I     | Input port / External interrupt                                       | _        | _       | _                          | _        | _         |             |

| 15    | P01/EXI1            | I     | Input port / External interrupt                                       | _        | _       | _                          | _        |           | _           |

| 14    | P02/EXI2            | I     | Input port / External interrupt                                       | _        |         |                            | _        |           |             |

| 13    | P03/EXI3            | I     | Input port / External interrupt                                       |          | _       |                            | _        |           |             |

| 21    | P20/LED0            | 0     | Output port / LED drive                                               | LSCLK    | 0       | Low-speed clock output     | _        | _         | _           |

| 20    | P21/LED1            | 0     | Output port / LED drive                                               | OUTCLK   | 0       | high-speed<br>clock output | _        |           | _           |

| 19    | P22/LED2            | 0     | Output port / LED drive                                               | _        | _       | _                          | _        |           | _           |

| 18    | P23/LED3            | 0     | Output port / LED drive                                               | _        |         | _                          | _        |           |             |

| PAD | Primary function |     |                   | Secondary function |     |             | Tertiary function |     |                                               |

|-----|------------------|-----|-------------------|--------------------|-----|-------------|-------------------|-----|-----------------------------------------------|

| No  | Pin name         | I/O | Description       | Pin name           | I/O | Description | Pin name          | I/O | Description                                   |

| 9   | P40              | I/O | Input/output port | _                  | _   | _           | SIN0              | 1   | SSIO0 data input                              |

| 8   | P41              | I/O | Input/output port | _                  | _   | _           | SCK0              | I/O | SSIO0<br>synchronous<br>clock<br>input/output |

| 7   | P42              | I/O | Input/output port | _                  |     | _           | SOUT0             | 0   | SSIO0 data output                             |

| 6   | P43              | I/O | Input/output port | _                  | _   | _           |                   | _   | _                                             |

<sup>\*:</sup> Applies to the ML610Q340.

# PIN DESCRIPTION

| Pin name            | I/O     | Description                                                                                                                                                                                                                                                | Primary/<br>Secondary/<br>Tertiary | Logic    |

|---------------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|----------|

| Power supply        |         |                                                                                                                                                                                                                                                            |                                    |          |

| V <sub>SS</sub>     | _       | Negative power supply pin                                                                                                                                                                                                                                  | _                                  | _        |

| $V_{DD}$            | _       | Positive power supply pin                                                                                                                                                                                                                                  | _                                  |          |

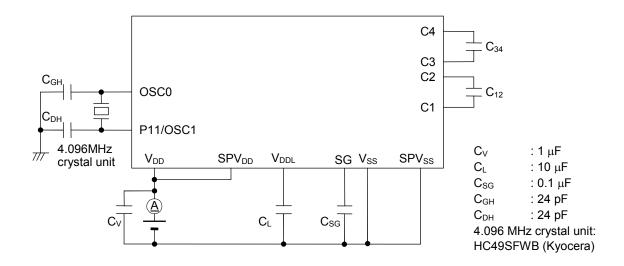

| V <sub>DDL</sub>    | _       | Positive power supply pin for internal logic (internally generated) Capacitors $C_L$ (see measuring circuit 1) are connected between this pin and $V_{SS}$                                                                                                 | _                                  | _        |

| SPV <sub>SS</sub>   | _       | Negative power supply pin for built-in speaker amplifier                                                                                                                                                                                                   | _                                  | _        |

| SPV <sub>DD</sub>   | _       | Positive power supply pin for built-in speaker amplifier                                                                                                                                                                                                   | _                                  | _        |

| V <sub>PP</sub> (*) |         | Power supply pin for flash memory                                                                                                                                                                                                                          | _                                  |          |

| Test                |         |                                                                                                                                                                                                                                                            |                                    |          |

| TEST                | I/O     | Input/output pin for testing. Has a pull-down resistor built in.                                                                                                                                                                                           | _                                  | Positive |

| System              | •       |                                                                                                                                                                                                                                                            |                                    |          |

| RESET_N             | I       | Reset input pin. When this pin is set to a "L" level, the device is placed in system reset mode and the internal circuit is initialized. If after that this pin is set to a "H" level, program execution starts. This pin has a pull-up resistor built in. |                                    | Negative |

| OSC0                | ı       | Pins for connecting a crystal unit for high speed clock.                                                                                                                                                                                                   | _                                  |          |

| OSC1                | 0       | Connect a 4.096 MHz crystal unit (see Measuring Circuit 1) to these pins. Also, connect capacitors ( $C_{DH}$ and $C_{GH}$ ) between these pins and $V_{SS}$ as required.                                                                                  | _                                  | 1        |

| LSCLK               | 0       | Low-speed clock output. This function is allocated to the secondary function of the P20 pin.                                                                                                                                                               | Secondary                          | _        |

| OUTCLK              | 0       | High-speed clock output. This function is allocated to the secondary function of the P21 pin.                                                                                                                                                              | Secondary                          |          |

| General-purpos      | e Input | port                                                                                                                                                                                                                                                       |                                    |          |

| P00-P03             | I       | General-purpose input ports.                                                                                                                                                                                                                               | Primary                            | Positive |

| General-purpos      | se Outp |                                                                                                                                                                                                                                                            |                                    |          |

| P20-P23             | 0       | General-purpose output ports.  Provided with a secondary function. Cannot be used as ports if their secondary function is used.                                                                                                                            | Primary                            | Positive |

| General-purpos      |         |                                                                                                                                                                                                                                                            |                                    |          |

| P40-P43             | I/O     | General-purpose input/output ports.  Provided with a secondary function. Cannot be used as ports if their secondary function is used.                                                                                                                      | Primary                            | Positive |

<sup>\*</sup>Applies to the ML610Q340.

| Pin name          | I/O     | Description                                                                                                                                                                                                         | Primary/<br>Secondary/<br>Tertiary | Logic                 |

|-------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|-----------------------|

| Synchronous se    | rial (S | SIO)                                                                                                                                                                                                                |                                    |                       |

| SIN0              | I       | Synchronous serial data input pin. Allocated to the tertiary function of the P40 pin.                                                                                                                               | Tertiary                           | Positive              |

| SCK0              | I/O     | Synchronous serial clock input/output pin. Allocated to the tertiary function of the P41 pin.                                                                                                                       | Tertiary                           | _                     |

| SOUT0             | 0       | Synchronous serial data output pin. Allocated to the tertiary function of the P42 pin.                                                                                                                              | Tertiary                           | Positive              |

| External interrup | t       |                                                                                                                                                                                                                     |                                    |                       |

| NMI               | I       | External non-maskable interrupt input pin. The interrupt occurs on both the rising and falling edges.                                                                                                               | Primary                            | Positive/<br>Negative |

| EXI0-3            | I       | External maskable interrupt input pins. It is possible, for each bit, to specify whether the interrupt is enabled and select the interrupt edge by software. Allocated to the primary function of the P00–P03 pins. | Primary                            | Positive/<br>Negative |

| LED drive         |         |                                                                                                                                                                                                                     |                                    |                       |

| LED0-3            | 0       | NMOS open drain pins to allow direct driving of LED. Allocated to the secondary function of the P20–P23 pins.                                                                                                       | Primary                            | Positive/<br>Negative |

| Voice output fun  | ction   |                                                                                                                                                                                                                     |                                    |                       |

| AOUT              | 0       | LINE output pin. When you use built-in speaker amplifier, connect with the SPIN pin.                                                                                                                                | _                                  | _                     |

| SPIN              | I       | Analog input pin of the internal speaker amplifier.                                                                                                                                                                 | _                                  | _                     |

| SG                | 0       | Reference voltage output pin of the internal speaker amplifier.                                                                                                                                                     | _                                  | _                     |

| SPP               | 0       | Positive output pin of the internal speaker amplifier.                                                                                                                                                              | _                                  | _                     |

| SPM               | 0       | Negative output pin of the internal speaker amplifier.                                                                                                                                                              | _                                  | _                     |

### TERMINATION OF UNUSED PINS

### **How to Terminate Unused Pins**

| Pin               | Recommended pin termination        |

|-------------------|------------------------------------|

| $V_{PP}$          | Open                               |

| RESET_N           | Open                               |

| TEST              | Open                               |

| SPV <sub>DD</sub> | V <sub>SS</sub>                    |

| SPV <sub>SS</sub> | V <sub>SS</sub>                    |

| AOUT              | Open                               |

| SPIN              | Open                               |

| SG                | Open                               |

| SPP               | Open                               |

| SPM               | Open                               |

| P00-P03           | V <sub>DD</sub> or V <sub>SS</sub> |

| P20-P23           | Open                               |

| P40-P43           | Open                               |

#### Note:

It is recommended to configure the unused input ports and input/output ports as inputs with pull-down resistors/pull-up resistors or outputs since the supply current may become excessively large if those pins are left open in the high impedance input setting.

# **ELECTRICAL CHARACTERISTICS**

# **Absolute Maximum Ratings**

$(V_{SS} = SPV_{SS} = 0V)$

| Parameter              | Symbol            | Condition     | Rating                       | Unit |

|------------------------|-------------------|---------------|------------------------------|------|

| Power supply voltage 1 | $V_{DD}$          | Ta = 25°C     | −0.3 to +7.0                 | V    |

| Power supply voltage 2 | SPV <sub>DD</sub> | Ta = 25°C     | -0.3 to +7.0                 | V    |

| Power supply voltage 3 | $V_{DDL}$         | Ta = 25°C     | -0.3 to +3.6                 | V    |

| Power supply voltage 4 | V <sub>PP</sub>   | Ta = 25°C     | -0.3 to +9.5                 | V    |

| Input voltage          | V <sub>IN</sub>   | Ta = 25°C     | -0.3 to V <sub>DD</sub> +0.3 | V    |

| Output voltage         | V <sub>OUT</sub>  | Ta = 25°C     | $-0.3$ to $V_{DD}$ +0.3      | V    |

| Output current 1       | I <sub>OUT1</sub> | P4, Ta = 25°C | –12 to +11                   | mA   |

| Output current 2       | I <sub>OUT2</sub> | P2, Ta = 25°C | -12 to +20                   | mA   |

| Power dissipation      | PD                | Ta = 25°C     | 861                          | mW   |

| Storage temperature    | T <sub>STG</sub>  | ı             | −55 to +150                  | °C   |

# **Recommended Operating Conditions**

$(V_{SS} = SPV_{SS} = 0V)$

|                                                        |                   |           | ,            | ,    |

|--------------------------------------------------------|-------------------|-----------|--------------|------|

| Parameter                                              | Symbol            | Condition | Range        | Unit |

| Operating temperature                                  | T <sub>OP</sub>   | _         | -40 to +85   | °C   |

| Operating voltage                                      | $V_{DD}$          | _         | 2.2 to 5.5   | V    |

| Operating voltage                                      | SPV <sub>DD</sub> | _         | 2.3 to 5.5   | V    |

| Operating frequency (CPU)                              | f <sub>OP</sub>   | _         | 437k to 4.2M | Hz   |

| High-speed crystal/ceramic oscillation frequency       | f <sub>XTH</sub>  | _         | 4.0M, 4.096M | Hz   |

| High-speed crystal oscillation                         | С <sub>DH</sub>   | _         | 15 to 32     |      |

| external capacitor                                     | С <sub>GH</sub>   | _         | 15 to 32     | pF   |

| Capacitor externally connected to V <sub>DDL</sub> pin | CL                | _         | 10±30%       | μF   |

| Capacitor externally connected to SG pin               | C <sub>SG</sub>   | _         | 0.1±30%      | μF   |

### **Flash Memory Operating Conditions**

$(V_{SS} = SPV_{SS} = 0V)$

| Parameter             | Symbol          | Symbol Condition    |             | Unit  |

|-----------------------|-----------------|---------------------|-------------|-------|

| Operating temperature | T <sub>OP</sub> | At write/erase      | 0 to +40    | °C    |

|                       | $V_{DD}$        | At write/erase      | 2.7 to 3.6  |       |

| Operating voltage     | $V_{DDL}$       | At write/erase (*1) | 2.5 to 2.75 | V     |

|                       | $V_{PP}$        | At write/erase (*1) | 7.7 to 8.3  |       |

| Maximum rewrite count | C <sub>EP</sub> | _                   | 80          | times |

| Data retention period | $Y_{DR}$        | _                   | 10          | years |

<sup>\*1:</sup> When writing data to, or erasing data from, flash ROM, it is necessary to apply a voltage within the range specified above to the V<sub>DDL</sub> pin.

# DC Characteristics (1 of 5)

$(V_{DD} = SPV_{DD} = 2.2 \text{ to } 5.5V, V_{SS} = SPV_{SS} = 0V,$ Ta = -40 to +85°C, unless otherwise specified)

| Parameter                            | Symbol            | Condition | Min. | Тур. | Max. | Unit | Measuring circuit |

|--------------------------------------|-------------------|-----------|------|------|------|------|-------------------|

| High-speed oscillation start time    | T <sub>XTH</sub>  | _         | _    | 2    | 20   | ms   |                   |

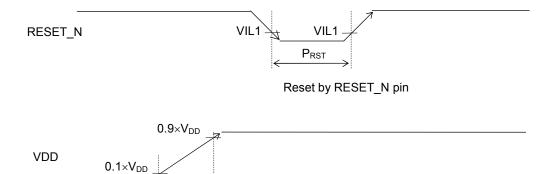

| Reset pulse width                    | P <sub>RST</sub>  | _         | 100  | _    | _    |      |                   |

| Reset noise rejection pulse width    | P <sub>NRST</sub> | _         | _    | _    | 0.4  | μS   | 1                 |

| Time from power-on reset to power-up | T <sub>POR</sub>  | _         | _    | _    | 10   | ms   |                   |

#### Reset

$\mathsf{T}_{\mathsf{POR}}$

Power-on reset

# DC Characteristics (2 of 5)

$(V_{DD} = SPV_{DD} = 2.3 \text{ to } 5.5V, V_{SS} = SPV_{SS} = 0V,$ Ta = -40 to +85°C, unless otherwise specified)

|                                                                  |                 |                                                                                   | ıa –                      | <del>-+0 10 100</del> | O, unicoo              | Othici Wist | specified)        |

|------------------------------------------------------------------|-----------------|-----------------------------------------------------------------------------------|---------------------------|-----------------------|------------------------|-------------|-------------------|

| Parameter                                                        | Symbol          | Condition                                                                         | Min.                      | Тур.                  | Max.                   | Unit        | Measuring circuit |

| LINE amplifier output load resistance                            | R <sub>LA</sub> | At 1/2V <sub>DD</sub> output                                                      | 10                        | _                     |                        | kΩ          |                   |

| LINE amplifier output voltage range                              | V <sub>AD</sub> | At output load                                                                    | V <sub>DD</sub> ×1/6      | _                     | V <sub>DD</sub> ×5/6   | V           |                   |

| SG output voltage                                                | V <sub>SG</sub> | _                                                                                 | 0.95 × V <sub>DD</sub> /2 | DV <sub>DD</sub> /2   | $1.05 \times V_{DD}/2$ | V           |                   |

| SG output resistance                                             | Rsg             | _                                                                                 | 57                        | 96                    | 135                    | kΩ          |                   |

| SPM, SPP output load resistance                                  | RLSP            | _                                                                                 | 8                         | _                     | _                      | Ω           |                   |

| Speaker amplifier output                                         | PSPO1           | $SPV_{DD} = 3.3V,$ $f = 1kHz,$ $RSPO = 8\Omega,$ $THD \ge 10\%$ $At SPIN Input$   | _                         | 0.5                   | _                      | W           | 1                 |

| power                                                            | PSPO2           | $SPV_{DD} = 5.0V,$ $f = 1kHz,$ $RSPO = 8\Omega,$ $THD \ge 10\%$ $At SPIN Input$   | _                         | 1                     |                        | W           |                   |

| Output offset voltage between SPM and SPP with no signal present | VOF             | SPV <sub>DD</sub> =3.0V,<br>SPIN – SPM gain<br>= +6dB<br>With a load of $8\Omega$ | -50                       | _                     | +50                    | mV          |                   |

# DC Characteristics (3 of 5) ML610Q340

$(V_{DD} = SPV_{DD} = 2.2 \text{ to } 5.5V, V_{SS} = SPV_{SS} = 0V,$ Ta = -40 to +85°C, unless otherwise specified)

| Parameter        | Symbol | Condition                                 |                            | Min. | Тур. | Max. | Unit | Measuring circuit |

|------------------|--------|-------------------------------------------|----------------------------|------|------|------|------|-------------------|

|                  |        | CPU: In STOP state.                       | Ta ≤ +40°C                 | _    | 0.5  | 2.0  |      |                   |

| Supply current 1 | IDD1   | Low-speed/high-speed oscillation: stopped | Ta ≤ +85°C                 | _    | 0.5  | 8    | μА   |                   |

| Supply current 4 | IDD4   | CPU: Running at 4.096MHz                  | $V_{DD} = SPV_{DD} = 3.0V$ | _    | 1.7  | 4    |      |                   |

|                  |        | Crystal/ceramic oscillating mode *1       | $V_{DD} = SPV_{DD} = 5.0V$ | _    | 2.2  | 4    |      | 1                 |

|                  |        | CPU: Running at 4.096MHz                  | $V_{DD} = SPV_{DD} = 3.0V$ | _    | 3    | 12   | mA   |                   |

| Supply current 5 | IDD5   | Crystal/ceramic                           |                            | _    | 8    | 12   |      |                   |

<sup>\*1:</sup> Use 4.096MHz Crystal Oscillator CHC49SFWB (Kyocera).

# DC Characteristics ML610340

$(V_{DD} = SPV_{DD} = 2.2 \text{ to } 5.5V, V_{SS} = SPV_{SS} = 0V,$ Ta = -40 to +85°C, unless otherwise specified)

| Parameter              | Symbol                                                                           | Condition                                                             |                                            | Min. | Тур. | Max. | Unit | Measuring circuit |

|------------------------|----------------------------------------------------------------------------------|-----------------------------------------------------------------------|--------------------------------------------|------|------|------|------|-------------------|

| Supply current 1       |                                                                                  | CPU: In STOP state.                                                   | Ta ≤ +40°C                                 |      | 0.5  | 2.0  |      |                   |

|                        | IDD1                                                                             | Low-speed/high-speed oscillation: stopped                             | Ta ≤ +85°C                                 | l    | 0.5  | 8    | μΑ   |                   |

| Owner by a surround of | IDD4                                                                             | CPU: Running at<br>4.096MHz<br>Crystal/ceramic<br>oscillating mode *1 | $V_{DD} = SPV_{DD} = 3.0V$                 | -    | 0.75 | 4    |      |                   |

| Supply current 4       |                                                                                  |                                                                       | $V_{DD} = SPV_{DD} = 5.0V$                 | _    | 1.5  | 4    | 4    | 1                 |

| Supply current 5       |                                                                                  | CPU: Running at<br>4.096MHz                                           | $V_{DD} = SPV_{DD} = 3.0V$                 | _    | 3    | 12   | mA   |                   |

|                        | IDD5  Crystal/ceramic oscillating mode *1 During voice playback (no output load) |                                                                       | V <sub>DD</sub> = SPV <sub>DD</sub> = 5.0V | _    | 8    | 12   |      |                   |

<sup>\*1:</sup> Use 4.096MHz Crystal Oscillator CHC49SFWB (Kyocera).

# DC Characteristics (4 of 5)

$(V_{DD} = SPV_{DD} = 2.2 \text{ to } 5.5V, V_{SS} = SPV_{SS} = 0V,$ Ta = -40 to +85°C, unless otherwise specified)

| Parameter                         | Symbol | Cor                                              | Min.                            | Тур.                    | Max. | Unit | Measuring circuit |   |

|-----------------------------------|--------|--------------------------------------------------|---------------------------------|-------------------------|------|------|-------------------|---|

| Output voltage 1 (P20–P23)        | VOH1   | IOH1 = -0.5mA                                    |                                 | V <sub>DD</sub><br>-0.5 | 1    | _    |                   |   |

| (P40–P43)                         | VOL1   | IOL1 = +0.5mA                                    |                                 | _                       | _    | 0.5  |                   |   |

| Output voltage 2                  | VOL2   | When LED drive                                   | $IOL2 = +5mA$ $V_{DD} \ge 2.2V$ | I                       | I    | 0.5  | V                 | 2 |

| (P20–P23)                         | VOLZ   | mode is selected                                 | $IOL2 = +8mA$ $V_{DD} \ge 2.3V$ | -                       | ı    | 0.5  |                   |   |

| Output leakage                    | ЮОН    | VOH = V <sub>DD</sub> (in high-impedance state)  |                                 |                         | _    | 1    |                   |   |

| current<br>(P20–P23)<br>(P40–P43) | IOOL   | VOL = V <sub>SS</sub> (in high-impedance state)  |                                 | -1                      | _    | _    | μΑ                | 3 |

| Input current 1                   | IIH1   | VIH1 = V <sub>DD</sub>                           |                                 | 0                       | l    | -1   |                   |   |

| (RESET_N)                         | IIL1   | VIL1 = V <sub>SS</sub>                           |                                 | -1500                   | -300 | -20  |                   |   |

| Input current 2                   | IIH2   | VIH2 = V <sub>DD</sub> (when pulled down)        |                                 | 2                       | 30   | 250  |                   |   |

| (NMI)<br>(P00–P03)<br>(P40–P43)   | IIL2   | VIL2 = V <sub>SS</sub> (v                        | -250                            | -30                     | -2   | μΑ   | 4                 |   |

|                                   | IIH2Z  | VIH2 = V <sub>DD</sub> (in high-impedance state) |                                 | _                       | _    |      |                   | 1 |

|                                   | IIL2Z  | VIL2 = V <sub>SS</sub> (in high-impedance state) |                                 | -1                      | _    |      |                   | _ |

| Input current 3                   | IIH3   | VIH3 = V <sub>DD</sub>                           |                                 | 20                      | 300  | 1500 |                   |   |

| (TEST)                            | IIL3   | VIL3                                             | -1                              | _                       | _    |      |                   |   |

# DC Characteristics (5 of 5)

$(V_{DD} = SPV_{DD} = 2.2 \text{ to } 5.5V, V_{SS} = SPV_{SS} = 0V,$ Ta = -40 to +85°C, unless otherwise specified)

| Parameter                                                         | Symbol | Condition                                         | Min.                     | Тур. | Max.                    | Unit | Measuring circuit |

|-------------------------------------------------------------------|--------|---------------------------------------------------|--------------------------|------|-------------------------|------|-------------------|

| Input voltage 1 (RESET_N)                                         | VIH1   | _                                                 | 0.7×<br>V <sub>DD</sub>  | _    | $V_{DD}$                |      |                   |

| (TEST)<br>(NMI)<br>(P00–P03)<br>(P11)<br>(P40–P43)                | VIL1   | _                                                 | 0                        | _    | 0.3×<br>V <sub>DD</sub> | V    | 5                 |

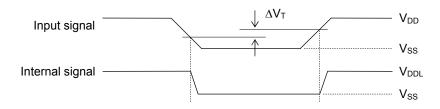

| Hysteresis width (RESET_N) (TEST) (NMI) (P00-P03) (P11) (P40-P43) | ΔVΤ    |                                                   | 0.05×<br>V <sub>DD</sub> | _    | 0.4×<br>V <sub>DD</sub> |      |                   |

| Input pin capacitance<br>(NMI)<br>(P00–P03)<br>(P11)<br>(P40–P43) | CIN    | f = 10kHz<br>V <sub>rms</sub> = 50mV<br>Ta = 25°C | _                        | _    | 10                      | pF   | _                 |

# **Hysteresis Width**

# **Measuring Circuits**

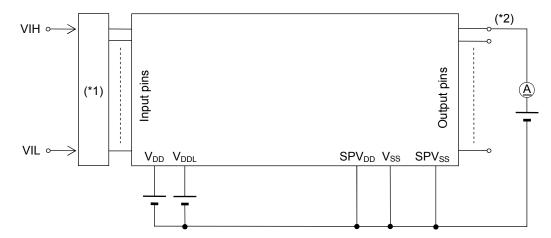

### Measuring circuit 1

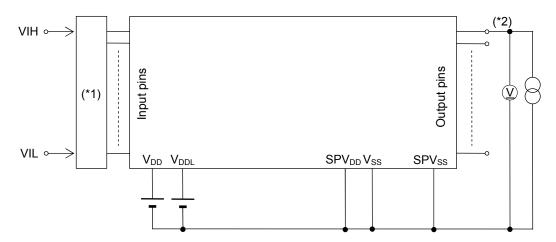

# Measuring circuit 2

- \*1: Input logic circuit to determine the specified measuring conditions.

- \*2: Measured at the specified output pins.

# Measuring circuit 3

- \*1: Input logic circuit to determine the specified measuring conditions.

- \*2: Measured at the specified output pins.

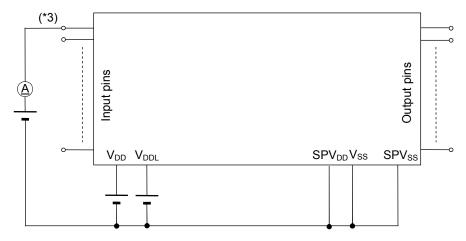

# Measuring circuit 4

\*3: Measured at the specified input pins.

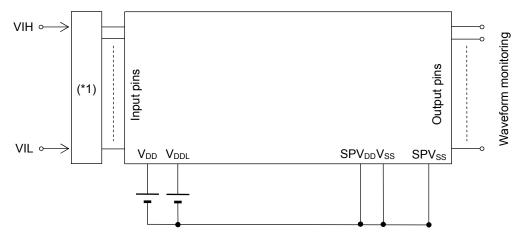

# Measuring circuit 5

\*1: Input logic circuit to determine the specified measuring conditions.

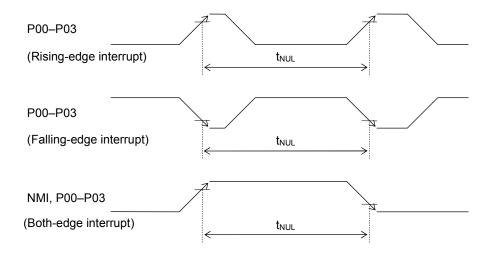

# **AC Characteristics (External Interrupt)**

( $V_{DD}$  = SPV<sub>DD</sub> = 2.2 to 5.5V,  $V_{SS}$  = SPV<sub>SS</sub> = 0V, Ta = -40 to +85°C, unless otherwise specified)

| Parameter                         | Symbol           | Condition                                           | Min.           | Тур. | Max.           | Unit |

|-----------------------------------|------------------|-----------------------------------------------------|----------------|------|----------------|------|

| External interrupt disable period | T <sub>NUL</sub> | Interrupt: Enabled (MIE = 1),<br>CPU: NOP operation | 2.5×<br>sysclk | _    | 3.5×<br>sysclk | μS   |

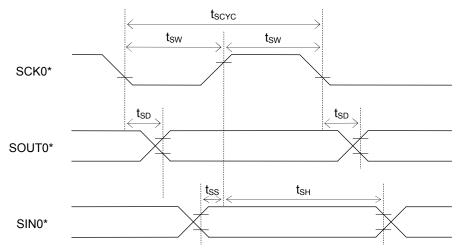

# **AC Characteristics (Synchronous Serial Port)**

$(V_{DD} = SPV_{DD} = 2.2 \text{ to } 5.5V, V_{SS} = SPV_{SS} = 0V,$ Ta = -40 to +85°C, unless otherwise specified)

|                                      |                   | .α                             | 10 10 00 0          | , amoud or          | nor mod op          | <del></del> |

|--------------------------------------|-------------------|--------------------------------|---------------------|---------------------|---------------------|-------------|

| Parameter                            | Symbol            | Condition                      | Min.                | Тур.                | Max.                | Unit        |

| SCK input cycle                      | +                 | High-speed oscillation stopped | 10                  | _                   | _                   | μS          |

| (slave mode)                         | t <sub>SCYC</sub> | During high-speed oscillation  | 500                 | _                   | _                   | ns          |

| SCK output cycle (master mode)       | t <sub>scyc</sub> | _                              | _                   | SCK <sup>(*1)</sup> | _                   | sec         |

| SCK input pulse width                |                   | High-speed oscillation stopped | 4                   | _                   | _                   | μS          |

| (slave mode)                         | t <sub>SW</sub>   | During high-speed oscillation  | 200                 | _                   | _                   | ns          |

| SCK output pulse width               | t <sub>sw</sub>   |                                | SCK <sup>(*1)</sup> | SCK <sup>(*1)</sup> | SCK <sup>(*1)</sup> | sec         |

| (master mode)                        | ısw               | _                              | ×0.4                | ×0.5                | ×0.6                | 300         |

| SOUT output delay time               | t <sub>SD</sub>   |                                | _                   |                     | 180                 | ns          |

| (slave mode)                         | ron.              |                                |                     |                     | 100                 | 110         |

| SOUT output delay time (master mode) | t <sub>SD</sub>   | _                              | _                   | _                   | 80                  | ns          |

| SIN input setup time (slave mode)    | t <sub>SS</sub>   | _                              | 50                  | _                   | _                   | ns          |

| SIN input hold time                  | t <sub>SH</sub>   | _                              | 50                  | _                   | _                   | ns          |

| *4. 0                                | 0001/0 /          | ( ()                           | /01001405           | 341                 |                     |             |

<sup>\*1:</sup> Clock period selected by S0CK3-0 of the serial port 0 mode register (SIO0MOD1)

<sup>\*:</sup> Indicates the secondary function of the corresponding port.

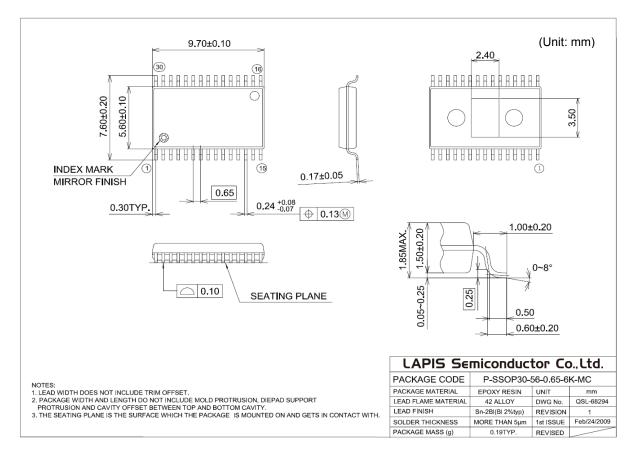

#### PACKAGE DIMENSIONS

Notes for Mounting the Surface Mount Type Package

The surface mount type packages are very susceptible to heat in reflow mounting and humidity absorbed in storage. Therefore, before you perform reflow mounting, contact ROHM's responsible sales person for the product name, package name, pin number, package code and desired mounting conditions (reflow method, temperature and times).

The heat resistance (example) of this LSI is shown below. Heat resistance ( $\theta$  Ja) changes with the size and the number of layers of a substrate.

| Die pad on the back of a package partial ground contact area | 100%                                |  |  |

|--------------------------------------------------------------|-------------------------------------|--|--|

| PCB                                                          | JEDEC<br>(W/L/t=76.2/114.5/1.6(mm)) |  |  |

| PCB Layer                                                    | 4L                                  |  |  |

| Air cooling conditions                                       | Calm (0m/sec)                       |  |  |

| Heat resistance (θJa)                                        | 45[°C/W]                            |  |  |

| Power consumption of Chip PMax at OutputPower 1W (5V)        | 0.818[W]                            |  |  |

| Power consumption of Chip PMax at OutputPower 0.5W (3.3V)    | 0.283[W]                            |  |  |

TjMax of this LSI is 125°C. TjMax is expressed with the following formulas. TjMax = TaMax +  $\theta$ Ja × PMax

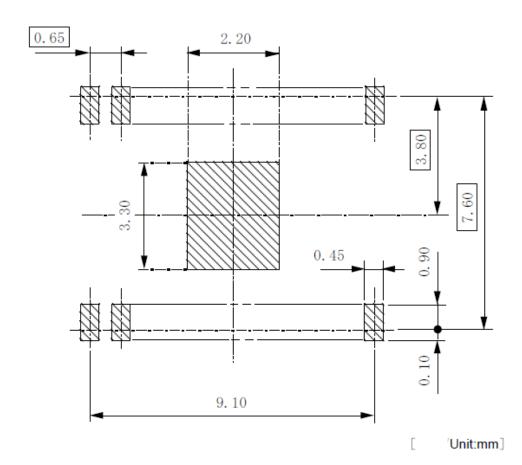

Mounting area for package lead soldering to PCB (reference data) is shown below. Die pad on the back of a package should connect with the substrate of opening or a  $V_{SS}$  for heat dissipation.

# Mounting area for package lead soldering to PC boards

When laying out PC boards, it is important to design the foot pattern so as to give consideration to ease of mounting, bonding, positioning of parts,reliability, wiring,and elimination of solder bridges.

The optimum design for the foot pattern varies with the materials of the substrate, the sort and thickness of used soldering paste, and the way of soldering. Therefore when laying out the foot pattern on the PC boards, refer to this figure which mean the mounting area that the package leads are allowable for soldering to PC boards.

# **REVISION HISTORY**

|                    |             | Page                |                    |                    |  |

|--------------------|-------------|---------------------|--------------------|--------------------|--|

| Document No.       | Date        | Previous<br>Edition | Current<br>Edition | Description        |  |

| FEDL610Q340FULL-01 | Jan 7, 2010 | _                   | -                  | Formally edition 1 |  |

#### **NOTICE**

No copying or reproduction of this document, in part or in whole, is permitted without the consent of LAPIS Semiconductor Co., Ltd.

The content specified herein is subject to change for improvement without notice.

The content specified herein is for the purpose of introducing LAPIS Semiconductor's products (hereinafter "Products"). If you wish to use any such Product, please be sure to refer to the specifications, which can be obtained from LAPIS Semiconductor upon request.

Examples of application circuits, circuit constants and any other information contained herein illustrate the standard usage and operations of the Products. The peripheral conditions must be taken into account when designing circuits for mass production.

Great care was taken in ensuring the accuracy of the information specified in this document. However, should you incur any damage arising from any inaccuracy or misprint of such information, LAPIS Semiconductor shall bear no responsibility for such damage.

The technical information specified herein is intended only to show the typical functions of and examples of application circuits for the Products. LAPIS Semiconductor does not grant you, explicitly or implicitly, any license to use or exercise intellectual property or other rights held by LAPIS Semiconductor and other parties. LAPIS Semiconductor shall bear no responsibility whatsoever for any dispute arising from the use of such technical information.

The Products specified in this document are intended to be used with general-use electronic equipment or devices (such as audio visual equipment, office-automation equipment, communication devices, electronic appliances and amusement devices).

The Products specified in this document are not designed to be radiation tolerant.

While LAPIS Semiconductor always makes efforts to enhance the quality and reliability of its Products, a Product may fail or malfunction for a variety of reasons.

Please be sure to implement in your equipment using the Products safety measures to guard against the possibility of physical injury, fire or any other damage caused in the event of the failure of any Product, such as derating, redundancy, fire control and fail-safe designs. LAPIS Semiconductor shall bear no responsibility whatsoever for your use of any Product outside of the prescribed scope or not in accordance with the instruction manual.

The Products are not designed or manufactured to be used with any equipment, device or system which requires an extremely high level of reliability the failure or malfunction of which may result in a direct threat to human life or create a risk of human injury (such as a medical instrument, transportation equipment, aerospace machinery, nuclear-reactor controller, fuel-controller or other safety device). LAPIS Semiconductor shall bear no responsibility in any way for use of any of the Products for the above special purposes. If a Product is intended to be used for any such special purpose, please contact a ROHM sales representative before purchasing.

If you intend to export or ship overseas any Product or technology specified herein that may be controlled under the Foreign Exchange and the Foreign Trade Law, you will be required to obtain a license or permit under the Law.

Copyright 2008 - 2011 LAPIS Semiconductor Co., Ltd.