## 600-mA Synchronous Buck Converter for 2-Cell Li+ Cellular Phones

## **DESCRIPTION**

The Si9167 provides a fully integrated synchronous buck converter solution for the latest 2-cell Lithium Ion battery cellular phones. Capable of delivering up to 600 mA of output current, the Si9167 provides ample power for various Baseband circuits as well as for some PAs.

The Si9167 combines the 2 MHz switching frequency with fully integrated high-frequency MOSFETs to deliver the smallest and most efficient converter available today. The 2 MHz switching frequency reduces the inductor height to a new level of less than 2 mm and minimizes the output capacitance requirement to less than 10  $\mu F,$  with only 10 mV peak-to-peak output ripple.

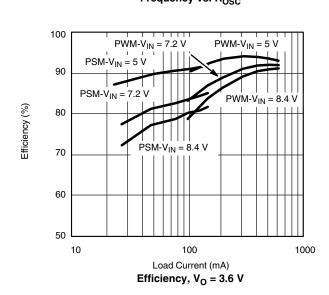

Combined with its integrated low gate charge high-frequency MOSFETs and internal synchronous rectifier, the Si9167 delivers efficiency up to 95 %. The programmable pulse-skipping mode maintains high efficiency even during the standby mode to increase overall battery life and talk time. In order to extract the last ounce of power from battery, Si9167 is designed with 100 % duty cycle capability for both PSM and PWM operating modes. With 100 % duty cycle, Si9167 operates like a saturated linear regulator to deliver the highest potential output voltage.

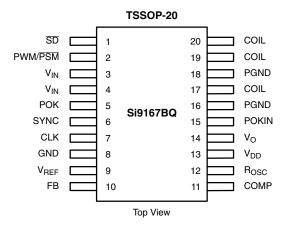

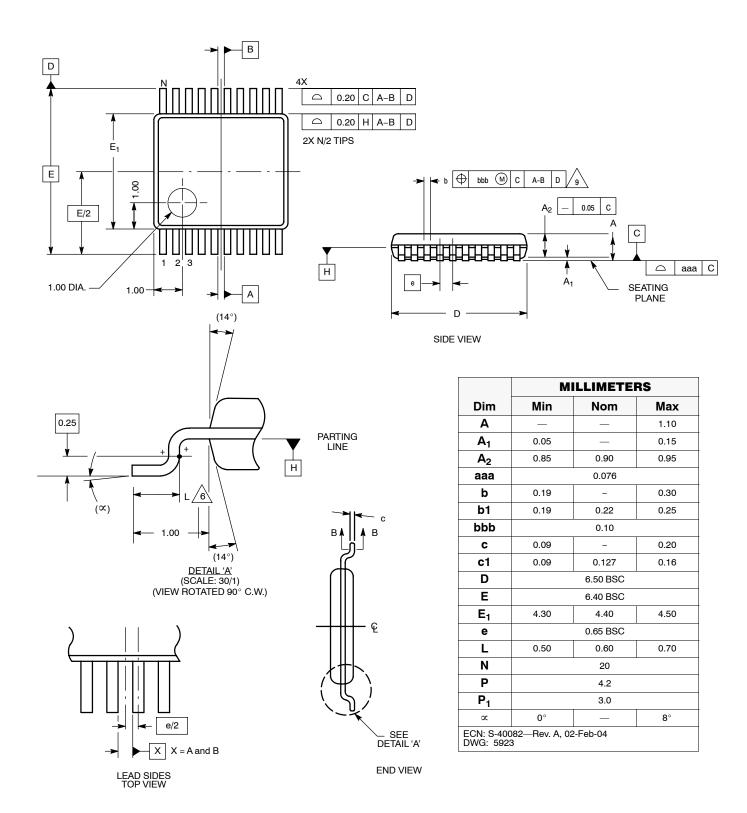

The Si9167 is available in TSSOP-20 pin package. In order to satisfy the stringent ambient temperature requirements, Si9167 is specified over the industrial temperature range of - 25 °C to 85 °C.

#### **FEATURES**

- Voltage Mode Control

- 5 V to 10 V Input Voltage Range

- Fully Integrated 600 mA MOSFET Switches

- Synchronous Rectifier Switch

- Synchronizable, Constant-Frequency PWM Mode (up to 2 MHz)

- Programmable PWM/PSM Control

- Up to 600 mA Output Current in PWM with 950  $\mu\text{A}$  Quiescent Current

- Up to 150 mA Output Current in PSM with 200  $\mu$ A Quiescent Current

- Low Dropout Operation at Low V<sub>IN</sub> - V<sub>OUT</sub>

- Integrated UVLO, POR and OTP

- · Integrated Soft-Start

- Shutdown Current < 1 μA

- · Power Good Comparator

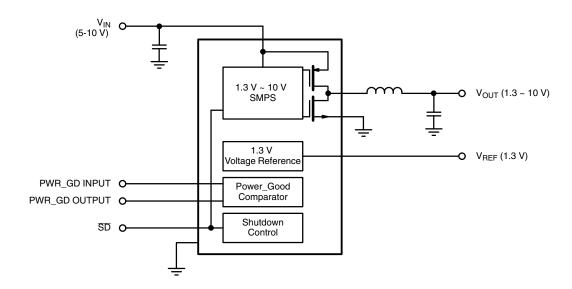

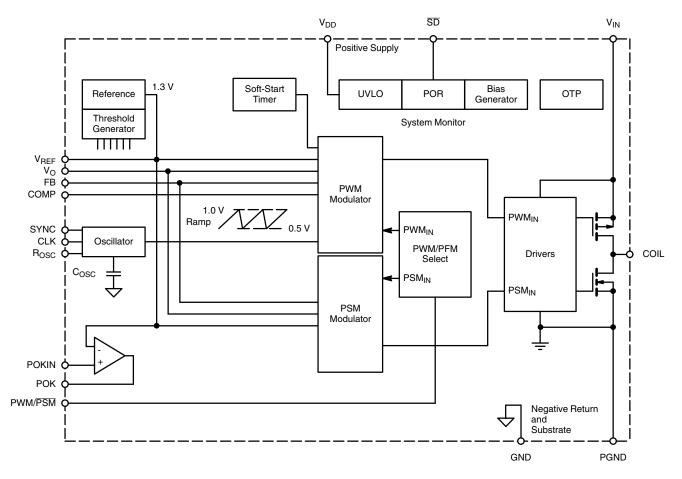

## **FUNCTIONAL BLOCK DIAGRAM**

| <b>ABSOLUTE MAXIMUM RATIN</b>                       | as                                   |                                    |      |  |

|-----------------------------------------------------|--------------------------------------|------------------------------------|------|--|

| Parameter                                           |                                      | Limit                              | Unit |  |

| Voltages Referenced to AGND                         |                                      |                                    |      |  |

| $V_{DD}$                                            |                                      | 13                                 |      |  |

| PWM/PSM, SYNC, CLK, SD, AIN, AO, V <sub>REF</sub> , | R <sub>OSC</sub> , COMP, FB          | - 0.3 V to V <sub>DD</sub> + 0.3 V |      |  |

| V <sub>O</sub>                                      |                                      | - 0.3 V to V <sub>S</sub> + 0.3 V  |      |  |

| PGND                                                |                                      | ± 0.3                              |      |  |

| Voltages Referenced to PGND                         |                                      |                                    | •    |  |

| V <sub>IN</sub>                                     |                                      | 13                                 | V    |  |

| COIL                                                |                                      | - 0.4 V to V <sub>S</sub> + 0.4 V  |      |  |

| Peak Output Current                                 |                                      | 3                                  | A    |  |

| Continuous Output Current                           |                                      | 1                                  | ^    |  |

| Storage Temperature                                 |                                      | - 65 to 150                        |      |  |

| Operating Junction Temperature                      |                                      | 150                                |      |  |

| Power Dissipation (Package) <sup>a</sup>            | 20-Pin TSSOP (Q Suffix) <sup>b</sup> | 1.56                               | W    |  |

| Thermal Impedance ( $\Theta_{JA}$ )                 | 20-Pin TSSOP                         | 80                                 | °C/W |  |

#### Notes:

- a. Device Mounted with all leads soldered or welded to PC board.

- b. Derate 12.5 mW/°C above 25 °C.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

| RECOMMENDED OPERATING RANGE |                                 |      |  |  |  |

|-----------------------------|---------------------------------|------|--|--|--|

| Parameter                   | Limit                           | Unit |  |  |  |

| Voltages Referenced to AGND | Voltages Referenced to AGND     |      |  |  |  |

| $V_{DD}$                    | 5 V to 10 V                     | V    |  |  |  |

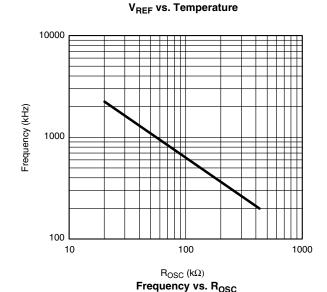

| Oscillator Frequency        | 200 kHz to 2 MHz                |      |  |  |  |

| Rosc                        | 20 k $\Omega$ to 300 k $\Omega$ | kΩ   |  |  |  |

| V <sub>OUT</sub>            | 1.3 V to 10 V                   | V    |  |  |  |

| PWM/PSM, SYNC, SD           | 0 V to V <sub>DD</sub>          | V    |  |  |  |

| V <sub>REF</sub> Capacitor  | 0.1                             | μF   |  |  |  |

| Voltages Referenced to PGND | ·                               |      |  |  |  |

| V <sub>IN</sub>             | 0.5 V to 10 V                   | V    |  |  |  |

| SPECIFICATIONS                  |                  |                                                                                  |                  |                      |                  |      |

|---------------------------------|------------------|----------------------------------------------------------------------------------|------------------|----------------------|------------------|------|

|                                 |                  | Test Conditions Unless Otherwise Specified                                       | - 2              | Limits<br>5 °C to 85 | °C               |      |

| Parameter                       | Symbol           | $5 \text{ V} \le \text{V}_{DD} \le 10 \text{ V}, \text{ V}_{IN} = \text{V}_{DD}$ | Min <sup>a</sup> | Typ <sup>b</sup>     | Max <sup>a</sup> | Unit |

| Reference                       |                  |                                                                                  |                  |                      |                  |      |

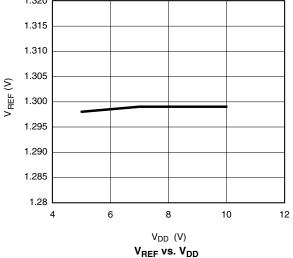

| Output Voltage                  | V <sub>REF</sub> | I <sub>REF</sub> = 0                                                             | 1.2675           | 1.3                  | 1.3325           | V    |

|                                 |                  | V <sub>DD</sub> = 7.2 V, I <sub>REF</sub> = 0, 25 °C                             | 1.280            | 1.3                  | 1.320            |      |

| V <sub>REF</sub> Current        | I <sub>REF</sub> |                                                                                  |                  | - 0.5                |                  | mA   |

| V <sub>REF</sub> PSRR           | P <sub>SRR</sub> |                                                                                  |                  | 60                   |                  | dB   |

| UVLO                            |                  |                                                                                  |                  |                      |                  |      |

| Under Voltage Lockout (Turn-On) |                  |                                                                                  | 4.25             | 4.5                  | 4.75             | V    |

| Hysteresis                      |                  |                                                                                  |                  | 0.2                  |                  | ]    |

| Soft-Start Time                 | <u>.</u>         |                                                                                  |                  |                      |                  |      |

| SS Time                         | t <sub>SS</sub>  |                                                                                  |                  | 10                   |                  | ms   |

|                                      |                                     | Test Conditions Unless Otherwise Specified                                       | Limits<br>- 25 °C to 85 °C |                  | °C               |          |

|--------------------------------------|-------------------------------------|----------------------------------------------------------------------------------|----------------------------|------------------|------------------|----------|

| Parameter                            | Symbol                              | $5 \text{ V} \le \text{V}_{DD} \le 10 \text{ V}, \text{ V}_{IN} = \text{V}_{DD}$ | Min <sup>a</sup>           | Typ <sup>b</sup> | Max <sup>a</sup> | Unit     |

| SD, SYNC, PWM/PSM                    |                                     |                                                                                  |                            |                  |                  |          |

| Logic High                           | T                                   |                                                                                  | 2.4                        |                  |                  | T        |

| Logic Low                            |                                     |                                                                                  |                            |                  | 0.8              | V        |

| Oscillator                           |                                     |                                                                                  |                            |                  |                  |          |

| Maximum Frequency                    | F <sub>MAX</sub>                    |                                                                                  |                            |                  | 2                | MHz      |

| Accuracy                             |                                     | 1 % External Resistor                                                            | - 20                       |                  | 20               |          |

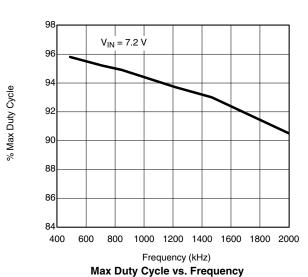

| Maximum Duty Cycle<br>(Non LDO Mode) | D <sub>MAX</sub>                    | F <sub>SW</sub> = 2 MHz                                                          |                            | 80               |                  | %        |

| SYNC Range                           | F <sub>SYNC</sub> /F <sub>OSC</sub> | F <sub>SYNC</sub> ≤ 2 MHz                                                        | 1.2                        | 1.5              |                  |          |

| SYNC Low Pulse Width                 |                                     |                                                                                  | 50                         |                  |                  |          |

| SYNC High Pulse Width                |                                     |                                                                                  | 50                         |                  |                  | ns       |

| SYNC t <sub>r</sub> , t <sub>f</sub> | t <sub>r</sub> , t <sub>f</sub>     | (10 % to 90 %)                                                                   |                            |                  | 50               | 1        |

| Error Amplifier                      | L                                   | · · · · · · · · · · · · · · · · · · ·                                            |                            |                  |                  |          |

| Input Regulation Range               | V <sub>FB</sub>                     |                                                                                  | 1.260                      |                  | 1.340            | V        |

| Input Bias Current                   | I <sub>BIAS</sub>                   | V <sub>FB</sub> = 1.4 V                                                          | - 1                        |                  | 1                | μΑ       |

| Open Loop Voltage Gain               | A <sub>VOL</sub>                    | . 5                                                                              | 50                         | 60               |                  | <u>'</u> |

| Power Supply Rejection               | P <sub>SRR</sub>                    |                                                                                  |                            | 60               |                  | dB       |

| Unity Gain BW                        | BW                                  |                                                                                  |                            | 2                |                  | MHz      |

| Output Current (Source)              |                                     | V <sub>FB</sub> = 1.05 V                                                         |                            | - 2              | - 0.5            | 101112   |

| Output Current (Sink)                | I <sub>EA</sub>                     | V <sub>FB</sub> = 1.55 V                                                         | 1                          | 2                | 0.0              | mA       |

| PSM Modulator                        |                                     | 1. LB 1.100 1                                                                    |                            |                  |                  |          |

| Inductor Peak Current                | I <sub>PEAK</sub>                   | V <sub>DD</sub> = 7.2 V, V <sub>OUT</sub> = 3.3 V                                |                            | 500              |                  | mA       |

| Output Capability                    | PEAK                                | V <sub>DD</sub> = 7.2 v, v <sub>OO1</sub> = 8.8 v                                |                            | 300              |                  | 111/     |

|                                      |                                     |                                                                                  | 600                        |                  |                  | l l      |

| PWM Mode Output <sup>c</sup>         | I <sub>OUT</sub>                    | $V_{DD} = V_{IN} = 7.2 \text{ V}, V_{OUT} = 3.3 \text{ V}$                       |                            |                  |                  | mA       |

| PSM Mode Output <sup>c</sup>         |                                     |                                                                                  | 150                        |                  |                  |          |

| r <sub>DS(ON)</sub> High Side        | r <sub>DS(ON-P)</sub>               | $V_{DD} = V_{IN} = 7.2 \text{ V}$                                                |                            |                  | 300              | mΩ       |

| r <sub>DS(ON)</sub> Low Side         | r <sub>DS(ON-N)</sub>               | 22 114                                                                           |                            |                  | 300              |          |

| Over Temperature Protection          | T                                   |                                                                                  |                            |                  |                  | _        |

| Trip Point                           |                                     |                                                                                  |                            | 165              |                  | °C       |

| Hysteresis                           |                                     |                                                                                  |                            | 25               |                  |          |

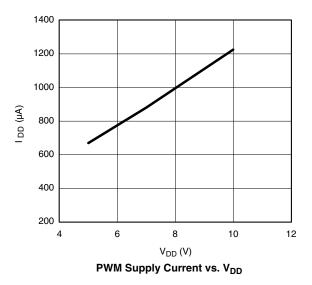

| Supply Name of Maria                 |                                     | V V 70V                                                                          |                            | 050              | 1050             | T        |

| Normal Mode                          |                                     | $V_{DD} = V_{IN} = 7.2 \text{ V}$                                                |                            | 950              | 1350             |          |

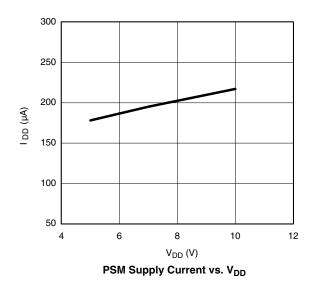

| PSM Mode                             |                                     | F <sub>OSC</sub> = 1.6 MHz                                                       |                            | 200              | 350              | μΑ       |

| Shutdown Mode                        |                                     |                                                                                  |                            |                  | 1                |          |

| Power Good Comparator                |                                     | Diging V                                                                         | 1.070                      | 1.000            | 1.000            |          |

| POKIN Trip Level                     |                                     | Rising V <sub>POKIN</sub>                                                        | 1.270                      | 1.300            | 1.330            | V        |

| POKIN Input Current                  |                                     |                                                                                  | - 20                       | F2               | 20               | nA       |

| POKIN Hysteresis                     |                                     |                                                                                  | 30                         | 50               |                  | mV       |

| POK Low Voltage                      |                                     | $I_{SINK(POK)} = 1 \text{ mA}$                                                   |                            |                  | 0.4              | V        |

| POK High Leakage Current             |                                     |                                                                                  |                            | 0.001            | 1                | μΑ       |

#### Notes

a. The algebraic convention whereby the most negative value is a minimum and the most positive a maximum, is used in this data sheet.

b. Typical values are for DESIGN AID ONLY, not guaranteed or subject to production testing.

c. Guaranteed by design and characterization, not subject to production testing.

# VISHAY.

## TYPICAL CHARACTERISTICS 25 °C, unless otherwise noted

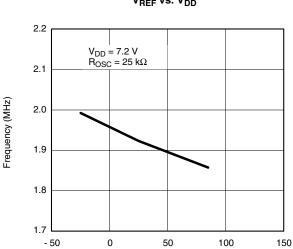

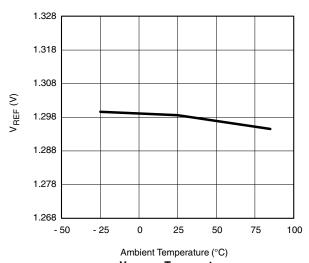

Ambient Temperature (°C)

Frequency vs. Temperature

## TYPICAL CHARACTERISTICS 25 °C, unless otherwise noted

## **TYPICAL WAVEFORMS**

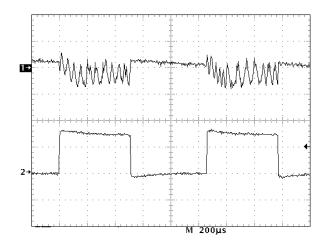

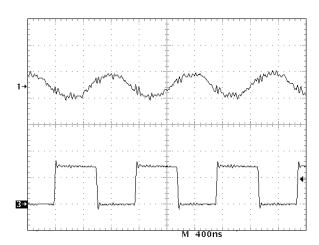

$\begin{array}{l} V_{IN} = 7.2 \text{ V, } V_O = 3.6 \text{ V, Step } I_O = 0 \text{ to } 150 \text{ mA} \\ \text{Step Load Slew Rate} = 1 \text{ A/µsec} \\ \text{Ch1:} \quad V_{OUT} \text{ (50 mV/div)} \\ \text{Ch2:} \quad I_{OUT} \text{ (100 mA/div)} \end{array}$

Figure 1. Transient Response PSM Mode

## **TYPICAL WAVEFORMS**

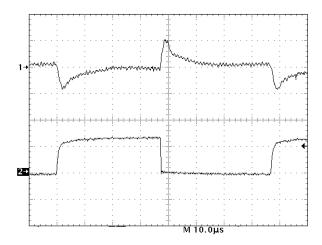

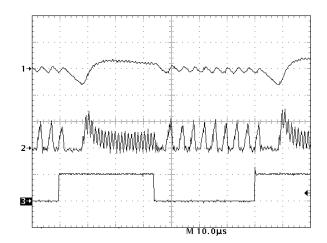

$\begin{array}{l} V_{IN}=7.2~V,~V_O=3.6~V,~Step~I_O=0~to~600~mA\\ Step~Load~Slew~Rate=1~A/\mu sec\\ Ch1:~~V_{OUT}~(100~mV/div)\\ Ch2:~~I_{OUT}~(500~mA/div) \end{array}$

Figure 2. Transient Response PWM Mode

$\begin{array}{lll} \rm V_{IN} = 7.2~V,~V_O = 3.6~V,~I_O = 150~mA \\ \rm Ch1: & V_{OUT}~(50~mV/div) \\ \rm Ch3: & Coil~(5~V/div) \end{array}$

Figure 3. PSM Output Ripple

$$\begin{split} &V_{IN} = 7.2 \text{ V, } V_O = 3.6 \text{ V, } I_O = 600 \text{ mA} \\ &Ch1: \quad &V_{OUT} \left(10 \text{ mV/div}\right) \\ &Ch3: \quad &Coil \left(5 \text{ V/div}\right) \end{split}$$

Figure 4. PWM Output Ripple

## **TYPICAL WAVEFORMS**

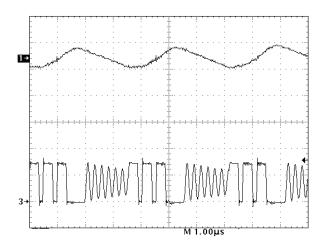

$\begin{array}{lll} V_{IN} = 7.2 \text{ V, } V_O = 3.6 \text{ V, } I_O = 150 \text{ mA} \\ \text{Ch1:} & V_{OUT} (200 \text{ mV/div}) \\ \text{Ch2:} & \text{Inductor Current (500 mA/div)} \\ \text{Ch3:} & \text{PWM/PSM} \text{ (High PWM, Low PSM)} \\ \end{array}$

Figure 5. PSM-PWM-PSM Transition

## **PIN CONFIGURATION**

| ORDERING INFORMATION |                   |               |

|----------------------|-------------------|---------------|

| Part Number          | Temperature Range | Package       |

| Si9167BQ-T1          | - 25 to 85 °C     | Tape and Reel |

| Eval Kit | Temperature Range | Board Type    |  |

|----------|-------------------|---------------|--|

| Si9167DB | - 25 to 85 °C     | Surface Mount |  |

| PIN DESCRIPTION |                 |                                                                                                              |  |  |

|-----------------|-----------------|--------------------------------------------------------------------------------------------------------------|--|--|

| Pin Number      | Name            | Function                                                                                                     |  |  |

| 1               | SD              | Shuts down the IC completely and decreases current consumed by the IC to < 1 μA.                             |  |  |

| 2               | PWM/PSM         | Logic high = PWM mode, logic low = PSM mode.                                                                 |  |  |

| 3, 4            | V <sub>IN</sub> | Input node for buck converter as well as input supply voltage for the internal MOSFET gate drive voltage.    |  |  |

| 5               | POK             | Power_good comparator output, It sinks current when VPOKIN < 1.3 V, high Impedance state during disable.     |  |  |

| 6               | SYNC            | Externally controlled synchronization signal. Logic high to low transition forces the clock synchronization. |  |  |

| 7               | CLK             | Oscillator output                                                                                            |  |  |

| 8               | GND             | Analog ground                                                                                                |  |  |

| 9               | $V_{REF}$       | 1.3 V reference. Bypassed with 0.1 μF capacitor.                                                             |  |  |

| 10              | FB              | Output voltage feedback                                                                                      |  |  |

| 11              | COMP            | Error amplifier output for external compensation network                                                     |  |  |

| 12              | Rosc            | External resistor to set the switching frequency                                                             |  |  |

| 13              | $V_{DD}$        | Supply voltage for the control circuit                                                                       |  |  |

| 14              | V <sub>O</sub>  | Direct output voltage sense                                                                                  |  |  |

| 15              | POKIN           | Power_good comparator input                                                                                  |  |  |

| 16, 18          | PGND            | Power ground                                                                                                 |  |  |

| 17, 19, 20      | COIL            | Inductor connection node                                                                                     |  |  |

# VISHAY

### **BLOCK DIAGRAM**

Figure 1.

## **DETAIL OPERATIONAL DESCRIPTION**

#### **UVLO**

The UVLO circuit prevents the internal MOSFET switches and oscillator circuit from turning on, when the input voltage is too low to regulate output voltage. Failing to do this could unintentionally lock up the system. The typical turn on threshold is 4.5 V with a turn off hysteresis of 0.2 V.

## **STARTUP**

Once the input voltage is above the turn on threshold, and with no other shutdown condition detected, the system enters a POR (power on reset) phase, which lasts about 1 ms. During this POR phase, most of the circuits are activated, except for the power switches. After the POR phase,

an internal soft-start circuit slowly regulates the output voltage from 0 V to its intended level. This soft-start phase typically lasts for 3 ms.

Note that the Si9167 always soft-starts in the PWM mode regardless of the voltage level on the PWM/PSM pin.

## **Shutdown**

The Si9167 is designed to conserve as much battery life as possible by decreasing current consumption of the IC during normal operation as well as in the shutdown mode. With logic low level on the  $\overline{SD}$  pin, current consumption of the Si9167 is decreased to less than 1  $\mu$ A by shutting off most of the circuits. The logic high enables the converter and starts up as described in "Start-Up" section above.

#### **DETAIL OPERATIONAL DESCRIPTION**

## **Over Temperature Protection**

The Si9167 is designed with an over temperature protection circuit to prevent the MOSFET switches from overheating. If the temperature reaches 165  $^{\circ}$ C, internal soft-start capacitor is discharged, shutting down the output stage. The converter remains in the disabled mode until the temperature in the IC decreases below 140  $^{\circ}$ C.

#### **PWM Mode**

With PWM/PSM pin pulled logic high, Si9167 operates in constant frequency (PWM) mode. The converter regulates the output voltage by modulating the MOSFET switch duty cycle. Switching harmonics generated by fixed-frequency operation are consistent and easy to filter. The switching frequency is programmed by the ROSC value as shown by the oscillator curve. In the PWM mode, the synchronous switch is always enabled, which permits the converter to run in continuous current mode, even when the output current reaches 0 A. In continuous current mode, the transfer function of the converter remains constant, providing fast transient response. If the converter operates in discontinuous current mode, overall loop gain decreases and transient response time can be ten times longer than if the converter remains in continuous current mode. This transient response time advantage can significantly decrease the size of the hold-up capacitors needed on the output of dc-dc converter to meet the transient voltage regulation.

The Si9167 can operate at 100 % duty cycle, when it operates like a saturated linear regulator. This allows the system designers to extract out the maximum stored energy from the battery. As input voltage drops close to output regulation level, the converter will approach maximum switching duty cycle, about 80 %, at full switching frequency. As input voltage further decreases, the converter will enter 100 % duty cycle mode. This instantaneous jump in duty cycle is due to BBM time and the internal propagation delays. In order to maintain regulation, the converter might change its duty cycle back and forth from 100 % to maximum switching duty cycle during this input voltage range. If the input voltage drops further, the converter will remain at 100 % duty cycle. If the input voltage increases to a point where it requires less than maximum duty cycle, about 80 %, the converter will resume normal PWM operation.

## **Pulse Skipping Mode**

Gate charge losses of MOSFETs can be the dominant power dissipation during light load (i.e. < 10 mA) if the converter is switching at high frequency. With PWM/PSM pin pulled logic low, the Si9167 operates in PSM mode. During this mode, the converter switching frequency is lower than PWM switching frequency in order to achieve high power efficiency at light load. By building up inductor current to a fixed level during each cycle, the converter regulates the output voltage with variable switching frequency, depending on the operating condition.

During PSM mode, a comparator detects the output voltage out of regulation and sets up a charging cycle. Depending upon the input to output voltage difference, the high-side MOSFET is on for certain amount of time and off for a shorter duration. This on-off cycle continues until the output voltage rises above the target level. the comparator detects this condition and idles the converter until the output falls under the converter output regulation level. Here, the comparator initializes another charge cycle. During the idle time, when both switches are off, the load is supplied by the output capacitor.

When the input voltage approaches the programmed output voltage the converter operates as a saturated linear regulator. If the input voltage is lower than the programmed output voltage then the converter operates in a 100 % duty cycle mode such that the output voltage will closely follow the input voltage.

#### **REF**

The reference voltage of the Si9167 is set at 1.3 V. The reference voltage is internally connected to the non-inverting inputs of the error amplifier. The reference voltage output is bypassed by  $0.1~\mu F$  capacitor.

## **Error Amplifier**

In order to establish high-speed system response, the Si9167 is designed with 2 MHz error amplifier to generate the widest converter bandwidth and 3.5 V/ $\mu$ s slew rate for fast large signal response.

## Oscillator

The oscillator is designed to operate up to 2 MHz minimal. The 2 MHz operating frequency allows the converter to minimize the inductor and capacitor size, improve the power density of the converter. Attaching a resistor to  $R_{OSC}$  pin easily programs the switching frequency. See oscillator frequency versus Rosc curve to select the proper values for desired operating frequency. The tolerance on the operating frequency is  $\pm$  20 % with 1 % tolerance resistor.

### **Synchronization**

The synchronization with external clock is easily accomplished by connecting the external clock into the SYNC pin. Logic high to low transition synchronizes the clock. The external clock frequency must be within 1.2 to 1.5 times the internal clock frequency.

## **CLK Output**

During PWM mode, CLK pin provides oscillator signal for users to synchronize other converters in order to set the harmonics to avoid IF bands in wireless applications. This is accomplished by connecting CLK of the master to Sync of the slave.

#### **DETAIL OPERATIONAL DESCRIPTION**

## **Break-Before-Make Timing**

A proper BBM time is essential in order to prevent shootthrough current and maintain high efficiency. The breakbefore-make time is set internally at 20 to 40 ns at  $V_{DD} = 7.2 \text{ V}$ . After one switch (either high-side or low-side) is turned off, 20 to 40 ns BBM time is set before the other switch turns on. The maximum and minimum controllable duty cycle is primarily limited by the BBM time. Since the BBM time is fixed, maximum controllable duty cycle will vary depending on the switching frequency. Typically, the higher the PWM switching frequency, the lower the maximum duty cycle and the higher the minimum duty cycle.

## **Output MOSFET Stage**

The high and low-side switches are integrated to provide optimum performance and to minimize the overall converter size. Both high and low-side switches are designed to handle

up to 600 mA of continuous current. The MOSFET switches were designed to minimize the gate charge loss as well as the conduction loss. For high frequency operation, switching losses can exceed conduction loss, if the switches are designed incorrectly. Under full load, efficiency of up to 95 % is accomplished with 7.2 V battery voltage (3.3 V output voltage).

## **Power Good Comparator**

The Si9167 has an uncommitted power good comparator. This comparator has its negative input connected directly to 1.3 V reference and has a typical hysteresis of 50 mV at room temperature. Its output is an open-drain N-Channel MOSFET capable of sinking 1 mA. This output is open circuit in the shutdown mode.

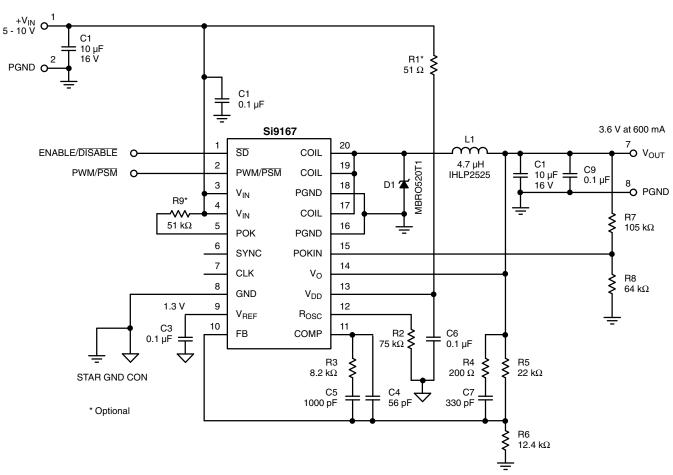

## STANDARD APPLICATION

Figure 2. Typical Application Circuit - Buck

Vishay Siliconix maintains worldwide manufacturing capability. Products may be manufactured at one of several qualified locations. Reliability data for Silicon Technology and Package Reliability represent a composite of all qualified locations. For related documents such as package/tape drawings, part marking, and reliability data, see http://www.vishay.com/ppg?70898.

## TSSOP: 20-LEAD (POWER IC ONLY)

Document Number: 72818 28-Jan-04

www.vishay.com

## **Legal Disclaimer Notice**

Vishay

## **Disclaimer**

ALL PRODUCT, PRODUCT SPECIFICATIONS AND DATA ARE SUBJECT TO CHANGE WITHOUT NOTICE TO IMPROVE RELIABILITY, FUNCTION OR DESIGN OR OTHERWISE.

Vishay Intertechnology, Inc., its affiliates, agents, and employees, and all persons acting on its or their behalf (collectively, "Vishay"), disclaim any and all liability for any errors, inaccuracies or incompleteness contained in any datasheet or in any other disclosure relating to any product.

Vishay makes no warranty, representation or guarantee regarding the suitability of the products for any particular purpose or the continuing production of any product. To the maximum extent permitted by applicable law, Vishay disclaims (i) any and all liability arising out of the application or use of any product, (ii) any and all liability, including without limitation special, consequential or incidental damages, and (iii) any and all implied warranties, including warranties of fitness for particular purpose, non-infringement and merchantability.

Statements regarding the suitability of products for certain types of applications are based on Vishay's knowledge of typical requirements that are often placed on Vishay products in generic applications. Such statements are not binding statements about the suitability of products for a particular application. It is the customer's responsibility to validate that a particular product with the properties described in the product specification is suitable for use in a particular application. Parameters provided in datasheets and/or specifications may vary in different applications and performance may vary over time. All operating parameters, including typical parameters, must be validated for each customer application by the customer's technical experts. Product specifications do not expand or otherwise modify Vishay's terms and conditions of purchase, including but not limited to the warranty expressed therein.

Except as expressly indicated in writing, Vishay products are not designed for use in medical, life-saving, or life-sustaining applications or for any other application in which the failure of the Vishay product could result in personal injury or death. Customers using or selling Vishay products not expressly indicated for use in such applications do so at their own risk. Please contact authorized Vishay personnel to obtain written terms and conditions regarding products designed for such applications.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted by this document or by any conduct of Vishay. Product names and markings noted herein may be trademarks of their respective owners.

## **Material Category Policy**

Vishay Intertechnology, Inc. hereby certifies that all its products that are identified as RoHS-Compliant fulfill the definitions and restrictions defined under Directive 2011/65/EU of The European Parliament and of the Council of June 8, 2011 on the restriction of the use of certain hazardous substances in electrical and electronic equipment (EEE) - recast, unless otherwise specified as non-compliant.

Please note that some Vishay documentation may still make reference to RoHS Directive 2002/95/EC. We confirm that all the products identified as being compliant to Directive 2002/95/EC conform to Directive 2011/65/EU.

Vishay Intertechnology, Inc. hereby certifies that all its products that are identified as Halogen-Free follow Halogen-Free requirements as per JEDEC JS709A standards. Please note that some Vishay documentation may still make reference to the IEC 61249-2-21 definition. We confirm that all the products identified as being compliant to IEC 61249-2-21 conform to JEDEC JS709A standards.

Revision: 02-Oct-12 Document Number: 91000

## **Mouser Electronics**

**Authorized Distributor**

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

Vishay:

SI9167BQ-T1-E3 SI9167BQ-T1