# MRF89XA Data Sheet

Ultra Low-Power, Integrated ISM Band Sub-GHz Transceiver

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION. INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights unless otherwise stated.

Microchip received ISO/TS-16949:2009 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC® MCUs and dsPIC® DSCs, KEELOQ® code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

# QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV = ISO/TS 16949=

#### **Trademarks**

The Microchip name and logo, the Microchip logo, AnyRate, AVR, AVR logo, AVR Freaks, BeaconThings, BitCloud, CryptoMemory, CryptoRF, dsPIC, FlashFlex, flexPWR, Heldo, JukeBlox, KEELOQ, KEELOQ logo, Kleer, LANCheck, LINK MD, maXStylus, maXTouch, MediaLB, megaAVR, MOST, MOST logo, MPLAB, OptoLyzer, PIC, picoPower, PICSTART, PIC32 logo, Prochip Designer, QTouch, RightTouch, SAM-BA, SpyNIC, SST, SST Logo, SuperFlash, tinyAVR, UNI/O, and XMEGA are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

ClockWorks, The Embedded Control Solutions Company, EtherSynch, Hyper Speed Control, HyperLight Load, IntelliMOS, mTouch, Precision Edge, and Quiet-Wire are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Adjacent Key Suppression, AKS, Analog-for-the-Digital Age, Any Capacitor, Anyln, AnyOut, BodyCom, chipKIT, chipKIT logo, CodeGuard, CryptoAuthentication, CryptoCompanion, CryptoController, dsPICDEM, dsPICDEM.net, Dynamic Average Matching, DAM, ECAN, EtherGREEN, In-Circuit Serial Programming, ICSP, Inter-Chip Connectivity, JitterBlocker, KleerNet, KleerNet logo, Mindi, MiWi, motorBench, MPASM, MPF, MPLAB Certified logo, MPLIB, MPLINK, MultiTRAK, NetDetach, Omniscient Code Generation, PICDEM, PICDEM.net, PICkit, PICtail, PureSilicon, QMatrix, RightTouch logo, REAL ICE, Ripple Blocker, SAM-ICE, Serial Quad I/O, SMART-I.S., SQI, SuperSwitcher, SuperSwitcher II, Total Endurance, TSHARC, USBCheck, VariSense, ViewSpan, WiperLock, Wireless DNA, and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

$\ensuremath{\mathsf{SQTP}}$  is a service mark of Microchip Technology Incorporated in the U.S.A.

Silicon Storage Technology is a registered trademark of Microchip Technology Inc. in other countries.

GestIC is a registered trademark of Microchip Technology Germany II GmbH & Co. KG, a subsidiary of Microchip Technology Inc., in other countries.

All other trademarks mentioned herein are property of their respective companies.

© 2010-2017, Microchip Technology Incorporated, All Rights Reserved.

ISBN: 978-1-5224-2296-9

### Ultra Low-Power, Integrated ISM Band Sub-GHz Transceiver

#### **Features**

- · Fully integrated ultra low-power, sub-GHz transceiver

- · Wide-band half-duplex transceiver

- · Supports proprietary sub-GHz wireless protocols

- · Simple 4-wire SPI-compatible interface

- CMOS/TTL-compatible I/Os

- · On-chip oscillator circuit

- · Dedicated clock output

- · Supports power-saving modes

- · Operating voltage: 2.1-3.6V

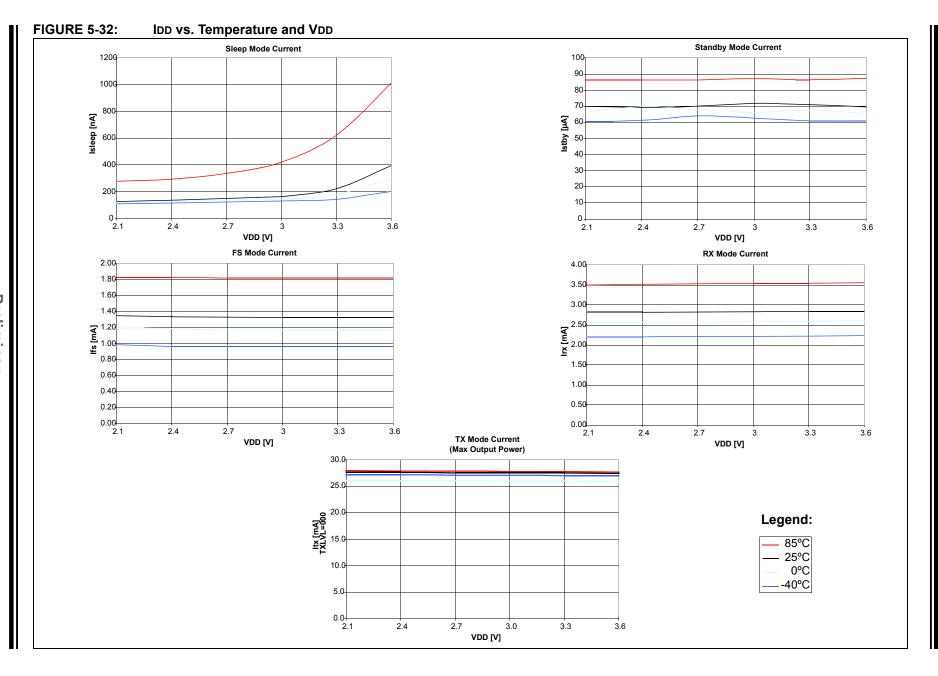

- · Low-current consumption, typically:

- 3 mA in RX mode

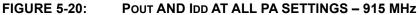

- 25 mA at +10 dBm in TX mode

- 0.1  $\mu A$  (Typical) and 2  $\mu A$  (Maximum) in Sleep mode

- Supports Industrial temperature range (-40°C to +85°C)

- · Complies with ETSI EN 300-220 and FCC part 15

- · Small, 32-pin TQFN package

#### **RF/Analog Features**

- Supports ISM band sub-GHz frequency ranges: 863–870, 902–928 and 950–960 MHz

- Modulation technique: Supports FSK and OOK

- Supports high data rates: Up to 200 kbps, NRZ coding

- Reception sensitivity: Down to -107 dBm at 25 kbps in FSK, -113 dBm at 2 kbps in OOK

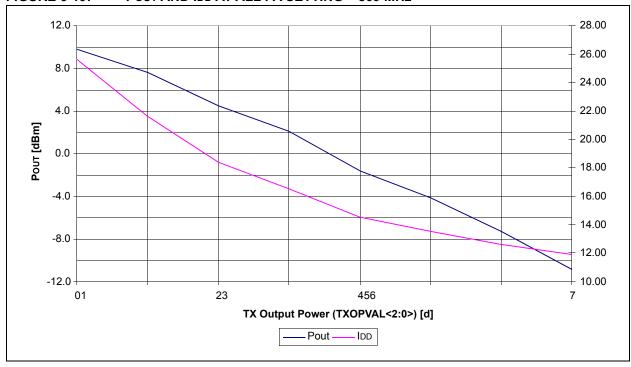

- RF output power: +12.5 dBm programmable in eight steps

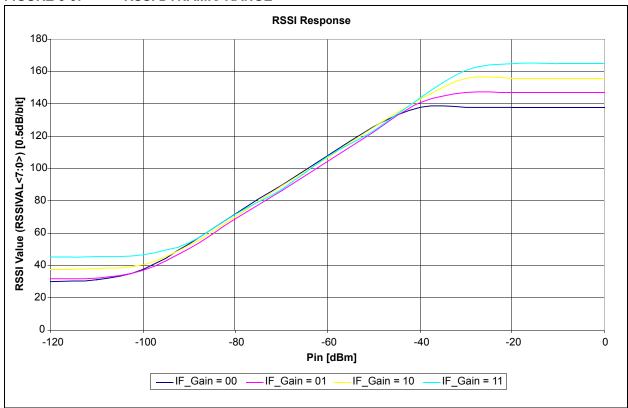

- Wide Received Signal Strength Indicator (RSSI), dynamic range: 70 dB from RX noise floor

- Signal-ended RF input/output

- · On-chip frequency synthesizer

- · Supports PLL loop filter with lock detect

- Integrated Power Amplifier (PA) and Low Noise Amplifiers (LNA)

- · Channel filters

- · On-chip IF gain and mixers

- · Integrated low-phase noise VCO

#### **Baseband Features**

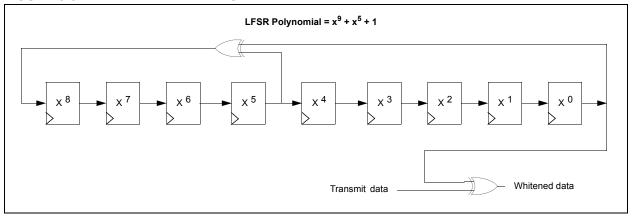

- Packet handling feature with data whitening and automatic CRC generation

- · Incoming Sync Word (pattern) recognition

- Built-in bit synchronizer for incoming data, and clock synchronization and recovery

- 64-byte transmit/receive FIFO with preload in Standby mode

- · Supports Manchester encoding/decoding techniques

#### **Typical Applications**

- · Home/industrial/building automation

- · Remote wireless control

- · Wireless PC peripherals

- · Remote keyless entry

- · Wireless sensor networks

- Vehicle sensor monitoring

- Telemetry

- · Data logging systems

- · Wireless alarm

- · Remote automatic meter reading

- · Security systems for home/industrial environments

- · Automobile immobilizers

- · Sports and performance monitoring

- · Wireless toy controls

- · Medical applications

#### **General Description**

The MRF89XA is a single chip, multi-channel FSK/OOK transceiver capable of operating in the 863-870 MHz and 902-928 MHz license-free ISM frequency bands, as well as the 950-960 MHz frequency band. The low-cost MRF89XA is optimized for very low-power consumption. It incorporates a baseband modem with data rates up to 200 kbps. Data handling features include a 64-byte FIFO, packet handling, automatic CRC generation and data whitening. Its highly integrated architecture allows for minimum external component count while still maintaining design flexibility.

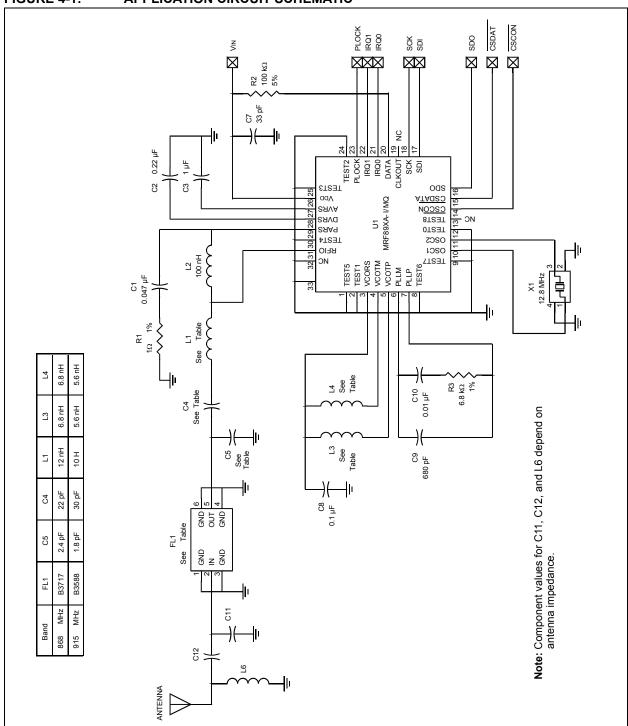

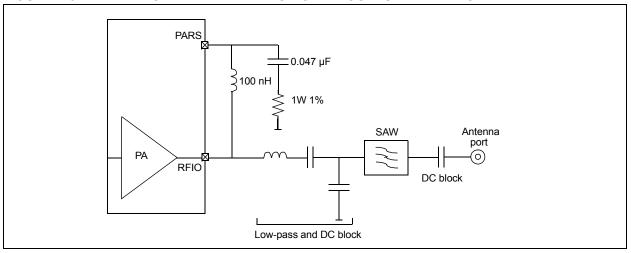

All critical RF and baseband functions are integrated in the MRF89XA, which minimizes the external component count and reduces the design time. The RF communication parameters are made programmable and most of them may be dynamically set. A microcontroller, RF SAW filter, 12.8 MHz crystal, and a few passive components are required to create a complete, reliable radio function. The MRF89XA uses several low-power mechanisms to reduce overall current consumption and extend battery life. Its small size and low-power consumption makes the MRF89XA ideal for a wide variety of short-range radio applications. The MRF89XA complies with European (ETSI EN 300-220) and United States (FCC Part 15.247 and 15.249) regulatory standards.

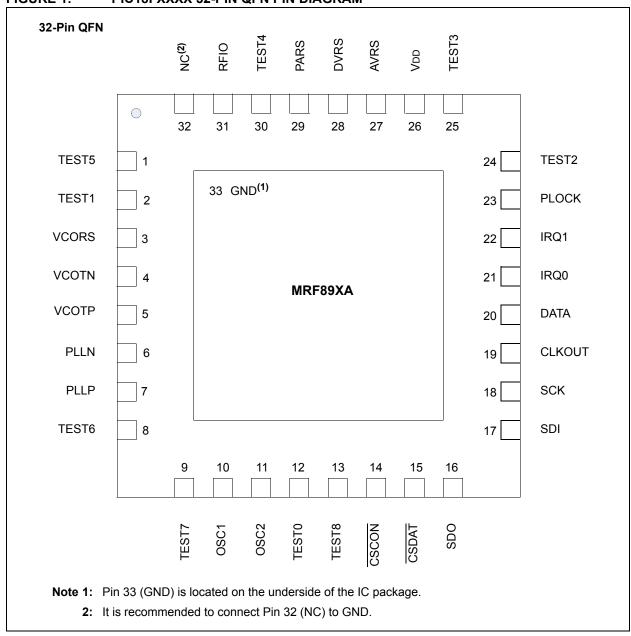

#### **Pin Diagram**

Figure 1 illustrates the top-view pin arrangement of the 32-pin QFN package.

FIGURE 1: PIC18FXXXX 32-PIN QFN PIN DIAGRAM

#### **Table of Contents**

| Overview                                         | 7   |

|--------------------------------------------------|-----|

| Hardware Description                             | 11  |

| Functional Description                           |     |

| Application Details                              |     |

| Electrical Characteristics                       | 103 |

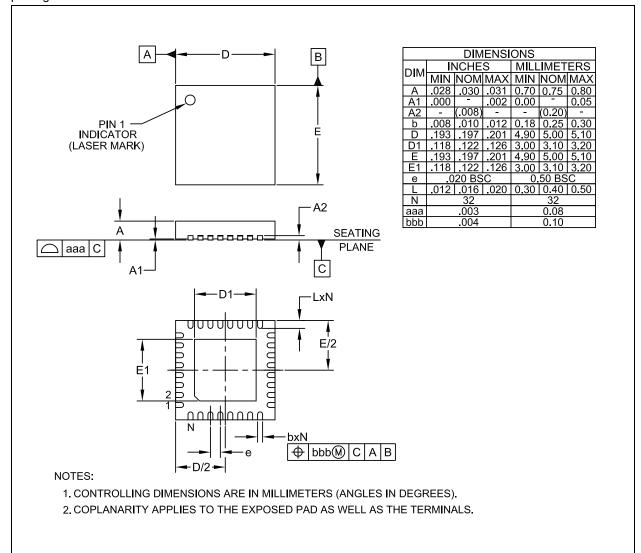

| Packaging Information                            | 129 |

| Appendix A: FSK and OOK RX Filters vs. Bit rates | 131 |

| Appendix B: CRC Computation in C                 | 132 |

| Appendix C: Revision History                     | 133 |

| The Microchip Web Site                           |     |

| Customer Change Notification Service             |     |

| Customer Support                                 |     |

| Product Identification System                    |     |

#### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- · Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

NOTES:

#### 1.0 OVERVIEW

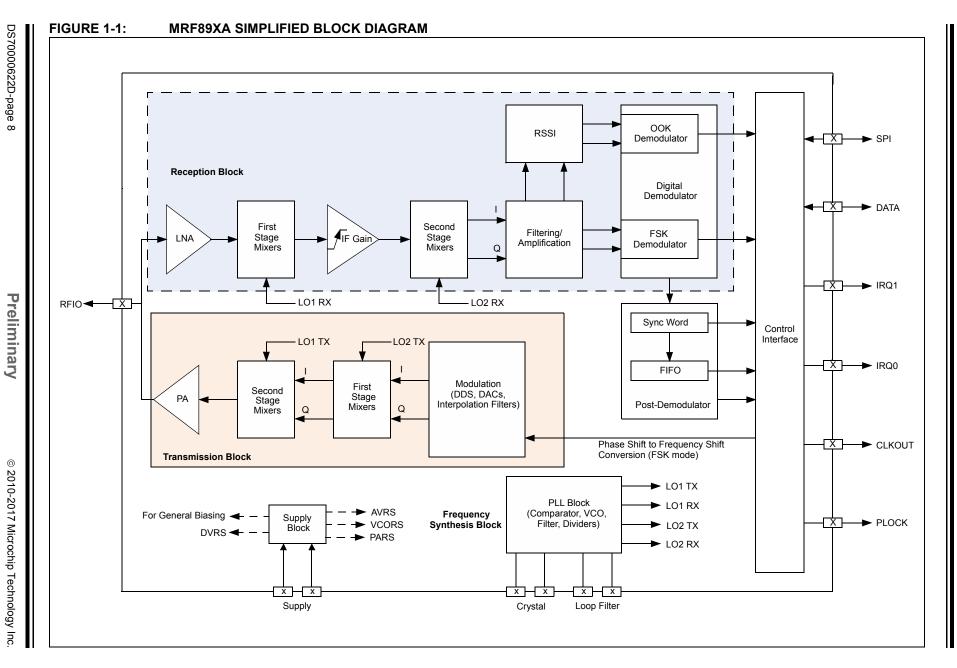

Microchip's MRF89XA is a fully integrated, half-duplex, sub-GHz transceiver. This low-power, single-chip FSK and OOK baseband transceiver supports:

- · Superheterodyne architecture

- Multi-channel, multi-band synthesizer with Phase Locked Loop (PLL) for easy RF design

- · Power Amplifier (PA)

- Low Noise Amplifier (LNA)

- · I/Q two stage down converter mixers

- I/Q demodulator, FSK/OOK

- · Baseband filters and amplifiers

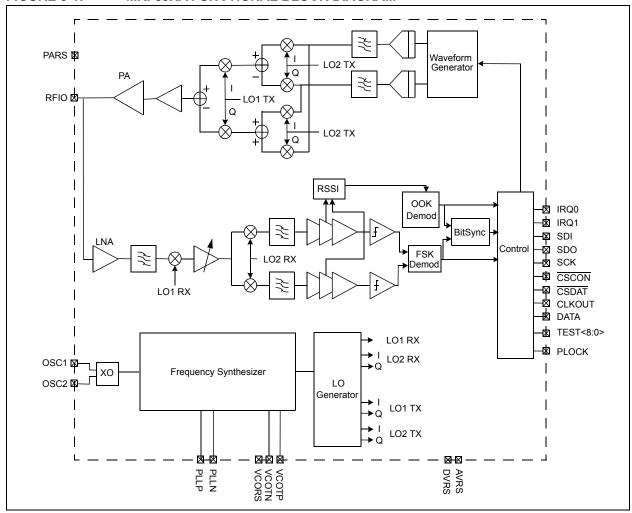

The simplified block diagram of the MRF89XA is illustrated in Figure 1-1.

The MRF89XA is a good option for low-cost, high-volume, low data rate (≤200 kbps), and two-way short-range wireless applications. This device is a single-chip FSK and OOK transceiver capable of operating in the 863-870 MHz and 902-928 MHz license-free ISM frequency bands, and the 950-960 MHz frequency band.

The low-cost MRF89XA is optimized for very low-power consumption (3 mA in Receive mode). It incorporates a baseband modem with data rates up to 200 kbps in FSK and 32 kbps in OOK. Data handling features include a 64-byte FIFO, packet handling, automatic CRC generation, and data whitening. The device also supports Manchester coding techniques. Its highly integrated architecture allows for minimum external component count while maintaining design flexibility. All major RF communication parameters are programmable and most of them may be dynamically set

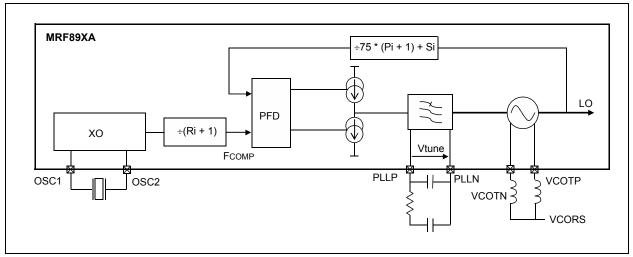

The MRF89XA supports a stable sensitivity and linearity characteristics for a wide supply range and is internally regulated. The frequency synthesizer of the MRF89XA is a fully integrated integer-N type PLL. The oscillator circuit provided on the MRF89XA device provides the reference clock for the PLL. The frequency synthesizer requires only five external components, which include the PLL loop filter and the VCO tank circuit. Low-phase noise provides for excellent adjacent channel rejection capability, Bit Error Rate (BER), and longer communication range.

The high-resolution PLL allows:

- · Usage of multiple channels in any of the bands

- Rapid settling time, which allows for faster frequency hopping

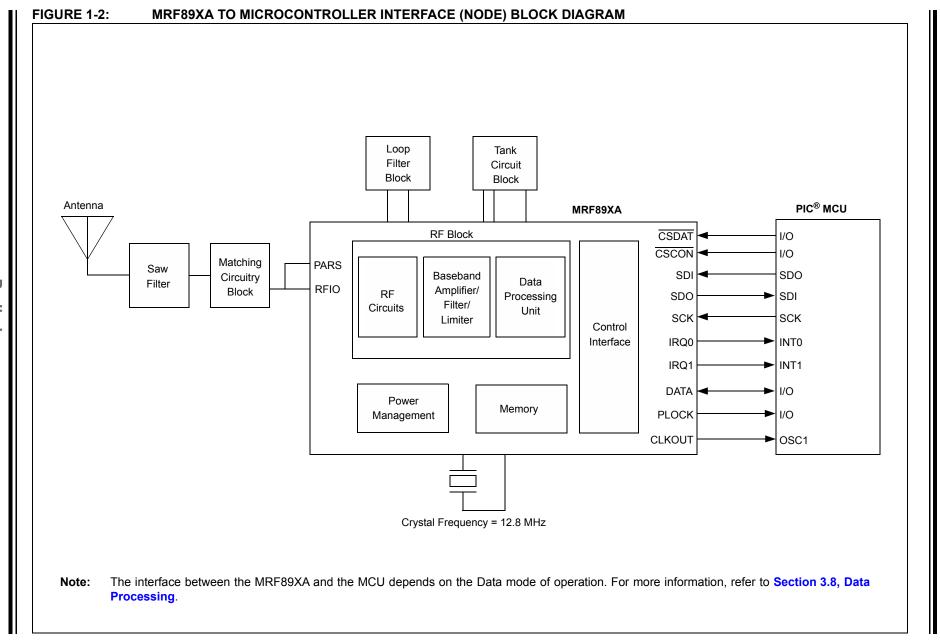

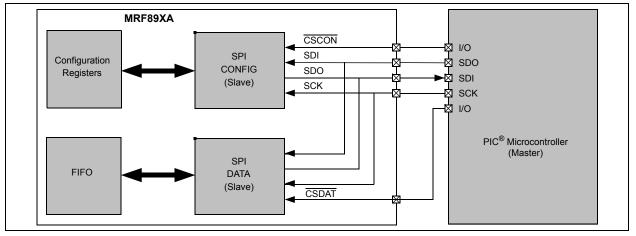

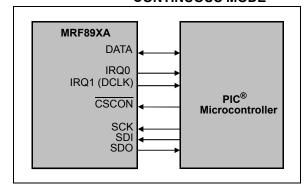

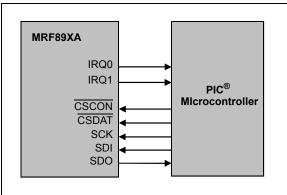

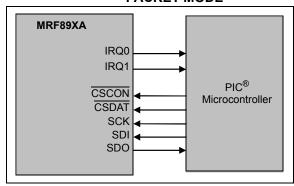

A communication link in most applications can be created using a low-cost 12.8 MHz crystal, a SAW filter, and a low-cost microcontroller. The MRF89XA provides a clock signal for the microcontroller. The transceiver can be interfaced with many popular Microchip PIC® microcontrollers through a 4-wire Serial Peripheral Interface (SPI), interrupts (IRQ0 and IRQ1), PLL lock, and clock out. The interface between the microcontroller and MRF89XA (a typical MRF89XA RF node) is illustrated in Figure 1-2.

The MRF89XA supports the following digital data processing features:

- · Received Signal Strength Indicator (RSSI)

- · Sync Word recognition

- · Packet handling

- · Interrupt and flags

- Different operating modes (Continuous, Buffered, and Packet)

- · Data filtering/whitening/encoding

- · Baseband power amplifier

- 64-byte TX/RX FIFO

The role of the digital processing unit is to interface the data to/from the modulator/demodulator and the microcontroller access points (SPI, IRQ and DATA pins). It also controls all of the Configuration registers. The receiver's Baseband Bandwidth (BBBW) can be programmed to accommodate various deviations and data rates requirements.

An optional Bit Synchronizer (BitSync) is provided, to supply a synchronous clock and data stream to a companion microcontroller in Continuous mode, or to fill the FIFO with glitch-free data in Buffered mode. The transceiver is integrated with different power-saving modes and a software wake-up time through the host microcontroller to keep track of the activities, which reduce the overall current consumption and extends the battery life. The small size and low-power consumption of the MRF89XA makes it ideal for various short-range radio applications.

The MRF89XA complies with European (ETSI EN 300-220) and United States (FCC Part 15.247 and 15.249) regulatory standards.

NOTES:

#### 2.0 HARDWARE DESCRIPTION

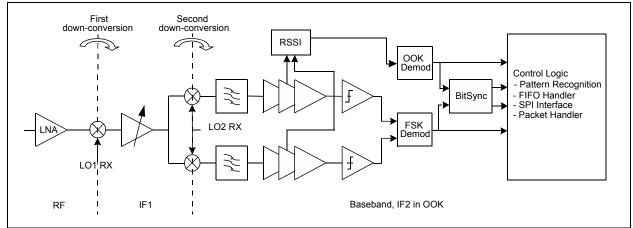

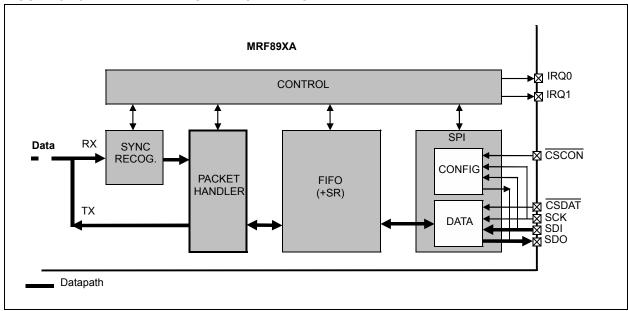

The MRF89XA is an integrated, single-chip, low-power ISM band sub-GHz transceiver. A detailed block diagram of the MRF89XA is illustrated in Figure 2-1. The frequency synthesizer is clocked by an external 12.8 MHz crystal, and frequency ranges from 863-870 MHz, 902-928 MHz, and 950-960 MHz are possible.

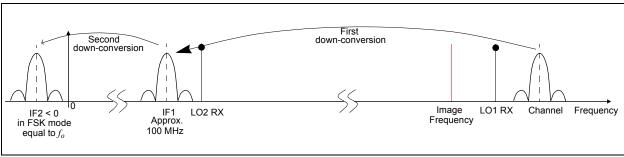

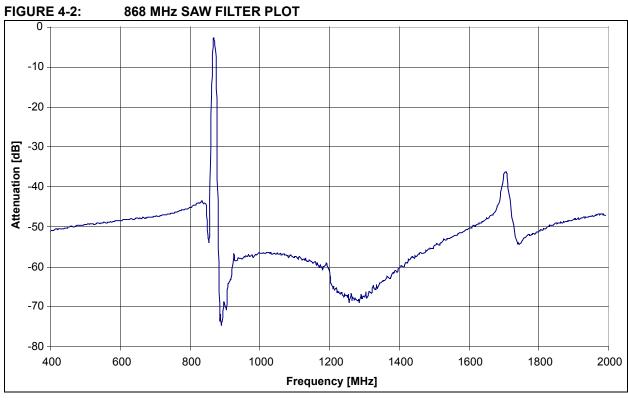

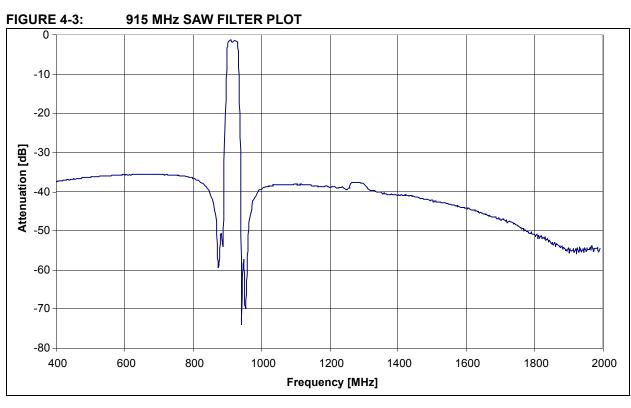

The MRF89XA receiver employs a superheterodyne architecture. The first IF is one-ninth of the RF frequency (approximately 100 MHz). The second down-conversion, down converts the I and Q signals to baseband in the case of the FSK receiver (zero-IF) and to a low-IF (IF2) for the OOK receiver. After the second down-conversion stage, the received signal is channel select filtered and amplified to a level adequate for demodulation. Both FSK and OOK demodulation are available. Image rejection is achieved using a SAW filter.

The baseband I and Q signals at the transmitter side are digitally generated by a Direct Digital Synthesis (DDS). whose Digital-to-Analog Converters (DAC) are followed by two anti-aliasing, low-pass filters that transform the digital signal into analog In-Phase (I) and Quadrature (Q) components with frequency as the selected Frequency Deviation ( $f_{dev}$ ). The transmitter supports both FSK and OOK modes of operation. The transmitter has a typical output power of +12.5 dBm. An internal transmit/receive switch combines the transmitter and receiver circuits into a single-ended RFIO pin (pin 31). The RFIO pin is connected through the impedance matching circuitry to an external antenna. The device operates in the low-voltage range of 2.1-3.6V, and in Sleep mode, it operates at a very low-current state, typically 0.1 µA.

The frequency synthesizer is based on an integer-N PLL having PLL bandwidth of 15 kHz. Two programmable frequency dividers in the feedback loop of the PLL and one programmable divider on the reference oscillator allow the LO frequency to be adjusted. The reference frequency is generated by a crystal oscillator running at 12.8 MHz.

The MRF89XA is controlled by a digital block that includes registers to store the configuration settings of the radio. These registers are accessed by a host microcontroller through a Serial Peripheral Interface (SPI). The quality of the data is validated using the RSSI and bit synchronizer blocks built into the transceiver. Data is buffered in a 64-byte transmitter or receiver FIFO. The transceiver is controlled through a 4-wire SPI, interrupts (IRQ0 and IRQ1), PLOCK, DATA, and Chip Select pins for SPI, which are illustrated in Figure 2-1. On-chip regulators provide stable supply voltages to sensitive blocks and allow the MRF89XA to be used with supply voltages from 2.1-3.6V. Most blocks are supplied with a voltage below 1.4V.

The MRF89XA supports the following feature blocks:

- · Data filtering and whitening

- · Bit synchronization

- · 64-byte transmit/receive FIFO buffer

- · General configuration registers

These features reduce the processing load, which allow the use of simple, low-cost, 8-bit microcontrollers for data processing.

PARS 🕸 Waveform Generator LO2 TX Q  $\approx$ RFIO 🗷 LO2 TX RSSI OOK Demod -⊠ IRQ0 -⊠ IRQ1 BitSync B SDI -⊠ SDO -⊠ SCK -⊠ CSCO Control FSK LO2 RX CSCON CSDAT CLKOUT LO1 RX CLKO

DATA LO1 RX TEST<8:0> LO2 RX OSC1 🖫

■ PLOCK Frequency Synthesizer ΧO OSC2 LO Generator → I → Q LO1 TX LO2 TX  $\boxtimes \boxtimes$ VCOTP VCOTN VCORS PLLN AVRS DVRS

FIGURE 2-1: DETAILED BLOCK DIAGRAM OF THE MRF89XA

TABLE 2-1: PIN DESCRIPTIONS

| Pin<br>Number | Pin Name | Pin Type       | Description                                                                                                                                                          |  |

|---------------|----------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1             | TEST5    | Digital I/O    | Test Pin. Connected to Ground during normal operation.                                                                                                               |  |

| 2             | TEST1    | Digital I/O    | Test Pin. Connected to Ground during normal operation.                                                                                                               |  |

| 3             | VCORS    | Analog Output  | Regulated voltage supply of the VCO (0.85V).                                                                                                                         |  |

| 4             | VCOTN    | Analog I/O     | VCO tank.                                                                                                                                                            |  |

| 5             | VCOTP    | Analog I/O     | VCO tank.                                                                                                                                                            |  |

| 6             | PLLN     | Analog I/O     | PLL loop filter.                                                                                                                                                     |  |

| 7             | PLLP     | Analog I/O     | PLL loop filter.                                                                                                                                                     |  |

| 8             | TEST6    | Digital I/O    | Test Pin. Connected to Ground during normal operation.                                                                                                               |  |

| 9             | TEST7    | Digital I/O    | Test Pin. Connected to Ground during normal operation.                                                                                                               |  |

| 10            | OSC1     | Analog Input   | Crystal connection.                                                                                                                                                  |  |

| 11            | OSC2     | Analog Input   | Crystal connection.                                                                                                                                                  |  |

| 12            | TEST0    | Digital Input  | Test Pin. Connected to Ground during normal operation.                                                                                                               |  |

| 13            | TEST8    | Digital I/O    | Test Pin. Allow pin to float; do not connect signal during normal operation.                                                                                         |  |

| 14            | CSCON    | Digital Input  | SPI Configure Chip Select.                                                                                                                                           |  |

| 15            | CSDAT    | Digital Input  | SPI Data Chip Select.                                                                                                                                                |  |

| 16            | SDO      | Digital Output | Serial data output interface from MRF89XA.                                                                                                                           |  |

| 17            | SDI      | Digital Input  | Serial data input interface to MRF89XA.                                                                                                                              |  |

| 18            | SCK      | Digital Input  | Serial clock interface.                                                                                                                                              |  |

| 19            | CLKOUT   | Digital Output | Clock output. Output clock at reference frequency divided by a programmable factor. Refer to the Clock Output Control Register (Register 2-28) for more information. |  |

| 20            | DATA     | Digital I/O    | NRZ data input and output (Continuous mode).                                                                                                                         |  |

| 21            | IRQ0     | Digital Output | Interrupt request output.                                                                                                                                            |  |

| 22            | IRQ1     | Digital Output | Interrupt request output.                                                                                                                                            |  |

| 23            | PLOCK    | Digital Output | PLL lock detection output. Refer to the FIFO Transmit PLL and RSSI Interrupt Request Configuration Register (Register 2-15) for more information.                    |  |

| 24            | TEST2    | Digital I/O    | Test Pin. Connected to Ground during normal operation.                                                                                                               |  |

| 25            | TEST3    | Digital I/O    | Test Pin. Connected to Ground during normal operation.                                                                                                               |  |

| 26            | VDD      | Power          | Supply voltage.                                                                                                                                                      |  |

| 27            | AVRS     | Analog Output  | Regulated supply of the analog circuitry (1.0V).                                                                                                                     |  |

| 28            | DVRS     | Analog Output  | Regulated supply of the digital circuitry (1.0V).                                                                                                                    |  |

| 29            | PARS     | Analog Output  | Regulated supply of the PA (1.8V).                                                                                                                                   |  |

| 30            | TEST4    | Digital I/O    | Test Pin. Connected to Ground during normal operation.                                                                                                               |  |

| 31            | RFIO     | Analog I/O     | RF input/output (for more information, see Section 2.3, RFIO Pin).                                                                                                   |  |

| 32            | NC       |                | No Connection. Connected to Ground during normal operation.                                                                                                          |  |

| 33            | Vss      | Ground         | Exposed Pad. Connected to Ground during normal operation.                                                                                                            |  |

### 2.1 Power Supply and Ground Block Pins

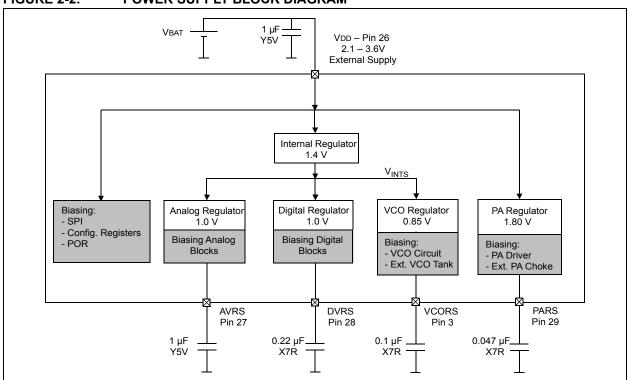

To provide stable sensitivity and linearity characteristics over a wide supply range, the MRF89XA is internally voltage regulated. This internal regulated power supply block structure is illustrated in Figure 2-2.

The power supply bypassing is essential for better handling of signal surges and noise in the power line. To ensure correct operation of the regulator circuit, the decoupling capacitor connection (shown in Figure 2-2) is recommended. These decoupling components are recommended for any design. The power supply block generates four regulated supplies for the analog, digital, VCO, and the PLL blocks to reduce the voltages for their specific requirements. However, Power-on Reset (POR), Configuration registers, and the SPI use the VDD supply given to the MRF89XA.

The large value decoupling capacitors should be placed at the PCB power input. The smaller value decoupling capacitors should be placed at every power point of the device and at bias points for the RF port. Poor bypassing can lead to conducted interference, which can cause noise and spurious signals to couple into the RF sections, thereby significantly reducing the performance.

It is recommended that the VDD pin have two bypass capacitors to ensure sufficient bypass and decoupling. However, based on the selected carrier frequency, the bypass capacitor values vary. The trace length (VDD pin to bypass capacitors) should be made as short as possible.

FIGURE 2-2: POWER SUPPLY BLOCK DIAGRAM

TABLE 2-2: POWER SUPPLY PIN DETAILS

| Blocks                               | Biasing Through | Associated Pins | Regulated Voltage<br>(in Volts) |

|--------------------------------------|-----------------|-----------------|---------------------------------|

| POR, SPI and Configuration Registers | VDD             | VDD             | 2.1–3.6                         |

| Regulated Supply (VINTS)             | VDD             | VDD             | 1.4                             |

| Analog                               | VINTS           | AVRS            | 1.0                             |

| Digital                              | VINTS           | DVRS            | 1.0                             |

| VCO                                  | VINTS           | VCORS           | 0.85                            |

| PA                                   | VDD             | PARS            | 1.8                             |

#### 2.2 Reset Pin

The device enters the Reset mode if any of the following events takes place:

- · Power-on Reset (POR)

- · Manual Reset

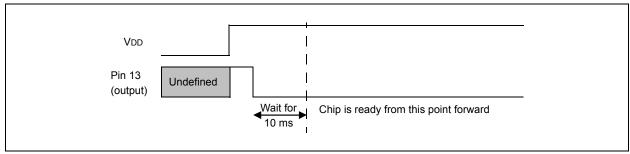

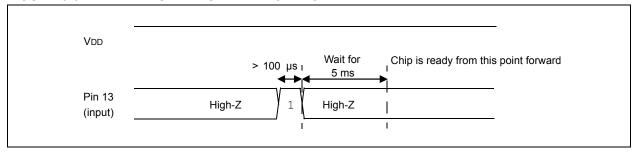

The POR happens when the MRF89XA is switched on using VDD. The POR cycle takes at least 10 ms to execute any communication operations on the SPI bus.

An external hardware or manual Reset of the MRF89XA can be performed by asserting the TEST8 pin (pin 13) to high for 100  $\mu$ s and then releasing the pin. After releasing the pin, it takes more than 5 ms for the transceiver to be ready for any operations. The reset pin is driven with an open-drain output; therefore, is pulled high while the device is in POR. The device does not accept commands during the Reset period. For more information, refer to **Section 3.1.2, Manual Reset**.

#### 2.3 RFIO Pin

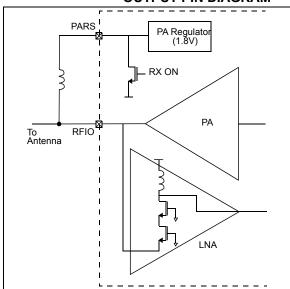

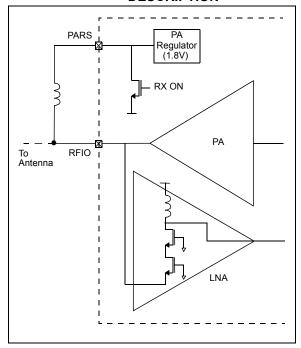

The receiver and the transmitter share the same RFIO pin (pin 31). Figure 2-3 illustrates the configuration of the common RF front-end.

- In Transmit mode, the PA and the PA regulator are ON with voltage on the PARS pin (pin 29) equal to the nominal voltage of the regulator (about 1.8V). The external RF choke inductance is used to bias the PA.

- In Receive mode, the PA and PA regulator are OFF and PARS is tied to the ground. The external RF choke inductor is used for biasing and matching the LNA (this is implemented as a common gate amplifier).

FIGURE 2-3: COMMON RF INPUT AND OUTPUT PIN DIAGRAM

The PA and the LNA front-ends in the MRF89XA, which share the same Input/Output pin, are internally matched to approximately  $50\Omega$ .

#### 2.4 Filters and Amplifiers Block

#### 2.4.1 INTERPOLATION FILTER

After the digital-to-analog conversion during transmission, both I and Q signals are smoothened by interpolation filters. These interpolation filters perform low pass filtering of the digitally generated signal and prevent the alias signals from entering the modulators.

#### 2.4.2 POWER AMPLIFIER

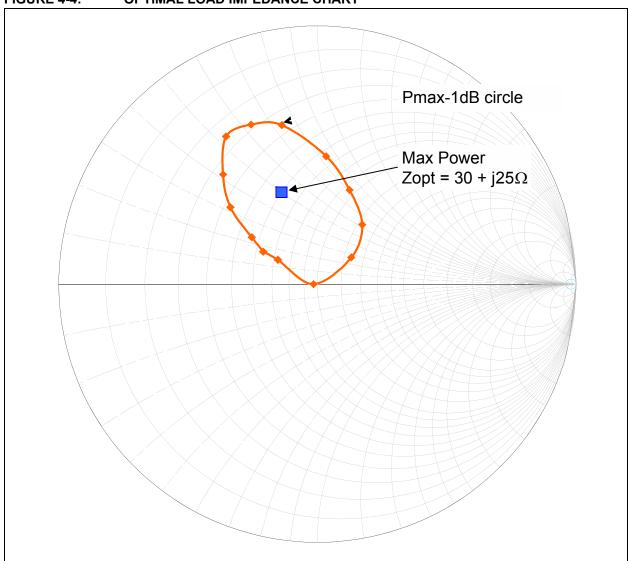

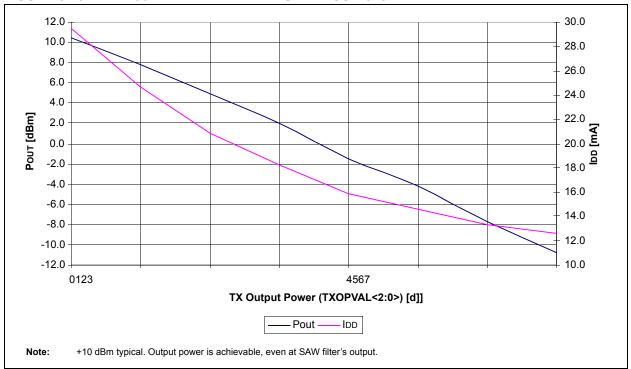

The Power Amplifier (PA) integrated in the MRF89XA operates under a regulated voltage supply of 1.8V. The external RF choke inductor is biased by an internal regulator output made available on the PARS pin (pin 29). Therefore, the PA output power is consistent over the power supply range. The consistency in operation is important for applications which allows both predictable RF performance and battery life.

An open collector output requires biasing using an inductor as an RF choke. For the recommended PA bias and matching circuit details see **Section 4.5.2**, **Suggested PA Biasing And Matching**.

**Note:** Image rejection is achieved using a SAW filter on the RF input.

The matching of the SAW filter depends on the SAW filter selected. Many modern SAW filters have  $50\Omega$  input and output, which simplifies matching for the MRF89XA. This is demonstrated in the application circuit. If the choice of SAW filter is different than  $50\Omega,$  the required impedance match on the input and output of the SAW filter is needed.

## 2.4.3 LOW NOISE AMPLIFIER (WITH FIRST MIXER)

In Receive mode, the RFIO pin (pin 31) is connected to a fixed-gain, common-gate, Low Noise Amplifier (LNA). The performance of this amplifier is such that the Noise Figure (NF) of the receiver is estimated to be approximately 7 dB.

The LNA has approximately  $50\Omega$  impedance, which functions well with the proposed antenna (PCB/ Monopole) during signal transmission. The LNA is followed by an internal RF band-pass filter.

#### 2.4.4 IF GAIN AND SECOND I/Q MIXER

Following the LNA and first down-conversion, there is an IF amplifier whose gain can be programmed from 13.5-0 dB in 4.5 dB steps, through the register DMODREG. For more information, refer to Section 2.14.2, Data And Modulation Configuration Register Details. The default setting corresponds to 0 dB gain, but lower values can be used to increase the RSSI dynamic range.

#### 2.4.5 CHANNEL FILTERS

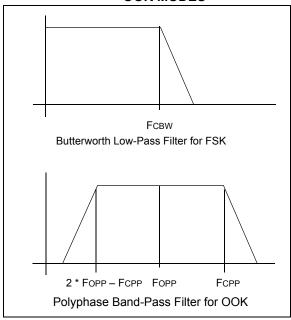

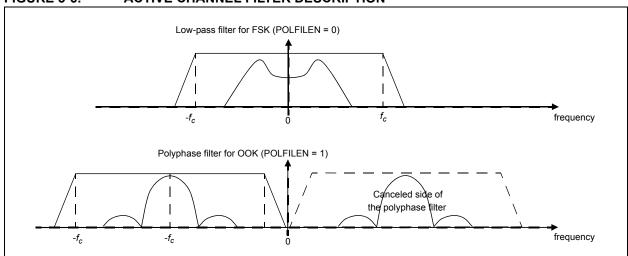

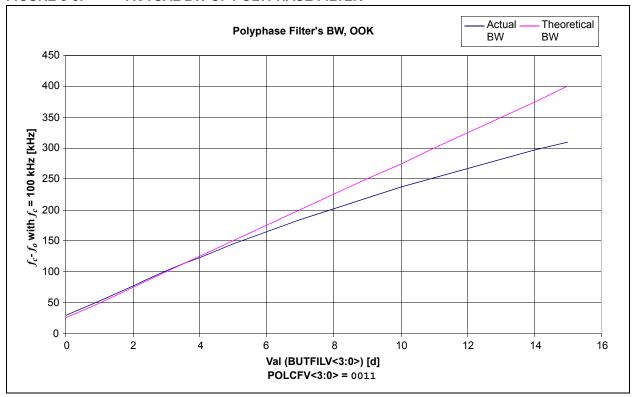

The second mixer stages are followed by the channel select filters. The channel select filters have a strong influence on the noise bandwidth and selectivity of the receiver, and therefore, its sensitivity. Each channel select filter features a passive second-order RC filter, with a programmable bandwidth, and the "fine" channel selection is performed by an active, third-order, Butterworth filter, which acts as a low-pass filter for the zero-IF configuration (FSK), or a complex polyphase filter for the low-IF (OOK) configuration. For more information on configuring passive and active filters see Section 3.4.4, Channel Filters.

#### 2.5 Frequency Synthesizer Block

The frequency synthesizer of the MRF89XA is a fully integrated integer-N type PLL. The crystal oscillator provides the reference frequency for the PLL. The PLL circuit requires only a minimum of five external components for the PLL loop filter and the VCO tank circuit.

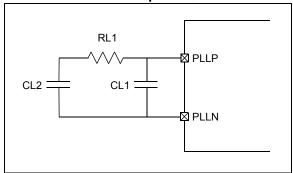

Figure 2-4 illustrates a block schematic of the MRF89XA PLL. The crystal reference frequency and the software controlled dividers R, P, and S blocks determine the output frequency of the PLL.

The VCO tank inductors are connected to an external differential input. Similarly, the loop filter is also located externally.

FIGURE 2-4: FREQUENCY SYNTHESIZER BLOCK DIAGRAM

### 2.5.1 REFERENCE OSCILLATOR PINS (OSC1/OSC2)

The MRF89XA has an internal, integrated oscillator circuit, and the OSC1 and OSC2 pins are used to connect to an external crystal resonator. The crystal oscillator provides the reference frequency for the PLL. The crystal oscillator circuit, with the required loading capacitors, provides a 12.8-MHz reference signal for the PLL. The PLL then generates the local oscillator frequency. It is possible to "pull" the crystal to the accurate frequency by changing the load capacitor value. The crystal oscillator load capacitance is typically 15 pF, which allows the crystal oscillator circuit to accept a wide range of crystals.

Choosing a higher tolerance crystal results in a lower TX to RX frequency offset and the ability to select a smaller deviation in baseband bandwidth. Therefore, the recommended crystal accuracy should be  $\leq 40$  ppm. The guidelines for selecting the appropriate crystal with specifications are explained in Section 4.7, Crystal Specification and Selection Guidelines.

**Note:** Crystal frequency error directly translates to carrier frequency (f<sub>rf</sub>), bit rate, and frequency deviation error.

#### 2.5.2 CLKOUT OUTPUT PIN (CLKOUT)

The transceiver can provide a clock signal through the CLKOUT pin (pin 19) to the microcontroller for accurate timing, thereby eliminating the need for a second crystal. This results in reducing the component count. The CLKOUT is a sub-multiple of the reference frequency and is programmable.

The two main functions of the CLKOUT output are:

- To provide a clock output for a host microcontroller, thus saving the cost of an additional oscillator.

- To provide an oscillator reference output. Measurement of the CLKOUT signal enables simple software trimming of the initial crystal tolerance.

**Note:** To minimize the current consumption of the MRF89XA, ensure that the CLKOUT signal is disabled when unused.

CLKOUT can be made available in any operation mode, except Sleep mode, and is automatically enabled at power-up.

### 2.5.3 PHASE-LOCKED LOOP ARCHITECTURE

The Integer-N Phase-Locked Loop (PLL) circuitry determines the operating frequency of the device. The PLL maintains accuracy using the crystal-controlled reference oscillator and provides maximum flexibility in performance to the designers.

The high resolution of the PLL allows the use of multiple channels in any of the bands. The on-chip PLL is capable of performing manual and automatic calibration to compensate for the changes in temperature or operating voltage.

#### 2.5.3.1 PLL Lock Pin (PLOCK)

The MRF89XA features a PLL lock (PLOCK) detect indicator. This is useful for optimizing power consumption by adjusting the synthesizer wake-up time. The lock status can also be read on the LSTSPLL bit from the FTPRIREG register (Register 2-15), and must be cleared by writing a '1' to this same register. The lock status is available on the PLOCK pin (pin 23) by setting the LENPLL bit in the FTPRIREG register.

### 2.5.4 VOLTAGE CONTROLLED OSCILLATOR

The integrated Voltage Controlled Oscillator (VCO) requires two external tank circuit inductors. As the input is differential, the two inductors must have the same nominal value. The performance of these components is essential for both the phase noise and the power consumption of the PLL. It is recommended that a pair of high Q inductors is selected. These should be mounted orthogonally to other inductors in the circuit (in particular the PA choke) to reduce spurious coupling between the PA and the VCO. For best performance, wire wound high-Q inductors with tight tolerance should be used as described in Section 4.0, Application Details. In addition, such measures may reduce radiated pulling effects and undesirable transient behavior, thus minimizing spectral occupancy.

**Note:** Ensuring a symmetrical layout of VCO inductors further improves the PLL spectral purity.

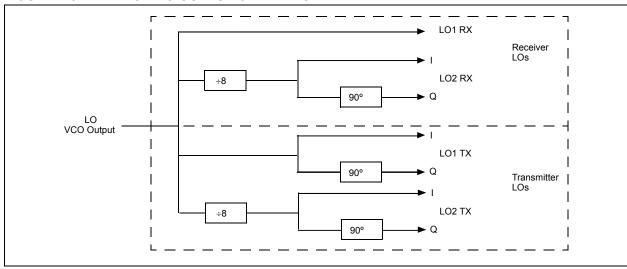

The output signal of the VCO is used as the input to the local oscillator (LO) generator stage, as illustrated in Figure 2-5. The VCO frequency is subdivided and used in a series of up or down conversions for transmission or reception.

FIGURE 2-5: LO VCO OUTPUT GENERATOR

### 2.6 MRF89XA Operating Modes (Includes Power-Saving Mode)

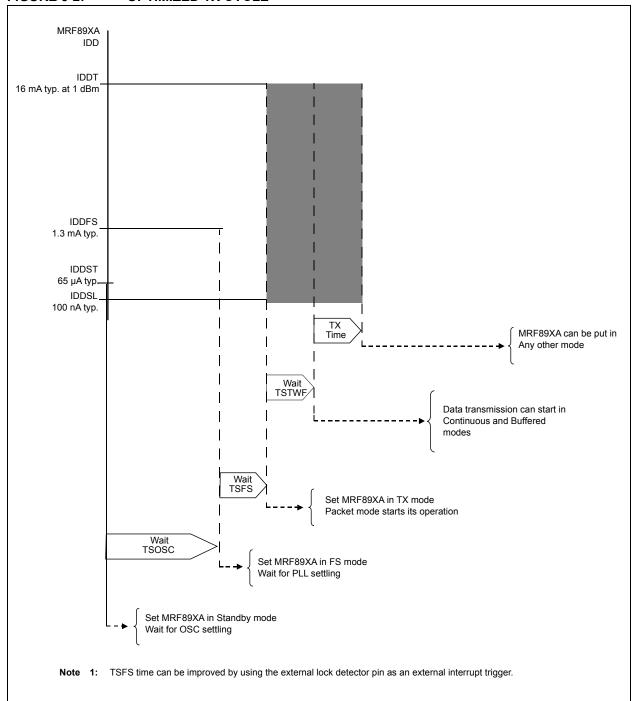

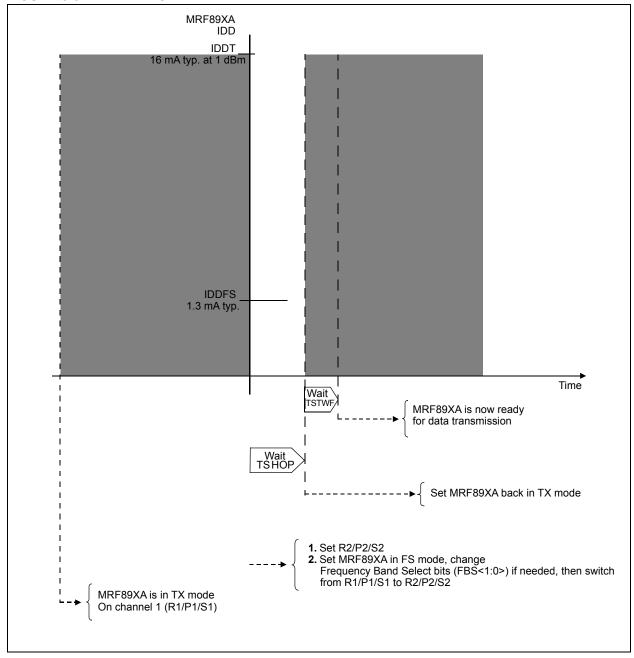

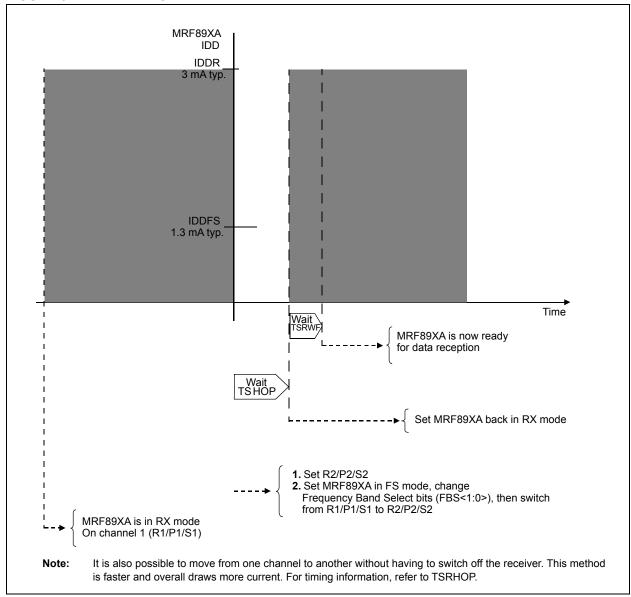

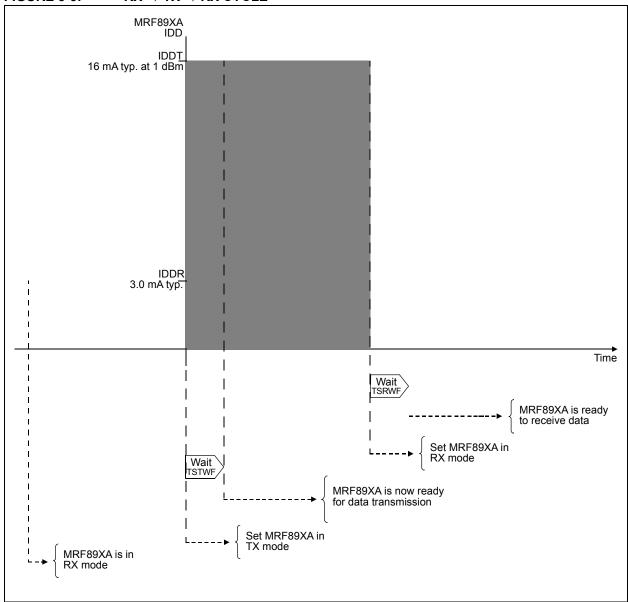

This section summarizes the settings for each operating mode of the MRF89XA to save power, which are based on the operations and available functionality. The timing requirements for switching between modes are described in Section 5.3, Switching Times and Procedures.

#### 2.6.1 MODES OF OPERATION

Table 2-3 lists the different operating modes of the MRF89XA that can be used to save power.

### 2.6.2 DIGITAL PIN CONFIGURATION VS. CHIP MODE

Table 2-4 lists the state of the digital I/Os in each of the above described modes of operation, regardless of the data operating mode (Continuous, Buffered, or Packet).

TABLE 2-3: OPERATING MODES

| Mode     | CMOD<2:0> bits<br>(GCONREG<7:5> | Active Blocks                                                                                                                                                                                     |

|----------|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Sleep    | 000                             | SPI, POR.                                                                                                                                                                                         |

| Standby  | 001                             | SPI, POR, Top regulator, digital regulator, XO, CLKOUT (if activated through CLKOREG).                                                                                                            |

| FS       | 010                             | Same as Standby + VCO regulator, all PLL and LO generation blocks.                                                                                                                                |

| Receive  | 011                             | Same as FS mode + LNA, first mixer, IF amplifier, second mixer set, channel filters, baseband amplifiers and limiters, RSSI, OOK or FSK demodulator, BitSync and all digital features if enabled. |

| Transmit | 100                             | Same as FS mode + DDS, Interpolation filters, all up-conversion mixers, PA driver, PA and external PARS pin (pin 29) output for the PA choke.                                                     |

TABLE 2-4: PIN CONFIGURATION VS. CHIP MODE

| Chip Mode<br>Pin    | Sleep<br>Mode | Standby<br>Mode       | FS Mode               | Receive<br>Mode       | Transmit<br>Mode      | Comment                                                                     |

|---------------------|---------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------------------------------------------------------------|

| CSCON               | Input         | Input                 | Input                 | Input                 | Input                 | CSCON has priority over CSDAT.                                              |

| CSDAT               | Input         | Input                 | Input                 | Input                 | Input                 | _                                                                           |

| SDO <sup>(4)</sup>  | Output        | Output                | Output                | Output                | Output                | Output only if $\overline{\text{CSCON}}$ or $\overline{\text{CSDAT}} = 0$ . |

| SDI                 | Input         | Input                 | Input                 | Input                 | Input                 | _                                                                           |

| SCK                 | Input         | Input                 | Input                 | Input                 | Input                 | _                                                                           |

| IRQ0 <sup>(3)</sup> | High-Z        | Output <sup>(1)</sup> | Output <sup>(1)</sup> | Output                | Output                | _                                                                           |

| IRQ1 <sup>(3)</sup> | High-Z        | Output <sup>(1)</sup> | Output <sup>(1)</sup> | Output                | Output                | _                                                                           |

| DATA                | Input         | Input                 | Input                 | Output                | Input                 | _                                                                           |

| CLKOUT              | High-Z        | Output                | Output                | Output                | Output                | _                                                                           |

| PLOCK               | High-Z        | Output <sup>(2)</sup> | Output <sup>(2)</sup> | Output <sup>(2)</sup> | Output <sup>(2)</sup> | _                                                                           |

- Note 1: High-Z if Continuous mode is activated; otherwise, Output.

- 2: Output if LENPLL = 1; otherwise, High-Z.

- **3:** Valid logic states must be applied to inputs at all times to avoid unwanted leakage currents. Suggestions for designers to:

- · Use external pull down resistor.

- Tri-state the microcontroller interrupt pin to output when setting the MRF89XA to sleep, then reverse

when waking it up. Since the microcontroller is in control, this should be easy to do and not require

an external pull down resistor.

- **4:** The SDO pin defaults to a high impedance (High-Z) state when any of the CS pins is high (the MRF89XA is not selected).

#### 2.7 Interrupt (IRQ0 and IRQ1) Pins

The Interrupt Requests (IRQ0 and IRQ1) pins 21 and 22 provide an interrupt signal to the host microcontroller from the MRF89XA. Interrupt requests are generated for the host microcontroller by pulling the IRQ0 (pin 21) or IRQ1 (pin 22) pin low or high based on the events and configuration settings of these interrupts. Interrupts must be enabled and unmasked before the IRQ pins are active. For detailed functional description of interrupts, see Section 3.8, Data Processing.

#### 2.8 DATA Pin

After OOK or FSK demodulation, the baseband signal is available to the user on the DATA pin (pin 20), when Continuous mode is selected. Therefore, in Continuous mode, the host microcontroller directly accesses the NRZ data to or from the modulator or demodulator, respectively, on the bidirectional DATA pin. The SPI Data, FIFO, and packet handler are therefore inactive. In Buffered and Packet modes, the data is retrieved from the FIFO through the SPI.

During transmission, the DATA pin is configured as DATA (Data Out) and with the internal Transmit mode disabled; this manually modulates the data from the external host microcontroller. If the Transmit mode is enabled, this pin can be tied "high" or can be left unconnected.

During reception, the DATA pin is configured as DATA (Data In); this pin receives the data in conjunction with DCLK. The DATA pin (unused in packed mode) should be pulled up to VDD through a 100 k $\Omega$  resistor.

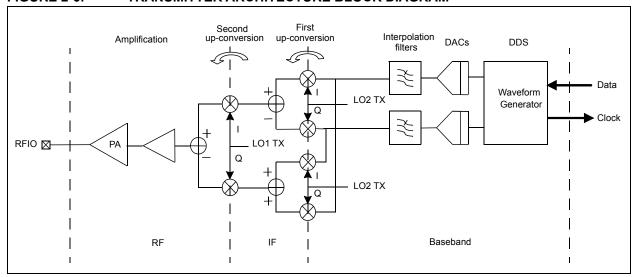

#### 2.9 Transmitter

The transmitter chain is based on the same doubleconversion architecture and uses the same intermediate frequencies as the receiver chain. The main blocks include:

- A digital waveform generator that provides the I and Q baseband signals. This block includes digital-to-analog converters and anti-aliasing lowpass filters.

- A compound image-rejection mixer to up-convert the baseband signal to the first IF at one-ninth of the carrier frequency (f<sub>rf</sub>), and a second image-rejection mixer to up-convert the IF signal to the RF frequency transmitter driver and power amplifier stages to drive the antenna port.

FIGURE 2-6: TRANSMITTER ARCHITECTURE BLOCK DIAGRAM

#### 2.9.1 TRANSMITTER ARCHITECTURE

Figure 2-6 illustrates the transmitter architecture block diagram. The baseband I and Q signals are digitally generated by a DDS whose Digital-to-Analog Converters (DAC) followed by two anti-aliasing low-pass filters transform the digital signal into analog in-phase (I) and quadrature (Q) components whose frequency is the selected frequency deviation, and is set using the FDVAL<7:0> bits from FDEVREG<7:0>.

In FSK mode, the input data switches the relative phase of I and Q between -90° and +90° with continuous phase. The modulation is therefore performed at this initial stage, because the information contained in the phase difference is converted into a frequency shift when the I and Q signals are up-converted in the first mixer stage. This first up-conversion stage is duplicated to enhance image rejection. The FSK convention is such that:

$$DATA = 1 \rightarrow f_{rf} + f_{dev}$$

$DATA = 0 \rightarrow f_{rf} - f_{dev}$

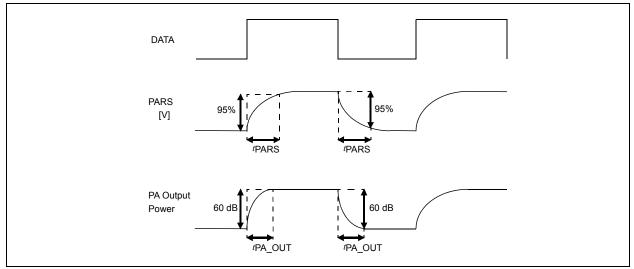

In OOK mode, the phase difference between the I and Q channels is kept constant (independent of the transmitted data). Thus, the first stage of up-conversion creates a fixed frequency signal at the low IF =  $f_{dev}$  (this explains why the transmitted OOK spectrum is offset by  $f_{dev}$ ). OOK Modulation is accomplished by switching the PA and PA regulator stages ON and OFF. By convention:

$$DATA = 1 \rightarrow PAon$$

$DATA = 0 \rightarrow PAoff$

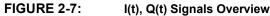

After the interpolation filters, a set of four mixers combines the I and Q signals and converts them into a pair of complex signals at the second intermediate frequency, equal to one-eighth of the LO frequency, or one-ninth of the RF frequency. These two new I and Q signals are then combined and up-converted to the final RF frequency by two quadrature mixers fed by the LO signal. The signal is pre-amplified, and then the transmitter output is driven by a final power amplifier stage. The I and Q signal details are illustrated in Figure 2-7.

#### 2.10 Receiver

The receiver is based on a superheterodyne architecture and comprises the following major blocks:

- An LNA that provides a low-noise RF gain followed by an RF band-pass filter.

- A first mixer, which down-converts the RF signal to an intermediate frequency equal to one-ninth of the carrier frequency (f<sub>rf</sub> 100 MHz for 915 MHz signals).

- A variable gain first-IF preamplifier followed by two second mixers, which down-convert the first IF signal to I and Q signals at a low frequency (zero-IF for FSK, low-IF for OOK).

- A two-stage IF filter followed by an amplifier chain is available for both I and Q channels. Limiters at the end of each chain drive the I and Q inputs to the FSK demodulator function. An RSSI signal is also derived from the I and Q IF amplifiers to drive the OOK detector. The second filter stage in each channel can be configured as either a third-order Butterworth low-pass filter for FSK operation or an image reject polyphase band-pass filter for OOK operation.

- An FSK arctangent type demodulator driven from the I and Q limiter outputs, and an OOK demodulator driven by the RSSI signal. Either detector can drive a data and clock recovery function that provides matched filter enhancement of the demodulated data.

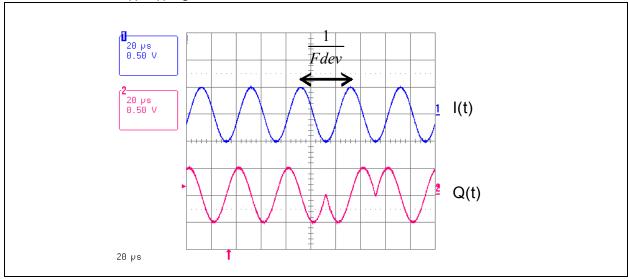

#### 2.10.1 RECEIVER ARCHITECTURE

Figure 2-8 illustrates the receiver architecture block diagram. The first IF is one-ninth of the RF frequency (approximately 100 MHz). The second down-conversion down-converts the I and Q signals to baseband in the case of the FSK receiver (zero-IF) and to a low-IF (IF2) for the OOK receiver.

After the second down-conversion stage, the received signal is channel-select filtered and amplified to a level adequate for demodulation. Both FSK and OOK demodulation are available. Finally, an optional bit synchronizer (BitSync) is provided to supply a synchronous clock and data stream to a companion microcontroller in Continuous mode, or to fill the FIFO buffers with glitch-free data in Buffered mode.

**Note:** Image rejection is achieved using a SAW filter on the RF input.

#### FIGURE 2-8: RECEIVER ARCHITECTURE BLOCK DIAGRAM

#### FIGURE 2-9: FSK RECEIVER SETTING

#### FIGURE 2-10: OOK RECEIVER SETTING

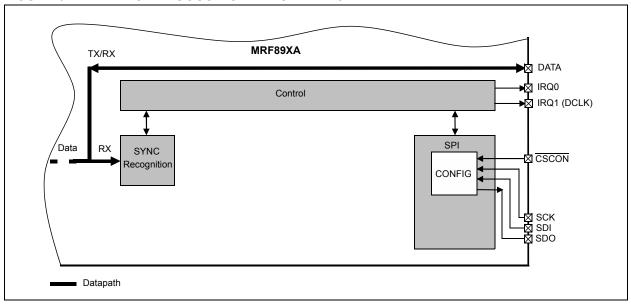

#### 2.11 Serial Peripheral Interface (SPI)

The MRF89XA communicates with the host microcontroller through a 4-wire SPI port as a slave device. An SPI-compatible serial interface allows the user to select, command, and monitor the status of the MRF89XA through the host microcontroller. All the registers are addressed through the specific addresses to control, configure, and read status bytes.

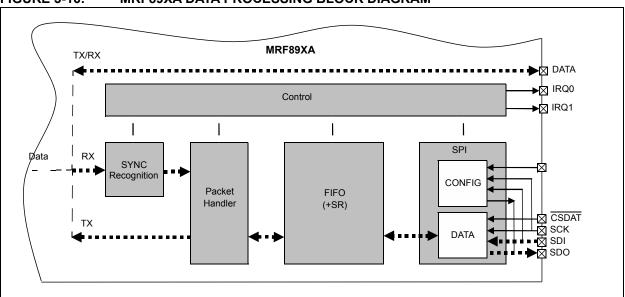

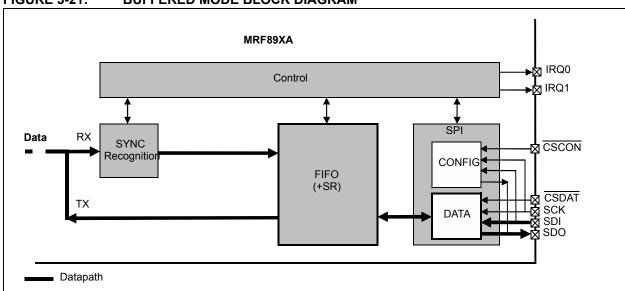

The SPI in the MRF89XA consists of the following two sub-blocks, as illustrated in Figure 2-11:

- SPI CONFIG: This sub-block is used in all data operation modes to read and write the configuration registers which control all the parameters of the chip (operating mode, frequency, and bit rate).

- SPI DATA: This sub-block is used in Buffered and Packet mode to write and read data bytes to and from the FIFO. (FIFO Interrupts can be used to manage the FIFO content).

Both of these SPIs are configured in Slave mode while the host microcontroller is configured as the master. They have separate selection pins (CSCON and CSDAT) but share the remaining pins:

- SCK (SPI Clock): Clock signal provided by the host microcontroller

- SDI (SPI Input): Data Input signal provided by the host microcontroller

- SDO (SPI Output): Data Output signal provided by the MRF89XA

As listed in Table 2-5, only one interface can be selected at a time, with CSCON having the priority:

TABLE 2-5: CONFIG VS. DATA SPI SELECTION

| CSDAT | CSCON | SPI    |

|-------|-------|--------|

| 0     | 0     | CONFIG |

| 0     | 1     | DATA   |

| 1     | 0     | CONFIG |

| 1     | 1     | None   |

All the parameters can be programmed and set through the SPI module. Any of these auxiliary functions can be disabled when it is not required. After power-on, all parameters are set to default values. The programmed values are retained during Sleep mode. The interface supports the read out of a status register, which provides detailed information about the status of the transceiver and the received data.

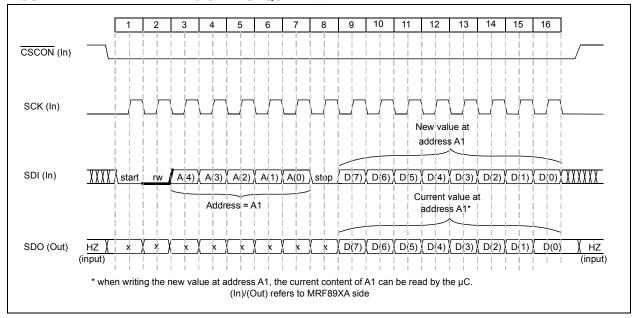

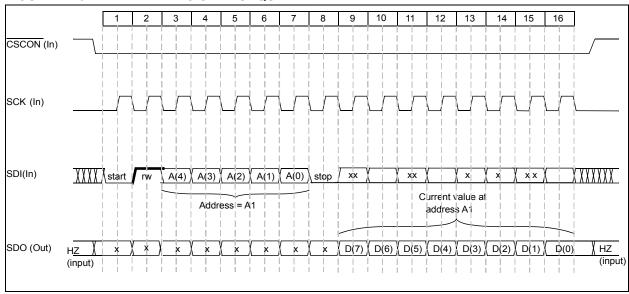

The MRF89XA supports SPI mode 0,0, which requires the SCK to remain idle in a low state. The CS pins, CSCON and CSDAT based on the mode (pin 14 and 15), must be held low to enable communication between the host microcontroller and the MRF89XA. The device's timing specification details are listed in Table 5-7. The SDO pin defaults to a high impedance (hi-Z) state when any of the CS pins is high (the MRF89XA is not selected). This pin has a tri-state buffer and uses a bus hold logic.

As the device uses byte writes, any of the Chip Select (CS) pins should be pulled low for 8 bits. Data bits on the SDI pin (pin 17) are shifted into the device upon the rising edge of the clock on the SCK pin (pin 18) whenever the CS pins are low. The maximum clock frequency for the SPI clock for CONFIG mode is 6 MHz. However, the maximum SPI Clock for DATA mode (to read/write FIFO) is 1 MHz. Data is received by the transceiver through the SDI pin and is clocked on the rising edge of SCK. The MRF89XA sends the data through the SDO pin and is clocked out on the falling edge of SCK. The Most Significant bit (MSb) is sent first in any data.

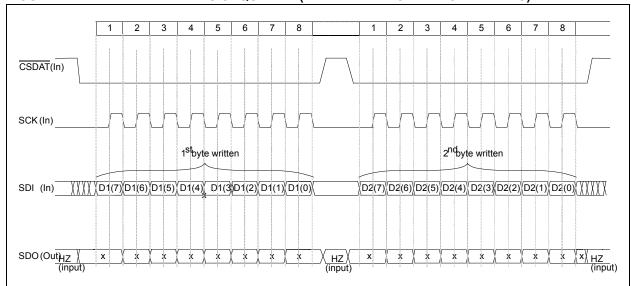

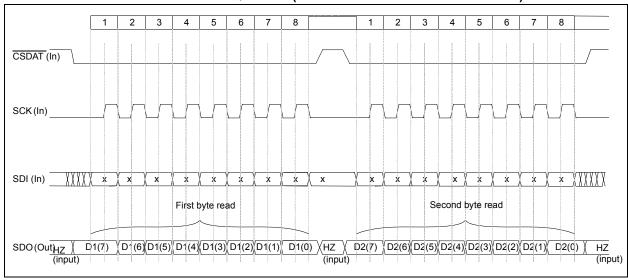

The SPI sequence diagrams are illustrated in Figure 2-12 through Figure 2-15.

#### 2.11.1 SPI CONFIG

**Write Register** - To write a value into a Configuration register, the timing diagram illustrated in Figure 2-12 should be followed by the host microcontroller. The new value of the register is effective from the rising edge of CSCON.

When writing more than one register successively, it is not compulsory to toggle CSCON back high between two write sequences. The bytes are alternatively considered as address and value. In this instance, all new values become effective on the rising edge of CSCON.

FIGURE 2-12: WRITE REGISTER SEQUENCE

Note:

**Read Register** - To read the value of a Configuration register, the timing diagram illustrated in Figure 2-13 should be followed by the host microcontroller.

Note: When reading more than one register successively, it is not compulsory to toggle CSCON back high between two read sequences. The bytes are alternatively considered as address and value.

FIGURE 2-13: READ REGISTER SEQUENCE

#### 2.11.2 SPI DATA

Write Byte (before/during TX) - To write bytes into the FIFO, the timing diagram illustrated in Figure 2-14 should be followed by the host microcontroller.

Note: It is compulsory to toggle CSDAT back high between each byte written. The byte is pushed into the FIFO on the rising edge of CSDAT.

FIGURE 2-14: WRITE BYTES SEQUENCE (EXAMPLE DIAGRAM FOR 2 BYTES)

**Read Byte (after/during RX)** - To read bytes from the FIFO, the timing diagram illustrated in Figure 2-15 should be followed by the host microcontroller.

**Note:** It is recommended to toggle CSDAT back high between each byte read.

FIGURE 2-15: READ BYTES SEQUENCE (EXAMPLE DIAGRAM FOR 2 BYTES)

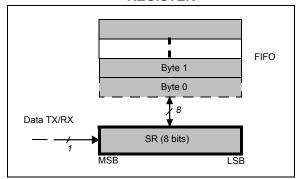

#### 2.12 FIFO and Shift Register (SR)

In Buffered and Packet modes of operation, data to be transmitted and data that has been received are stored in a configurable First In First Out (FIFO) buffer. The FIFO is accessed through the SPI data interface and provides several interrupts for transfer management.

The FIFO is 1 byte (8 bits) wide; therefore, it only performs byte (parallel) operations, whereas the demodulator functions serially. A shift register (SR) is therefore employed to interface the demodulator and the FIFO. In Transmit mode, it takes bytes from the FIFO and outputs them serially (MSB first) at the programmed bit rate to the modulator. Similarly, in Receive mode, the shift register gets bit-by-bit data from the demodulator and writes them byte-by-byte to the FIFO. This is illustrated in Figure 2-16.

FIGURE 2-16: FIFO AND SHIFT REGISTER

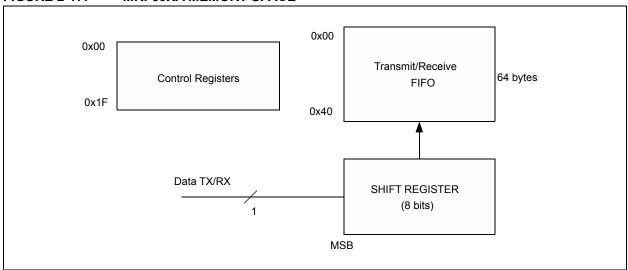

## 2.13 MRF89XA Configuration, Control and Status Registers

The memory in the MRF89XA transceiver is implemented as static RAM and is accessible through the SPI port. The memory configuration of the MRF89XA is illustrated in Figure 2-17 and Figure 2-18.

FIGURE 2-17: MRF89XA MEMORY SPACE

FIGURE 2-18: MRF89XA REGISTERS MEMORY MAP

|      | Register Name |      | Register Name |

|------|---------------|------|---------------|

| 0x00 | GCONREG       | 0x10 | FILCREG       |

| 0x01 | DMODREG       | 0x11 | PFCREG        |

| 0x02 | FDEVREG       | 0x12 | SYNCREG       |

| 0x03 | BRSREG        | 0x13 | RSTSREG       |

| 0x04 | FLTHREG       | 0x14 | RSVREG        |

| 0x05 | FIFOCREG      | 0x15 | OOKCREG       |

| 0x06 | R1CREG        | 0x16 | SYNCV31REG    |

| 0x07 | P1CREG        | 0x17 | SYNCV23REG    |

| 0x08 | S1CREG        | 0x18 | SYNCV15REG    |

| 0x09 | R2CREG        | 0x19 | SYNCV07REG    |

| 0x0A | P2CREG        | 0x1A | TXCONREG      |

| 0x0B | S2CREG        | 0x1B | CLKOREG       |

| 0x0C | PACREG        | 0x1C | PLOADREG      |

| 0x0D | FTXRXIREG     | 0x1D | NADDSREG      |

| 0x0E | FTPRIREG      | 0x1E | PKTCREG       |

| 0x0F | RSTHIREG      | 0x1F | FCRCREG       |

The MRF89XA registers handle command, configuration, control, status, or data/FIFO fields as listed in Table 2-6. The registers operate on parameters common to transmit and receive modes, Interrupts, Sync pattern, crystal oscillator, and packets.

The FIFO serves as a buffer for data transmission and reception. There is a shifted register (SR) to handle bit shifts for the FIFO during transmission and reception. POR sets default values in all Configuration/Control/ Status registers.

TABLE 2-6: CONFIGURATION/CONTROL/STATUS REGISTER DESCRIPTION

| General C           | General Configuration Registers: Size – 13 Bytes, Start Address – 0x00 |                                            |                                                                                            |  |  |

|---------------------|------------------------------------------------------------------------|--------------------------------------------|--------------------------------------------------------------------------------------------|--|--|

| Register<br>Address | Register<br>Name                                                       | Register Description                       | Related Control Functions                                                                  |  |  |

| 0x00                | GCONREG                                                                | General Configuration Register             | Transceiver mode, frequency band selection, VCO trimming, PLL frequency dividers selection |  |  |

| 0x01                | DMODREG                                                                | Data and Modulation Configuration Register | Modulation type, Data mode, OOK threshold type, IF gain                                    |  |  |

| 0x02                | FDEVREG                                                                | Frequency Deviation Control Register       | Frequency deviation in FSK Transmit mode                                                   |  |  |

| 0x03                | BRSREG                                                                 | Bit Rate Set Register                      | Operational bit rate                                                                       |  |  |

| 0x04                | FLTHREG                                                                | Floor Threshold Control Register           | Floor threshold in OOK Receive mode                                                        |  |  |

| 0x05                | FIFOCREG                                                               | FIFO Configuration Register                | FIFO size and threshold                                                                    |  |  |

| 0x06                | R1CREG                                                                 | R1 Counter Set Register                    | Value input for R1 counter                                                                 |  |  |

| 0x07                | P1CREG                                                                 | P1 Counter Set Register                    | Value input for P1 counter                                                                 |  |  |

| 0x08                | S1CREG                                                                 | S1 Counter Set Register                    | Value input for S1 counter                                                                 |  |  |

| 0x09                | R2CREG                                                                 | R2 Counter Set Register                    | Value input for R2 counter                                                                 |  |  |

| 0x0A                | P2CREG                                                                 | P2 Counter Set Register                    | Value input for P2 counter                                                                 |  |  |

| 0x0B                | S2CREG                                                                 | S2 Counter Set Register                    | Value input for S2 counter                                                                 |  |  |

| 0x0C                | PACREG                                                                 | Power Amplifier Control Register           | Ramp Control of PA regulator output voltage in OOK                                         |  |  |

| Interrupt C         | Interrupt Configuration Registers: Size – 3 Bytes, Start Address – 0x0D |                                                                        |                                                                                                                                                           |  |  |

|---------------------|-------------------------------------------------------------------------|------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Register<br>Address | Register<br>Name                                                        | Register Description                                                   | Related Control Functions                                                                                                                                 |  |  |

| 0x0D                | FTXRXIREG                                                               | FIFO, Transmit and Receive Interrupt<br>Request Configuration Register | Interrupt request (IRQ0 and IRQ1) in<br>Receive mode, interrupt request (IRQ1) in<br>Transmit mode, interrupt request for FIFO<br>full, empty and overrun |  |  |

| 0x0E                | FTPRIREG                                                                | FIFO Transmit PLL and RSSI Interrupt<br>Configuration Register         | FIFO fill method, FIFO fill, interrupt request (IRQ0) for transmit start, interrupt request for RSSI, PLL lock enable and status                          |  |  |

| 0x0F                | RSTHIREG                                                                | RSSI Threshold Interrupt Request<br>Configuration Register             | RSSI threshold for interrupt                                                                                                                              |  |  |

| Receiver 0          | Receiver Configuration Registers: Size – 6 Bytes, Start Address – 0x10 |                                         |                                                                                                                                 |  |  |

|---------------------|------------------------------------------------------------------------|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|--|--|

| Register<br>Address | Register<br>Name                                                       | Register Description                    | Related Control Functions                                                                                                       |  |  |

| 0x10                | FILCREG                                                                | Filter Configuration Register           | Passive filter bandwidth selection, sets the receiver bandwidth (Butterworth filter)                                            |  |  |

| 0x11                | PFCREG                                                                 | Polyphase Filter Configuration Register | Selects the central frequency of the polyphase filter                                                                           |  |  |

| 0x12                | SYNCREG                                                                | Sync Control Register                   | Enables polyphase filter (in OOK receive mode, bit synchronizer control, Sync Word recognition, Sync Word size, Sync Word error |  |  |

| 0x13                | RESVREG                                                                | Reserved Register                       | Reserved for future use                                                                                                         |  |  |

#### TABLE 2-6: CONFIGURATION/CONTROL/STATUS REGISTER DESCRIPTION (CONTINUED)

| Receiver (          | Receiver Configuration Registers: Size – 6 Bytes, Start Address – 0x14 |                            |                                                                                                                                                  |  |  |

|---------------------|------------------------------------------------------------------------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Register<br>Address | Register<br>Name                                                       | Register Description       | Related Control Functions                                                                                                                        |  |  |

| 0x14                | RSTSREG                                                                | RSSI Status Read Register  | RSSI output                                                                                                                                      |  |  |

| 0x15                | OOKCREG                                                                | OOK Configuration Register | RSSI threshold size in OOK demodulator,<br>RSSI threshold period in OOK demodulator,<br>cut-off frequency of the OOK threshold in<br>demodulator |  |  |

| Sync Wor            | Sync Word Configuration Registers: Size – 4 Bytes, Start Address – 0x16 |                                                           |                                                   |  |  |

|---------------------|-------------------------------------------------------------------------|-----------------------------------------------------------|---------------------------------------------------|--|--|

| Register<br>Address | Register<br>Name                                                        | Register Description                                      | Related Control Functions                         |  |  |

| 0x16                | SYNCV31REG                                                              | Sync Value 1 <sup>st</sup> Byte Configuration<br>Register | Configuring first byte of the 32-bit<br>Sync Word |  |  |

| 0x17                | SYNCV23REG                                                              | Sync Value 2 <sup>nd</sup> Byte Configuration Register    | Configuring second byte of the 32-bit Sync Word   |  |  |

| 0x18                | SYNCV15REG                                                              | Sync Value 3 <sup>rd</sup> Byte Configuration<br>Register | Configuring third byte of the 32-bit<br>Sync Word |  |  |

| 0x19                | SYNCV07REG                                                              | Sync Value 4 <sup>th</sup> Byte Configuration<br>Register | Configuring fourth byte of the 32-bit Sync Word   |  |  |

| Transmitte          | Transmitter Configuration Registers: Size – 1 Byte, Start Address – 0x1A |                                             |                                                        |  |  |  |  |  |

|---------------------|--------------------------------------------------------------------------|---------------------------------------------|--------------------------------------------------------|--|--|--|--|--|

| Register<br>Address | Register<br>Name                                                         | Register Description                        | Related Control Functions                              |  |  |  |  |  |

| 0x1A                | TXCONREG                                                                 | Transmit Configuration Register             | Transmit interpolation cut-off frequency, power output |  |  |  |  |  |

| Oscillator          | Configuration F                                                          | Registers: Size – 1 Byte, Start Address – 0 | iv1R                                                   |  |  |  |  |  |

| Oscillator          | Configuration                                                            | registers. Size – 1 byte, Start Address – 0 |                                                        |  |  |  |  |  |

| Register<br>Address | Register<br>Name                                                         | Register Description                        | Related Control Functions                              |  |  |  |  |  |

| 0x1B                | CLKOREG                                                                  | Clock Output Control Register               | Clock-out control, frequency                           |  |  |  |  |  |

| Packet Ha           | Packet Handling Configuration Registers: Size – 4 Bytes, Start Address – 0x1C |                                               |                                                                                                               |  |  |  |  |

|---------------------|-------------------------------------------------------------------------------|-----------------------------------------------|---------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Register<br>Address | Register<br>Name                                                              | Redister Description   Related Control Flinct |                                                                                                               |  |  |  |  |

| 0x1C                | PLOADREG                                                                      | Payload Configuration Register                | Enable Manchester encoding/decoding, payload length                                                           |  |  |  |  |

| 0x1D                | NADDSREG                                                                      | Node Address Set Register                     | Node's local address for filtering of received packets                                                        |  |  |  |  |

| 0x1E                | PKTCREG                                                                       | Packet Configuration Register                 | Packet format, size of the preamble, whitening, CRC on/off, address filtering of received packets, CRC status |  |  |  |  |

| 0x1F                | FCRCREG                                                                       | FIFO CRC Configuration Register               | FIFO auto-clear (if CRC failed), FIFO access                                                                  |  |  |  |  |

#### 2.14 General Configuration Registers

#### 2.14.1 GENERAL CONFIGURATION REGISTER DETAILS

## REGISTER 2-1: GCONREG: GENERAL CONFIGURATION REGISTER (ADDRESS:0X00) (POR:0X28)

| R/W-0     | R/W-0 | R/W-1    | R/W-0 | R/W-1     | R/W-0 | R/W-0 | R/W-0 |

|-----------|-------|----------|-------|-----------|-------|-------|-------|

| CMOD<2:0> |       | FBS<1:0> |       | VCOT<1:0> |       | RPS   |       |

| bit 7     |       |          |       |           |       |       | bit 0 |

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |

|-------------------|------------------|------------------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |

| r = Reserved      |                  |                                    |                    |

#### bit 7-5 CMOD<2:0>: Chip Mode bits

These bits select the mode of operation of the transceiver.

111 = Reserved; do not use

110 = Reserved; do not use

101 = Reserved; do not use

100 = Transmit mode

011 = Receive mode

010 = Frequency Synthesizer mode

001 = Standby mode (default)

000 = Sleep mode

#### bit 4-3 **FBS<1:0>:** Frequency Band Select bits

These bits set the frequency band to be used in Sub-GHz range.

11 = Reserved

10 = 950-960 MHz or 863-870 MHz (application circuit dependent)

01 = 915-928 MHz (default)

00 **= 902-915** MHz

#### bit 2-1 **VCOT<1:0>:** TX bits

For each AFC cycle run, these bits toggle between logic '1' and logic '0'.

11 = Vtune + 180 mV typ

10 = Vtune + 120 mV typ

01 = Vtune + 60 mV typ

00 = Vtune determined by tank inductors values (default)

#### bit 0 RPS: RPS Select bit

This bit selects between the two sets of frequency dividers of the PLL, Ri/Pi/Si. For more information, see **Section 3.2.7**, **Frequency Calculation**.

1 = Enable R2/P2/S2 set

0 = Enable R1/P1/S1 set (default)

#### 2.14.2 DATA AND MODULATION CONFIGURATION REGISTER DETAILS

## REGISTER 2-2: DMODREG: DATA AND MODULATION CONFIGURATION REGISTER (ADDRESS:0X01) (POR:0X88)

| R/W-1 | R/W-0                          | R/W-0 | R/W-0  | R/W-1       | R/W-0 | R/W-0 | R/W-0 |

|-------|--------------------------------|-------|--------|-------------|-------|-------|-------|

| MODSE | MODSEL<1:0> DMODE0 OOKTYP<1:0> |       | DMODE1 | IFGAIN<1:0> |       |       |       |

| bit 7 |                                |       |        |             |       |       | bit 0 |

| R = Readable bit  | W = Writable bit                  | U = Unimplemented bit | U = Unimplemented bit, read as '0' |  |  |

|-------------------|-----------------------------------|-----------------------|------------------------------------|--|--|

| -n = Value at POR | n = Value at POR '1' = Bit is set |                       | x = Bit is unknown                 |  |  |

| r = Reserved      |                                   |                       |                                    |  |  |

bit 7-6 **MODSEL<1:0>:** Modulation Type Selection bits

These bits set the type of modulation to be used in Sub-GHz range.

11 = Reserved

10 = FSK (default)

01 **= OOK**

00 = Reserved

bit 5 **DMODE0:** Data Mode 0 bit<sup>(1)</sup>

Setting this bit selects the data operational mode as LSB. Use this bit with DMODE1 to select the operational mode.

0 = Default

bit 4-3 **OOKTYP<1:0>:** OOK Demodulator Threshold Type bits

The combination of these bits selects the Demodulator Threshold Type for operation.

11 = Reserved

10 = Average Mode

01 = Peak Mode (default)

00 = Fixed threshold mode

bit 2 **DMODE1**: Data Mode 1 bit<sup>(1)</sup>

Setting this bit selects the data operational mode as MSB. Use this bit with DMODE0 to select the operational mode.

0 = Default

bit 1-0 **IFGAIN<1:0>:** IF Gain bits.

Selects gain on the IF chain.

11 = -13.5 dB

10 = -9 dB

01 = -4.5 dB

00 = 0 dB (maximal gain) (default)

**Note 1:** The combination of DMODE1:DMODE0 selects the Data Operation mode. See Table 2-7 for the available Data Operation mode settings.

#### TABLE 2-7: DATA OPERATION MODE SETTINGS

| Data Operation Mode       | DMODE1 | DMODE0      |  |

|---------------------------|--------|-------------|--|

| Continuous (default mode) | 0      | 0           |  |

| Buffered                  | 0      | 1           |  |

| Packet                    | 1      | x (x = 0/1) |  |

#### 2.14.3 FREQUENCY DEVIATION CONTROL REGISTER DETAILS

### REGISTER 2-3: FDEVREG: FREQUENCY DEVIATION CONTROL REGISTER (ADDRESS:0X02) (POR:0X03)

|            | •     |       | ·     |       |       |       |       |  |

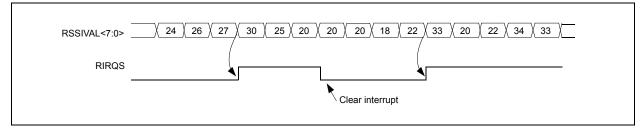

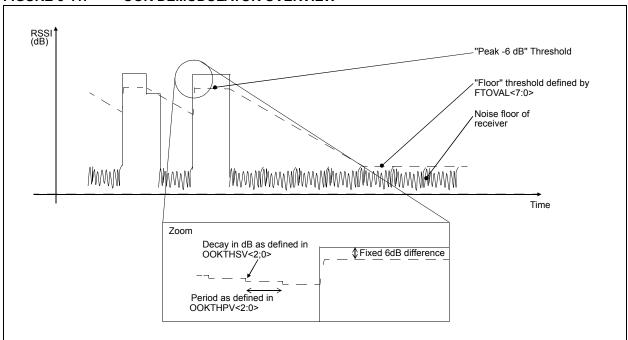

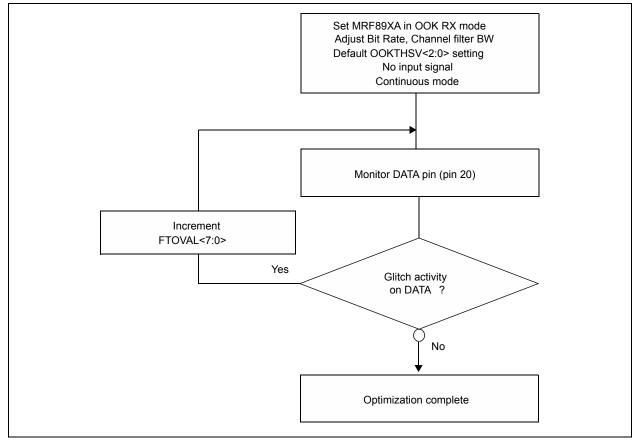

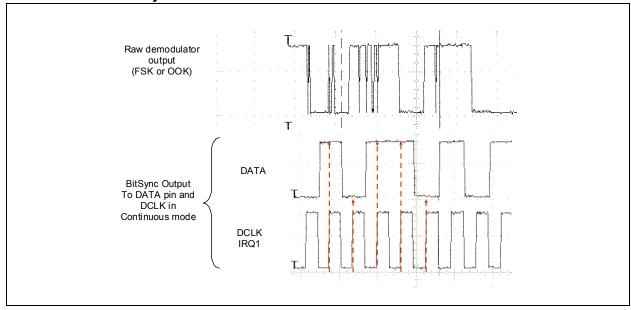

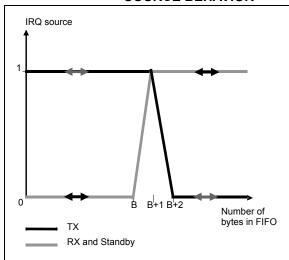

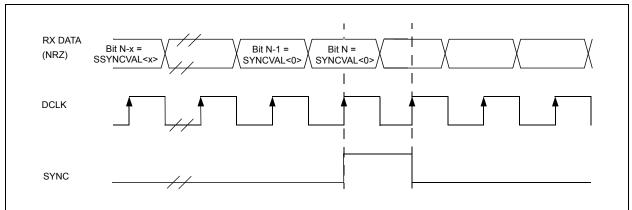

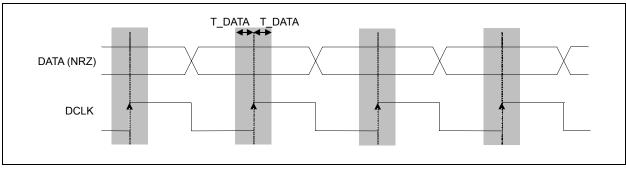

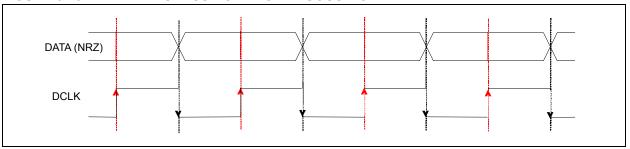

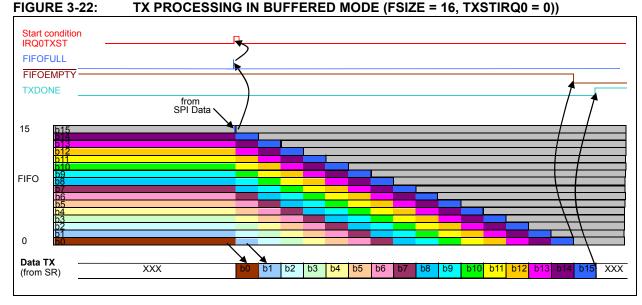

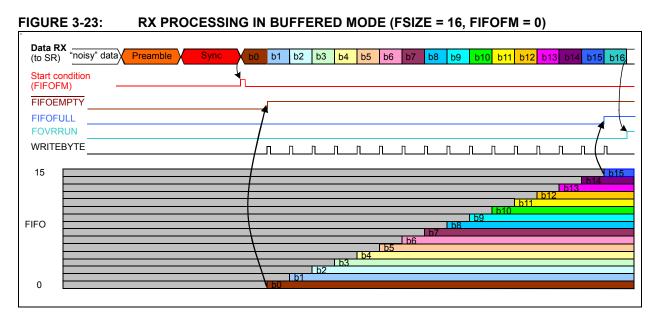

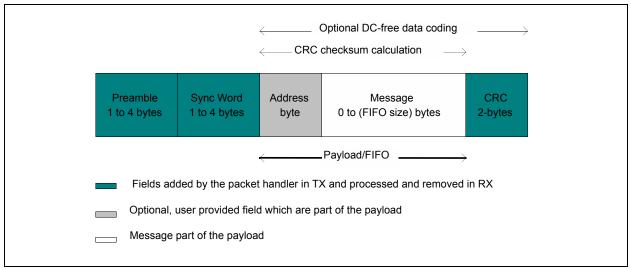

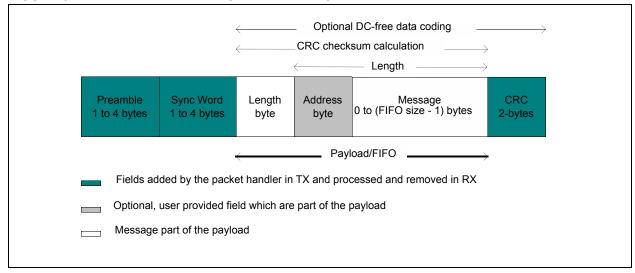

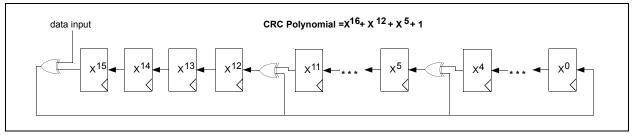

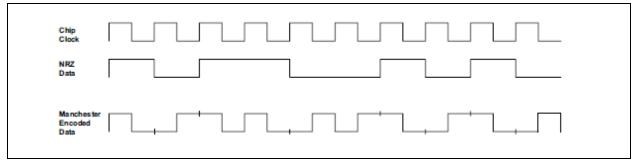

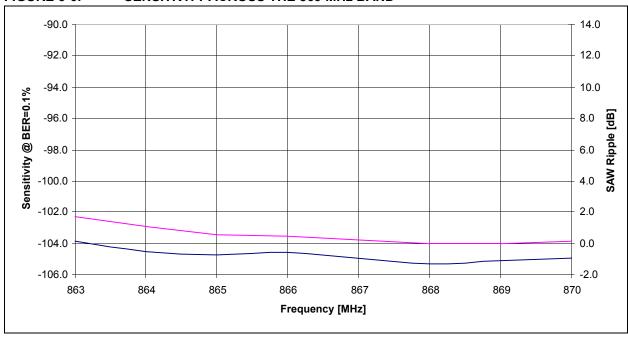

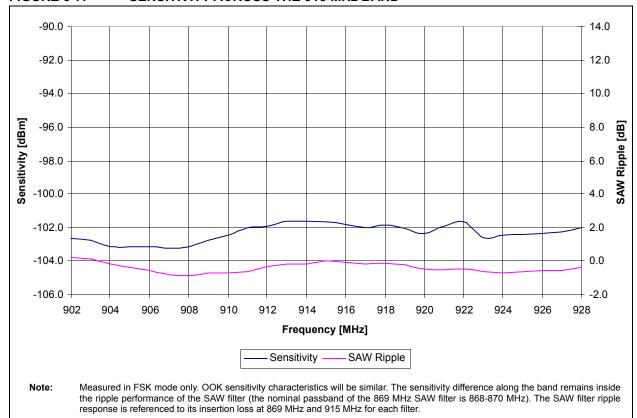

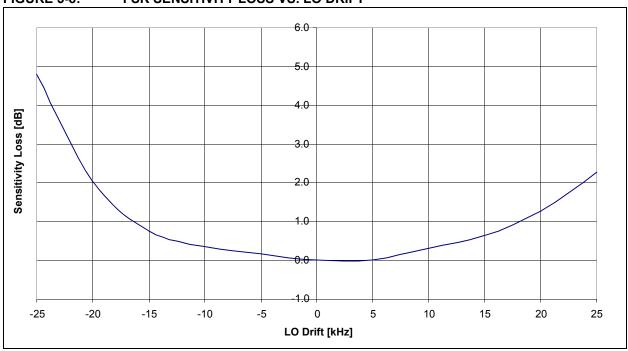

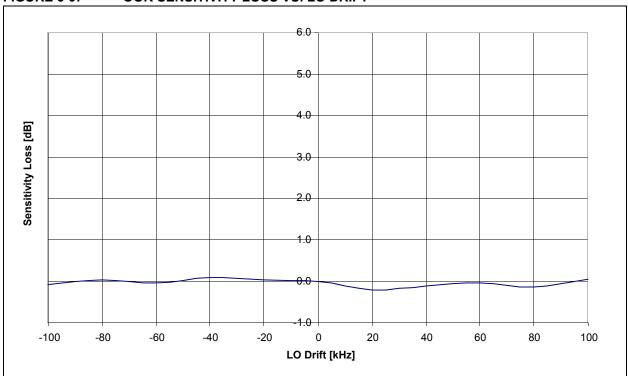

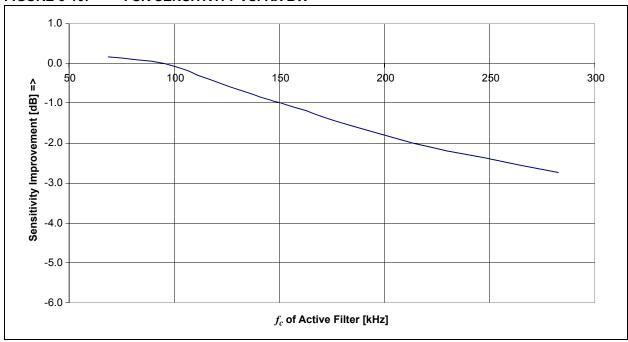

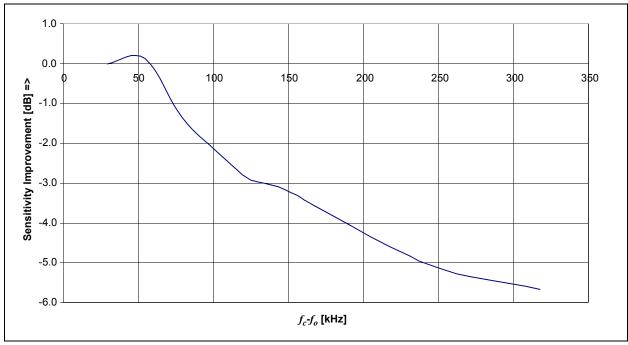

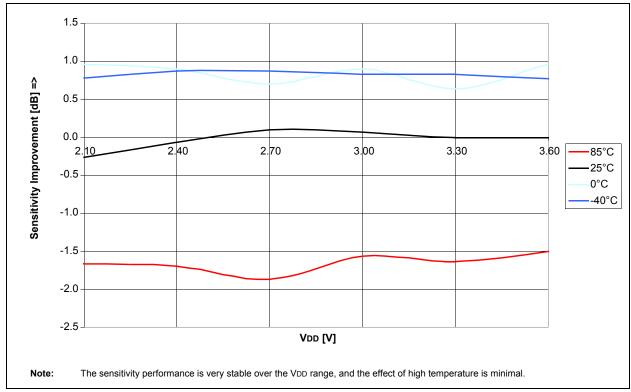

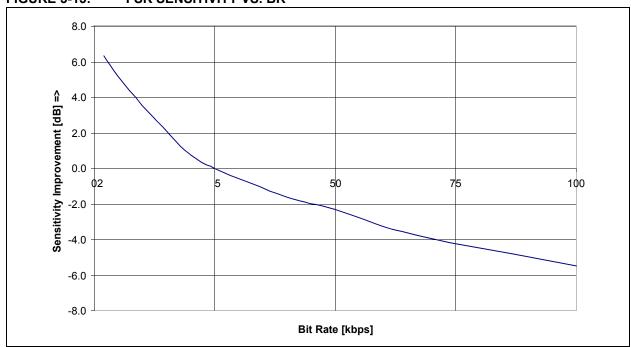

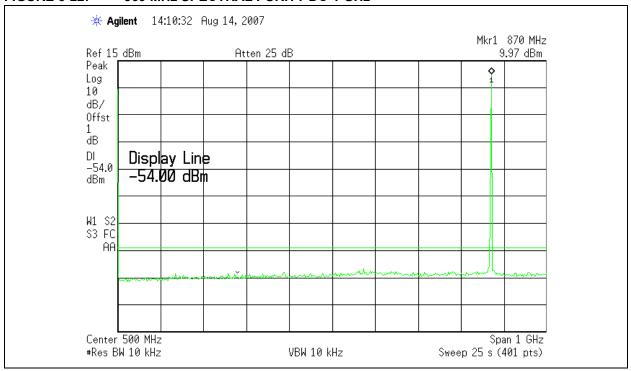

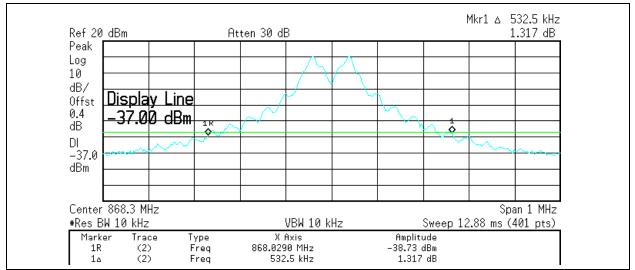

|------------|-------|-------|-------|-------|-------|-------|-------|--|