# HS-117RH, HS-117EH

Radiation Hardened Adjustable Positive Voltage Regulator

The radiation hardened HS-117RH and HS-117EH are adjustable positive voltage linear regulators capable of operating with input voltages up to 40V<sub>DC</sub>. The HS-117EH encompasses all of the production testing of the HS-117RH and additionally is tested in the Enhanced Low Dose Rate Sensitivity (ELDRS) product manufacturing flow. The output voltage is adjustable from 1.25V to 37V with two external resistors. The device is capable of sourcing from 5mA to 1.25A max (0.5A max for the TO-39 package). Current protection is provided by the on-chip thermal shutdown and output current limiting circuitry.

The HS-117xH's advantage over other industry types is its incorporated circuitry that minimizes the effects of radiation and temperature on device stability.

The HS-117RH and HS-117EH are constructed in the dielectrically isolated Rad Hard Silicon Gate (RSG) process and are immune to single event latch-up and are specifically designed to provide highly reliable performance in harsh radiation environments.

# **Applications**

- · Adjustable voltage regulators

- · Adjustable current regulators

# **Features**

- Electrically screened to DLA SMD # 5962-99547

- · Superior temperature stability

- · Overcurrent and over-temperature protection

- Wide input voltage range . . . . . . . . . . 4.25V to 40V

- Operating temperature range.....-55°C to +125°C

- · QML qualified per MIL-PRF-38535 requirements

- · Radiation environment

- Total Dose, High Dose Rate ...... 300krad(Si)

- Total Dose, Low Dose Rate...... 100krad(Si)\*

- \* Product capability established by initial characterization. The EH version is acceptance tested on a wafer-by-wafer basis to 50krad(Si) at low dose rate.

## **Related Literature**

For a full list of related documents, visit our website

• HS-117RH, HS-117EH device pages

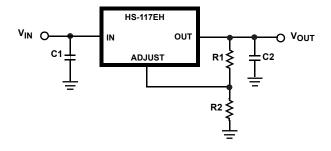

$V_{OUT} = V_{REF} (1+R2/R1) + I_{ADJ} R2$

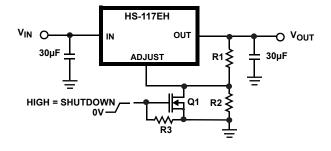

FIGURE 1. TYPICAL APPLICATION

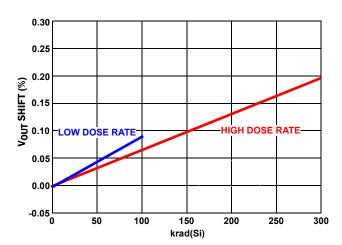

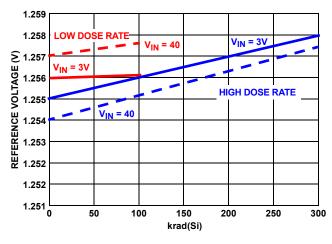

FIGURE 2. V<sub>OUT</sub> SHIFT vs HIGH and LOW DOSE RATE RADIATION

# **Typical Applications**

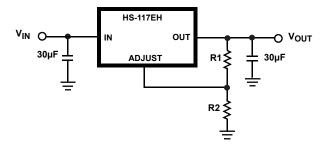

$V_{OUT} = V_{REF} (1 + R2/R1) + I_{ADJ}*R2$

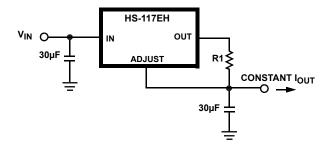

$I_{OUT} = V_{REF} / R1$

FIGURE 4. CONSTANT CURRENT REGULATOR

FIGURE 3. RESISTOR ADJUSTED OUTPUT VOLTAGE

In shutdown  $V_{OUT} = V_{REF}$

FIGURE 5. REGULATOR SHUTDOWN

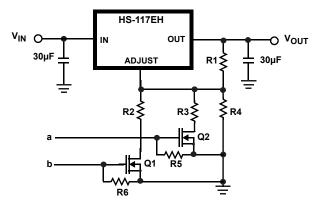

FIGURE 6. FOUR DIGITALLY PROGRAMMED OUTPUT VOLTAGES

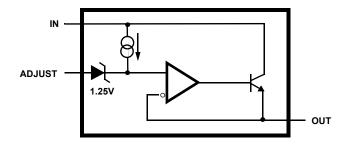

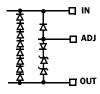

# **Functional Block Diagram**

# **Ordering Information**

| ORDERING SMD NUMBER (Note 2) | PART NUMBER<br>(Note 1)   | TEMPERATURE RANGE (°C) | PACKAGE DESCRIPTION (RoHS Compliant) | PKG.<br>DWG. # |

|------------------------------|---------------------------|------------------------|--------------------------------------|----------------|

| 5962F9954702V9A              | HS0-117EH-Q               | -55 to +125            | DIE                                  | -              |

| 5962F9954701V9A              | HS0-117RH-Q               | -55 to +125            | DIE                                  | -              |

| HS0-117RH/SAMPLE             | HS0-117RH/SAMPLE (Note 3) | -55 to +125            | DIE                                  | -              |

| 5962F9954702VUC              | HS2-117EH-Q               | -55 to +125            | 3 Ld METAL CAN                       | T3.C           |

| 5962F9954701VUC              | HS2-117RH-Q               | -55 to +125            | 3 Ld METAL CAN                       | T3.C           |

| 5962F9954701QUC              | HS2-117RH-8               | -55 to +125            | 3 Ld METAL CAN                       | T3.C           |

| HS2-117RH/PROTO              | HS2-117RH/PROTO (Note 3)  | -55 to +125            | 3 Ld METAL CAN                       | T3.C           |

| 5962F9954702VYC              | HSYE-117EH-Q              | -55 to +125            | 3 PAD CLCC                           | J3.A           |

| 5962F9954701VYC              | HSYE-117RH-Q              | -55 to +125            | 3 PAD CLCC                           | J3.A           |

| 5962F9954701QYC              | HSYE-117RH-8              | -55 to +125            | 3 PAD CLCC                           | J3.A           |

| HSYE-117RH/PROTO             | HSYE-117RH/PROTO (Note 3) | -55 to +125            | 3 PAD CLCC                           | J3.A           |

| 5962F9954701VXC              | HS9S-117RH-Q              | -55 to +125            | 3 Ld T0-257                          | T3.D           |

| 5962F9954701QXC              | HS9S-117RH-8              | -55 to +125            | 3 Ld T0-257                          | T3.D           |

| 5962F9954702VXC              | HS9S-117EH-Q              | -55 to +125            | 3 Ld TO-257                          | T3.D           |

| HS9S-117RH/PROTO             | HS9S-117RH/PROTO (Note 3) | -55 to +125            | 3 Ld TO-257                          | T3.D           |

- 1. These Pb-free Hermetic packaged products employ 100% Au plate e4 termination finish, which is RoHS compliant and compatible with both SnPb and Pb-free soldering operations.

- 2. Specifications for Rad Hard QML devices are controlled by the Defense Logistics Agency Land and Maritime (DLA). The SMD numbers listed must be used when ordering.

- 3. The /PROTO and /SAMPLE are not rated or certified for Total Ionizing Dose (TID) or Single Event Effect (SEE) immunity. These parts are intended for engineering evaluation purposes only. The /PROTO parts meet the electrical limits and conditions across temperature specified in the DLA SMD and are in the same form and fit as the qualified device. The /SAMPLE parts are capable of meeting the electrical limits and conditions specified in the DLA SMD at +25 °C only. The /SAMPLE parts do not receive 100% screening across temperature to the DLA SMD electrical limits. These part types do not come with a Certificate of Conformance because they are not DLA qualified devices.

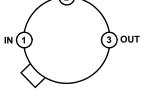

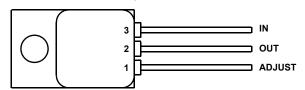

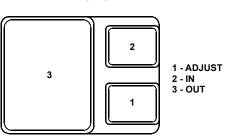

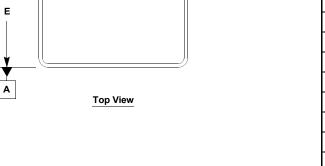

# **Pin Configurations**

HS2-117RH (TO-39 CAN) BOTTOM VIEW ADJUST

HS9S-117RH (TO-257AA FLANGE MOUNT) TOP VIEW

HSYE-117RH (SMD.5 CLCC) BOTTOM VIEW

NOTE: No current JEDEC outline for the SMD.5 package. See SMD for package dimensions. The TO-257 is a totally isolated metal package.

# **Pin Descriptions**

| HS2-117RH<br>(T0-39) | HS9S-117RH<br>(TO-257AA) | HSYE-117RH<br>(SMD.5 CLCC) | PIN NAME | DESCRIPTION                   |

|----------------------|--------------------------|----------------------------|----------|-------------------------------|

| 1                    | 3                        | 2                          | IN       | Regulator Input               |

| 2                    | 1                        | 1                          | ADJUST   | Voltage Adjust Feedback Input |

| 3                    | 2                        | 3                          | OUT      | Regulator Output              |

## **Absolute Maximum Ratings**

| Input to Output Voltage Differential 40V                     |

|--------------------------------------------------------------|

| Input to Output Voltage Differential (Note 6) 40V            |

| Maximum Output Current1.5A                                   |

| Maximum Power Dissipation T <sub>C</sub> = +25 °C            |

| HS2-117 (T0-39 Can)8W                                        |

| HS9S-117 (TO-257AA Flange Mount) 50W                         |

| HSYE-117 (SMD.5 CLCC)27.5W                                   |

| Maximum Power Dissipation $T_C = +100^{\circ} C (Note 7)$    |

| HS2-117 (T0-39 Can)                                          |

| HS9S-117 (TO-257AA Flange Mount) 20W                         |

| HSYE-117 (SMD.5 CLCC)                                        |

| ESD Rating                                                   |

| Human Body Model (HBM) (Tested per MIL-PRF-883 3015.7) 1500V |

| Machine Model (MM) (Tested per EIA/JESD22-A115-A)            |

## **Thermal Information**

| Thermal Resistance (Typical)                      | $\theta_{JA}(^{\circ}C/W)$ | θ <sub>JC</sub> (°C/W) |

|---------------------------------------------------|----------------------------|------------------------|

| T0-39 (Notes 4, 5, 7)                             | 125                        | 15                     |

| TO-257AA ( <u>Notes 4</u> , <u>5</u> , <u>7</u> ) | 26                         | 2.5                    |

| SMD.5 ( <u>Notes 4</u> , <u>5</u> , <u>7</u> )    | 42                         | 4.5                    |

| Maximum Storage Temperature Range                 | 6!                         | 5°C to +150°C          |

| Maximum Junction Temperature (T <sub>JMAX</sub> ) |                            | +175°C                 |

## **Recommended Operating Conditions**

| Ambient Operating Temperature Range | 55°C to +125°C |

|-------------------------------------|----------------|

| Input Voltage Range                 | 4.25V to 40V   |

| Output Voltage Range                | 1.25V to 37V   |

| Minimum Output Current              | 5mA            |

CAUTION: Do not operate at or near the maximum ratings listed for extended periods of time. Exposure to such conditions can adversely impact product reliability and result in failures not covered by warranty.

#### NOTES:

- 4. θ<sub>JA</sub> is measured with the component mounted on a high-effective thermal conductivity test board in free air. See <u>TB379</u> for details.

- 5. For  $\theta_{JC}$ , the "case temp" location is the center of the exposed metal pad on the package underside.

- 6. The maximum supply limit specified is for operation in a heavy ion environment at an LET =  $87.4 \text{MeV} \cdot \text{cm}^2/\text{mg}$ .

- 7. The linear derating factor for T0-39 package is 0.067 W/°C, for T0-257AA package is 0.4 W/°C, for the SMD.5 package is 0.22 W/°C

# **Electrical Specifications** $V_{DIFF} = 3V$ , $T_A = 25$ °C, unless otherwise noted. **Boldface limits apply across the operating temperature range,** -55 °C to +125 °C.

| PARAMETER SY                                        |                   | TEST CONDITIONS                                                                               | MIN<br>(Note 8)    | TYP   | MAX<br>(Note 8) | UNIT |

|-----------------------------------------------------|-------------------|-----------------------------------------------------------------------------------------------|--------------------|-------|-----------------|------|

| Reference Voltage                                   | V <sub>REF</sub>  | $V_{DIFF} = 3V, V_{DIFF} = 40V,$<br>5.0mA \le I <sub>OUT</sub> \le 5.5mA                      |                    | 1.255 | 1.30            | V    |

| Line Regulation                                     | R <sub>LINE</sub> | $V_{REF} = V_{OUT} - V_{ADJ}$ , $3V \le V_{DIFF} \le 40V$ ,<br>5.0mA $\le I_{OUT} \le 5.5$ mA | <b>-0.02</b> 0.009 |       | 0.02            | %    |

| Load Regulation                                     | R <sub>LOAD</sub> | V <sub>DIFF</sub> = 3V, 5mA ≤ I <sub>OUT</sub> ≤ 1.25A<br>TO-257AA and SMD.5 packages only    | -1.5               | -0.1  | 1.5             | %    |

|                                                     |                   | V <sub>DIFF</sub> = 3V, 5mA ≤ I <sub>OUT</sub> ≤ 500mA<br>TO-39 package                       | -1.5               | -0.8  | 1.5             | %    |

| Adjust Pin Current                                  | I <sub>ADJ</sub>  | V <sub>DIFF</sub> = 3V, V <sub>DIFF</sub> = 40V,<br>5.0mA ≤ I <sub>OUT</sub> ≤ 5.5mA          |                    | 64    | 100             | μΑ   |

| Adjust Pin Current Change                           | dl <sub>ADJ</sub> | 3V I <sub>ADJ</sub> - 40V I <sub>ADJ</sub><br>5.0mA ≤ I <sub>OUT</sub> ≤ 5.5mA                | <b>-6</b> 2.36     |       | 6               | μΑ   |

| Maximum Output Current                              | lout              | TO-257AA and SMD.5 packages only                                                              | 1.25               |       |                 | Α    |

|                                                     |                   | TO-39 package                                                                                 | 0.5                |       |                 | Α    |

| V <sub>IN</sub> Applied to V <sub>OUT</sub> Turn-On | T <sub>ON</sub>   |                                                                                               |                    | 0.2   |                 | ms   |

| Max. Output Short-Circuit Current Limit             | I <sub>sc</sub>   | V <sub>OUT</sub> = OV                                                                         |                    | 3     |                 | Α    |

| Over-Temperature Shutdown                           | ОТ                |                                                                                               |                    | 150   | 175             | °C   |

| Over-Temperature Hysteresis                         | OT_HYS            |                                                                                               |                    | 20    |                 | °C   |

Post Radiation Electrical Specifications  $V_{DIFF} = 3V$ ,  $T_A = +25$ °C, unless otherwise noted. Boldface limits apply over a total lonizing dose of 300krad(SI) with exposure at a high dose rate of 50 to 300krad(SI)/s; or over a total lonizing dose of 50krad(SI) with exposure a low dose rate of <10mrad(SI)/s.

| PARAMETER                 | SYMBOL            | CONDITIONS                                                                                    | MIN<br>(Note 8) | MAX<br>(Note 8) | UNIT |

|---------------------------|-------------------|-----------------------------------------------------------------------------------------------|-----------------|-----------------|------|

| Reference Voltage         | V <sub>REF</sub>  | V <sub>DIFF</sub> = 3V, V <sub>DIFF</sub> = 40V, 5.0mA ≤ I <sub>OUT</sub> ≤ 5.5mA             | 1.20            | 1.30            | ٧    |

| Line Regulation           | R <sub>LINE</sub> | $V_{REF} = V_{OUT} \cdot V_{ADJ}$ , $3V \le V_{DIFF} \le 40V$ , $5.0mA \le I_{OUT} \le 5.5mA$ | -0.02           | 0.02            | %    |

| Load Regulation           | R <sub>LOAD</sub> | V <sub>DIFF</sub> = 3V, 5mA ≤ I <sub>OUT</sub> ≤ 1.25A (TO-257AA and SMD.5 packages only)     | -1.5            | 1.5             | %    |

|                           |                   | V <sub>DIFF</sub> = 3V, 5mA ≤ I <sub>OUT</sub> ≤ 500mA (TO-39 package)                        | -1.5            | 1.5             | %    |

| Adjust Pin Current        | I <sub>ADJ</sub>  | V <sub>DIFF</sub> = 3V, V <sub>DIFF</sub> = 40V, 5.0mA ≤ I <sub>OUT</sub> ≤ 5.5mA             |                 | 100             | μΑ   |

| Adjust Pin Current Change | dl <sub>ADJ</sub> | 3V I <sub>ADJ</sub> - 40V I <sub>ADJ</sub> , 5.0mA ≤ I <sub>OUT</sub> ≤ 5.5mA                 | -6              | 6               | μΑ   |

| Output Current            | lout              | TO-257AA and SMD.5 packages only                                                              | 1.25            |                 | Α    |

|                           |                   | TO-39 package                                                                                 | 0.5             |                 | Α    |

#### NOTE:

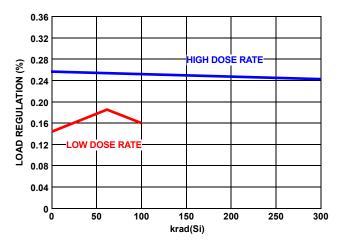

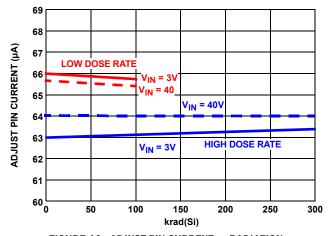

Post Radiation Characteristics This data is a typical mean test data post total dose radiation exposure at both a low dose rate (LDR) of <10mrad(Si)/s to 100krad(Si) and at a high dose rate (HDR) of 50 to 300rad(Si)/s to 300krad(Si). This data is intended to show typical parameter shifts due to low dose rate radiation. These are not limits nor are they guaranteed.

0.009 0.008 0.007 0.006 0.005 0.004 0.003 0.002 0.001 0 50 100 150 200 250 300 krad(Si)

FIGURE 7. REFERENCE VOLTAGE vs RADIATION

FIGURE 8. LINE REGULATION (3V  $\leq$  V<sub>DIFF</sub>  $\leq$  40V) vs RADIATION

FIGURE 9. LOAD REGULATION (I $_{\mbox{OUT}}$  5mA to 1.25A) vs RADIATION

FIGURE 10. ADJUST PIN CURRENT VS RADIATION

<sup>8.</sup> Compliance to datasheet limits is assured by one or more methods: production test, characterization, and/or design.

# **Typical Performance Curves**

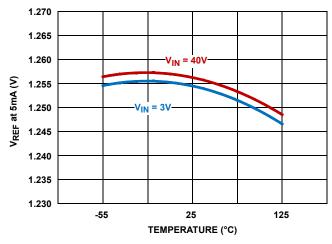

FIGURE 11. V<sub>REF</sub> vs TEMPERATURE

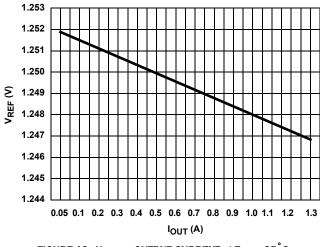

FIGURE 12. V<sub>REF</sub> vs OUTPUT CURRENT at T<sub>A</sub> = +25°C

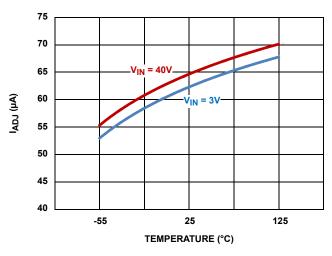

FIGURE 13.  $I_{\mbox{\scriptsize ADJ}}$  vs TEMPERATURE

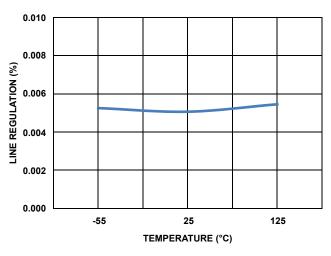

FIGURE 14. LINE REGULATION vs TEMPERATURE

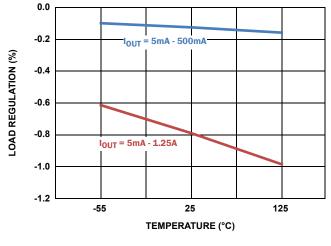

FIGURE 15. LOAD REGULATION vs TEMPERATURE

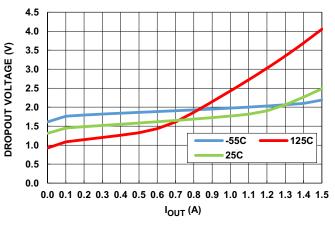

FIGURE 16. DROPOUT VOLTAGE vs OUTPUT CURRENT,  $V_{IN} = 12V$

# Typical Performance Curves (Continued)

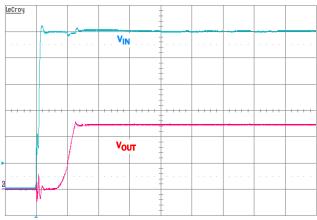

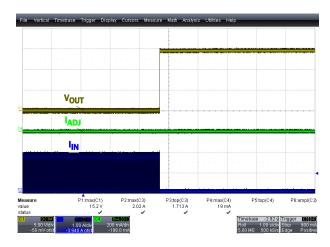

FIGURE 17. POWER-ON  $V_{IN} = 12V$ ,  $V_{OUT} = 5V$ ,  $RI = 10\Omega$

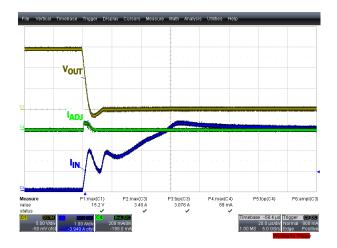

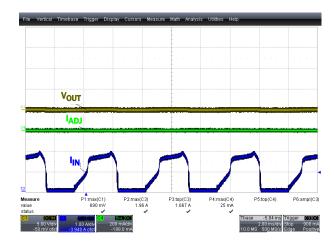

FIGURE 19. SHORT-CIRCUIT INTO OVER-TEMPERATURE PROTECTION

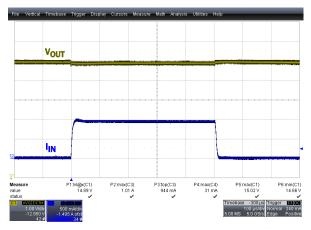

FIGURE 21. SHORT-CIRCUIT CURRENT LIMIT DETAIL

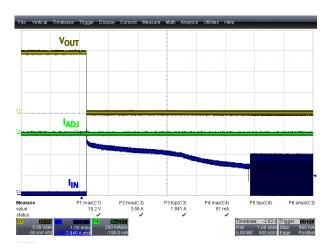

FIGURE 18.  $V_{IN}$  = 30V,  $V_{OUT}$  = 15V,  $I_{OUT}$  0 -1A STEP

FIGURE 20. SHORT-CIRCUIT RECOVERY

FIGURE 22. SHORT-CIRCUIT OVER-TEMPERATURE PROTECTION DETAIL

# **Functional Description**

#### **Functional Overview**

The radiation hardened HS-117RH and HS-117EH are adjustable positive voltage linear regulators capable of operating with input voltages up to  $40\text{V}_{DC}.$  The output voltage is adjustable from 1.25V (VREF) to 37V with two external resistors. The device is capable of sourcing from 5mA to 1.25APEAK (0.5APEAK for the TO-39 can package). Dual mode protection is provided by the on-chip +175°C thermal shutdown at output current limiting circuitry.

The HS-117xH's advantage over other industry types is its incorporated circuitry that minimizes the effects of radiation and temperature on device stability providing < 0.2% shifts in output voltage over 300krad(Si) of High Dose Rate (HDR) and 100krad(Si) of Low Dose Rate (LDR) gamma radiation.

The HS-117RH and HS-117EH are constructed in the dielectrically isolated Rad Hard Silicon Gate (RSG) process and are both immune to single event latch-up and are specifically designed to provide highly reliable performance providing power in harsh radiation environments.

#### **Output Voltage Adjustment**

The HS-117 is an adjustable output voltage regulator operating with a 1.25V reference voltage developed between the OUT and ADJUST pins. The ADJ current ( $I_{ADJ}$ ) is typically 64 $\mu$ A at +25  $^{\circ}$ C and 100 $\mu$ A maximum over temperature.

The HS-117's minimum current load for the regulation amplifier feedback to maintain stability is 5mA. To ensure stability in all situations, the minimum resistor between the VOUT and ADJ should be 120 $\Omega$ .

Referring to <u>Figure 1 on page 1</u>, the reference voltage is programmed to a constant current source by resistor  $R_1$ , and this current flows through  $R_2$  to ground to set the output voltage. See <u>Equation 1</u>.

$$V_{OUT} = 1.25(1 + R_2/R_1) + I_{ADJ}R_2$$

(EQ. 1)

In practical applications the R $_2$  value is in the range of a few k $\Omega$ , so that the I $_{ADJ}$  x R $_2$  contribution can be ignored in the V $_{OUT}$  calculation; simplifying the V $_{OUT}$  calculation to Equation 2:

$$V_{OUT} = 1.25(1 + R_2/R_1)$$

(EQ. 2)

#### **CURRENT LIMITING**

The HS-117 has internal current limiting that is activated whenever the output current exceeds the lower limit of the Maximum Output Current parameter shown in the "Electrical Specifications" on page 5, (typically limiting to ~1.5A) to a maximum limit of typically 3A in an output short-circuit condition.

During a short-circuit condition, if the regulator's differential voltage exceeds the Absolute Maximum Rating of 40V (for example,  $V_{\text{IN}} \ge 40V$ ,  $V_{\text{OUT}} = 0V$ ), the device can be damaged.

## **Performance and PCB Layout Considerations**

To optimize load regulation performance, implement Kelvin connections for the  $\rm R_1$  and  $\rm R_2$  resistors. In practice, the  $\rm R_1$  connection must be close to the OUT and ADJUST pins. This connection eliminates PCB trace resistance being included in the constant current determination. In contrast, place the  $\rm R_2$  to ground connection as close as possible to the negative load pin to ensure that the voltage being delivered to the load is as designed for by the choice of  $\rm R_1$  and  $\rm R_2$  values.

Ripple rejection can be improved by placing a  $10\mu F$  capacitor across the  $R_2$  resistor. At low output voltage, increasing this capacitor value further decreases output ripple.

#### **Input Capacitor**

Input bypass capacitance is recommended to enhance regulator stability if the device is located more than a few inches from its power source. Mount the input bypass capacitor (C1) with the shortest possible track length directly across the regulator's input and ground terminals. A  $30\mu F$  tantalum capacitor should be adequate for most applications.

#### **Output Capacitor**

Frequency compensation for the regulator is provided by the output capacitor (C2) and is required to ensure output stability. A minimum (C2) capacitance value of  $30\mu\text{F}$  is recommended for SEE tolerance. Higher values of output capacitance can be used to enhance loop stability, transient response, and output noise, but they must have sufficient ESR. Use Equation 3 to calculate your ESR zero and adjust the capacitance or ESR to ensure the zero is 13.3kHz or lower to ensure adequate phase and gain margin. This can be achieved by using a  $30\mu\text{F}$  capacitor with ESR of  $400\text{m}\Omega$  or greater.

$$f_{ESRzero} = \frac{1}{2 \times \pi \times R_{ESR} \times C_{OUT}}$$

(EQ. 3)

## **Adjust Capacitor**

In typical resistor-adjusted voltage regulator applications (Figures 1 and 3), adding a capacitor between the ADJUST pin and the circuit GND can improve load transient stability. A 100nF ceramic capacitor is adequate.

#### **Thermal Considerations**

The HS-117 has a thermal limiting circuit that is designed to protect the regulator when the junction temperature is typically >  $+150^{\circ}$  C. The regulator output turns off and then on again as the die cools. If the device is continuously operated in an over-temperature condition, this feature provides protection from catastrophic device damage due to accidental or prolonged overheating.

The HS-117 is available in a T0-39 3 pin can, a T0-257AA flange mount, and a SMD.5 CLCC surface mount package. These packages represent a wide range of thermal resistance to the die and thus a wide range of power dissipation (PD) capabilities. See "Thermal Information" on page 5 for the relevant package thermal impedances. The "Absolute Maximum Ratings" on page 5 lists the power dissipation limitations by package.

When developing circuits using the HS-117, test thermal performance and limitations to ensure acceptable performance. As with all tabbed packaged devices, flange mounting to a thermal heat-sink is recommended for the TO-257AA best practices.

# T0-257AA Package Characteristics

## **Weight of Packaged Device**

4.50g (Typical)

#### **Case Characteristics**

Finish: Gold Potential: Unbiased

# **T0-39 Package Characteristics**

## **Weight of Packaged Device**

0.91g (Typical)

#### **Case Characteristics**

Finish: Steel, Gold Potential: Unbiased

# SMD.5 CLCC Package Characteristics

## **Weight of Packaged Device**

0.91g (Typical)

#### **Case Characteristics**

Finish: Gold, Ceramic Potential: Unbiased

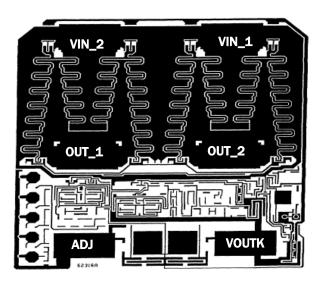

# **Die Characteristics**

#### **Die Dimensions**

$2616\mu m \ x \ 2794\mu m \ (103 \ mils \ x \ 110 \ mils)$ Thickness:  $483\mu m \pm 25\mu m \ (19 \ mils \ \pm 1 \ mil)$

#### **Interface Materials**

#### **GLASSIVATION**

Type: PSG

Thickness: 8kÅ ± 1kÅ

#### **TOP METALLIZATION**

Type: Al/Cu/Si (98.75%/0.5%/0.75%)

Thickness: 16kÅ

#### **BACKSIDE FINISH**

Gold

### **Assembly Related Information**

#### **SUBSTRATE POTENTIAL**

Unbiased (DI)

## **Additional Information**

#### **WORST CASE CURRENT DENSITY**

$< 2 \times 10^5 \, \text{A/cm}^2$

#### **PROCESS**

**Dielectrically Isolated RH - Si-GATE**

#### **TRANSISTOR COUNT:**

96

# **Metallization Mask Layout**

TABLE 1. DIE LAYOUT X-Y COORDINATES (Notes 9, 10)

| PAD NAME | Χ<br>(μm) | Y<br>(µm) | dΧ<br>(μm) | dΥ<br>(μm) |

|----------|-----------|-----------|------------|------------|

| VIN_1    | 1214      | 2191      | 514        | 257        |

| VIN_2    | 14        | 2191      | 514        | 257        |

| VOUT_1   | 14        | 934       | 514        | 257        |

| ADJ      | 0         | 0         | 514        | 257        |

| VOUTK    | 1361      | 14        | 514        | 257        |

| VOUT_2   | 1214      | 934       | 514        | 257        |

- 9. Origin of coordinates is the centroid of pad ADJ.

- 10. Bond Pads sized for is 5mil diameter wire.

**Revision History** The revision history provided is for informational purposes only and is believed to be accurate, but not warranted. Please visit our website to make sure you have the latest revision.

| DATE         | REVISION | CHANGE                                                                                                                                                                                                                                                                                                                                                                                   |

|--------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Aug 12, 2025 | 11.01    | Updated Figure 18 label. Replaced the External Bypass Capacitors section with three new sections. Updated POD J3.A to the latest revision; changes are as follows: -On bottom view, removed the termination numbering ("1", "2", "3") -Updated the package thickness minimum spec from 0.110 in. to 0.112 in. and from 2.79mm to 2.84mm -Updated note 4.                                 |

| Mar 28, 2019 | 11.00    | Updated links throughout document. Updated Related Literature section. Updated SEL/SEB LET <sub>TH</sub> information in Features section on page 1. Added Note 3. Updated Figure 16. Removed About Intersil section. Updated POD J3.A to the latest revision, changes are as follows: -Updated Max value for Symbol A from: 0.124inches/3.15mm to: 0.122inches/3.10mm Updated Disclaimer |

| Mar 25, 2014 | 10.00    | Updated "Ordering Information on page 3. Expanded content in datasheet from 3 to 15 pages.                                                                                                                                                                                                                                                                                               |

| Sep 4, 2012  | 9.00     | Added HS-117EH as Device # to datasheet (EH FGs already added to the Ordering Information table), making this a 2-part datasheet: HS-117RH, HS-117EH.  Global search/change HS-117RH to HS-117RH, HS-117EH.                                                                                                                                                                              |

| Dec 15, 2011 | 8.00     | Added parts to datasheet: HS2-117EH-Q, HS0-117EH-Q, HS9S-117EH-Q and HSYE-117EH-Q                                                                                                                                                                                                                                                                                                        |

| Oct 10, 2003 | 7.00     | Revised datasheet includes a new date and file number.                                                                                                                                                                                                                                                                                                                                   |

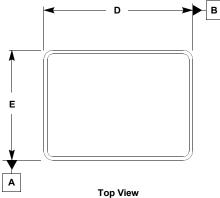

# **Package Outline Drawings**

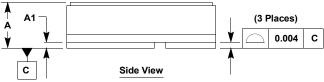

For the most recent package outline drawing, see <u>J3.A</u>.

**Bottom View**

J3.A 3 Pad Hermetic SMD.5 Package Bottom Terminal Ceramic Leadless Chip Carrier (CLCC)

|        | Inches |       | Millimeters |       |       |

|--------|--------|-------|-------------|-------|-------|

| Symbol | Min    | Max   | Min         | Max   | Notes |

| Α      | 0.112  | 0.122 | 2.84        | 3.10  | 3     |

| A1     | 0.010  | 0.020 | 0.25        | 0.51  | -     |

| b      | 0.281  | 0.291 | 7.13        | 7.39  | -     |

| b1     | 0.220  | 0.230 | 5.58        | 5.84  | -     |

| b2     | 0.090  | 0.100 | 2.28        | 2.54  | -     |

| b3     | 0.115  | 0.125 | 2.92        | 3.18  | -     |

| D      | 0.395  | 0.405 | 10.03       | 10.28 | -     |

| D1     | 0.030  | -     | 0.76        | -     | -     |

| Е      | 0.291  | 0.301 | 7.39        | 7.64  | -     |

| е      | 0.075  | BSC   | 1.91        | BSC   | -     |

Rev. 6 8/2025

#### Notes:

- 1. Controlling dimensions are in inches (mm for reference only).

- 2. Dimensioning and tolerance per ANSI Y14.5M 1982.

- 3. The maximum "A" dimension is package height before being solder dipped.

- 4. Patterned after MIL-STD-1835 CBCC1-N3 (C-B1).

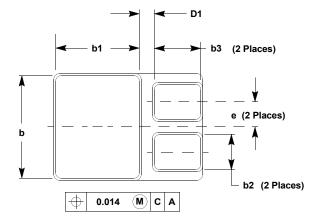

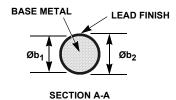

# Metal Can Package

For the most recent package outline drawing, see <u>T3.C</u>.

**T3.C** 3 LEAD TO-39 (TO-205) METAL CAN PACKAGE

|                 | INCHES    |       | MILLIM   | ETERS |       |

|-----------------|-----------|-------|----------|-------|-------|

| SYMBOL          | MIN       | MAX   | MIN      | MAX   | NOTES |

| Α               | 0.160     | 0.180 | 4.07     | 4.58  | -     |

| Øb              | 0.016     | 0.019 | 0.41     | 0.48  | 1     |

| Øb <sub>1</sub> | 0.016     | 0.021 | 0.41     | 0.53  | 1     |

| Øb <sub>2</sub> | 0.016     | 0.024 | 0.41     | 0.61  | -     |

| ØD              | 0.350     | 0.370 | 8.89     | 9.40  | -     |

| ØD <sub>1</sub> | 0.315     | 0.335 | 8.00     | 8.51  | -     |

| е               | 0.200 BSC |       | 5.08 BSC |       | -     |

| e <sub>1</sub>  | 0.100     | BSC   | 2.54 BSC |       | -     |

| F               | 0.009     | 0.050 | 0.23     | 1.27  | -     |

| k               | 0.027     | 0.034 | 0.69     | 0.086 | -     |

| k <sub>1</sub>  | 0.027     | 0.045 | 0.69     | 1.14  | 2     |

| L               | 0.500     | 0.750 | 12.70    | 19.05 | 1     |

| L <sub>1</sub>  | -         | 0.050 | -        | 1.27  | 1     |

| L <sub>2</sub>  | 0.250     | -     | 6.35     | -     | 1     |

| α               | 45° BSC   |       | 45°      | BSC   | 3     |

| β               | 90° BSC   |       | 90°      | BSC   | -     |

| N               | (         | 3     | ;        | 3     | 4     |

Rev. 0 6/01

- 1. (All leads) Øb applies between  $\mathsf{L}_1$  and  $\mathsf{L}_2.$  Øb  $_1$  applies between L<sub>2</sub> and 0.500 from the reference plane. Diameter is uncontrolled in L<sub>1</sub> and beyond 0.500 from the reference plane.

- 2. Measured from maximum diameter of the product.

- 3.  $\alpha$  is the basic spacing from the centerline of the tab to terminal 1 looking at the bottom of the package.

- 4. N is the maximum number of terminal positions.

- 5. Controlling dimension: Millimeter.

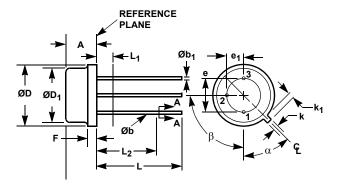

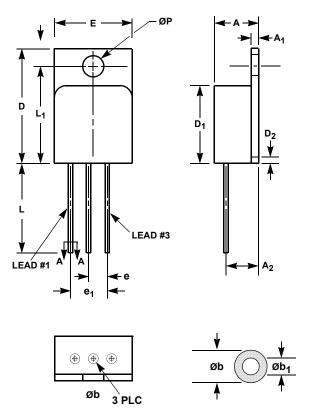

# Hermetic Metal Package

For the most recent package outline drawing, see  $\underline{\mathsf{T3.D}}$ .

T3.D 3 LEAD JEDEC TO-257AA HERMETIC METAL PACKAGE

|                 | INCHES    |       | MILLIMETERS |       |       |

|-----------------|-----------|-------|-------------|-------|-------|

| SYMBOL          | MIN       | MAX   | MIN         | MAX   | NOTES |

| Α               | 0.188     | 0.200 | 4.78        | 5.08  | 7     |

| A <sub>1</sub>  | 0.035     | 0.045 | 0.89        | 1.14  | -     |

| A <sub>2</sub>  | 0.120     | BSC   | 3.05        | BSC   | -     |

| D               | 0.645     | 0.665 | 16.39       | 16.89 | -     |

| D <sub>1</sub>  | 0.410     | 0.430 | 10.41       | 10.92 | -     |

| D <sub>2</sub>  | -         | 0.038 | -           | 0.97  | -     |

| е               | 0.100 BSC |       | 2.54 BSC    |       | -     |

| e <sub>1</sub>  | 0.200     | BSC   | 5.08 BSC    |       | -     |

| Е               | 0.410     | 0.420 | 10.41       | 10.67 | -     |

| Øb              | 0.025     | 0.040 | 0.64        | 1.02  | 1, 2  |

| Øb <sub>1</sub> | 0.025     | 0.035 | 0.64        | 0.89  | 1, 2  |

| L               | 0.500     | 0.750 | 12.70       | 19.05 | -     |

| L <sub>1</sub>  | 0.527     | 0.537 | 13.39       | 13.64 | -     |

| Р               | 0.140     | 0.150 | 3.56        | 3.81  | -     |

| N               | 3         |       | ;           | 3     | 5     |

Rev. 2 3/09

- 1. Dimension Øb<sub>1</sub> applies to base metal only. Dimension Øb applies to plated part.

- 2. Section A-A dimension apply between 0.100 inch (2.54mm) to 0.150 inch (3.81mm) from lead tip.

- 3. Die to base BeO isolated, terminals to case is plated.

- 4. Controlling dimensions are in inches (mm for reference only).

- 5. N is the maximum number of terminal positions.

- 6. Patterned after MIL-STD-1835 MSFM1-P3AA.

- 7. "A" minimum dimension not meeting the MIL-STD 0.190 minimum dimension.

#### **IMPORTANT NOTICE AND DISCLAIMER**

RENESAS ELECTRONICS CORPORATION AND ITS SUBSIDIARIES ("RENESAS") PROVIDES TECHNICAL SPECIFICATIONS AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS OR IMPLIED, INCLUDING, WITHOUT LIMITATION, ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT OF THIRD-PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for developers who are designing with Renesas products. You are solely responsible for (1) selecting the appropriate products for your application, (2) designing, validating, and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. Renesas grants you permission to use these resources only to develop an application that uses Renesas products. Other reproduction or use of these resources is strictly prohibited. No license is granted to any other Renesas intellectual property or to any third-party intellectual property. Renesas disclaims responsibility for, and you will fully indemnify Renesas and its representatives against, any claims, damages, costs, losses, or liabilities arising from your use of these resources. Renesas' products are provided only subject to Renesas' Terms and Conditions of Sale or other applicable terms agreed to in writing. No use of any Renesas resources expands or otherwise alters any applicable warranties or warranty disclaimers for these products.

(Disclaimer Rev.1.01)

# **Corporate Headquarters**

TOYOSU FORESIA, 3-2-24 Toyosu, Koto-ku, Tokyo 135-0061, Japan www.renesas.com

#### **Trademarks**

Renesas and the Renesas logo are trademarks of Renesas Electronics Corporation. All trademarks and registered trademarks are the property of their respective owners.

#### **Contact Information**

For further information on a product, technology, the most up-to-date version of a document, or your nearest sales office, please visit <a href="https://www.renesas.com/contact-us/">www.renesas.com/contact-us/</a>.