***RoHS Compliant***

# **SATA-Disk Module 4**

***SDM4 7P/90D Middle Profile Specifications***

**January 17<sup>th</sup>, 2012**

**Version 1.1**

**Apacer**

*Access the best*

***Apacer Technology Inc.***

4<sup>th</sup> Fl., 75 Hsin Tai Wu Rd., Sec.1, Hsichih, New Taipei City, Taiwan 221

Tel: +886-2-2698-2888 Fax: +886-2-2698-2889

[www.apacer.com](http://www.apacer.com)

## Features:

- **Standard Serial ATA 2.6 (Gen. 2)**

- Serial ATA 2.6 (Gen. 2)

- SATA II, 3.0 Gbps

- ATA-compatible command set

- **Capacities**

- 2, 4, 8, 16, 32 GB

- **Performance\***

- Burst read/write: 300 MB/sec

- Sustained read: up to 85 MB/sec

- Sustained write: up to 80 MB/sec

- **Intelligent endurance design**

- Built-in hardware ECC, enabling up to 16/24 bit correction per 1K bytes

- Static wear-leveling scheme together with dynamical block allocation to significantly increase the lifespan of a flash device and optimize the disk performance

- Flash bad-block management

- S.M.A.R.T.

- Power Failure Management

- ATA Secure Erase

- TRIM

- **NAND Flash Type:** SLC

- **Zero power data retention**

- No battery required for data storage

- **Temperature ranges**

- Operation:

- Standard: 0°C to 70°C (32 ~ 158°F)

- Extended: -40°C to 85°C(-40° ~ 185°F)

- Storage: -40°C to 100°C (-40° ~ 212°F)

- **Supply voltage**

- 5.0 V ± 5%

- **Power consumption (typical)\***

- Active mode: 233 mA@5.0 V

- Idle mode: 75 mA@5.0 V

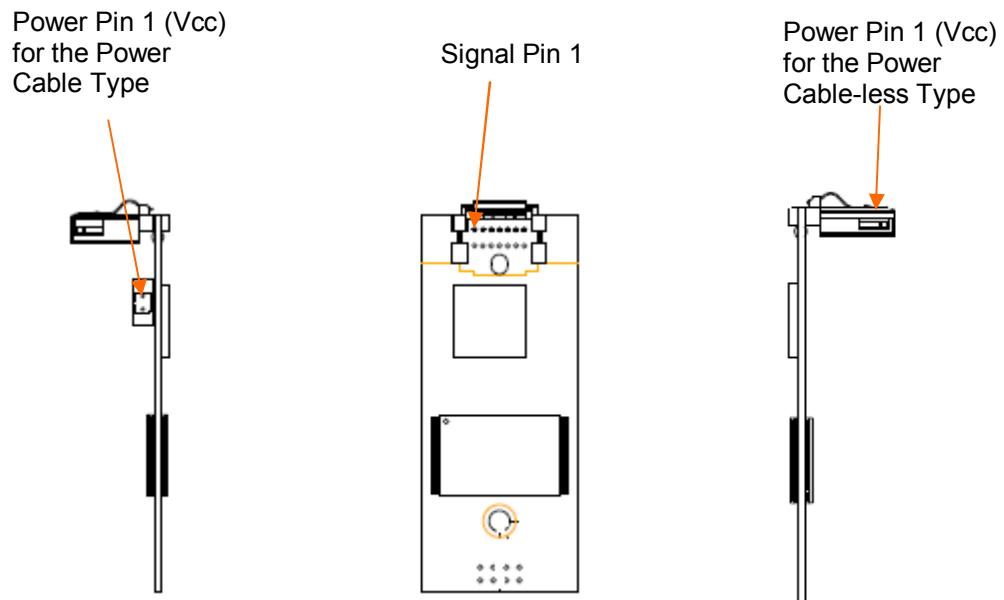

- **Connector type**

- 7-pin signal connector

- Power segment in two types: power cable and power cable-less types

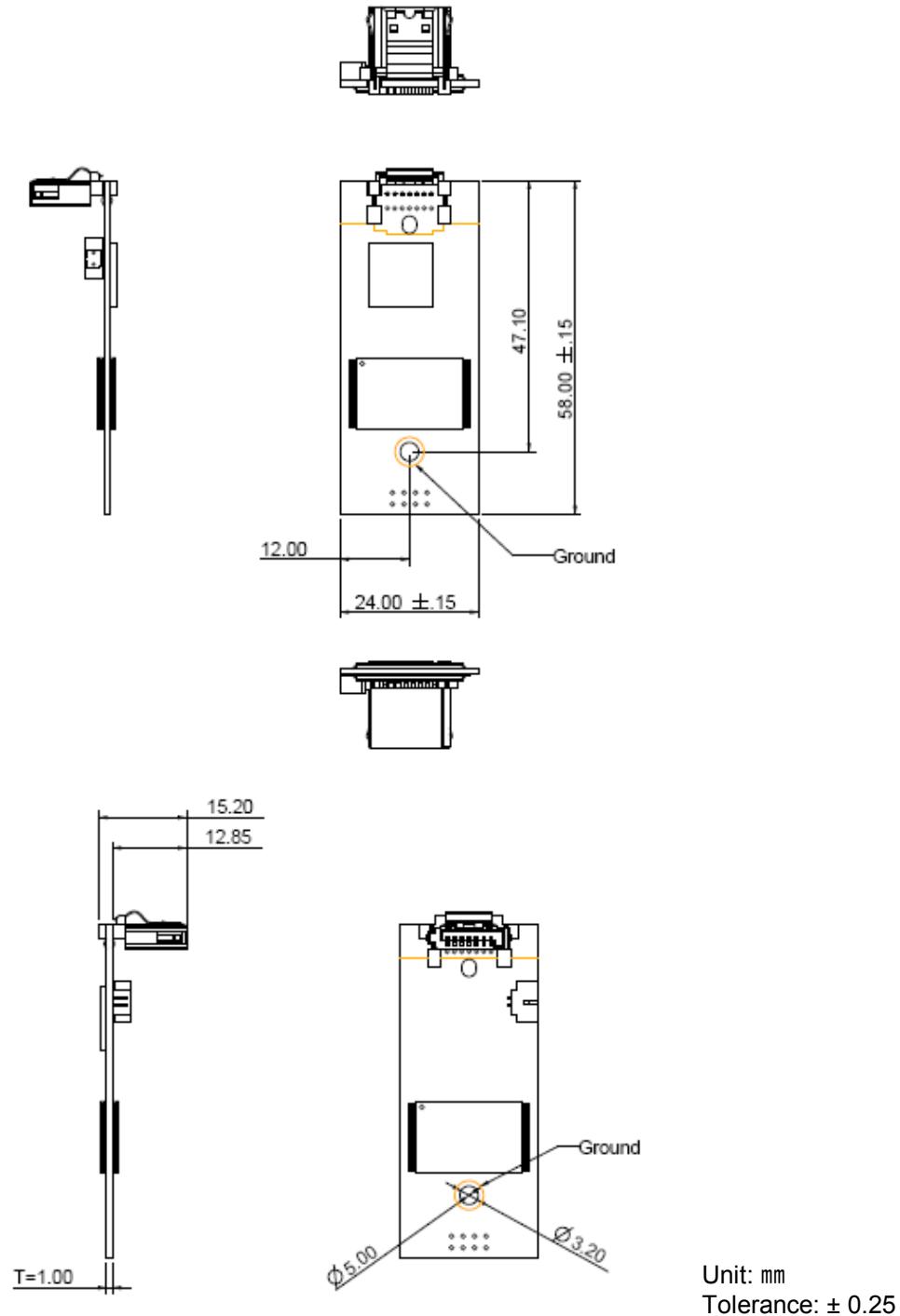

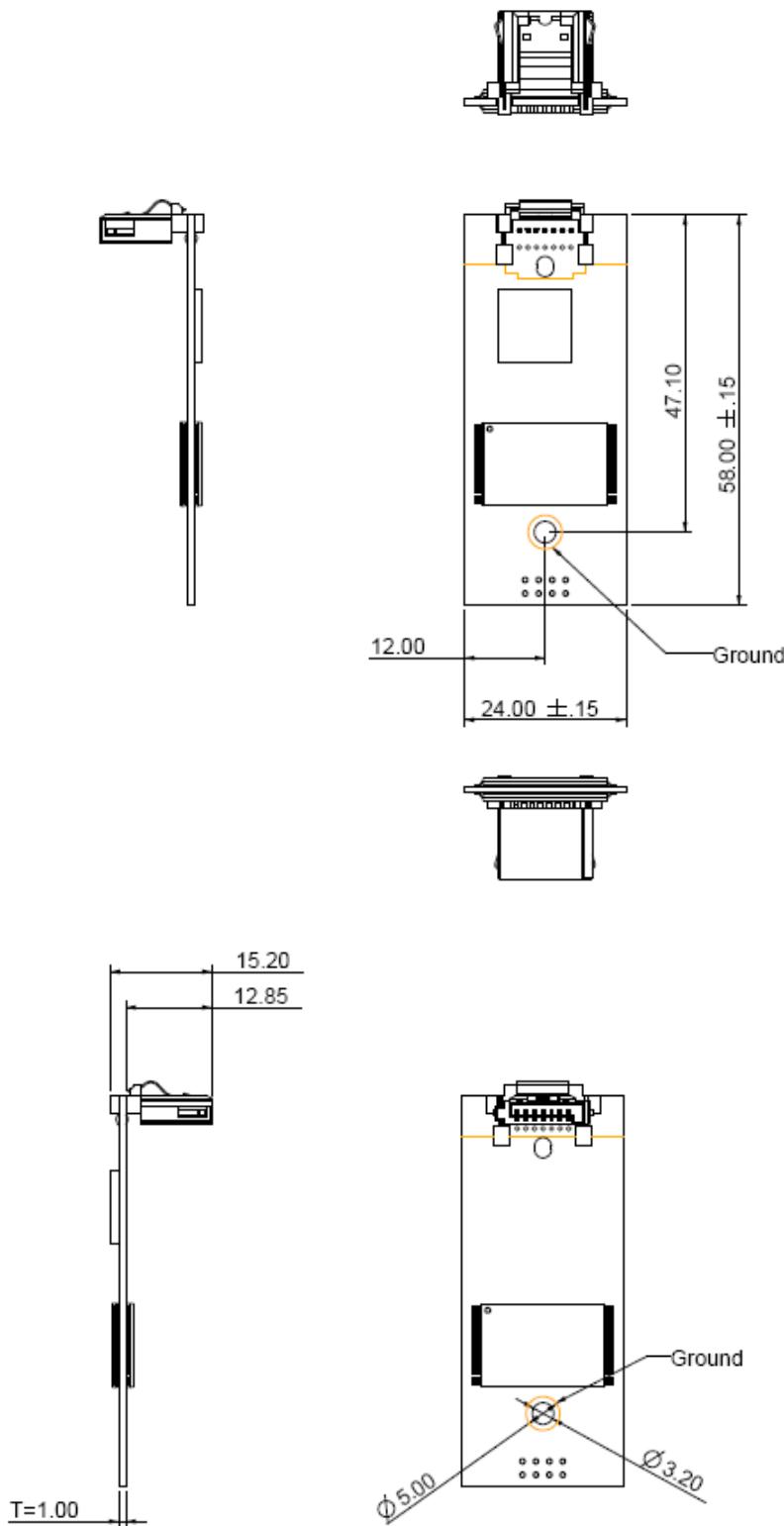

- **Form factor**

- Middle profile SATA Disk Module

- Dimension: 58.0 x 24.0 x1.0\*\*, unit: mm

- **Shock & Vibration**

- Shock: 50g (approx.)

- Vibration: 15g (approx.)

- **MTBF: >2,000,000**

- **RoHS compliant**

\*Varies from capacities. The values for performances and power consumptions presented are typical and may vary depending on flash configurations or platform settings. The term idle refers to the standby state of the device.

\*\*Implies to only the thickness of the module, without including the height/thickness of the connector head.

---

## Table of Contents

|                                                |           |

|------------------------------------------------|-----------|

| <b>1. GENERAL DESCRIPTION .....</b>            | <b>3</b>  |

| 1.1 PERFORMANCE-OPTIMIZED CONTROLLER .....     | 3         |

| 1.1.1 <i>Power Management Unit (PMU)</i> ..... | 3         |

| 1.1.2 <i>SRAM Buffer</i> .....                 | 3         |

| <b>2. FUNCTIONAL BLOCK .....</b>               | <b>4</b>  |

| <b>3. PIN ASSIGNMENTS .....</b>                | <b>5</b>  |

| <b>4. CAPACITY SPECIFICATION .....</b>         | <b>7</b>  |

| 4.1 PERFORMANCE SPECIFICATION .....            | 7         |

| 4.1.1 <i>ATA Mode Support</i> .....            | 7         |

| 4.1.2 <i>Performance</i> .....                 | 7         |

| 4.2 ENVIRONMENTAL SPECIFICATIONS .....         | 8         |

| 4.3 MEAN TIME BETWEEN FAILURES (MTBF) .....    | 8         |

| 4.4 CERTIFICATION AND COMPLIANCE .....         | 8         |

| <b>5. FLASH MANAGEMENT .....</b>               | <b>9</b>  |

| 5.1 ERROR CORRECTION/DETECTION .....           | 9         |

| 5.2 BAD BLOCK MANAGEMENT .....                 | 9         |

| 5.3 WEAR LEVELING .....                        | 9         |

| 5.4 POWER FAILURE MANAGEMENT .....             | 9         |

| 5.5 ATA SECURE ERASE .....                     | 9         |

| 5.6 S.M.A.R.T. .....                           | 10        |

| 5.7 TRIM .....                                 | 10        |

| <b>6. SOFTWARE INTERFACE .....</b>             | <b>11</b> |

| 6.1 COMMAND SET .....                          | 11        |

| <b>7. ELECTRICAL SPECIFICATION .....</b>       | <b>12</b> |

| 7.1 ELECTROSTATIC DISCHARGE .....              | 12        |

| 7.2 ELECTRICAL FAST TRANSIENT/BURST .....      | 13        |

| <b>8. PHYSICAL CHARACTERISTICS .....</b>       | <b>14</b> |

| 8.1 POWER CABLE TYPE .....                     | 14        |

| 8.2 POWER CABLE-LESS TYPE .....                | 15        |

| <b>9. PRODUCT ORDERING INFORMATION .....</b>   | <b>16</b> |

| 9.1 PRODUCT CODE DESIGNATIONS .....            | 16        |

## 1. General Description

Apacer's SATA-Disk Module 4 (SDM4) is a high-performance, embedded SSD designed to replace the conventional SATA hard disk drive. SDM SSD can be plugged into a standard Serial ATA 7-pin connector commonly found in desktops, IT-STB, industrial PC and thin client systems. Moreover, Apacer provides an innovative way for design-in customers to strengthen the vibration-resistance between SDM4 and mainboard.

Apacer's SDM4 has a built-in microcontroller with file management firmware that communicates with SATA standard interface. This means SDM4 does not require additional or proprietary host software such as Flash File System (FFS) and Memory Technology Driver (MTD). This product is well suited for embedded flash storage applications offering new and expanded functionalities as well as more cost-effective designs, better performance and increased reliability.

SDM4 Series is designed to work at 5 Volts and uses a standard SATA driver that complies with major operating systems such as Microsoft's Windows series.

Featuring technologies as Apacer-specific Wear-leveling algorithms, S.M.A.R.T, Enhanced Data Integrity, Intelligent Power Failure Management, ATA Secure Erase, and TRIM, Apacer assures users of a versatile device on data storage.

This SDM4 SSD is designed to be rugged for industrial applications where harsh, demanding environments are often encountered, and has gone through environmental testings such as shock, wide temperature range and ESD. Our SSD meets international standards and we specialized in customization services in both hardware and systems.

Our customization services include:

- Product change notification (PCN)<sup>1</sup>

- Pre-installed software, custom software imaging and ID strings<sup>2</sup>

- Customize packaging and labeling<sup>2</sup>

- Specified testing<sup>2</sup>

- Safety packaging, such as ESD protection pad, honeycomb-cut packing in sponge, or other types of protection.

- Field Application Engineers in our overseas branches for technical support

<sup>1</sup>Usually notified by our sales representatives or product managers, instead of on packages.

<sup>2</sup>Depending on specified requests

### 1.1 Performance-Optimized Controller

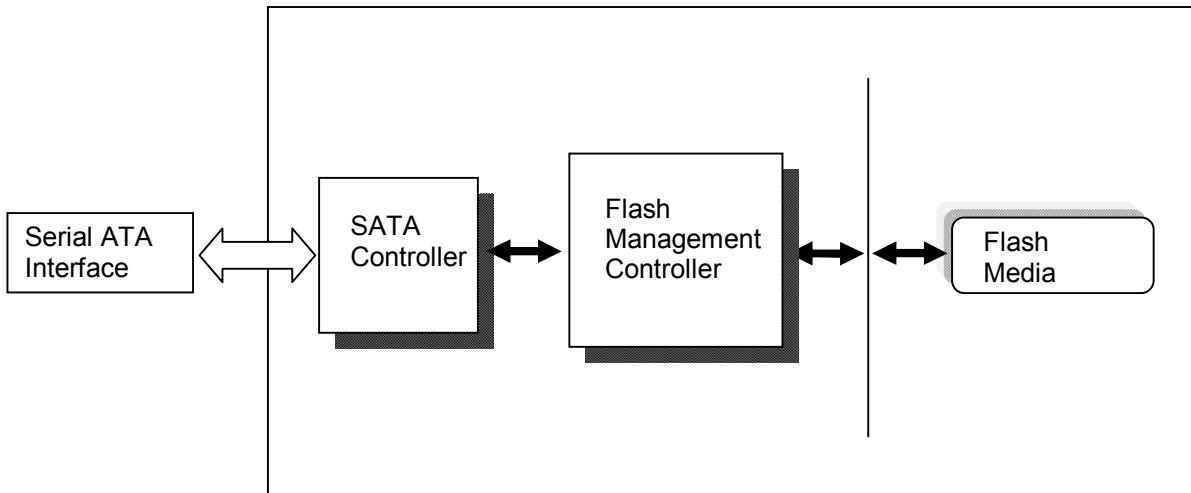

The heart of SDM4 is the Flash controller, which translates standard SATA signals into the data and controls of the flash media. The SATA and Flash Management controller are specifically designed to attain high data throughput from the host to the flash.

#### 1.1.1 Power Management Unit (PMU)

The power management unit (PMU) controls the power consumption of SDM4. It can dramatically extend product battery life by leaving the idle part of the circuitry into sleep mode. The PMU has zero wake-up latency.

#### 1.1.2 SRAM Buffer

The Flash Controller performs as a SRAM buffer to optimize the host's data transfer to and from the flash media.

## 2. Functional Block

SDM4 includes the SATA and Flash Management controllers, and flash media, as well as the SATA standard interface. Figure 2-1 shows the functional block diagram.

**Figure 2-1:** Functional block diagram

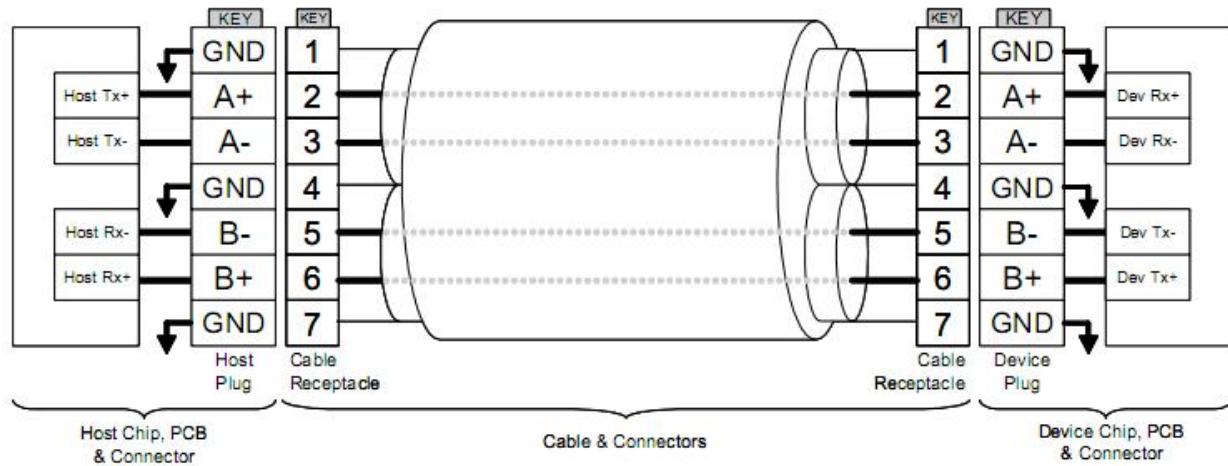

### 3. Pin Assignments

**Table 3-1:** Signal segment

| Name | Type | Description                    |

|------|------|--------------------------------|

| S1   | GND  |                                |

| S2   | RxP  | + Differential Receive Signal  |

| S3   | RxN  | - Differential Receive Signal  |

| S4   | GND  |                                |

| S5   | TxN  | - Differential Transmit Signal |

| S6   | TxP  | + Differential Transmit Signal |

| S7   | GND  |                                |

**Table 3-2:** Power segment

| Name | Description |

|------|-------------|

| P1   | VCC (5V)    |

| P2   | GND         |

**Figure 3-1: SATA Cable/Connector Connection Diagram**

The connector on the left represents the Host with TX/RX differential pairs connected to a cable. The connector on the right shows the Device with TX/RX differential pairs also connected to the cable. Notice also the ground path connecting the shielding of the cable to the Cable Receptacle.

## 4. Capacity Specification

Capacity specification of SDM4 product family is available as shown in Table 4-1. It lists the specific capacity and the default numbers of heads, sectors and cylinders for each product line.

**Table 4-1: Capacity specifications**

| Capacity | Total bytes*   | Cylinders | Heads | Sectors | Max LBA    |

|----------|----------------|-----------|-------|---------|------------|

| 2 GB     | 2,011,226,112  | 3,897     | 16    | 63      | 3,928,176  |

| 4 GB     | 4,011,614,208  | 7,773     | 16    | 63      | 7,835,184  |

| 8 GB     | 8,012,390,400  | 15,525    | 16    | 63      | 15,649,200 |

| 16 GB    | 16,013,942,784 | 16,383    | 16    | 63      | 31,277,232 |

| 32 GB    | 32,017,047,552 | 16,383    | 16    | 63      | 62,533,296 |

\*Display of total bytes varies from file systems, which means not all of the bytes can be used for storage.

### 4.1 Performance Specification

#### 4.1.1 ATA Mode Support

SDM4 supports the following ATA operating modes:

- Supports up to PIO Mode-4

- Supports up to Multi-word DMA Mode-2

- Supports up to Ultra DMA Mode-5

#### 4.1.2 Performance

Performances of SDM4 are listed below in table 4-2.

**Table 4-2: Performance (Typical)**

| Performance            | Capacity | 2 GB | 4 GB | 8 GB | 16 GB | 32 GB |

|------------------------|----------|------|------|------|-------|-------|

| Sustained read (MB/s)  |          | 75   | 80   | 80   | 85    | 85    |

| Sustained write (MB/s) |          | 26   | 50   | 50   | 80    | 80    |

Note: Results may differ from various flash configurations.

## 4.2 Environmental Specifications

Environmental specification of SDM4 product family which follows the MIL-STD-202 and MIL-STD-810 standards is available as shown in Table 4-3.

**Table 4-3** SDM4 environmental specifications

| Item                    | Specification                                       |

|-------------------------|-----------------------------------------------------|

| operating temp.         | 0~70(°C) <sup>*1</sup> ; -40~85(°C) <sup>*2</sup>   |

| non-operating temp.     | -40~100(°C)                                         |

| humidity                | 10~95% R.H, non-condensing                          |

| operating vibration     | 10~2000(Hz), 15(G), sine wave, 1(hr)/per axis       |

| non-operating vibration | 20~2000(Hz), 7.7(Grms), random wave, 1(hr)/per axis |

| operating shock         | 50(G), 11(ms), half-sine wave                       |

| non-operating shock     | 1500(G), 0.5(ms), half-sine wave                    |

\*1 : commercial grade

\*2 : industrial grade

## 4.3 Mean Time Between Failures (MTBF)

Mean Time Between Failures (MTBF) is predicted based on reliability data for the individual components in SDM4. Although many component MTBFs are given in databases and often these values are not really accurate, the prediction result for SDM4 is more than 2,000,000 hours.

Notes about the MTBF:

The MTBF is predicated and calculated based on "Telcordia Technologies Special Report, SR-332, Issue 2" method.

## 4.4 Certification and Compliance

SDM4 complies with the following standards:

- CE – EN55022/55024

- FCC 47CFR Part15 Class B

- RoHS

- MIL-STD-202 and MIL-STD-810

- SATA II (SATA Rev. 2.6)

- Up to ATA/ATAPI-7 ( including S.M.A.R.T.)

## 5. Flash Management

### 5.1 Error Correction/Detection

SDM4 implements a hardware ECC scheme, based on the BCH algorithm. It can detect and correct up to 16 bits or 24 bits error in 1K bytes.

### 5.2 Bad Block Management

Although bad blocks on the flash media are already identified by the flash manufacturer, they can also be accumulated over time during operation. SDM4's controller maintains a table that lists those normal blocks with disk data, the free blocks for wear leveling, and bad blocks with errors. When a normal block is detected broken, it is replaced with a free block and listed as a bad block. When a free block is detected broken, it is then removed from the free block list and marked as a bad block.

During device operation, this ensures that newly accumulated bad blocks are transparent to the host. The device will stop file write service once there are only two free blocks left such that the read function is still available for copying the files from the disk into another.

### 5.3 Wear Leveling

The NAND flash devices are limited by a certain number of write cycles. When using a FAT-based file system, frequent FAT table updates are required. If some area on the flash wears out faster than others, it would significantly reduce the lifetime of the whole SSD, even if the erase counts of others are far from the write cycle limit. Thus, if the write cycles can be distributed evenly across the media, the lifetime of the media can be prolonged significantly. This scheme is called wear leveling.

Apacer's wear-leveling scheme is achieved both via buffer management and Apacer-specific static wear leveling. They both ensure that the lifetime of the flash media can be increased, and the disk access performance is optimized as well.

### 5.4 Power Failure Management

The Low Power Detection on the controller initiates crucial data saving before the power supplied to the device is too low. This feature prevents the device from crash and ensures data integrity during an unexpected power-off.

### 5.5 ATA Secure Erase

Accomplished by the Secure Erase (SE) command, which added to the open ANSI standards that control disk drives, "ATA Secure Erase" is built into the disk drive itself and thus far less susceptible to malicious software attacks than external software utilities. It is a positive easy-to-use data destroy command, amounting to electronic data shredding. Executing the command causes a drive to internally completely erase all possible user data. This command is carried out within disk drives, so no additional software is required. Once executed, neither data nor the erase counter on the device would be recoverable, which blurs the accuracy of device lifespan. The process to erase will not be stopped until finished while encountering power failure, and will be continued when power is back on.

---

## 5.6 S.M.A.R.T.

---

S.M.A.R.T. is an acronym for Self-Monitoring, Analysis and Reporting Technology, an open standard allowing disk drives to automatically monitor their own health and report potential problems. It protects the user from unscheduled downtime by monitoring and storing critical drive performance and calibration parameters. Ideally, this should allow taking proactive actions to prevent impending drive failure.

Apacer SDM4 uses the standard SMART command B0h to read data from the drive for SMART feature as the SATA Rev.2.6 ATA/ATAPI-7 specifications. Based on the SFF-8035i Rev. 2.0 specifications, Apacer SMART defines vendor-specified SMART Attribute IDs (A0h, A1h, A2h, A3h, A4h-A5h) in SDM4. They represent initial back block count, bad block count, spare block count, maximum erase count, and average erase counts respectively. When the Apacer SMART Utility running on the host, it analyzes and reports the disk status to the host before SDM4 is in critical condition.

---

## 5.7 TRIM

---

Made of millions of NAND flash cells, SSD can be written into groups called pages in 4K size generally, but can only be erased in larger groups called blocks of 128 pages or 512KB. These stipulations are partially the source of many performance issues. Until an address gets used again, the SSD has to keep track of every last bit of data that's written on it. The ATA-TRIM instruction tilts the balance in favor of the SSD. TRIM addresses a major part of the performance degradation issue over time that plagues all SSDs. A TRIM enabled drive running an OS with TRIM support will stay closer to its peak performance over time.

## 6. Software Interface

### 6.1 Command Set

This section defines the software requirements and the format of the commands the host sends to SDM4. Commands are issued to SDM4 by loading the required registers in the command block with the supplied parameters, and then writing the command code to the Command register.

**Table 6-1:** Command set

| <b>Code</b> | <b>Command</b>               | <b>Code</b> | <b>Command</b>         |

|-------------|------------------------------|-------------|------------------------|

| E5h         | Check Power Mode             | F3h         | Security Erase Prepare |

| 06h         | Data Set Management          | F4h         | Security Erase Unit    |

| 90h         | Execute Device Diagnostic    | F5h         | Security Freeze Lock   |

| E7h         | Flush Cache                  | F1h         | Security Set Password  |

| EAh         | Flush Cache EXT              | F2h         | Security Unlock        |

| Ech         | Identify Device              | 70h         | Seek                   |

| E3h         | Idle                         | Efh         | Set Features           |

| E1h         | Idle Immediate               | C6h         | Set Multiple Mode      |

| 91h         | Initialize Device Parameters | E6h         | Sleep                  |

| C8h         | Read DMA                     | B0h         | SMART                  |

| 25h         | Read DMA EXT                 | E2h         | Standby                |

| C4h         | Read Multiple                | E0h         | Standby Immediate      |

| 29h         | Read Multiple EXT            | Cah         | Write DMA              |

| 20h         | Read Sector                  | 35h         | Write DMA EXT          |

| 24h         | Read Sector EXT              | C5h         | Write Multiple         |

| 40h         | Read Verify Sectors          | 39h         | Write Multiple EXT     |

| 42h         | Read Verify Sectors EXT      | 30h         | Write Sector           |

| 10h         | Recalibrate                  | 34h         | Write Sector EXT       |

| F6h         | Security Disable Password    |             |                        |

## 7. Electrical Specification

**Caution: Absolute Maximum Stress Ratings** – Applied conditions greater than those listed under “Absolute Maximum Stress Ratings” may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these conditions or conditions greater than those defined in the operational sections of this data sheet is not implied. Exposure to absolute maximum stress rating conditions may affect device reliability.

**Table 7-1:** Operating range

| Range                | Ambient Temperature | 5V         |

|----------------------|---------------------|------------|

| Standard             | 0°C to +70°C        |            |

| Extended Temperature | -40°C to 85°C       | 4.75-5.25V |

**Table 7-2:** Absolute maximum power pin stress ratings

| Parameter                                              | Symbol   | Conditions                         |

|--------------------------------------------------------|----------|------------------------------------|

| Input Power                                            | $V_{DD}$ | -0.3V min. to 6.5V max.            |

| Voltage on any pin except $V_{DD}$ with respect to GND | V        | -0.5V min. to $V_{DD} + 0.5V$ max. |

**Table 7-3:** Recommended system power-up timing

| Symbol           | Parameter                   | Typical | Maximum | Units |

|------------------|-----------------------------|---------|---------|-------|

| $T_{PU-READY}^1$ | Power-up to Ready Operation | 200     | 1000    | ms    |

| $T_{PU-WRITE}^1$ | Power-up to Write Operation | 200     | 1000    | ms    |

This parameter is measured only for initial qualification and after a design or process change that could affect this parameter.

**Table 7-4:** Typical power consumption

| Modes | Capacity  | 2 GB | 4 GB | 8 GB | 16 GB | 32 GB |

|-------|-----------|------|------|------|-------|-------|

|       |           | 187  | 224  | 233  | 220   | 230   |

|       | Idle (mA) | 71   | 72   | 72   | 75    | 75    |

Note: Results may differ from various flash configurations.

### 7.1 Electrostatic Discharge

#### Electrostatic discharge

| Item          | Amount of Discharge | Voltage | Required Criteria | Complied To Criteria (A,B,C) |

|---------------|---------------------|---------|-------------------|------------------------------|

| Air Discharge | 10                  | +8kV    | B                 | A                            |

|               | 10                  | -8kV    | B                 | A                            |

|                                |    |      |   |   |

|--------------------------------|----|------|---|---|

| Contact Discharge              | 25 | +4kV | B | A |

|                                | 25 | -4kV | B | A |

| Indirect Discharge (HCP)       | 25 | +4kV | B | A |

|                                | 25 | -4kV | B | A |

| Indirect Discharge (VCP Front) | 25 | +4kV | B | A |

|                                | 25 | -4kV | B | A |

| Indirect Discharge (VCP Left)  | 25 | +4kV | B | A |

|                                | 25 | -4kV | B | A |

| Indirect Discharge (VCP Back)  | 25 | +4kV | B | A |

|                                | 25 | -4kV | B | A |

| Indirect Discharge (VCP Right) | 25 | +4kV | B | A |

|                                | 25 | -4kV | B | A |

## 7.2 Electrical Fast Transient/Burst

### Electrical Fast Transient/Burst

| Inject Line | Polarity | Voltage kV | Inject Time (Second) | Inject Method | Required Criteria | Complied to Criteria |

|-------------|----------|------------|----------------------|---------------|-------------------|----------------------|

| L-N-PE      | ±        | 1kV        | 60                   | Direct        | B                 | A                    |

### Notes about Electrostatic Discharge & Electrical Fast Transient/Burst

The tests performed are from lowest level up to the highest level as required by standard, but only highest level is shown on the report.

Meet criteria A: Operate as intended during and after the test

Meet criteria B: Operate as intended after the test

Meet criteria C: Loss/Error of function

Additional Information:

EUT stopped operation and could / could not be reset by operator at kV.

No false alarms or other malfunctions were observed during or after the test.

The Contact discharges were applied at least total 200 discharges at a minimum of four test points.

## 8. Physical Characteristics

### 8.1 Power Cable Type

## 8.2 Power Cable-less Type

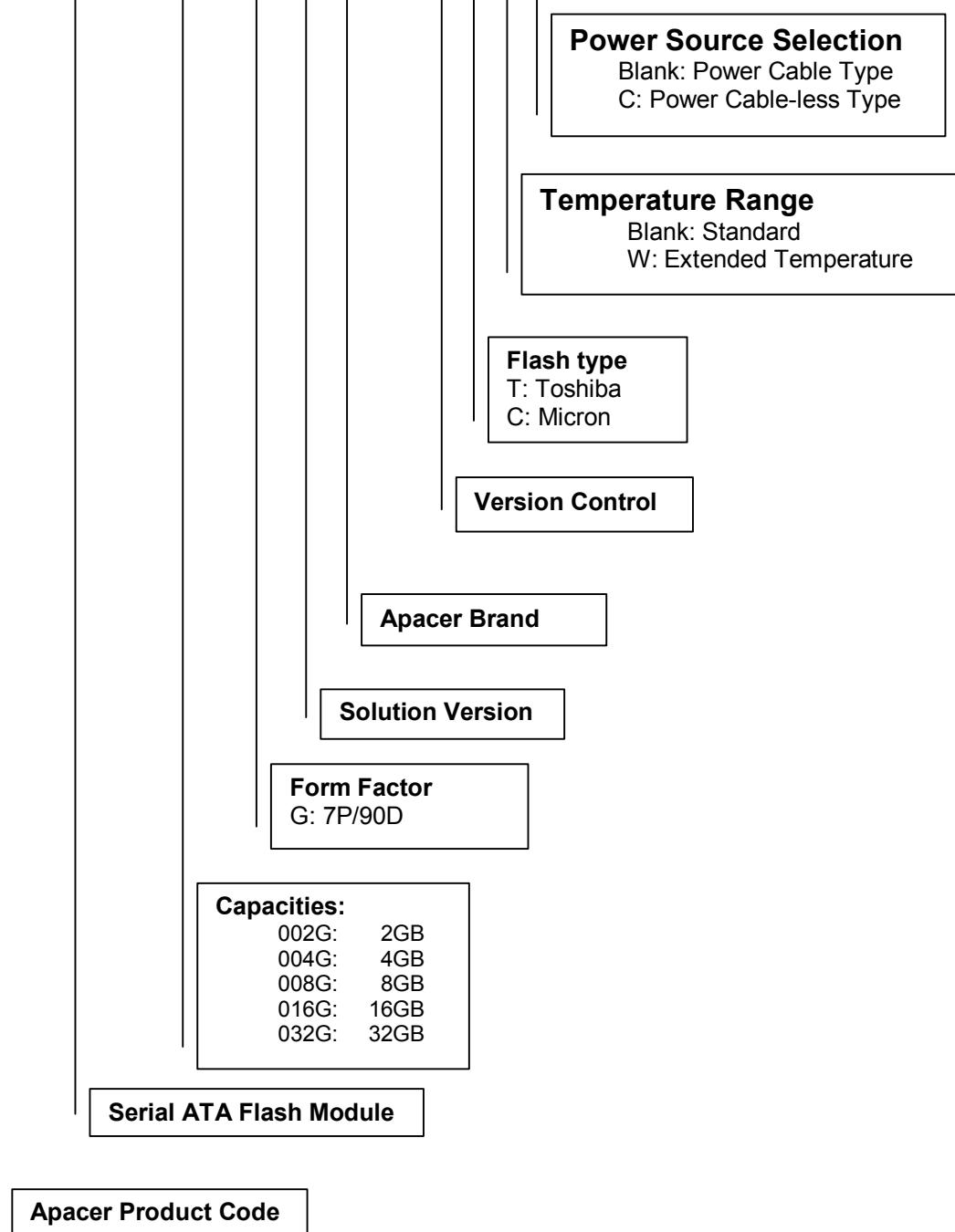

## 9. Product Ordering Information

### 9.1 Product Code Designations

AP SDM x x x x G 5 AN - A X X X

## 9.2 Valid Combinations

### 7P/90D MP: Power Cable Type

| Capacity | Standard         | Extended Temperature |

|----------|------------------|----------------------|

| 2GB      | APSDM002GG5AN-AT | APSDM002GG5AN-ATW    |

| 4GB      | APSDM004GG5AN-AT | APSDM004GG5AN-ATW    |

| 8GB      | APSDM008GG5AN-AT | APSDM008GG5AN-ATW    |

| 16GB     | APSDM016GG5AN-AC | APSDM016GG5AN-ACW    |

| 32GB     | APSDM032GG5AN-AC | APSDM032GG5AN-ACW    |

### 7P/90D MP: Power Cable-less Type

| Capacity | Standard          | Extended Temperature |

|----------|-------------------|----------------------|

| 2GB      | APSDM002GG5AN-ATC | APSDM002GG5AN-ATWC   |

| 4GB      | APSDM004GG5AN-ATC | APSDM004GG5AN-ATWC   |

| 8GB      | APSDM008GG5AN-ATC | APSDM008GG5AN-ATWC   |

| 16GB     | APSDM016GG5AN-ACC | APSDM016GG5AN-ACWC   |

| 32GB     | APSDM032GG5AN-ACC | APSDM032GG5AN-ACWC   |

**Note:** Valid combinations are those products in mass production or will be in mass production. Consult your Apacer sales representative to confirm availability of valid combinations and to determine availability of new combinations.

---

## Revision History

| Revision | Date       | Description                                                                                          | Remark |

|----------|------------|------------------------------------------------------------------------------------------------------|--------|

| 1.0      | 12/02/2011 | Official release                                                                                     |        |

| 1.1      | 1/17/2012  | Revised capacity information<br>Updated Product Ordering Information<br>Added Power cable-less model |        |

## Global Presence

### Taiwan (Headquarters)

**Apacer Technology Inc.**

4<sup>th</sup> Fl., 75 Hsin Tai Wu Rd., Sec.1

Hsichih, New Taipei City

Taiwan 221

R.O.C.

Tel: +886-2-2698-2888

Fax: +886-2-2698-2889

[amtsales@apacer.com](mailto:amtsales@apacer.com)

### U.S.A.

**Apacer Memory America, Inc.**

386 Fairview Way, Suite102,

Milpitas, CA 95035

Tel: 1-408-518-8699

Fax: 1-408-935-9611

[sa@apacerus.com](mailto:sa@apacerus.com)

### Japan

**Apacer Technology Corp.**

5F, Matsura Bldg., Shiba, Minato-Ku

Tokyo, 105-0014, Japan

Tel: 81-3-5419-2668

Fax: 81-3-5419-0018

[jpservices@apacer.com](mailto:jpservices@apacer.com)

### Europe

**Apacer Technology B.V.**

Science Park Eindhoven 5051 5692 EB Son,

The Netherlands

Tel: 31-40-267-0000

Fax: 31-40-267-0000#6199

[sales@apacer.nl](mailto:sales@apacer.nl)

### China

**Apacer Electronic (Shanghai) Co., Ltd**

1301, No.251,Xiaomuqiao Road, Shanghai,

200032, China

Tel: 86-21-5529-0222

Fax: 86-21-5206-6939

[sales@apacer.com.cn](mailto:sales@apacer.com.cn)

### India

**Apacer Technologies Pvt Ltd,**

#1064, 1st Floor, 7th 'A' Main,

3rd Block Koramangala, Bangalore – 560 034

Tel: +91 80 4152 9061/62/63

Fax: +91 80 4170 0215

[sales\\_india@apacer.com](mailto:sales_india@apacer.com)

# Mouser Electronics

Authorized Distributor

Click to View Pricing, Inventory, Delivery & Lifecycle Information:

[Apacer](#):

[APSDM002GG5AN-AT](#) [APSDM004GG5AN-AT](#) [APSDM008GG5AN-AT](#) [APSDM016GG5AN-AC](#) [APSDM032GG5AN-AC](#)

[APSDM002GG5AN-ATW](#) [APSDM004GG5AN-ATW](#) [APSDM008GG5AN-ATW](#) [APSDM016GG5AN-ACW](#)

[APSDM032GG5AN-ACW](#)