#### DISTINCTIVE CHARACTERISTICS

- 1024 x 4 organization

- High speed 20 ns Max. access time

- Separate data inputs and outputs

- · Memory reset function

- High density SLIM 24-pin 300-MIL package

- Three-state output buffers

- Single +5 V power supply ±10%

- Low-power version

#### GENERAL DESCRIPTION

The Am9150 is a high-performance, static, n-channel, read/write, random-access memory organized as 1024 x 4. It features single 5 V supply operation, TTL-compatible input and output levels, and separate input and output pins for improved system performance and ease of use.

The Am9150 also incorporates a reset feature which will reset the entire contents of the memory to logical LOW in two cycle times by controlling  $\overline{R}$  ( $\overline{RESET}$ ) and  $\overline{S}$  ( $\overline{CS}$ ).

The Am9150 has four control signals  $\overline{\mathbb{N}}$ ,  $\overline{\mathbb{S}}$ ,  $\overline{\mathbb{W}}$  and  $\overline{\mathbb{G}}$ . The  $\overline{\mathbb{S}}$  input controls read, write and reset operations of the device and provides for easy selection of an individual device when the outputs are tied together. The  $\overline{\mathbb{W}}$  ( $\overline{\mathbb{W}}$ E) input controls the normal read and write operations, and the  $\overline{\mathbb{G}}$  ( $\overline{\mathbb{OE}}$ ) controls the state of the outputs.

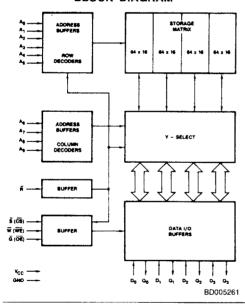

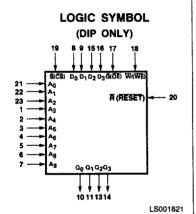

#### **BLOCK DIAGRAM**

#### MODE SELECT TABLE

| Inputs |       |      |       |                                                                   |                                                           |

|--------|-------|------|-------|-------------------------------------------------------------------|-----------------------------------------------------------|

| S      | W     | G    | R     | Outputs                                                           | Mode                                                      |

| HLLLL  | XHLHX | XXLH | XLHHH | Hi-Z<br>Hi-Z<br>Hi-Z<br>Q <sub>0</sub> - Q <sub>3</sub><br>Hi-Z , | Not Selected<br>Reset*<br>Write<br>Read<br>Output Disable |

H = High \*See Reset cycle description.

X = Don't Care

#### PRODUCT SELECTOR GUIDE

| Part Number   |                 | Am9150-20 Am9150-2 |     | Am9150-35 | Am9150-45 | Am91L50-25 | Am91L50-35 | Am91L50-45 |

|---------------|-----------------|--------------------|-----|-----------|-----------|------------|------------|------------|

| Maximum Acces | ss Time (ns)    | 20                 | 25  | 35        | 45        | 25         | 35         | 45         |

| 1 Man (-A)    | 0°C to +70°C    | 180                | 180 | 180       | 180       | 130        | 130        | 130        |

| ICC Max. (mA) | -55°C to +125°C | N/A                | 180 | 180       | 180       | N/A        | N/A        | N/A        |

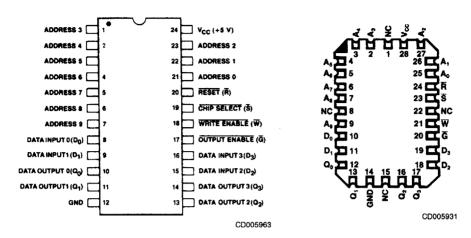

## CONNECTION DIAGRAMS Top View

Note: Pin 1 is marked for orientation.

АХэ

AX<sub>4</sub>

AX5 AY0

AY<sub>1</sub>

AY<sub>2</sub>

A<sub>2</sub>

A<sub>4</sub>

A<sub>5</sub>

Α6

A<sub>7</sub>

Ag

# Address Designators External Internal A<sub>0</sub> A<sub>X<sub>0</sub></sub> A<sub>1</sub> A<sub>X1</sub> A<sub>2</sub> A<sub>X2</sub>

**METALLIZATION AND PAD**

LAYOUT

Die Size: 0.93" x 0.163"

**4-54** Am9150

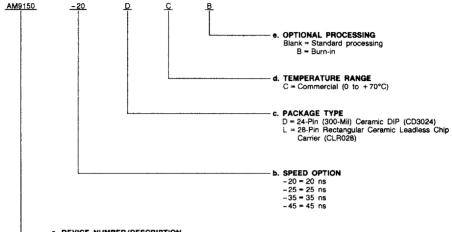

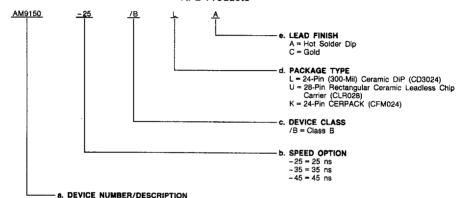

#### ORDERING INFORMATION

#### Standard Products

AMD standard products are available in several packages and operating ranges. The order number (Valid Combination) is formed by a combination of: a. Device Number

- b. Speed Option (if applicable)

- c. Package Type

- d. Temperature Range

- e. Optional Processing

a. DEVICE NUMBER/DESCRIPTION Am9150/Am91L50 1024 x 4 High-Speed Static R/W RAM Am91L50 = Low-Power Version

| Valid Combinations |          |  |  |  |  |  |  |  |  |  |

|--------------------|----------|--|--|--|--|--|--|--|--|--|

| AM9150-20          |          |  |  |  |  |  |  |  |  |  |

| AM9150-25          |          |  |  |  |  |  |  |  |  |  |

| AM9150-35          | DC, DCB, |  |  |  |  |  |  |  |  |  |

| AM9150-45          | LC, LCB  |  |  |  |  |  |  |  |  |  |

| AM91L50-25         |          |  |  |  |  |  |  |  |  |  |

| AM91L50-35         |          |  |  |  |  |  |  |  |  |  |

| AM91L50-45         |          |  |  |  |  |  |  |  |  |  |

#### Valid Combinations

Valid Combinations list configurations planned to be supported in volume for this device. Consult MSIS sales department to confirm availability of specific valid combinations, and to obtain additional data on MSIS's standard military grade products.

#### MILITARY ORDERING INFORMATION

#### **APL Products**

AMD products for Aerospace and Defense applications are available in several packages and operating ranges. APL (Approved Products List) products are fully compliant with MIL-STD-983C requirements. The order number (Valid Combination) for APL products is formed by a combination of: a. Device Number

- b. Speed Option (if applicable)

- c. Device Class

- d. Package Type

- e. Lead Finish

#### **APL Products**

Valid Combinations

AM9150-25

/BLA

AM9150-35

/BUC

/BKA

/BKA

Am9150

1024 x 4 High-Speed Static R/W RAM

#### Valid Combinations

Valid Combinations list configurations planned to be supported in volume for this device. Consult MSIS sales department to confirm availability of specific valid combinations, and to obtain additional data on MSIS's standard military grade products.

#### **Group A Tests**

Group A tests consist of Subgroups 1, 2, 3, 7, 8, 9, 10, 11.

#### PIN DESCRIPTION

#### A<sub>0</sub> - A<sub>9</sub> Address (Inputs)

AM9150-45

The 10 address inputs select one of the 1024 4-bit words in the RAM.

#### S Chip Select (Input; Active LOW)

An active-LOW input which selects the device for operation. When  $\overline{S}$  is HIGH, the device is deselected and the outputs will be in a high-impedance state.

#### Write Enable (Input; Active LOW)

$\overline{W}$  controls read and write operations. When  $\overline{W}$  is HiGH and  $\overline{G}$  is LOW, data will be present at the data outputs. When  $\overline{W}$  is LOW, data present on the data inputs will be written into the selected memory location. The data outputs will be in a high-impedance state.

#### RESET (Input; Active LOW)

An active-Low pulse on  $\overline{R}$  while  $A_0 - A_9$  are stable,  $\overline{S}$  is LOW, and  $\overline{W}$  and  $\overline{G}$  are HIGH resets the whole memory.

#### G Output Enable (Input; Active LOW)

$\overline{S}$  controls the state of the data outputs in conjunction with  $\overline{S}$  and  $\overline{W}$ .

#### D<sub>0</sub> - D<sub>3</sub> Data Input

Data inputs to the RAM.

#### Q<sub>0</sub> - Q<sub>3</sub> Data Output

Data outputs from the RAM. The data outputs will be in a high-impedance state when either  $\overline{S}$  or  $\overline{G}$  are HIGH or  $\overline{W}$  is LOW.

V<sub>CC</sub> Power Supply +5 Volts

V<sub>SS</sub> Ground

#### ABSOLUTE MAXIMUM RATINGS (Note 1) Storage Temperature ......-65 to +150°C Ambient Temperature with Power Applied ...... -55 to +125°C Supply Voltage with Respect to Ground.....-0.5 V to +7.0 V Signal Voltages with Respect to Ground......-3.5 V to +7.0 V Power Dissipation (Package Limitation) ...................... 1.2 W

The products described by this specification include internal circuitry designed to protect input devices from damaging accumulations of static charge. It is suggested nevertheless, that conventional precautions be observed during storage, handling and use in order to avoid exposure to excessive voltages.

#### **OPERATING RANGES** (Note 2)

|                      | (T <sub>A</sub> ) 0 to +70°C+5.0 V ±10% |

|----------------------|-----------------------------------------|

| Military (M) Devices |                                         |

| Ambient Temperature  | (T <sub>A</sub> )55 to +125°C           |

|                      | +5.0 V ±10%                             |

Operating ranges define those limits between which the functionality of the device is guaranteed.

DC CHARACTERISTICS over operating ranges unless otherwise specified (for APL Products, Group A, Subgroups 1, 2, 3 are tested unless otherwise noted)

| Parameter       | Parameter                                   |                                                                  |        | Am   | 9150 | Am9  | 1    |    |

|-----------------|---------------------------------------------|------------------------------------------------------------------|--------|------|------|------|------|----|

| Symbol          | Description                                 | Test Condition                                                   | Min.   | Max. | Min. | Max. | Unit |    |

| <sup>ј</sup> ОН | Output HIGH Current                         | V <sub>OH</sub> = 2.4 V                                          |        | 4    |      | -4   |      | mA |

| <sup>l</sup> OL | Output LOW Current                          | V <sub>OL</sub> = 0.4 V                                          |        | 12   |      | 12   |      | mA |

| VIH             | Input HIGH Voltage                          |                                                                  |        | 2.2  | 6.0  | 2.2  | 6.0  | V  |

| VIL             | Input LOW Voltage                           | GND ≤ V <sub>I</sub> ≤ V <sub>CC</sub>                           |        | -2.5 | 0.8  | -2.5 | 0.8  | V  |

| liX             | Input Load Current                          |                                                                  |        | -10  | 10   | -10  | 10   | μΑ |

| loz             | Output Leakage Current                      | GND ≤ V <sub>O</sub> ≤ V <sub>CC</sub> Output Disabled           |        | ~ 10 | 10   | -10  | 10   | μΑ |

| Ci              | Input Capacitance                           | Test Frequency ≈ 1.0 MHz T <sub>A</sub> = 25°C. All Pins at 0 V. |        |      | 5    |      | 5    |    |

| Со              | Output Capacitance                          | V <sub>CC</sub> = 5 V (Note 8)                                   | ',     |      | 7    |      | 7    | pF |

| 1               | Vac Operation County                        | 10                                                               | COM'L. |      | 180  |      | 130  |    |

| Icc             | V <sub>CC</sub> Operating Supply<br>Current | Max V <sub>CC</sub> \$ ≤ V <sub>IL</sub> Output MIL              |        |      | 180  |      | N/A  | mA |

| los             | Output Short Circuit Current                | GND ≤ V <sub>O</sub> ≤ V <sub>CC</sub> (Notes                    | 7, B)  | ±50  | ±300 | ±50  | ±300 | mA |

Notes: 1. Absolute Maximum Ratings are intended for user guidelines and are not tested.

- 2. For test and correlation purposes, ambient temperature is defined as the "instant-ON" case temperature.

- 2. For less and correlation purposes, ambient temperature is defined as the "instant-ON" case temperature.

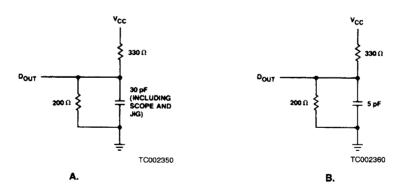

3. Test conditions assume signal transition times of 10 ns or less, timing reference levels of 1.5 V, input pulse levels of 0 to 3.0 V and output loading of the specified |<sub>OL</sub>/|<sub>OH</sub> and 30 pF load capacitance. Output timing reference is 1.5 V.

4. The internal write time of the memory is defined by the overlap of \$\frac{5}{5}\$ LOW and \$\widetilde{W}\$ LOW. Both signals must be LOW to initiate a write and either signal can terminate a write by going HIGH. The data input setup and hold timing is referenced to the rising edge of the signal that terminates the write. \$\widetilde{R}\$ must be HIGH.

- 5. Transition is measured at 1.5 V on the inputs to VOH 500 mV and VOL + 500 mV on the outputs using the load shown in B. under Switching Test Circuits.

6. W and R are HIGH for read cycle.

- 7. For test purposes, not more than one output at a time should be shorted. Short circuit test duration should not exceed 30 seconds.

- 8. This parameter is not tested, but guaranteed by characterization.

**SWITCHING CHARACTERISTICS** over operating ranges unless otherwise specified (for APL Products, Group A, Subgroups 9, 10, 11 are tested unless otherwise noted)

|       | Parameter<br>Symbol |                  |                                                   |                                         | Am9150-20 |          | Am9150-25<br>Am91L50-25 |          | Am9150-35<br>Am91L50-35 |          | Am9150-45<br>Am91L50-45 |          |            |

|-------|---------------------|------------------|---------------------------------------------------|-----------------------------------------|-----------|----------|-------------------------|----------|-------------------------|----------|-------------------------|----------|------------|

| No.   | Standard            | Alternate        | Parameter<br>Description                          |                                         | Min.      | Max.     | Min.                    | Max.     | Min.                    | Max.     | Min.                    | Max.     | Uni        |

| READ  | CYCLE               |                  |                                                   | •                                       |           |          | •                       |          |                         |          |                         |          |            |

| 1     | TAVAV               | tBC              | Read Cycle Time (Note 6                           | 6)                                      | 20        | 1        | 25                      | 1        | 35                      |          | 45                      |          | ns         |

| 2     | TAVQV               | taa              | Address Access Time                               |                                         |           | 20       | <b>!</b>                | 25       |                         | 35       |                         | 45       | ns         |

| 3     | TSLQV               | tACS             | Chip Select Access Time                           |                                         |           | 10       | t                       | 15       |                         | 20       | <b>!</b>                | 25       | ns         |

| 4     | TGLQV               | toe              | Output Enable Access Ti                           |                                         |           | 10       | 1                       | 15       |                         | 20       | <b>!</b>                | 25       | ns         |

| 5     | TSLQX               | tCLZ             | Chip Select LOW to Outp<br>Low-Z (Notes 5, 8)     |                                         | 0         |          | 0                       |          | 0                       |          | 0                       |          | ns         |

| 6     | TSHQZ               | tCHZ             | Chip Select HIGH to Out<br>Hi-Z (Notes 5, 8)      | tput in                                 | 0         | 15       | 0                       | 20       | 0                       | 25       | 0                       | 30       | ns         |

| 7     | TGLQX               | <sup>t</sup> OLZ | Output Enable LOW to O Low-Z (Note 5, 8)          | Output in                               | 0         |          | 0                       |          | 0                       |          | 0                       |          | ns         |

| 8     | TGHQZ               | tонz             | Output Enable HIGH to C<br>Hi-Z (Notes 5, 8)      | Output in                               | 0         | 15       | 0                       | 20       | 0                       | 25       | 0                       | 30       | ns         |

| 9     | TAXQX               | <sup>t</sup> OHA | Output Hold after                                 | COM'L.                                  | 3         | ļ        | 3                       |          | 3                       | <u> </u> | 3                       | ļ        | ns         |

|       | <u> </u>            | <u> </u>         | Address Change                                    | MIL.                                    | 1         | <u> </u> | 1                       | 1        | 1                       | l        | 1                       | <u> </u> | Ш.         |

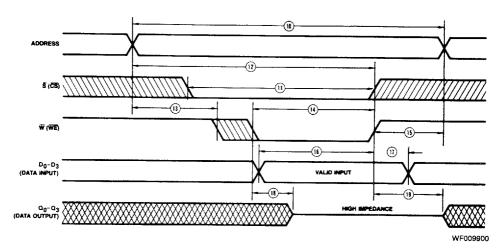

| WRITE | CYCLE               |                  |                                                   |                                         |           |          |                         |          |                         |          |                         |          |            |

| 10    | TAVAV               | twc              | Write Cycle Time (Note                            | 4)                                      | 20        | T        | 25                      |          | 35                      |          | 45                      |          | ns         |

| 11    | TSLWH               | tcw              | Chip Select LOW to Write Enable HIGH              |                                         | 10        |          | 15                      |          | 20                      |          | 30                      |          | ns         |

| 12    | TAVWH               | taw              | Address Valid to End of Write                     |                                         | 15        |          | 20                      |          | 30                      |          | 40                      |          | ns         |

| 13    | TAVWL               | tas              | Address Valid to Beginning of Write               |                                         | 5         |          | 5                       |          | 5                       |          | 5                       |          | ns         |

| 14    | TWLWH               | twp              | Write Pulse Width                                 |                                         | 10        |          | 15                      |          | 20                      |          | 30                      |          | ns         |

| 15    | TWHAX               | twn              | Address Hold after End of Write                   |                                         | 5         |          | 5                       |          | 5                       |          | 5                       |          | ns         |

| 16    | TDVWH               | t <sub>DW</sub>  | Data in Valid to Write Enable<br>HIGH             |                                         | 10        |          | 15                      |          | 20                      |          | 30                      | ļ        | ns         |

| 17    | TWHDX               | t <sub>DH</sub>  | Data Hold after End of                            | Write                                   | 5         | <u></u>  | 5                       |          | 5                       |          | 5                       |          | ns         |

| 18    | TWLQZ               | twz              | Write Enable LOW to Output in Hi-Z (Notes 5, 8)   |                                         | °         | 15       | 0                       | 20       | 0                       | 25       | 0                       | 30       | ns         |

| 19    | TWHQX               | tow              | Write Enable HIGH to Output in Low-Z (Notes 5, 8) |                                         | 0         |          | 0                       | <u> </u> | 0                       |          | 0                       |          | ns         |

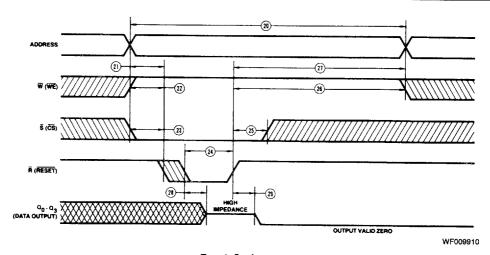

| RESE  | T CYCLE             |                  |                                                   |                                         |           |          |                         |          |                         |          |                         |          |            |

| 20    | TAVAV               | †RRC             | Reset Cycle Time                                  |                                         | 40        |          | 50                      |          | 70                      |          | 90                      |          | ns         |

| 21    | TAVRL               | tRSA             | Address Valid to Beginn<br>Reset                  | ning of                                 | 0         |          | 0                       |          | °                       |          | 0                       |          | ns         |

| 22    | TWHRL               | trsw             | of Reset                                          | Write Enable HIGH to Beginning of Reset |           |          | 0                       |          | 0                       |          | °                       |          | n:         |

| 23    | TSLRL               | trscs            | Chip Select LOW to Beginning of<br>Reset          |                                         | 0         | ļ        | 0                       |          | 0                       |          | 0                       |          | n:         |

| 24    | TRLRH               | tRP              | Reset Pulse Width                                 |                                         | 20        |          | 20                      |          | 30                      | 1        | 40                      | <b></b>  | n:         |

| 25    | TRHSX               | tRHCS            | Chip Select Hold after End of Reset               |                                         | 0         |          | 0                       |          | 0                       |          | 0                       |          | ns         |

| 26    | TRHWL               | tahw             | Write Enable Hold after End of Reset              |                                         | 20        | -        | 30                      | -        | 40                      | -        | 50                      | -        | n:         |

| 27    | TRHAX               | trha .           | Address Hold after End                            |                                         | 20        | 1 45     | 30                      | 100      | 0                       | 25       | 0                       | 35       | +          |

| 28    | TRLOZ               | t <sub>RHZ</sub> | Reset LOW to Output in<br>(Notes 5, 8)            |                                         | 0         | 15       | 0                       | 20       | 0                       | 25       | 1 0                     | 35       | n          |

| 29    | TRHQX               | tRLZ             | Reset HIGH to Output (Notes 5, 8)                 | iri LOW-Z                               | <u> </u>  |          |                         |          | L                       |          |                         |          | <u>L</u> " |

|       |                     |                  |                                                   |                                         |           |          |                         |          |                         |          |                         |          |            |

Notes: See notes following DC Characteristics table.

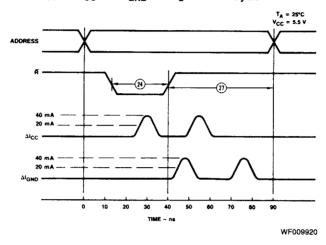

#### RESET CYCLE

The reset cycle is initiated by  $\overline{R}$  going LOW for a time  $\geq$  t<sub>RP</sub>, and is terminated by holding  $\overline{R}$  HIGH for a time  $\geq$  t<sub>RHA</sub>. The addresses to the device must be stable during the RESET cycle time. The entire contents of the RAM will be reset to ZERO regardless of the address chosen during the cycle. The

control  $\overline{S}$  must be  $\leqslant$  V<sub>IL</sub> maximum, and  $\overline{W}$  must be  $\geqslant$  V<sub>IH</sub> minimum and it is recommended that  $\overline{G}$  be  $\geqslant$  V<sub>IH</sub> minimum.

The reset cycle is normally associated with current spikes, both at  $V_{CC}$  and GND as shown in the graph. To attenuate the current spikes, an external bypass capacitor (high frequency, 0.1  $\mu$ F) for each Am9150 socket is recommended.

#### Typical I<sub>CC</sub> and I<sub>GND</sub> During a Reset Cycle

#### SWITCHING TEST CIRCUITS

Am9150 4-59

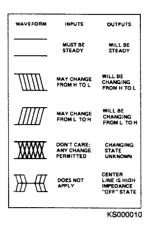

# SWITCHING WAVEFORMS KEY TO SWITCHING WAVEFORMS

**①**

WF009890

Read Cycle

**4-60** Am9150

### SWITCHING WAVEFORMS (Cont'd.)

Write Cycle

**Reset Cycle**