# HGTD8P50G1, HGTD8P50G1S

May 1996

# 8A, 500V P-Channel IGBTs

#### **Features**

- 8A, 500V

- 3.7V V<sub>CE(SAT)</sub>

- Typical Fall Time 1800ns

- · High Input Impedance

- $T_J = +150^{\circ}C$

#### Description

The HGTD8P50G1 and the HGTD8P50G1S are P-channel enhancement-mode insulated gate bipolar transistors (IGBTs) designed for high voltage, low on-dissipation applications such as switching regulators and motor drives. This P- channel IGBT can be paired with N-Channel IGBTs to form a complementary power switch and it is ideal for half bridge circuit configurations. These types can be operated directly from low power integrated circuits.

#### **PACKAGING AVAILABILITY**

| PART NUMBER | PACKAGE  | BRAND  |  |

|-------------|----------|--------|--|

| HGTD8P50G1  | TO-251AA | G8P50G |  |

| HGTD8P50G1S | TO-252AA | G8P50G |  |

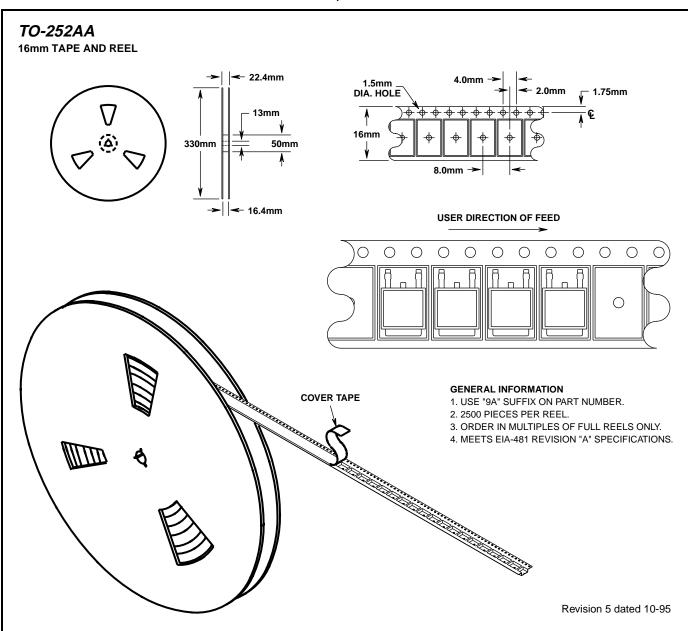

NOTE: When ordering, use the entire part number. Add the suffix 9A to obtain the TO-252AA variant in the tape and reel, i.e., HGTD8P50G1S9A.

The development type number for these devices is TA49015.

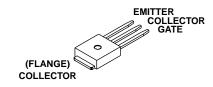

#### **Package**

#### JEDEC TO-251AA

#### **JEDEC TO-252AA**

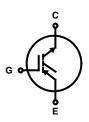

### Symbol

HCTD9D50C1/C19

### **Absolute Maximum Ratings** T<sub>C</sub> = +25°C, Unless Otherwise Specified

|                                                                      | HG1D8P50G1/G1S | UNITS |

|----------------------------------------------------------------------|----------------|-------|

| Collector-Emitter Breakdown Voltage                                  | -500           | V     |

| Emitter-Collector Breakdown Voltage                                  | 10             | V     |

| Collector Current Continuous                                         |                |       |

| At $T_C = +25^{\circ}C$ $I_{C25}$                                    | -12            | Α     |

| At $T_C = +90^{\circ}C$ $I_{C90}$                                    | -8             | Α     |

| Collector Current Pulsed (Note 1)                                    | -18            | Α     |

| Gate-Emitter Voltage ContinuousV <sub>GES</sub>                      | ±20            | V     |

| Gate-Emitter Voltage Pulsed                                          | ±30            | V     |

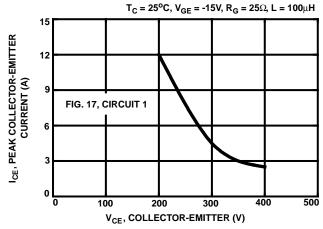

| Switching SOA at T <sub>C</sub> = +25°C, V <sub>CL</sub> = -350VSSOA |                |       |

| No Snubber, Figure 17 - Circuit 1                                    | -3             | Α     |

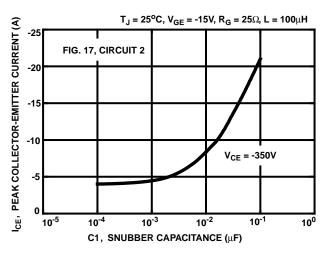

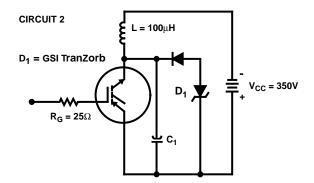

| With 0.1μF Capacitor, Figure 17 - Circuit 2                          | -18            | Α     |

| Power Dissipation Total at $T_C = +25^{\circ}C$ $P_D$                | 66             | W     |

| Power Dissipation Derating T <sub>C</sub> > +25°C                    | 0.53           | W/°C  |

| Operating and Storage Junction Temperature                           | -40 to +150    | °C    |

| Maximum Lead Temperature for Soldering                               | +260           | °C    |

NOTE:

1.  $T_J = 25^{\circ}C$ ,  $V_{CL} = 350V$ ,  $R_{GE} = 25\Omega$ , Figure 17 - Circuit 2 ( $C_1 = 0.1 \mu F$ )

LIMITS

# Specifications HGTD8P50G1, HGTD8P50G1S

**Electrical Specifications**  $T_C = +25^{\circ}C$ , Unless Otherwise Specified

| PARAMETERS                           | SYMBOL                | TEST CONDITIONS                                     |                                                                                               | MIN  | TYP  | MAX  | UNIT |

|--------------------------------------|-----------------------|-----------------------------------------------------|-----------------------------------------------------------------------------------------------|------|------|------|------|

| Collector-Emitter Breakdown Voltage  | BV <sub>CES</sub>     | I <sub>CE</sub> = -250μA<br>V <sub>CL</sub> = -600V | V <sub>GE</sub> = 0V                                                                          | -500 | -    | -    | V    |

| Emitter-Collector Breakdown Voltage  | BV <sub>ECS</sub>     | I <sub>EC</sub> = 1mA                               | V <sub>GE</sub> = 0V                                                                          | 10   | -    | -    | ٧    |

| Collector-Emitter Leakage Current    | I <sub>CES</sub>      | V <sub>CE</sub> = BV <sub>CES</sub>                 | $T_{C} = +25^{\circ}C$                                                                        | -    | -    | -250 | μΑ   |

|                                      |                       | V <sub>CE</sub> = 0.8 BV <sub>CES</sub>             | $T_{C} = +150^{\circ}C$                                                                       | -    | -    | -1.0 | mA   |

| Collector-Emitter Saturation Voltage | V <sub>CE(SAT)</sub>  | I <sub>CE</sub> = -3.0A                             | $T_{C} = +25^{\circ}C$                                                                        | -    | -2.5 | -2.9 | V    |

|                                      |                       | V <sub>GE</sub> = -15V                              | T <sub>C</sub> = +150°C                                                                       | -    | -2.3 | -2.8 | ٧    |

|                                      |                       | I <sub>CE</sub> = I <sub>C90</sub>                  | $T_{C} = +25^{\circ}C$                                                                        | -    | -3.0 | -3.7 | ٧    |

|                                      |                       | V <sub>GE</sub> = -15V                              | T <sub>C</sub> = +150°C                                                                       | -    | -3.3 | -4.0 | ٧    |

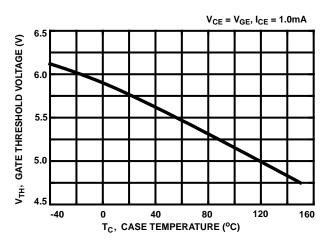

| Gate-Emitter Threshold Voltage       | V <sub>GE(TH)</sub>   | I <sub>CE</sub> = -1.0mA                            | V <sub>CE</sub> = V <sub>GE</sub>                                                             | -4.5 | -6.0 | -7.5 | ٧    |

| Gate-Emitter Leakage Current         | I <sub>GES</sub>      | V <sub>GE</sub> = ±20V                              |                                                                                               | -    | -    | ±100 | nA   |

| Gate-Emitter Plateau Voltage         | V <sub>GE(PL)</sub>   | I <sub>C</sub> = 3A                                 | V <sub>CE</sub> = 0.5 BV <sub>CES</sub>                                                       | -    | -7.0 | -    | ٧    |

| On-State Gate Charge                 | Q <sub>G(ON)</sub>    | $I_C = 3A$ ,<br>$V_{CE} = 0.5 \text{ BV}_{CES}$     | V <sub>GE</sub> = -15V                                                                        | -    | 16   | 25   | nC   |

|                                      |                       |                                                     | V <sub>GE</sub> = -20V                                                                        | -    | 22   | 30   | nC   |

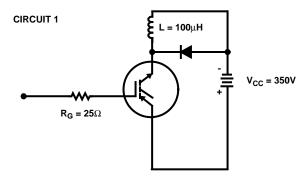

| Current Turn-On Delay Time           | t <sub>D(ON)I</sub>   | $R_L = 113\Omega$                                   | I <sub>CE</sub> = -3A,                                                                        | -    | 45   | -    | ns   |

| Current Rise Time                    | t <sub>RI</sub>       |                                                     | $V_{GE} = -15V$ $V_{CE} = -350V$                                                              | -    | 85   | -    | ns   |

| Current Turn-off Delay Time          | t <sub>D(OFF)</sub> I | L = 100μH                                           | $R_G = 25\Omega$<br>$T_J = +150^{\circ}C$                                                     | -    | 480  | 680  | ns   |

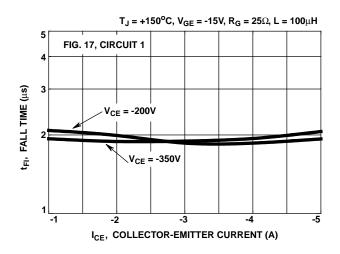

| Current Fall Time                    | t <sub>FI</sub>       |                                                     | Fig. 17, Circuit 1                                                                            | -    | 1800 | 2500 | ns   |

| Turn-Off Energy (Note 1)             | E <sub>OFF</sub>      |                                                     |                                                                                               | -    | 0.8  | -    | mJ   |

| Current Turn-Off Delay Time          | t <sub>D(OFF)</sub> I | L = 100μH                                           | I <sub>CE</sub> = -8A,                                                                        | -    | 100  | 200  | ns   |

| Current Fall Time                    | t <sub>FI</sub>       |                                                     | $V_{GE} = -15V$ $V_{CE} = -350V$                                                              | -    | 3500 | 4000 | ns   |

| Turn-Off Energy (Note 1)             | E <sub>OFF</sub>      |                                                     | $R_G = 25\Omega$ $T_J = +150^{\circ}C$ Fig. 17, Circuit 2 $C_1 = .022\mu F$                   | -    | 1.3  | -    | mJ   |

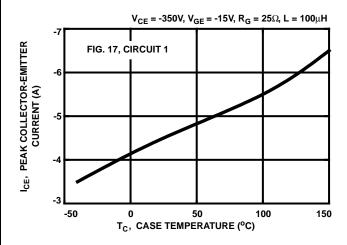

| Latching Current                     | IL                    | L = 100μH                                           | $V_{GE} = -15V$ $R_{G} = 25\Omega$ $T_{J} = +25^{\circ}C$ $V_{CE} = -350V$ Fig. 17, Circuit 1 | -3   | -    | -    | А    |

| Thermal Resistance                   | $R_{\theta JC}$       |                                                     |                                                                                               | -    | 1.75 | 1.90 | °C/W |

#### NOTE:

Turn-Off Energy Loss (E<sub>OFF</sub>) is defined as the integral of the instantaneous power loss starting at the trailing edge of the input pulse and ending at the point where the collector current equals zero (I<sub>CE</sub> = 0A). The HGTD8P50G1 and HGTD8P50G1S were tested per JEDEC standard No. 24-1 Method for Measurement of Power Device Turn-Off Switching Loss. This test method produces the true total Turn-Off Energy Loss. Turn-On losses include diode losses.

# Typical Performance Curves

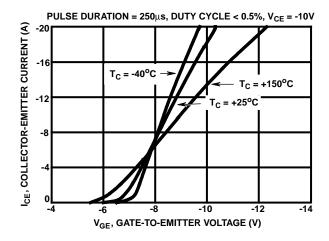

FIGURE 1. TRANSFER CHARACTERISTICS

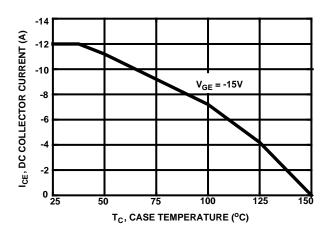

FIGURE 3. MAXIMUM DC COLLECTOR CURRENT AS A FUNCTION OF CASE TEMPERATURE

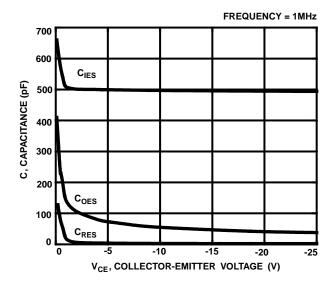

FIGURE 5. CAPACITANCE AS A FUNCTION OF COLLECTOR-EMITTER VOLTAGE

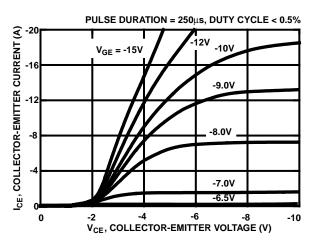

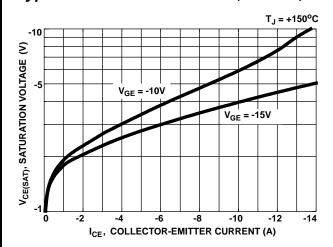

FIGURE 2. SATURATION CHARACTERISTICS

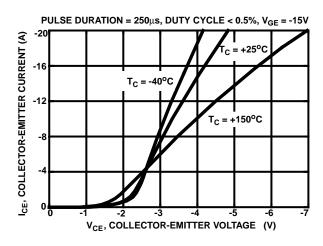

FIGURE 4. COLLECTOR-EMITTER SATURATION VOLTAGE

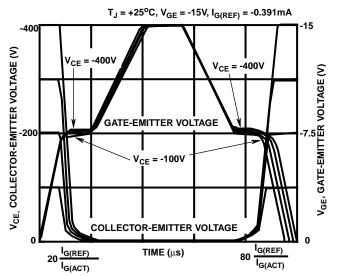

FIGURE 6. NORMALIZED SWITCHING WAVEFORMS AT CONSTANT GATE CURRENT. (REFER TO APPLICATION NOTES AN7254 AND AN7260)

## Typical Performance Curves (Continued)

FIGURE 7. SATURATION VOLTAGE AS A FUNCTION OF COLLECTOR-EMITTER CURRENT

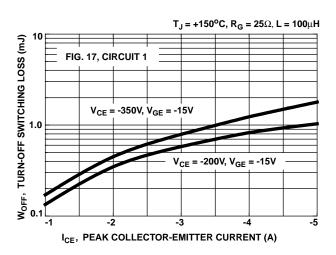

FIGURE 8. TURN-OFF SWITCHING LOSS AS A FUNCTION OF COLLECTOR-EMITTER CURRENT

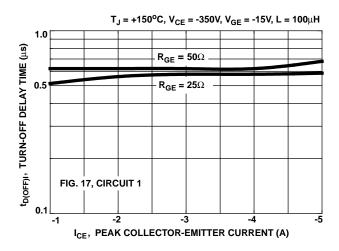

FIGURE 9. TURN-OFF DELAY AS A FUNCTION OF COLLECTOR-EMITTER CURRENT

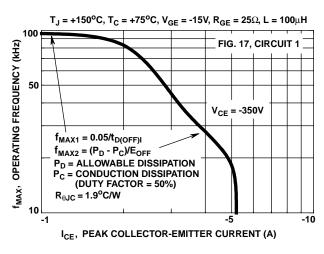

FIGURE 10. OPERATING FREQUENCY AS A FUNCTION OF COLLECTOR-EMITTER CURRENT AND VOLTAGE

FIGURE 11. FALL TIME AS A FUNCTION OF COLLECTOR-EMITTER CURRENT

FIGURE 12. LATCHING CURRENT AS A FUNCTION OF SNUBBER CAPACITANCE

## Typical Performance Curves (Continued)

FIGURE 13. LATCHING CURRENT AS A FUNCTION OF JUNCTION TEMPERATURE

FIGURE 14. GATE THRESHOLD VOLTAGE AS A FUNCTION OF JUNCTION TEMPERATURE

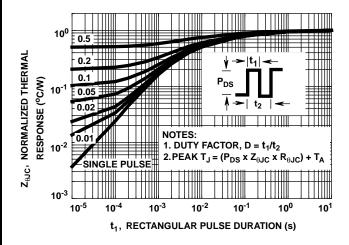

FIGURE 15. IGBT NORMALIZED TRANSIENT THERMAL IMPEDANCE, JUNCTION TO CASE

FIGURE 16. LATCHING CURRENT AS A FUNCTION OF COLLECTOR-EMITTER VOLTAGE

## **Test Circuits**

FIGURE 17. INDUCTIVE SWITCHING TEST CIRCUITS

## **Operating Frequency Information**

Operating frequency information for a typical device (Figure 10) is presented as a guide for estimating device performance for a specific application. Other typical frequency vs collector current ( $I_{CE}$ ) plots are possible using the information shown for a typical unit in Figure 7, Figure 8 and Figure 9. The operating frequency plot (Figure 10) of a typical device shows  $f_{MAX1}$  or  $f_{MAX2}$  whichever is smaller at each point. The information is based on measurements of a typical device and is bounded by the maximum rated junction temperature.

$f_{MAX1}$  is defined by  $f_{MAX1} = 0.05/t_{D(OFF)I}$ .  $t_{D(OFF)I}$  deadtime (the denominator) has been arbitrarily held to 10% of the onstate time for a 50% duty factor. Other definitions are possible. t<sub>D(OFF)I</sub> is defined as the time between the 90% point of the trailing edge of the input pulse and the point where the collector current falls to 90% of its maximum value. Device Turn-Off delay can establish an additional frequency limiting condition for an application other than T<sub>JMAX</sub>. t<sub>D(OFF)I</sub> is important when controlling output ripple under a lightly loaded condition.  $f_{MAX2}$  is defined by  $f_{MAX2} = (P_D - P_D)$  $P_C$ )/ $E_{OFF}$ . The allowable dissipation ( $P_D$ ) is defined by  $P_D$  = (T<sub>JMAX</sub> - T<sub>C</sub>)/R<sub>BJC</sub>. The sum of device switching and conduction losses must not exceed Pd. A 50% duty factor was used (Figure 10) and the conduction losses (Pc) are approximated by  $Pc = (V_{CF} \cdot I_{CF})/2$ .  $E_{OFF}$  is defined as the integral of the instantaneous power loss starting at the trailing edge of the input pulse and ending at the point where the collector current equals zero ( $I_{CE} = 0A$ ).

The switching power loss (Figure 10) is defined as  $f_{MAX2} \bullet E_{OFF}$ . Turn-On switching losses are not included because they can be greatly influenced by external circuit conditions and components.

## Handling Precautions for IGBTs

Insulated Gate Bipolar Transistors are susceptible to gate-insulation damage by the electrostatic discharge of energy through the devices. When handling these devices, care should be exercised to assure that the static charge built in the handler's body capacitance is not discharged through the device. With proper handling and application procedures, however, IGBTs are currently being extensively used in production by numerous equipment manufacturers in military, industrial and consumer applications, with virtually no damage problems due to electrostatic discharge. IGBTs can be handled safely if the following basic precautions are taken:

- Prior to assembly into a circuit, all leads should be kept shorted together either by the use of metal shorting springs or by the insertion into conductive material such as "†ECCOSORBD LD26" or equivalent.

- When devices are removed by hand from their carriers, the hand being used should be grounded by any suitable means - for example, with a metallic wristband.

- 3. Tips of soldering irons should be grounded.

- 4. Devices should never be inserted into or removed from circuits with power on.

- Gate Voltage Rating Never exceed the gate-voltage rating of V<sub>GEM</sub>. Exceeding the rated V<sub>GE</sub> can result in permanent damage to the oxide layer in the gate region.

- 6. Gate Termination The gates of these devices are essentially capacitors. Circuits that leave the gate opencircuited or floating should be avoided. These conditions can result in Turn-On of the device due to voltage buildup on the input capacitor due to leakage currents or pickup.

- 7. **Gate Protection** These devices do not have an internal monolithic zener diode from gate to emitter. If gate protection is required an external zener is recommended.

#### HARRIS SEMICONDUCTOR IGBT PRODUCT IS COVERED BY ONE OR MORE OF THE FOLLOWING U.S. PATENTS:

| 4,364,073 | 4,417,385 | 4,430,792 | 4,443,931 | 4,466,176 | 4,516,143 | 4,532,534 | 4,567,641 |

|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| 4,587,713 | 4,598,461 | 4,605,948 | 4,618,872 | 4,620,211 | 4,631,564 | 4,639,754 | 4,639,762 |

| 4,641,162 | 4,644,637 | 4,682,195 | 4,684,413 | 4,694,313 | 4,717,679 | 4,743,952 | 4,783,690 |

| 4,794,432 | 4,801,986 | 4,803,533 | 4,809,045 | 4,809,047 | 4,810,665 | 4,823,176 | 4,837,606 |

| 4,860,080 | 4,883,767 | 4,888,627 | 4,890,143 | 4,901,127 | 4,904,609 | 4,933,740 | 4,963,951 |

| 4,969,027 |           |           |           |           |           |           |           |

<sup>†</sup> Trademark Emerson and Cumming, Inc.

# HGTD8P50G1, HGTD8P50G1S

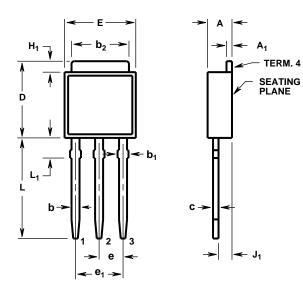

# TO-251AA

#### 3 LEAD JEDEC TO-251AA PLASTIC PACKAGE

| Lead 1  | Gate      |

|---------|-----------|

| Lead 2  | Collector |

| Lead 3  | Emitter   |

| Term. 4 | Collector |

|                | INC       | HES   | MILLIM   |      |       |

|----------------|-----------|-------|----------|------|-------|

| SYMBOL         | MIN       | MAX   | MIN      | MAX  | NOTES |

| Α              | 0.086     | 0.094 | 2.19     | 2.38 | -     |

| A <sub>1</sub> | 0.018     | 0.022 | 0.46     | 0.55 | 3, 4  |

| b              | 0.028     | 0.032 | 0.72     | 0.81 | 3, 4  |

| b <sub>1</sub> | 0.033     | 0.040 | 0.84     | 1.01 | 3     |

| b <sub>2</sub> | 0.205     | 0.215 | 5.21     | 5.46 | 3, 4  |

| С              | 0.018     | 0.022 | 0.46     | 0.55 | 3, 4  |

| D              | 0.270     | 0.290 | 6.86     | 7.36 | -     |

| Е              | 0.250     | 0.265 | 6.35     | 6.73 | -     |

| е              | 0.090     | TYP   | 2.28 TYP |      | 5     |

| e <sub>1</sub> | 0.180 BSC |       | 4.57 BSC |      | 5     |

| H <sub>1</sub> | 0.035     | 0.045 | 0.89     | 1.14 | -     |

| J <sub>1</sub> | 0.040     | 0.045 | 1.02     | 1.14 | 6     |

| L              | 0.355     | 0.375 | 9.02     | 9.52 | -     |

| L <sub>1</sub> | 0.075     | 0.090 | 1.91     | 2.28 | 2     |

#### NOTES:

- These dimensions are within allowable dimensions of Rev. C of JEDEC TO-251AA outline dated 9-88.

- 2. Solder finish uncontrolled in this area.

- 3. Dimension (without solder).

- 4. Add typically 0.002 inches (0.05mm) for solder plating.

- 5. Position of lead to be measured 0.250 inches (6.35mm) from bottom of dimension D.

- 6. Position of lead to be measured 0.100 inches (2.54mm) from bottom of dimension D.

- 7. Controlling dimension: Inch.

- 8. Revision 2 dated 10-95.

## HGTD8P50G1, HGTD8P50G1S

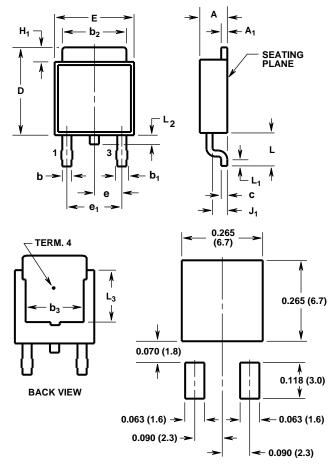

#### TO-252AA

## SURFACE MOUNT JEDEC TO-252AA PLASTIC PACKAGE

MINIMUM PAD SIZE RECOMMENDED FOR SURFACE-MOUNTED APPLICATIONS

| Lead 1  | Gate      |

|---------|-----------|

| Lead 3  | Source    |

| Term. 4 | Collector |

|                | INCHES |       | MILLIM   |      |       |

|----------------|--------|-------|----------|------|-------|

| SYMBOL         | MIN    | MAX   | MIN      | MAX  | NOTES |

| Α              | 0.086  | 0.094 | 2.19     | 2.38 | -     |

| A <sub>1</sub> | 0.018  | 0.022 | 0.46     | 0.55 | 4, 5  |

| b              | 0.028  | 0.032 | 0.72     | 0.81 | 4, 5  |

| b <sub>1</sub> | 0.033  | 0.040 | 0.84     | 1.01 | 4     |

| b <sub>2</sub> | 0.205  | 0.215 | 5.21     | 5.46 | 4, 5  |

| b <sub>3</sub> | 0.190  | -     | 4.83     | -    | 2     |

| С              | 0.018  | 0.022 | 0.46     | 0.55 | 4, 5  |

| D              | 0.270  | 0.290 | 6.86     | 7.36 | -     |

| Е              | 0.250  | 0.265 | 6.35     | 6.73 | -     |

| е              | 0.090  | TYP   | 2.28 TYP |      | 7     |

| e <sub>1</sub> | 0.180  | BSC   | 4.57 BSC |      | 7     |

| H <sub>1</sub> | 0.035  | 0.045 | 0.89     | 1.14 | -     |

| J <sub>1</sub> | 0.040  | 0.045 | 1.02     | 1.14 | -     |

| L              | 0.100  | 0.115 | 2.54     | 2.92 | -     |

| L <sub>1</sub> | 0.020  | -     | 0.51     | -    | 4, 6  |

| L <sub>2</sub> | 0.025  | 0.040 | 0.64     | 1.01 | 3     |

| L <sub>3</sub> | 0.170  | -     | 4.32     | =    | 2     |

#### NOTES:

- These dimensions are within allowable dimensions of Rev. B of JEDEC TO-252AA outline dated 9-88.

- 2.  $L_3$  and  $b_3$  dimensions establish a minimum mounting surface for terminal 4.

- 3. Solder finish uncontrolled in this area.

- 4. Dimension (without solder).

- 5. Add typically 0.002 inches (0.05mm) for solder plating.

- 6.  $L_1$  is the terminal length for soldering.

- 7. Position of lead to be measured 0.090 inches (2.28mm) from bottom of dimension D.

- 8. Controlling dimension: Inch.

- 9. Revision 5 dated 10-95.

All Harris Semiconductor products are manufactured, assembled and tested under ISO9000 quality systems certification.

Harris Semiconductor products are sold by description only. Harris Semiconductor reserves the right to make changes in circuit design and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Harris is believed to be accurate and reliable. However, no responsibility is assumed by Harris or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Harris or its subsidiaries.

#### Sales Office Headquarters

For general information regarding Harris Semiconductor and its products, call 1-800-4-HARRIS

#### **NORTH AMERICA**

Harris Semiconductor P. O. Box 883, Mail Stop 53-210 Melbourne, FL 32902 TEL: 1-800-442-7747

(407) 729-4984 FAX: (407) 729-5321

#### **EUROPE**

Harris Semiconductor Mercure Center 100, Rue de la Fusee 1130 Brussels, Belgium TEL: (32) 2.724.2111 FAX: (32) 2.724.22.05

# HARRIS SEMICONDUCTOR

#### ASI/

Harris Semiconductor PTE Ltd. No. 1 Tannery Road Cencon 1, #09-01 Singapore 1334 TEL: (65) 748-4200 FAX: (65) 748-0400