TOSHIBA CCD LINEAR IMAGE SENSOR CCD (Charge Coupled Device)

# **TCD1501D**

1

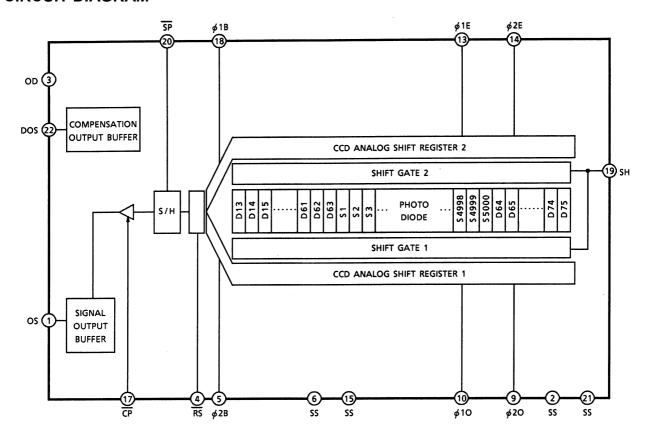

The TCD1501D which includes sample—and—hold circuit is a high sensitive and low dark current 5000 elements CCD image sensor. The sensor is designed for facsimile, imagescanner and OCR. The device contains a row of 5000 elements photodiodes which provide a 16 lines / mm (400DPI) across a A3 size paper. The device is operated by 5 V (pulse), and 12 V power supply.

## **FEATURES**

• Number of Image Sensing Elements : 5000 elements

Image Sensing Element Size : 7 µm by 7 µm on 7 µm centers

Photo Sensing Region : High sensitive and low voltage dark signal pn photodiode

Clock

2 Phase (5 V)

Internal Circuit

Package

22 pin Cerdip

Weight: 5.2g (Typ.)

## **MAXIMUM RATINGS (Note 1)**

| CHARACTERISTIC                | SYMBOL           | RATING  | UNIT |  |  |

|-------------------------------|------------------|---------|------|--|--|

| Clock Pulse Voltage           | Vφ               |         |      |  |  |

| Shift Pulse Voltage           | V <sub>SH</sub>  |         |      |  |  |

| Reset Pulse Voltage           | VRS              | -0.3~8  | V    |  |  |

| Clamp Pulse Voltage           | VCP              |         | V    |  |  |

| Sample and Hold Pulse Voltage | V <sub>SP</sub>  |         |      |  |  |

| Power Supply Voltage          | V <sub>OD</sub>  | -0.3~15 |      |  |  |

| Operating Temperature         | T <sub>opr</sub> | -25~60  | °C   |  |  |

| Storage Temperature           | T <sub>stg</sub> | -40~100 | °C   |  |  |

Note 1: All voltage are with respect to SS terminals (Ground).

# **CIRCUIT DIAGRAM**

2

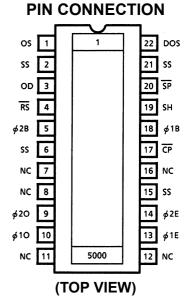

## **PIN NAMES**

| <sub>φ</sub> 1Ε, Ο | Clock (Phase 1)             |

|--------------------|-----------------------------|

| <sub>φ</sub> 2E, Ο | Clock (Phase 2)             |

| φIB                | Final Stage Clock (Phase 1) |

| <sub>φ</sub> 2B    | Final Stage Clock (Phase 2) |

| SH                 | Shift Gate                  |

| RS                 | Reset Gate                  |

| SP                 | Sample and Hold Gate        |

| CP                 | Clamp Gate                  |

| OS                 | Signal Output               |

| DOS                | Compensation Output         |

| OD                 | Power                       |

| SS                 | Ground                      |

| NC                 | Non Connection              |

## **OPTICAL / ELECTRICAL CHARACTERISTICS**

(Ta = 25°C,  $V_{OD}$  = 12 V,  $V_{\phi}$  =  $V_{\overline{RS}}$  =  $V_{SH}$  =  $V_{\overline{SP}}$  =  $V_{\overline{CP}}$  = 5 V,  $f_{\phi}$  = 0.5 MHz,  $f_{RS}$  = 1 MHz,  $t_{INT}$  (INTEGRATION TIME) = 10 ms, LIGHT SOURCE = DAYLIGHT FLUORESCENT LAMP, LOAD RESISTANCE = 100 k $\Omega$ )

| CHARACTERISTIC                 | SYMBOL               | MIN. | TYP. | MAX. | UNIT     | NOTE     |

|--------------------------------|----------------------|------|------|------|----------|----------|

| Sensitivity                    | R                    | 10.4 | 13   | 15.6 | V / Ix·s |          |

| Photo Response Non Uniformity  | PRNU                 | _    | _    | 10   | %        | (Note 2) |

|                                | PRNU (3)             | _    | 6    | 10   | mV       | (Note 9) |

| Register Imbalance             | RI                   | _    | _    | 3    | %        | (Note 3) |

| Saturation Output Voltage      | V <sub>SAT</sub>     | 2    | 3    | _    | ٧        | (Note 4) |

| Saturation Exposure            | SE                   | 0.13 | 0.23 | _    | lx⋅s     | (Note 5) |

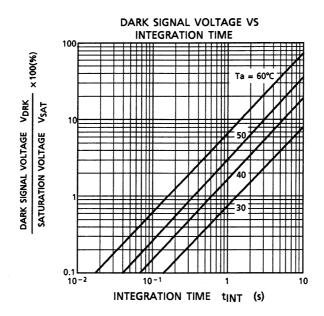

| Dark Signal Voltage            | V <sub>DRK</sub>     | _    | 1    | 2    | mV       | (Note 6) |

| Dark Signal Non Uniformity     | DSNU                 | _    | 2    | 3    | mV       | (Note 6) |

| DC Power Dissipation           | PD                   | _    | 240  | 325  | mW       |          |

| Total Transfer Efficiency      | TTE                  | 92   | _    | _    | %        |          |

| Output Impedance               | Z <sub>o</sub>       | _    | 0.5  | 1    | kΩ       |          |

| Dynamic Range                  | DR                   | _    | 3000 | _    | _        | (Note 7) |

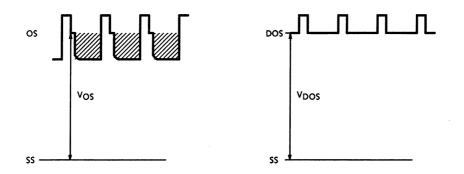

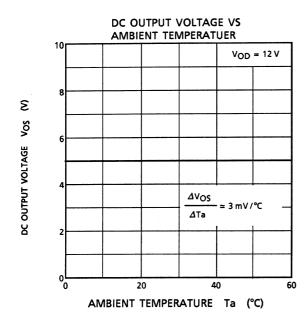

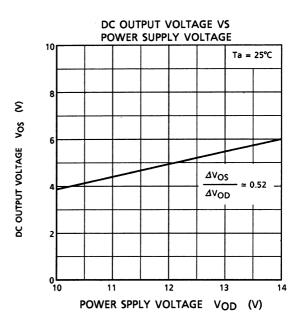

| DC Signal Output Voltage       | Vos                  | 4    | 5    | 6.5  | V        | (Note 8) |

| DC Compensation Output Voltage | V <sub>DOS</sub>     | 4    | 5    | 6.5  | V        | (Note 8) |

| DC Differential Error Voltage  | Vos-V <sub>DOS</sub> |      |      | 400  | mV       |          |

Note 2: Measured at 50% of SE (Typ.)

Definition of PRNU : PRNU =  $\frac{\Delta \chi}{\overline{\chi}} \times 100(\%)$

Where  $\bar{\chi}$  is average of total signal output and  $\Delta \chi$  is the maximum deviation from  $\bar{\chi}$  under uniform illumination.

Note 3: Measured at 50% of SE (Typ.)

RI is defined as follows:

RI =

$$\frac{\sum_{\sum_{j=1}^{4999} |\chi n - \chi n + 1|}{|\chi n - \chi n + 1|}}{4999 \times \chi} \times 100(\%)$$

Where  $\chi n$  and  $\chi n + 1$  are signal output of each pixel.  $\bar{\chi}$  is average of total signal output.

Note 4: V<sub>SAT</sub> is defined as minimum saturation output voltage of all effective pixels.

Note 5: Definition of SE : SE =  $\frac{V_{SAT}}{R}$  (lx·s)

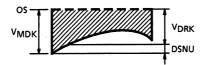

Note 6:  $V_{DRK}$  is defined as average dark signal voltage of all effective pixels.

DSNU is defined as different voltage between  $V_{DRK}$  and  $V_{MDK}$  when  $V_{MDK}$  is maximum dark signal voltage.

Note 7: Definition of DR : DR =  $\frac{V_{SAT}}{V_{DRK}}$

$V_{\mbox{\footnotesize{DRK}}}$  is proportional to  $t_{\mbox{\footnotesize{INT}}}$  (Integration Time).

So the shorter  $t_{\mbox{\scriptsize INT}}$  condition makes wider DR values.

Note 8: DC signal output voltage and DC compensation output voltage are defined as follows:

Note 9: PRUN (3) is defined as maximum voltage with next pixel, where measured 5% of SE (Typ.).

# **OPERATING CONDITION**

| CHARACTERISTIC                  |           | SYMBOL                                       | MIN. | TYP. | MAX. | UNIT |

|---------------------------------|-----------|----------------------------------------------|------|------|------|------|

| Clock Pulse Voltage             | "H" Level | V <sub>φ</sub> 1E, O<br>V <sub>φ</sub> 2E, O | 4.5  | 5    | 5.5  | V    |

|                                 | "L" Level | V <sub>φ</sub> 2E, O                         | 0    | _    | 0.5  |      |

| First Otaga Olash Vallaga       | "H" Level | V <sub>0</sub> 1B                            | 4.5  | 5    | 5.5  | V    |

| Final Stage Clock Voltage       | "L" Level | V <sub>φ</sub> 1B<br>V <sub>φ</sub> 2B       | 0    | _    | 0.5  |      |

| Shift Pulse Voltage             | "H" Level | V <sub>SH</sub>                              | 4.5  | 5    | 5.5  | V    |

|                                 | "L" Level |                                              | 0    | _    | 0.5  |      |

| Decet Dules Vellege             | "H" Level | V <sub>RS</sub>                              | 4.5  | 5    | 5.5  | V    |

| Reset Pulse Voltage             | "L" Level |                                              | 0    | _    | 0.5  |      |

| Clamp Pulse Voltage             | "H" Level | V <sub>CP</sub>                              | 4.5  | 5    | 5.5  | V    |

|                                 | "L" Level |                                              | 0    | _    | 0.5  |      |

| Sample and Hold Pulse Voltage * | "H" Level | V <sub>SP</sub>                              | 4.5  | 5    | 5.5  | V    |

|                                 | "L" Level |                                              | 0    | _    | 0.5  |      |

| Power Supply Voltage            |           | V <sub>OD</sub>                              | 11.4 | 12.0 | 13.0 | ٧    |

<sup>\*:</sup> Supply "L" level to  $\overline{\sf SP}$  terminal when sample-and-hold circuitry is not used.

# CLOCK CHARACTERISTICS (Ta=25°C)

| CHARACTERISTIC                   | SYMBOL          | MIN. | TYP. | MAX. | UNIT |

|----------------------------------|-----------------|------|------|------|------|

| Clock Pulse Frequency            | $f_{\phi}$      | _    | 0.5  | 6.0  | MHz  |

| Reset Pulse Frequency            | fRS             | _    | 1.0  | 12.0 | MHz  |

| Sample and Hold Pulse Frequency  | f SP            | _    | 1.0  | 12.0 | MHz  |

| Clock Capacitance                | $C_{\phi E}$    | _    | 350  | 450  | pF   |

|                                  | $C_{\phi O}$    | _    | 350  | 450  |      |

| Final Stage Clock Capacitance    | С <sub>ФВ</sub> | _    | 10   | 20   | pF   |

| Shift Gate Capacitance           | C <sub>SH</sub> | _    | 10   | 20   | pF   |

| Reset Gate Capacitance           | CRS             | _    | 10   | 20   | pF   |

| Clamp Gate Capacitance           | C CP            | _    | 10   | 20   | pF   |

| Sample and Hold Gate Capacitance | C SP            | _    | 10   | 20   | pF   |

6 2001-05-14

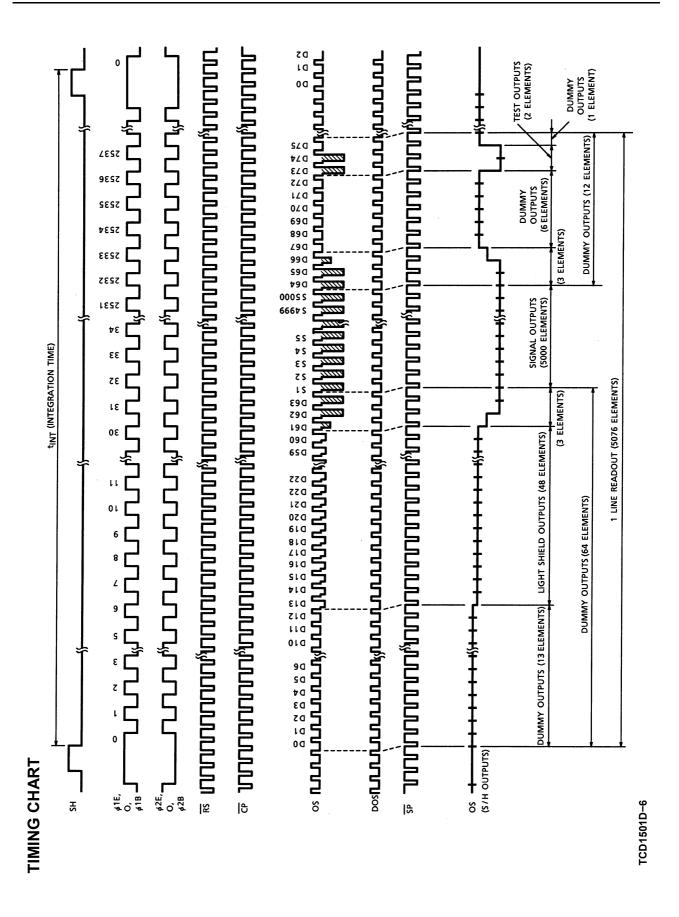

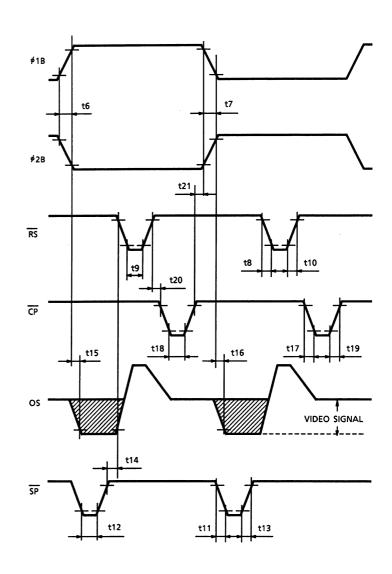

# **TIMING REQUIREMENTS**

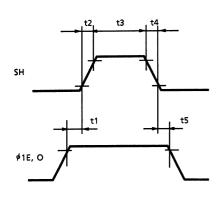

SH, ∮1 TIMING

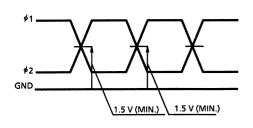

$\phi$ 1,  $\phi$ 2,  $\overline{RS}$ ,  $\overline{CP}$ , OS,  $\overline{SP}$  TIMING

TCD1501D

| CHARACTERISTIC                                                        | SYMBOL   | MIN. | TYP.<br>(Note 10) | MAX. | UNIT |

|-----------------------------------------------------------------------|----------|------|-------------------|------|------|

| Pulse Timing of SH and $_{\phi}$ 10, E                                | t1, t5   | 100  | 300               | _    | ns   |

| SH Pulse Rise Time, Fall Time                                         | t2, t4   | 0    | 50                | _    | ns   |

| SH Pulse Width                                                        | t3       | 500  | 1000              | _    | ns   |

| $_{\phi}$ 1, $_{\phi}$ 2 Pulse Rise Time, Fall Time                   | t6, t7   | 0    | 100               | _    | ns   |

| RS Pulse Rise Time, Fall Time                                         | t8, t10  | 0    | 20                | _    | ns   |

| RS Pulse Width                                                        | t9       | 20   | 250               | _    | ns   |

| SP Pulse Rise Time, Fall Time                                         | t11, t13 | 0    | 20                | _    | ns   |

| SP Pulse Width                                                        | t12      | 20   | _                 | _    | ns   |

| Pulse Timing of SP and RS                                             | t14      | 0    | 50                | _    | ns   |

| Video Data Delay Time (Note 11)                                       | t15, t16 | _    | 30                | _    | ns   |

| CP Pulse Rise Time, Fall Time                                         | t17, t19 | 0    | 20                | _    | ns   |

| CP Pulse Width                                                        | t18      | 20   | _                 | _    | ns   |

| Pulse Timing of RS and CP                                             | t20      | 0    | _                 | _    | ns   |

| Pulse Timing of $_{\phi}$ 1B, $_{\phi}$ 2B and $\overline{\text{CP}}$ | t21      | 0    | _                 | _    | ns   |

Note 10: TYP. is the case of  $f_{RS}$  = 1.0 MHz

Note 11: Load Resistance is 100  $k\Omega$

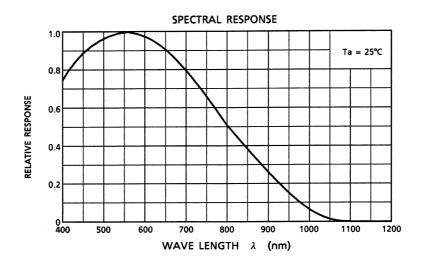

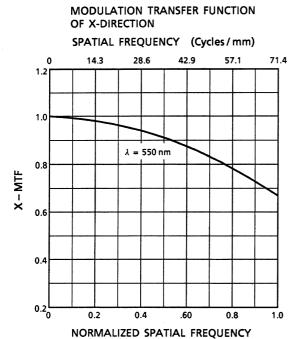

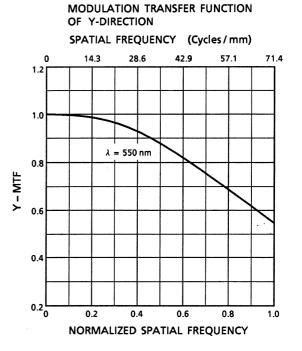

#### **TYPICAL PERFORMANCE CURVES**

# **TYPICAL PERFORMANCE CURVES(Cont.)**

#### PRECAUTIONS FOR USE OF CCD IMAGE SENSOR

#### 1. Static Electricity

This device has some weakly terminals for static electricity. Therefor, please pay attention to treat this device.

CCD Image Sensor is protected against static electricity, but inferior puncture mode device due to static electricity is sometimes detected. In handling the device, it is necessary to execute the following static electricity preventive measures, in order to prevent the trouble rate increase of the manufacturing system due to static electricity.

- a. Prevent the generation of static electricity due to friction by making the work with bare hands or by putting on cotton gloves and non-charging working clothes.

- b. Discharge the static electricity by providing earth plate or earth wire on the floor, door or stand of the work room.

- c. Ground the tools such as soldering iron, radio cutting plier or pincette.

- It is not necessarily required to execute all precaution items for static electricity.

- It is all right to mitigate the precautions by confirming that the trouble rate within the prescribed range.

#### 2. Window Glass

As the dust and station on the glass window of the package will cause black flow on the picture, never fail to clean the glass surface before using. (Blow compressed vapor, and wipe off the dust, and dirt with soft cloth or paper slightly moistened with alcohol).

Fully take care for the handling of the device as the window glass will break or a strong friction is given to the window glass surface.

#### 3. Incident Light

CCD image sensor has sensitivity in a wide range zone of light wave length, but its characteristics will sometimes widely change when used with long wave length input light outside the visual light zone.

11

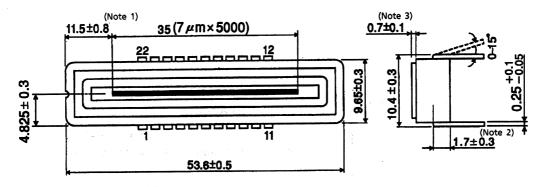

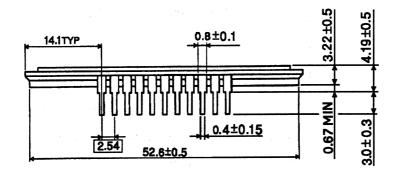

## **PACKEGE DIMENSIONS**

WDIP22-G-400-2.54D (B)

Unit: mm

Note 1: No. 1 SENSOR ELEMENT (S1) TO EDGE OF PACKAGE.

Note 2: TOP OF CHIP TO BOTTOM OF PACKAGE.

Note 3: GLASS THICKNES (n = 1.5)

Weight: 5.2 g (Typ.)

12

#### **RESTRICTIONS ON PRODUCT USE**

000707EBA

- TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such TOSHIBA products could cause loss of human life, bodily injury or damage to property. In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the "Handling Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability Handbook" etc..

- The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These TOSHIBA products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunction or failure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc.. Unintended Usage of TOSHIBA products listed in this document shall be made at the customer's own risk.

- The products described in this document are subject to the foreign exchange and foreign trade laws.

- The information contained herein is presented only as a guide for the applications of our products. No

responsibility is assumed by TOSHIBA CORPORATION for any infringements of intellectual property or other

rights of the third parties which may result from its use. No license is granted by implication or otherwise under

any intellectual property or other rights of TOSHIBA CORPORATION or others.

- The information contained herein is subject to change without notice.