# HIGH EFFICIENCY CHARGE PUMP FOR 7 WLEDS WITH I<sup>2</sup>C INTERFACE

#### **FEATURES**

- 3.0 V to 6.0 V Input Voltage Range

- ×1 and ×1.5 Charge Pump

- Fully Programmable Current with I<sup>2</sup>C

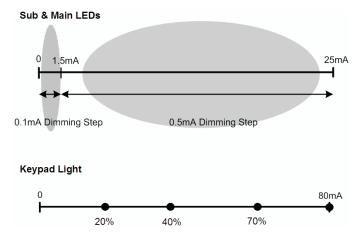

- 64 Dimming Steps with 25mA Maximum (Sub and Main Display Banks)

- 4 Dimming Steps with 80mA Maximum (DM5 for Auxiliary Application)

- 2% Current Matching for Sub LEDs at Light Load Condition (Each 100μA)

- 750 kHz Charge Pump Frequency

- Continuous 230mA Maximum Output Current

- Auto Switching Between ×1 and ×1.5 Mode for Maximum Efficiency

- Built-in Soft Start and Current Limit

- Open Lamp Detection

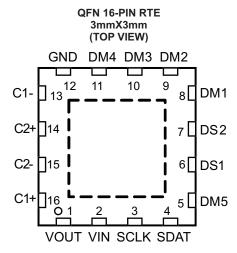

- 16-Pin 3mm x 3mm QFN

- TPS60250 (I<sup>2</sup>C Slave Address: 1110111)

- TPS60252 (I<sup>2</sup>C Slave Address: 1110110)

#### **APPLICATIONS**

- Cellular Phones

- PDA, PMP, GPS (Up To 4 Inch LCD Display)

- Multidisplay Handheld Devices

#### DESCRIPTION

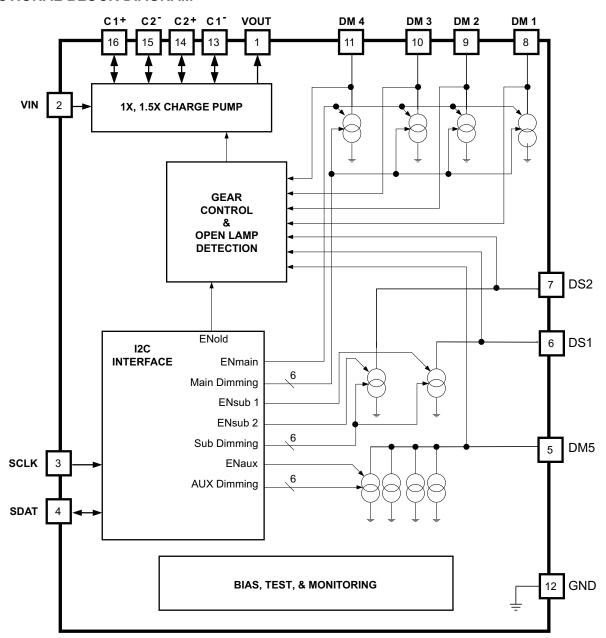

The TPS60250/2 are high efficiency, constant frequency charge pump DC/DC converters that use dual mode  $1\times$  and  $1.5\times$  conversions to maximize efficiency over the input voltage range. The devices drive up to five white LEDs for the main display and up to two white LEDs for the sub display with regulated constant current for uniform intensity. By utilizing adaptive  $1\times/1.5\times$  charge pump modes and very low-dropout current regulators, the TPS60250/2 achieve high efficiency over the full 1-cell lithium-battery input voltage range.

Four enable inputs, ENmain, ENsub1, ENsub2, and ENaux, available through the I<sup>2</sup>C, are used for simple on/off controls for the independent main, sub1, sub2, and DM5 displays, respectively. To lower the operating current when using one sub display LED, the devices provide completely separate operation for the sub display LEDs.

The TPS60250/2 are available in a 16-pin 3mm x 3mm thin QFN.

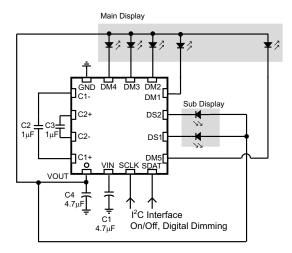

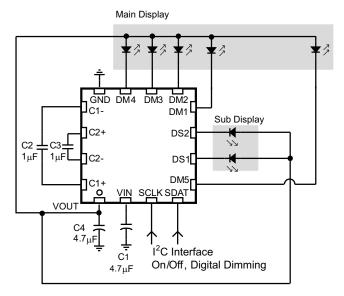

Figure 2. Typical Application for Sub and Main

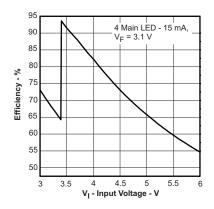

Figure 1. Efficiency vs Input Voltage ORDERING INFORMATION<sup>(1)</sup>

| PART NUMBER | PACKAGE                      | T <sub>A</sub> |  |  |

|-------------|------------------------------|----------------|--|--|

| TPS60250RTE | 16 Din 2 mm v 2 mm OEN (DTE) | −40°C to +85°C |  |  |

| TPS60252RTE | 16-Pin 3 mm × 3 mm QFN (RTE) | -40 C t0 +65°C |  |  |

(1) For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI web site at www.ti.com.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

#### **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range (unless otherwise noted)(1)

|                 |                                        | VALUE      | UNIT |

|-----------------|----------------------------------------|------------|------|

| VI              | Input voltage range (all pins)         | -0.3 to 7  | V    |

|                 | MAX Output current limit               | 650        | mA   |

|                 | HBM ESD Rating (2)                     | 2          | kV   |

|                 | CDM ESD Rating <sup>(3)</sup>          | 500        | V    |

|                 | MM ESD Rating <sup>(4)</sup>           | 200        | V    |

| T <sub>A</sub>  | Operating temperature range            | -40 to 85  | °C   |

| TJ              | Maximum operating junction temperature | 150        | °C   |

| T <sub>ST</sub> | Storage temperature                    | -55 to 150 | °C   |

<sup>(1)</sup> Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### **DISSIPATION RATINGS**

| P  | PACKAGE    | THERMAL RESISTANCE, $R_{\theta JC}$ | THERMAL RESISTANCE, $R_{\theta JA}$ | T <sub>A</sub> ≤ 25°C POWER<br>RATING | DERATING FACTOR<br>ABOVE T <sub>A</sub> = 25°C | T <sub>A</sub> = 85°C POWER<br>RATING |  |

|----|------------|-------------------------------------|-------------------------------------|---------------------------------------|------------------------------------------------|---------------------------------------|--|

| QF | FN 3×3 RTE | 74.6°C/W                            | 48.7°C/W                            | 2.05 W                                | 1.13 W                                         | 0.821 W                               |  |

# RECOMMENDED OPERATING CONDITIONS

|                                 |                                | MIN | NOM | MAX | UNIT |

|---------------------------------|--------------------------------|-----|-----|-----|------|

| $V_{I}$                         | Input voltage range            | 3.0 |     | 6.0 | V    |

| $I_{O(max)}$                    | Maximum output current         |     | 230 |     | mA   |

| C <sub>I</sub>                  | Input capacitor                |     | 4.7 |     | μF   |

| Co                              | Output capacitor               |     | 4.7 |     | μF   |

| C <sub>1</sub> , C <sub>2</sub> | Flying capacitor               |     | 1.0 |     | μF   |

| T <sub>A</sub>                  | Operating ambient temperature  | -40 |     | 85  | °C   |

| $T_J$                           | Operating junction temperature | -40 |     | 125 | °C   |

#### **ELECTRICAL CHARACTERISTICS**

$V_1 = 3.5 \text{ V}$ ,  $T_A = -40^{\circ}\text{C}$  to 85°C, typical values are at  $T_A = 25^{\circ}\text{C}$  (unless otherwise noted)

| PARAMETER          |                                        | TEST CONDITIONS                                                                                       | MIN | TYP | MAX | UNIT |

|--------------------|----------------------------------------|-------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| SUPPLY V           | OLTAGE                                 |                                                                                                       |     |     |     |      |

| VI                 | Input voltage range                    |                                                                                                       | 3.0 |     | 6.0 | V    |

| IQ                 | Operating quiescent current            | 750 kHz Switching in 1.5× mode ( $I_{MAIN\_LED} = 15 \text{ mA} \times 4$ , $I_{O} = 60 \text{ mA}$ ) |     |     | 6.7 | mA   |

|                    |                                        | No switching in $\times 1$ mode ( $I_0 = 100 \mu A$ )                                                 |     |     | 68  | μΑ   |

| I <sub>SD</sub>    | Shutdown current                       | Enable Control Register has 0x00                                                                      |     |     | 1.3 | μΑ   |

| V <sub>UVLO1</sub> | UVLO Threshold voltage1 (1)            | V <sub>I</sub> falling                                                                                | 2.2 | 2.4 | 2.6 | V    |

| V <sub>UVLO2</sub> | UVLO Threshold voltage2 <sup>(2)</sup> | V <sub>I</sub> falling                                                                                | 1.2 | 1.3 | 1.5 | V    |

<sup>(1)</sup> Shut down charge pump and power stage and keep I<sup>2</sup>C content

Submit Documentation Feedback

Copyright © 2007–2008, Texas Instruments Incorporated

<sup>(2)</sup> The Human body model (HBM) is a 100 pF capacitor discharged through a 1.5kΩ resistor into each pin. The testing is done according JEDECs EIA/JESD22-A114.

<sup>(3)</sup> Charged Device Model

<sup>(4)</sup> Machine Model (MM) is a 200pF capacitor discharged through a 500 nH inductor with no series resistor into each pin. The testing is done according JEDECs EIA/JESD22-A115.

<sup>(2)</sup> Shut down completely and come up with all 0's after device restart

# **ELECTRICAL CHARACTERISTICS (continued)**

$V_1 = 3.5 \text{ V}$ ,  $T_A = -40 ^{\circ}\text{C}$  to 85  $^{\circ}\text{C}$ , typical values are at  $T_A = 25 ^{\circ}\text{C}$  (unless otherwise noted)

|                        | PARAMETER                                                                                                                                                                                   | TEST CONDITIONS                                                                                                                   | MIN TYP | MAX | UNIT |

|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|---------|-----|------|

| V <sub>hys</sub>       | Under-voltage lockout hysterisis                                                                                                                                                            | UVLO1                                                                                                                             | 210     |     | mV   |

| T <sub>S</sub>         | Soft start time (3)                                                                                                                                                                         | $V_I = 3 \text{ V}, C_O = 1 \mu\text{F},$<br>$I_{MAIN\_LED} = 15 \text{ mA} \times 4$                                             | 0.5     |     | ms   |

| CHARGE P               | UMP                                                                                                                                                                                         |                                                                                                                                   |         |     |      |

| V <sub>out</sub>       | Overvoltage limit                                                                                                                                                                           |                                                                                                                                   | 6.5     |     | V    |

| Fs                     | Switching frequency                                                                                                                                                                         |                                                                                                                                   | 750     |     | kHz  |

|                        |                                                                                                                                                                                             | ×1 Mode, (V <sub>I</sub> –V <sub>O</sub> )/I <sub>O</sub>                                                                         |         | 1.2 |      |

| R <sub>O</sub>         | Open loop output impedance                                                                                                                                                                  | $\times$ 1.5 Mode, (V <sub>I</sub> $\times$ 1.5 – V <sub>O</sub> )/I <sub>O</sub> V <sub>I</sub> = 3.0V (I <sub>O</sub> = 120 mA) | 3.5     | 5.0 | Ω    |

| CURRENT                | SINK                                                                                                                                                                                        | 1                                                                                                                                 |         | ļ.  |      |

| K <sub>m_sub</sub>     | Current matching of sub LEDs at light load condition (4)                                                                                                                                    | $I_{SUB\_LED}$ = 100 $\mu$ A $\times$ 2, $V_{DXX}$ = 0.4 $V$                                                                      | 0       | ±2% |      |

| K <sub>m_main</sub>    | LED to LED Current matching <sup>(5)</sup> $ \begin{aligned} & I_{\text{MAIN LED}} = 15 \text{ mA} \times 4, \\ & 3.0 \text{ V} \leq \text{V}_{\text{I}} \leq 4.2 \text{ V} \end{aligned} $ |                                                                                                                                   | ±0.1%   | ±5% |      |

| Ka                     | Current accuracy                                                                                                                                                                            | I <sub>LED</sub> = 15 mA                                                                                                          |         | ±7% |      |

| I <sub>D_MS</sub>      | Maximum LED current of DM1-4 and DS1-2                                                                                                                                                      | Main and Sub Display Current Register = 0x01&2(111111), V <sub>DXX</sub> = 0.2 V                                                  | 25.5    |     | mA   |

| I <sub>D DM5</sub>     | Maximum LED current of DM5                                                                                                                                                                  | Aux Display Current Register = 0×03 (XXXX11)                                                                                      | 80      |     | mA   |

| $V_{DropOut}$          | LED Drop out voltage                                                                                                                                                                        | See (6)                                                                                                                           | 80      | 120 | mV   |

| $V_{TH\_GU}$           | 1× Mode to 1.5× mode transition threshold voltage <sup>(7)</sup>                                                                                                                            | $V_{DXX}$ Falling, 15 mA $\times$ 4 measured on the lowest $V_{DXX}$                                                              | 85 100  | 120 | mV   |

| $V_{TH\_GD}$           | Input voltage hysteresis for 1.5× to 1× mode transition                                                                                                                                     | Measured as $V_I - (V_O - V_{DXX\_MIN})$ , $I_{MAIN\_LED} = 15 \text{ mA} \times 4$                                               | 550     |     | mV   |

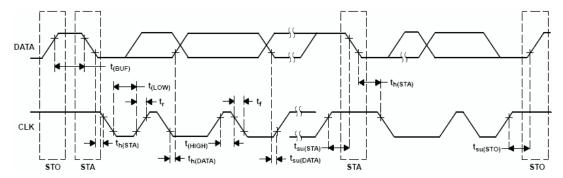

| SERIAL IN              | TERFACE TIMING REQUIREMENTS                                                                                                                                                                 |                                                                                                                                   |         |     |      |

| f <sub>max</sub>       | Clock frequency                                                                                                                                                                             |                                                                                                                                   |         | 400 | kHz  |

| t <sub>wH(HIGH)</sub>  | Pulse duration, clock high time                                                                                                                                                             |                                                                                                                                   | 600     |     | ns   |

| t <sub>wL(LOW)</sub>   | Pulse duration, clock low time                                                                                                                                                              |                                                                                                                                   | 1300    |     | ns   |

| t <sub>r</sub>         | DATA and CLK rise time                                                                                                                                                                      |                                                                                                                                   |         | 300 | ns   |

| t <sub>f</sub>         | DATA and CLK fall time                                                                                                                                                                      |                                                                                                                                   |         | 300 | ns   |

| t <sub>h(STA)</sub>    | High time (repeated) START condition(after this period the first clock pulse is generated)                                                                                                  |                                                                                                                                   | 600     |     | ns   |

| t <sub>su(STA)</sub>   | Setup time for repeated START condition                                                                                                                                                     |                                                                                                                                   | 600     |     | ns   |

| t <sub>h(DATA)</sub>   | Data input hold time                                                                                                                                                                        |                                                                                                                                   | 0       |     | ns   |

| t <sub>su(DATA)</sub>  | Data input setup time                                                                                                                                                                       |                                                                                                                                   | 100     |     | ns   |

| t <sub>su(STO)</sub>   | STOP condition setup time                                                                                                                                                                   |                                                                                                                                   | 600     |     | ns   |

| t <sub>(BUF)</sub>     | Bus free time                                                                                                                                                                               |                                                                                                                                   | 1300    |     | ns   |

| I <sup>2</sup> C COMPA | TIBLE INTERFACE VOLTAGE SPECIFICA                                                                                                                                                           | TION (SCLK, SDAT, VIO)                                                                                                            |         | Ų.  |      |

| V <sub>IL</sub>        | Low-level input voltage                                                                                                                                                                     | 3.0 V ≤ V <sub>1</sub> ≤ 6.0 V                                                                                                    | 0       | 0.5 | ٧    |

| V <sub>IH</sub>        | High-level input voltage                                                                                                                                                                    | 3.0 V ≤ V <sub>1</sub> ≤ 6.0 V                                                                                                    | 1.1     |     | V    |

| V <sub>OL</sub>        | Low-level output voltage                                                                                                                                                                    | I <sub>LOAD</sub> = 2 mA                                                                                                          |         | 0.4 | V    |

- (3) Measurement Condition: From enabling the LED driver to 90% output voltage after V<sub>I</sub> is already up.

- LED current matching is defined as: (I<sub>SUB\_LED\_WORST</sub> I<sub>AVG\_SUB</sub>) / I<sub>AVG\_SUB</sub>

LED to LED Current Matching is defined as: (I<sub>MAIN\_LED\_WORST</sub> I<sub>AVG\_MAIN</sub>) / I<sub>AVG\_MAIN</sub>

Dropout Voltage is defined as V<sub>DXX</sub> (WLED Cathode) to GND voltage at which current into the LED drops 10% from the LED current at V<sub>DXX</sub> = 0.2 V, WLED current = 15 mA × 4.

- As V<sub>I</sub> drops, V<sub>DXX</sub> eventually falls below the switchover threshold of 100mV, and TPS60250/2 switches to 1.5× mode. See the *Operating* Principle section for details about the mode transition thresholds.

# **PIN ASSIGNMENTS**

# **TERMINAL FUNCTIONS**

| TERI | TERMINAL I/O |     | DEGODIDATION                                                                                               |

|------|--------------|-----|------------------------------------------------------------------------------------------------------------|

| NAME | NO.          | 1/0 | DESCRIPTION                                                                                                |

| VOUT | 1            | 0   | Connect the anodes of the sub, main, and aux display white LEDs to this pin.                               |

| VIN  | 2            | I   | Supply voltage input. Connect to a 3 V to 6 V input supply source.                                         |

| SCLK | 3            | I   | I <sup>2</sup> C Interface                                                                                 |

| SDAT | 4            | I/O | I <sup>2</sup> C Interface                                                                                 |

| DM5  | 5            | I   | Current sink inputs. Connect the cathode of the aux display or the 5th main display white LED to this pin. |

| DS1  | 6            | I   | Current sink inputs. Connect the cothods of one of the cub display white LEDs to those pine                |

| DS2  | 7            | I   | Current sink inputs. Connect the cathode of one of the sub display white LEDs to these pins.               |

| DM1  | 8            | I   |                                                                                                            |

| DM2  | 9            | I   | Company sind in the Company the arthur of any of the main display white LEDs to these pins                 |

| DM3  | 10           | I   | Current sink input. Connect the cathode of one of the main display white LEDs to these pins.               |

| DM4  | 11           | I   |                                                                                                            |

| GND  | 12           | -   | Ground                                                                                                     |

| C1-  | 13           | -   | Connect to the flying capacitor C1                                                                         |

| C2+  | 14           | -   | Connect to the flying capacitor C2                                                                         |

| C2-  | 15           | -   | Connect to the flying capacitor C2                                                                         |

| C1+  | 16           | -   | Connect to the flying capacitor C1                                                                         |

# **FUNCTIONAL BLOCK DIAGRAM**

# **TYPICAL CHARACTERISTICS**

# **TABLE OF GRAPHS**

| DESCRIPTION            |                                                                                                        |          |  |  |

|------------------------|--------------------------------------------------------------------------------------------------------|----------|--|--|

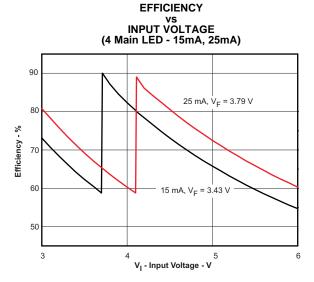

| F(C-1                  | Efficiency vs Input Voltage, 4 Main LED - 15 mA, 25 mA                                                 |          |  |  |

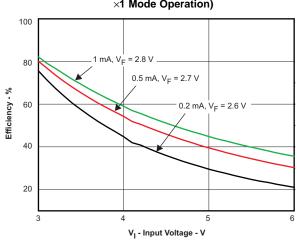

| Efficiency             | Efficiency vs Input Voltage, 2 Sub LED with Light Load Condition, ×1 Mode Operation                    | Figure 4 |  |  |

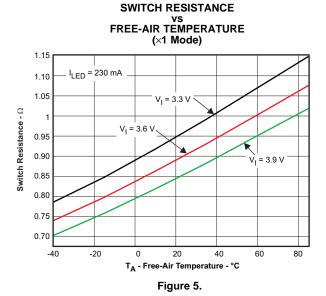

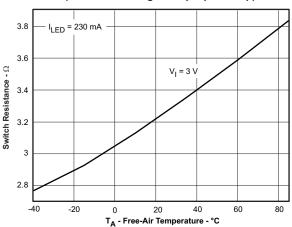

|                        | Switch Resistance vs Free-Air Temperature, ×1 Mode, I <sub>LED</sub> = 230 mA                          | Figure 5 |  |  |

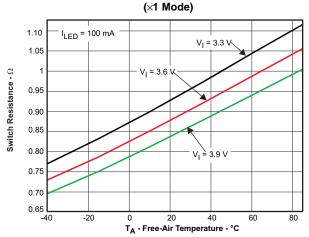

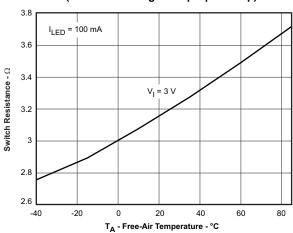

| Output Impedance of ×1 | Switch Resistance vs Free-Air Temperature, ×1 Mode, I <sub>LED</sub> = 100 mA                          |          |  |  |

| and ×1.5 Mode          | Switch Resistance vs Free-Air Temperature, ×1.5 Mode Charge Pump Open-Loop , I <sub>LED</sub> = 230 mA | Figure 7 |  |  |

|                        | Switch Resistance vs Free-Air Temperature, ×1.5 Mode Charge Pump Open-Loop, I <sub>LED</sub> = 100 mA  | Figure 8 |  |  |

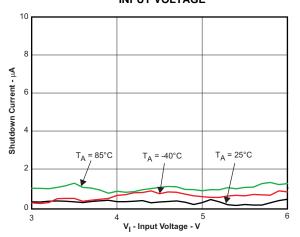

| Shutdown Current       | Shutdown Current vs Input Voltage                                                                      | Figure 9 |  |  |

# **TYPICAL CHARACTERISTICS (continued)**

| DESCRIPTION            |                                                      |           |  |  |

|------------------------|------------------------------------------------------|-----------|--|--|

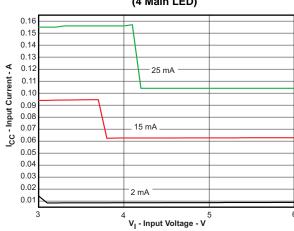

| Input Current          | Input Current vs Supply Voltage, 4 Main LED          | Figure 10 |  |  |

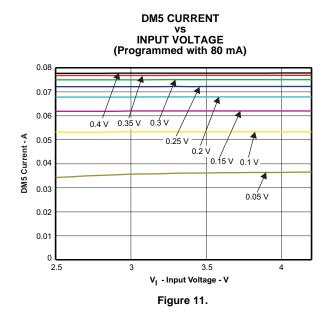

| DM5 with Maximum 80 mA | DM5 Current vs Input Voltage, Programmed with 80 mA  | Figure 11 |  |  |

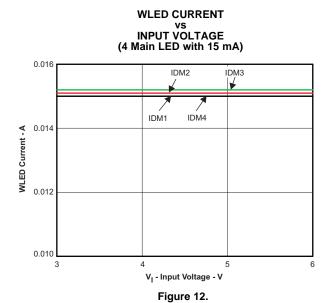

| Current Accuracy       | WLED Current vs Input Voltage, 4 Main LED with 15 mA | Figure 12 |  |  |

Figure 3.

EFFICIENCY

vs

INPUT VOLTAGE

(2 Sub LED with Light Load Condition,

×1 Mode Operation)

Figure 4.

# SWITCH RESISTANCE vs FREE-AIR TEMPERATURE

Figure 6.

# SWITCH RESISTANCE vs FREE-AIR TEMPERATURE (×1.5 Mode Charge Pump Open-Loop)

Figure 7.

#### SHUTDOWN CURRENT vs INPUT VOLTAGE

Figure 9.

#### **SWITCH RESISTANCE**

#### vs FREE-AIR TEMPERATURE (×1.5 Mode Charge Pump Open-Loop)

Figure 8.

#### INPUT CURRENT vs SUPPLY VOLTAGE (4 Main LED)

Figure 10.

# **APPLICATION INFORMATION**

#### APPLICATION OVERVIEW

Most of the current handsets fall into one of three categories. First is the clamshell design, with a main display on the inside, a secondary display on the outside and a keypad backlight. Second is the bar design, with a main display and a keypad backlight. Third is the slide type (slide-up and slide-down) design, with a main display and two keypad banks (inside and outside). The TPS60250/2 are well suited for use in these three major phone designs because the devices have 7 individually regulated white LED current paths that drive up to five white LEDs in the main display and up to two white LEDs in sub display with regulated constant current for uniform intensity. The main and sub display LED channels drive up to 25 mA and the auxiliary LED output (DM5) that drives up to 80 mA can be assigned to keypad backlight, torch light, or low cost/weak camera flash application using the I<sup>2</sup>C interface.

The TPS60250/2 circuits use only 4 external components: the input/output capacitors and 2 charge pump flying capacitors. The few external components combined with the small  $3\text{mm} \times 3\text{mm}$  QFN package provide for a small total solution size. By combining independent control of three separate banks of backlight LEDs with low cost and weak flash capability, the TPS60250/2 help designers minimize power consumption especially in the case of a light load condition while reducing component count and package size.

#### **OPERATING PRINCIPLE**

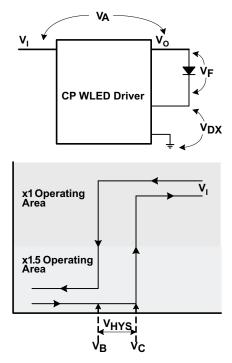

Charge pumps are becoming increasingly attractive in battery-operated applications where board space and maximum height of the converter are critical constraints. The major advantage of a charge pump is the use of only capacitors as storage elements. The TPS60250/2 charge pumps provide regulated LED current from a 3 V to 6 V input source. The devices operate in two modes. The 1× mode, where the input is connected to the output through a pass element, and a high efficiency 1.5× charge pump mode. The IC maximizes power efficiency by operating in 1× and 1.5× modes as input voltage and LED current conditions require. The mode of operation is automatically selected by comparing the forward voltage of the WLED plus the voltage of current sink for each LED with the input voltage. The IC starts up in 1× mode, and automatically transitions to 1.5× if the voltage at any current sink input (DM\_or DS\_) falls below the 100 mV transition voltage. The IC returns to 1× mode as the input rises. Figure 13 provides a visual explanation of the 1× to 1.5× transition.

In  $1.5\times$  mode, the internal oscillator determines the charge/discharge cycles for the flying capacitors. During a charge cycle, the flying capacitors are connected in series and charged up to the input voltage. After the on-time of the internal oscillator expires, the flying capacitors are reconfigured to be in parallel and then connected in series to the input voltage. This provides an output of  $1.5\times$  the input voltage. After the off-time of the internal oscillator expires, another charge cycle initiates and the process repeats.

Figure 13. Input Voltage Hysteresis Between ×1 and ×1.5 Mode

As shown in Figure 13, there is input hysteresis voltage between  $1\times$  and  $1.5\times$  mode to ensure stable operation during mode transition. For the 1 cell Li-lon battery input voltage range, the TPS6025/2 operate in  $1\times$  mode when a fully charged battery is installed. Once the battery voltage drops below the  $V_B$  level, which is the mode transition voltage from  $1\times$  to  $1.5\times$ , the WLED driver operates in  $1.5\times$  mode. Once in  $1.5\times$  mode, the battery voltage must rise to the  $V_C$  level in order to transition from  $1.5\times$  to  $1\times$ . This hysteresis ensures stable operation when there is some input voltage fluctuation at the  $1\times/1.5\times$  mode transition.

The transition voltage,  $V_B$ , depends on  $V_{DX}$  (the mode transition threshold voltage),  $V_F$  (WLED forward voltage drop) and  $V_A$  (the drop out voltage of the charge pump stage) and is calculated as follows:

$$V_B = V_A + V_F + V_{DX}$$

$V_A = R_{OUT1X} \times I_{LEDTOTAL}$

Where  $R_{OUT1X}$  is the 1× mode output impedance of the IC. See the Electrical Characteristics table for output impedance specifications.

The TPS60250/2 switch up to 1.5× mode when the input voltage is below  $V_B$  and remain in 1.5× mode as long as the input is lower than  $V_C$ . 1.5× Mode is exited when the input voltage rises above  $V_C$ .  $V_C$  is calculated as:

$$V_{C} = V_{F} + 550 \text{ mV}$$

The input voltage mode transition hysteresis voltage ( $V_{HYS}$ ) between 1× and 1.5× is calculated using the following equation.

$$V_{HYS} = V_C - V_B = 550 \text{ mV} - V_{DX} - V_A$$

, where  $V_{DX} = 100 \text{mV}$

Note that  $V_A$  is the key factor in determining  $V_{HYS}$  and is dependant on the  $1\times$  mode charge pump output impedance and WLED current.

# LED CURRENT SINKS (DM\_, DS\_)

The TPS60250/2 have constant current sinks which drive seven individual LED current paths. Each current sink regulates the LED current to a constant value determined by the I<sup>2</sup>C interface. The internal register addressing allows the LED main channels DM1~DM5 to be controlled independently from the LED sub channels DS1~DS2. All LED channels sink up to 25 mA of current except DM5 which has an 80 mA maximum current when configured as an auxiliary output. Using the I<sup>2</sup>C interface, the user may assign DM5 to the main display bank with up to 25 mA current or as an auxiliary output for torch or keypad light or low/weak camera flash with 80 mA current. DM5 has 64 dimming steps; the same as the main and sub display banks when assigned to the main display. However, it has its own current programming register and enable control. When assigned as an auxiliary, DM5 has 4 dimming steps (full scale, 70%, 40%, 20%).

These optimized current sinks minimize the voltage headroom required to drive each LED and maximize power efficiency by increasing the amount of time the controller stays in 1× mode before transitioning to 1.5× mode.

#### **OPEN LAMP DETECTION**

In system production it is often necessary to leave LED current paths open depending on the phone model. For example, one phone may use 2 LEDs to backlight the main display while another uses 4 LEDs. Rather than use two different ICs for these different phone applications, the TPS60250/2 may be used in both applications with no additional efficiency loss in the 2 LED applications. In traditional LED driver applications when an LED current path is open, the current sink voltage falls to ground and the current regulation circuitry drives the output to maximum voltage in an attempt to regulate the current for the missing LED path. This severely reduces system efficiency. The TPS60250/2 use 7 internal comparators to detect open lamp condition, when one or more open LED conditions occur, TPS60250/2 prevent activation of 1.5X mode transition due to missing LEDs. Open lamp detection is enabled/disabled using the I<sup>2</sup>C interface.

#### **CAPACITOR SELECTION**

The TPS60250/2 are optimized to work with ceramic capacitors with a dielectric of X5R or better. The two flying capacitors must be the same value for proper operation. The 750 kHz switching frequency requires that the flying capacitor be less than 4.7  $\mu$ F. Use of 1  $\mu$ F ceramic capacitors for both charge pump flying capacitors is recommended.

For good input voltage filtering, low ESR ceramic capacitors are recommended. A 1  $\mu$ F ceramic input capacitor is sufficient for most applications. For better input voltage filtering this value can be increased to 4.7  $\mu$ F.

The output capacitor controls the amount of ripple on the output. Since small ripple is undetectable by the human eye, a 4.7  $\mu$ F output capacitor works well. If better output filtering and lower ripple is desired, a larger output capacitor may be used.

#### SETTING THE LED CURRENT

Figure 14. Dimming Steps for Sub, Main, and Keypad Backlight

Figure 14 shows the dimming steps for sub, main, and auxiliary display banks in a 25 mA maximum current

applications. In order to satisfy today's requirements on LED current , the TPS60250/2 cover the low LED current area from 100  $\mu$ A to 1.5 mA with 100  $\mu$ A dimming steps (total 16 steps for a 25 mA maximum current) for the new LCD panels which have improved transparency rates. For LED currents in the range from 2 mA to 25 mA, the devices use 48 dimming steps with 0.5 mA steps. Also, DM5 has 4 dimming steps once the current path is assigned for auxiliary applications with a 80 mA maximum current.

#### **SERIAL INTERFACE**

The serial interface is compatible with the standard and fast mode  $I^2C$  specifications, allowing transfers at up to 400 kHz. The interface adds flexibility to the WLED driver solution, enabling most functions to be programmed to new values depending on the instantaneous application requirements. Register contents remain intact as long as  $V_{CC}$  remains above UVLO2 (typical 1.3 V).

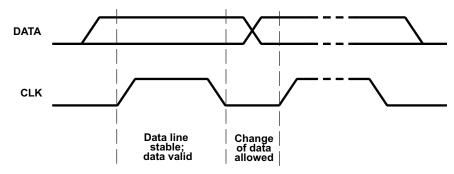

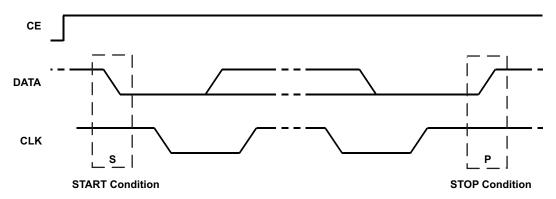

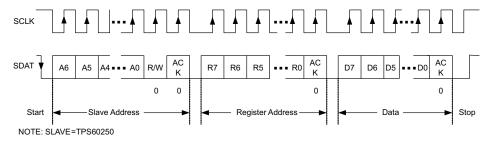

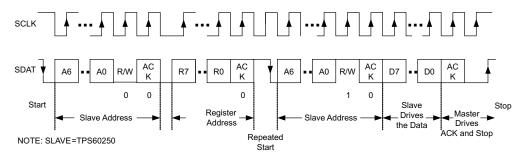

For normal data transfer, DATA is allowed to change only when CLK is low. Changes when CLK is high are reserved for indicating the start and stop conditions. During data transfer, the data line must remain stable whenever the clock line is high. There is one clock pulse per bit of data. Each data transfer is initiated with a start condition and terminated with a stop condition. When addressed, the TPS60250/2 devices generate an acknowledge bit after the reception of each byte. The master device (microprocessor) must generate an extra clock pulse that is associated with the acknowledge bit. The TPS60250/2 devices must pull down the DATA line during the acknowledge clock pulse so that the DATA line is a stable low during the high period of the acknowledge clock pulse. Setup and hold times must be taken into account. During read operations, a master must signal the end of data to the slave by not generating an acknowledge bit on the last byte that was clocked out of the slave. In this case, the slave TPS60250/2 devices must leave the data line high to enable the master to generate the stop condition.

Figure 15. Bit Transfer on the Serial Interface

Figure 16. START and STOP Conditions

Figure 17. Serial I/F READ From TPS60250/2: Protocol A

Figure 18. Serial I/F READ From TPS60250/2: Protocol B

Figure 19. Serial I/F Timing Diagram

The I<sup>2</sup>C interface uses a combined protocol in which the START condition and the Slave Address are both repeated. The TPS60250 provides two I<sup>2</sup>C Slave Addresses using an internal EEPROM in case more than 1 device is used in the system. The TPS60250 primary I<sup>2</sup>C Slave Address is **1110111** and the TPS60252 primary I<sup>2</sup>C Slave Address is **1110110**. For the alternative I<sup>2</sup>C addresses, contact the factory.

#### Enable Control Register (Address: 0x00h)

| ENABLE   | В7 | В6    | B5     | B4     | В3     | B2    | B1   | В0   |

|----------|----|-------|--------|--------|--------|-------|------|------|

| BIT NAME | X  | ENold | ENmain | ENsub2 | ENsub1 | ENaux | DM5H | DM5L |

Bit 6 ENold (Enable Open Lamp Detection)

1: Open Lamp Detection Enabled

0: Open Lamp Detection Disabled

Bit 5 ENmain

1: Enable Main Display LEDs (DM1-DM4)

0: Disable Main Display LEDs

Bit 4 ENsub2

1: Enable Sub Display LED 2 (DS2)

0: Disable Sub Display LED 2

Bit 3 ENsub1

1: Enable Sub Display LED 1 (DS1)

0: Disable Sub Display LED 1

Bit 2 ENaux

1: Enable Aux Display LED (DM5)

0: Disable Aux Display LED

Bits 1,0 DM5H, DM5L

| DM5H<br>(B1) | DM5L<br>(B0) | DM5 Mode and Shutdown Mode                                                                                               |

|--------------|--------------|--------------------------------------------------------------------------------------------------------------------------|

| 0            | 0            | Shutdown mode. All outputs disabled but keep register values                                                             |

| 0            | 1            | Enable the IC and Group DM5 as main display with maximum current of 25 mA                                                |

| 1            | 0            | Enable the IC and set DM5 as Aux output with maximum current of 80 mA. Dimming steps determined by laux0 and laux1 bits. |

| 1            | 1            | Shutdown mode. All outputs disabled but keep register values                                                             |

#### Sub Display Current Control Register (Address: 0x01h)

| SUB DISP<br>CURRENT | В7 | В6 | B5    | В4    | В3    | B2    | B1    | В0    |

|---------------------|----|----|-------|-------|-------|-------|-------|-------|

| BIT NAME            | X  | X  | Isub5 | Isub4 | Isub3 | lsub2 | lsub1 | lsub0 |

Bits 5 - 0 Isub5 - Isub0 (total 64 steps)

6-Bit command (64 steps) to these bits sets the current for DS1 and DS2.

For LED currents between 0 and 1.5 mA, one step = 0.1 mA increment

For LED currents between 1.5 and 25.5 mA, one step = 0.5 mA increment

# Main Display Current Control Register (Address: 0x02h)

| MAIN DISP<br>CURRENT | В7 | В6 | В5     | В4     | В3     | B2     | B1     | В0     |

|----------------------|----|----|--------|--------|--------|--------|--------|--------|

| BIT NAME             | X  | X  | Imain5 | Imain4 | Imain3 | lmain2 | lmain1 | Imain0 |

Bits 5 - 0 Imain5 - Imain0 (total 64 steps)

6-Bit command (64 steps) to these bits sets the current for DM1-DM4.

For LED currents between 0 and 1.5 mA, one step = 0.1mA increment

For LED currents between 1.5 and 25.5 mA, one step = 0.5 mA increment

Submit Documentation Feedback

Copyright © 2007–2008, Texas Instruments Incorporated

# Aux Output Brightness and Operation Mode Control Register (Address: 0x03h)

| AUX DISP<br>CURRENT | В7    | В6    | В5    | B4    | В3    | B2    | B1    | В0    |

|---------------------|-------|-------|-------|-------|-------|-------|-------|-------|

| BIT NAME            | laux5 | laux4 | laux3 | laux2 | laux1 | laux0 | Mode1 | Mode0 |

# Bits 7 - 2 (DM5 set to Main Display Mode)

laux5 - laux0 (total 64 steps)

6-Bit command (64 steps) to these bits sets the current for DM5.

For LED currents between 0 and 1.5 mA, one step = 0.1mA increment

For LED currents between 1.5 and 25.5 mA, one step = 0.5 mA increment

# Bits 7 - 2 (DM5 set to Aux Display Mode)

| laux5<br>(B7) | laux4<br>(B6) | laux3<br>(B5) | laux2<br>(B4) | laux1<br>(B3) | laux0<br>(B2) | Aux Dimming<br>Step |

|---------------|---------------|---------------|---------------|---------------|---------------|---------------------|

| X             | Х             | Χ             | X             | 0             | 0             | 20%                 |

| X             | Х             | Χ             | Χ             | 0             | 1             | 40%                 |

| Х             | Х             | Х             | Х             | 1             | 0             | 70%                 |

| Х             | Х             | Х             | Х             | 1             | 1             | 100%                |

#### Bits 1,0 Mode1, Mode0

| Mode1<br>(B1) | Mode0<br>(B0) | TPS60250/2 Mode                                                                                                                                              |

|---------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0             | 0             | Auto-Switchover Mode. The TPS60250/2 select 1x/1.5x mode as described in the <i>Operating Principle</i> section.                                             |

| 0             | 1             | $1\times$ Mode. TPS60250/2 remain in $1\times$ mode regardless of the input voltage. LED current may not regulate at lower input voltages when in this mode. |

| 1             | 0             | 1.5× Mode. TPS60250/2 remain in 1.5× mode regardless of the input voltage.                                                                                   |

| 1             | 1             | Auto-Switchover Mode. The TPS60250/2 select 1x/1.5x mode as described in the <i>Operating Principle</i> section.                                             |

#### **APPLICATION CIRCUITS**

Figure 20. The Typical Application Circuit for Sub and Main Display

As shown in Figure 20, typical application circuit for a clam shell phone has 5 main LEDs and 2 sub LEDs. Recently, the LCD panel makers have developed a new panel that has an improved transparency rate which makes system efficiency with 100  $\mu$ A LED current a critical load point. To meet system efficiency requirements with the light load conditions for the new LCD operating panels, the TPS60250/2 have a maximum 55  $\mu$ A operating current with 100  $\mu$ A output load condition. In this application, the controller always operates in 1× mode due to the WLED's low forward voltage drop (about 2.6  $V_F$  with a 100  $\mu$ A WLED current). Thus, the total efficiency at the light load condition is determined using Equation 1:

$$\eta_{Light} = \frac{I_O \times V_F}{V_{in} \times (I_O + I_{op})}$$

(1)

Where:

Io: Output Load (WLED) Current

V<sub>F</sub>: Forward Voltage Drop of WLED

Vin: Input Voltage

Iop: Operating Current of LED Driver

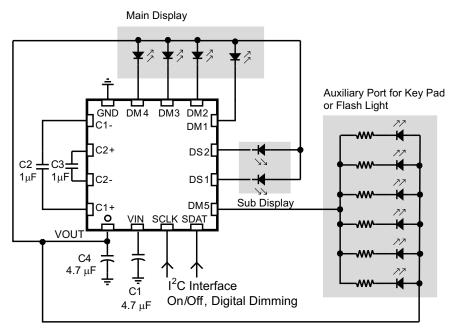

Figure 21. The Typical Application Circuit for Sub, Main, and Keypad Backlight

Figure 21 shows the typical application circuit for sub, main, and keypad backlight. In this application, DM5 is assigned as the auxiliary input for the keypad lighting application.

#### **LAYOUT GUIDELINES**

There are several points to consider when laying out a PCB for charge pump based solutions. In general, all capacitors should be as close as possible to the device. This is especially important when placing the flying capacitors (C2, C3 in Figure 20 and Figure 21). In cases where DM5 is assigned for torch/flash applications, with a maximum 80 mA WLED current, this current path must be kept wide to reduce the trace resistance.

# **Revision History**

| C | Changes from Revision B (November 2007) to Revision C |   |  |  |  |  |

|---|-------------------------------------------------------|---|--|--|--|--|

| • | Added TPS60252 device information                     | 1 |  |  |  |  |

ti.com 11-Jul-2008

#### PACKAGING INFORMATION

| Orderable Device | Status <sup>(1)</sup> | Package<br>Type | Package<br>Drawing | Pins | Package<br>Qty | e Eco Plan <sup>(2)</sup> | Lead/Ball Finish | MSL Peak Temp <sup>(3)</sup> |

|------------------|-----------------------|-----------------|--------------------|------|----------------|---------------------------|------------------|------------------------------|

| TPS60250RTER     | ACTIVE                | QFN             | RTE                | 16   | 3000           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

| TPS60250RTERG4   | ACTIVE                | QFN             | RTE                | 16   | 3000           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

| TPS60250RTET     | ACTIVE                | QFN             | RTE                | 16   | 250            | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

| TPS60250RTETG4   | ACTIVE                | QFN             | RTE                | 16   | 250            | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

| TPS60252RTER     | ACTIVE                | QFN             | RTE                | 16   | 3000           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

| TPS60252RTERG4   | ACTIVE                | QFN             | RTE                | 16   | 3000           | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

| TPS60252RTET     | ACTIVE                | QFN             | RTE                | 16   | 250            | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

| TPS60252RTETG4   | ACTIVE                | QFN             | RTE                | 16   | 250            | Green (RoHS & no Sb/Br)   | CU NIPDAU        | Level-2-260C-1 YEAR          |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

**NRND:** Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

PREVIEW: Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

(2) Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

TBD: The Pb-Free/Green conversion plan has not been defined.

**Pb-Free** (RoHS): TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes.

**Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

**Green (RoHS & no Sb/Br):** TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

(3) MSL, Peak Temp. -- The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

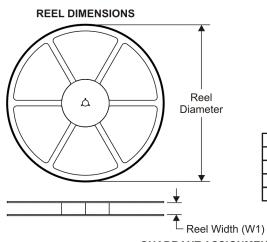

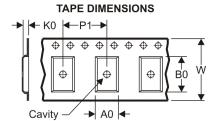

# TAPE AND REEL INFORMATION

| A0 | Dimension designed to accommodate the component width     |

|----|-----------------------------------------------------------|

|    | Dimension designed to accommodate the component length    |

| K0 | Dimension designed to accommodate the component thickness |

| W  | Overall width of the carrier tape                         |

| P1 | Pitch between successive cavity centers                   |

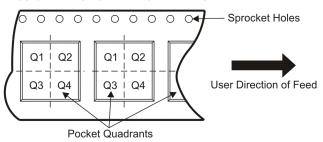

QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

## \*All dimensions are nominal

| Device       | Package<br>Type | Package<br>Drawing |    | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0 (mm) | B0 (mm) | K0 (mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|--------------|-----------------|--------------------|----|------|--------------------------|--------------------------|---------|---------|---------|------------|-----------|------------------|

| TPS60250RTER | QFN             | RTE                | 16 | 3000 | 330.0                    | 12.4                     | 3.3     | 3.3     | 1.1     | 8.0        | 12.0      | Q2               |

| TPS60250RTET | QFN             | RTE                | 16 | 250  | 180.0                    | 12.4                     | 3.3     | 3.3     | 1.1     | 8.0        | 12.0      | Q2               |

| TPS60252RTER | QFN             | RTE                | 16 | 3000 | 330.0                    | 12.4                     | 3.3     | 3.3     | 1.1     | 8.0        | 12.0      | Q2               |

| TPS60252RTET | QFN             | RTE                | 16 | 250  | 180.0                    | 12.4                     | 3.3     | 3.3     | 1.1     | 8.0        | 12.0      | Q2               |

\*All dimensions are nominal

| Device       | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|--------------|--------------|-----------------|------|------|-------------|------------|-------------|

| TPS60250RTER | QFN          | RTE             | 16   | 3000 | 346.0       | 346.0      | 29.0        |

| TPS60250RTET | QFN          | RTE             | 16   | 250  | 190.5       | 212.7      | 31.8        |

| TPS60252RTER | QFN          | RTE             | 16   | 3000 | 346.0       | 346.0      | 29.0        |

| TPS60252RTET | QFN          | RTE             | 16   | 250  | 190.5       | 212.7      | 31.8        |

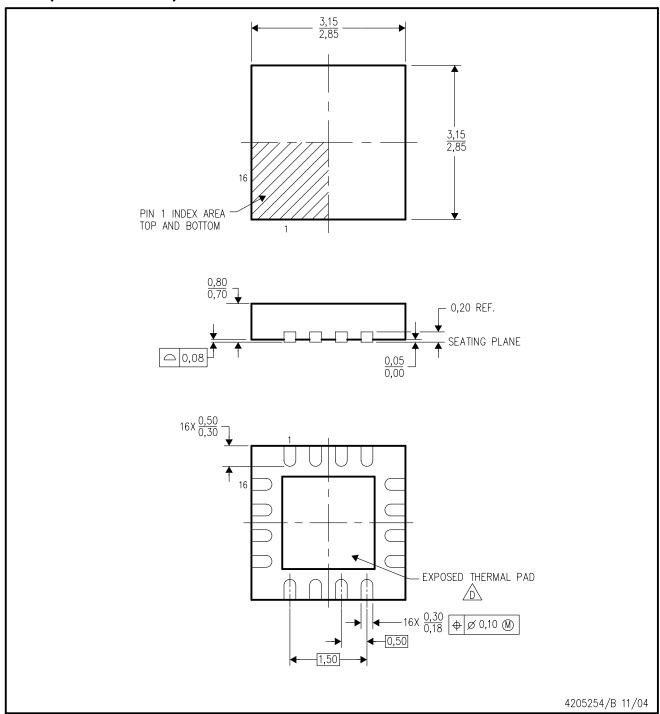

# RTE (S-PQFP-N16)

# PLASTIC QUAD FLATPACK

NOTES:

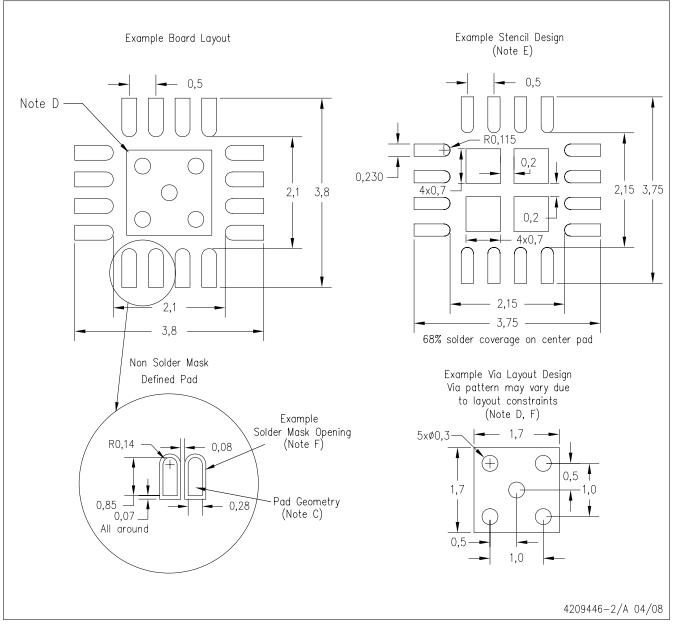

- A. All linear dimensions are in millimeters. Dimensioning and tolerancing per ASME Y14.5M-1994.

- B. This drawing is subject to change without notice.

- C. Quad Flatpack, No-leads (QFN) package configuration.

- The package thermal pad must be soldered to the board for thermal and mechanical performance. See the Product Data Sheet for details regarding the exposed thermal pad dimensions.

- E. Falls within JEDEC MO-220.

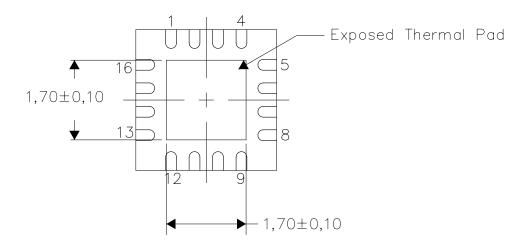

## THERMAL PAD MECHANICAL DATA

RTE (S-PWQFN-N16)

#### THERMAL INFORMATION

This package incorporates an exposed thermal pad that is designed to be attached directly to an external heatsink. The thermal pad must be soldered directly to the printed circuit board (PCB). After soldering, the PCB can be used as a heatsink. In addition, through the use of thermal vias, the thermal pad can be attached directly to the appropriate copper plane shown in the electrical schematic for the device, or alternatively, can be attached to a special heatsink structure designed into the PCB. This design optimizes the heat transfer from the integrated circuit (IC).

For information on the Quad Flatpack No—Lead (QFN) package and its advantages, refer to Application Report, QFN/SON PCB Attachment, Texas Instruments Literature No. SLUA271. This document is available at www.ti.com.

The exposed thermal pad dimensions for this package are shown in the following illustration.

Bottom View

NOTE: All linear dimensions are in millimeters

Exposed Thermal Pad Dimensions

# RTE (S-PWQFN-N16)

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Publication IPC-7351 is recommended for alternate designs.

- D. This package is designed to be soldered to a thermal pad on the board. Refer to Application Note, Quad Flat—Pack Packages, Texas Instruments Literature No. SCBA017, SLUA271, and also the Product Data Sheets for specific thermal information, via requirements, and recommended board layout. These documents are available at www.ti.com <a href="https://www.ti.com">https://www.ti.com</a>>.

- E. Laser cutting apertures with trapezoidal walls and also rounding corners will offer better paste release. Customers should contact their board assembly site for stencil design recommendations. Refer to IPC 7525 for stencil design considerations.

- F. Customers should contact their board fabrication site for minimum solder mask web tolerances between signal pads.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

TI products are not authorized for use in safety-critical applications (such as life support) where a failure of the TI product would reasonably be expected to cause severe personal injury or death, unless officers of the parties have executed an agreement specifically governing such use. Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications, and acknowledge and agree that they are solely responsible for all legal, regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications, notwithstanding any applications-related information or support that may be provided by TI. Further, Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.

TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or "enhanced plastic." Only products designated by TI as military-grade meet military specifications. Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk, and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS 16949 requirements. Buyers acknowledge and agree that, if they use any non-designated products in automotive applications, TI will not be responsible for any failure to meet such requirements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

**Applications Products Amplifiers** amplifier.ti.com Audio www.ti.com/audio Data Converters Automotive www.ti.com/automotive dataconverter.ti.com DLP® Products Broadband www.dlp.com www.ti.com/broadband DSP Digital Control dsp.ti.com www.ti.com/digitalcontrol Clocks and Timers www.ti.com/clocks Medical www.ti.com/medical Military Interface www.ti.com/military interface.ti.com Optical Networking Logic logic.ti.com www.ti.com/opticalnetwork Power Mgmt power.ti.com Security www.ti.com/security Telephony Microcontrollers microcontroller.ti.com www.ti.com/telephony Video & Imaging www.ti-rfid.com www.ti.com/video RF/IF and ZigBee® Solutions www.ti.com/lprf Wireless www.ti.com/wireless

> Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2009, Texas Instruments Incorporated