### CMOS 4-Bit Microcontroller

# TMP47C623F, TMP47C823F

The TMP47C623/823 are high speed and high performance 4-bit single chip microcomputers based on the TLCS-470A series with a LCD driver, High Speed Event Counter and Pulse output circuit.

| Part No.   | ROM          | RAM         | Package             | OTP Version  |

|------------|--------------|-------------|---------------------|--------------|

| TMP47C623F | 6144 × 8-bit | 384 × 4-bit | D OFFICA 1430 1 00A | TMD47D022\/F |

| TMP47C823F | 8192 × 8-bit | 512 × 4-bit | P-QFP64-1420-1.00A  | TMP47P823VF  |

#### **Features**

- ◆4-bit single chip microcomputer

- ◆Instruction execution time:

1.3  $\mu$ s (at 6 MHz), 244  $\mu$ s (at 32.8 kHz)

- ◆ 100 basic instructions

- Table look-up instructions

- ◆Subroutine nesting: 15 levels max.

- ◆6 interrupt sources (External: 2, Internal: 4)

All sources have independent latches each, and multiple interrupt control is available.

- ◆I/O port (32 to 28 pins)

- Input 2 ports 5 pins I/O 7 ports 27 pins

- ◆Two 12-bit Timer / Counters

Timer, event counter, and pulse width measurement mode

- ◆16-bit High Speed Event Counter

- ◆Interval Timer (22 stages)

- ◆Watchdog Timer

- ◆Serial Interface with 8-bit buffer

- Simultaneous transmission and reception capability.

- External / internal colck, leading / trailing edge, and 4/8-bit mode

- ◆LCD driver

- LCD direct drive capability (max. 12-digit display at 1/4 duty LCD)

- 1/4, 1/3 1/2 duties or static drive are programmably selectable.

TMP47C623F

TMP47C823F TMP47P823VF

- For a discussion of how the reliability of microcontrollers can be predicted, please refer to Section 1.3 of the chapter entitled Quality and Reliability Assurance / Handling Precautions.

- TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such TOSHIBA

- making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such TOSHIBA products could cause loss of human life, bodily injury or damage to property. In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the "Handling Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability Handbook" etc..

The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These TOSHIBA products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunction or failure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments transportation instruments traffic signal instruments control instruments, medical instruments. transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc.. Unintended Usage of TOSHIBA products listed in this document shall be made at the customer's

- The products described in this document are subject to the foreign exchange and foreign trade laws.

- The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA CORPORATION for any infringements of intellectual property or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any intellectual property or other rights of TOSHIBA CORPORATION or others.

The information contained herein is subject to change without notice.

2000-10-19 3-23-1

P-OFP64-1420-1.00A

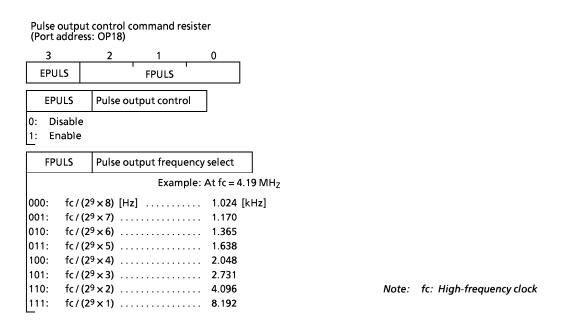

- ◆Pulse output

- Pulse output frequency select

- ♦ High current outputs

- LED direct drive capability (typ.20 mA x 4 bits)

- ◆Dual-clock operation

- High-speed / Low-power consumption operating mode

- ♦Hold function

- Battery / Capacitor back-up

- ◆Real Time Emulator: BM47C823F0A

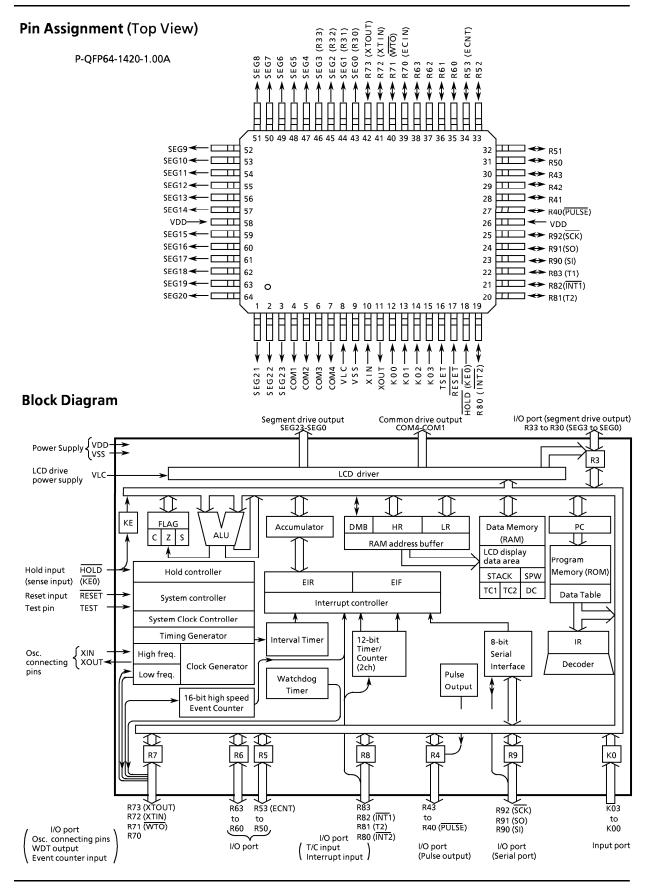

# **Pin Function**

| Pin Name                | Input/Output  | Fu                                                                                              | nctions                                                                            |  |  |  |

|-------------------------|---------------|-------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|--|--|--|

| K03 to K00              | Input         | 4-bit input port                                                                                |                                                                                    |  |  |  |

|                         |               | 4-bit I/O port with latch.                                                                      | LCD Segment drive output.                                                          |  |  |  |

| R33 to R30              | 1/0           | When used as input port the latch must be set to "1".                                           | When used as segment drive output the port R3 control resister must be set to "1". |  |  |  |

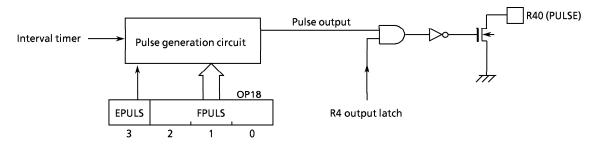

| R43 to R41              | 1/0           | 4-bit I/O port with latch. When used as input port, pulse output, the latch must be set to "1". |                                                                                    |  |  |  |

| R40 (PULSE)             | I/O (Output)  | the latch must be set to "1".                                                                   | Pulse output                                                                       |  |  |  |

| R53 (ECNT)              |               |                                                                                                 | External interrupt input                                                           |  |  |  |

| R52 to R50              | I/O           | 4-bit I/O port with latch.  When used as input port, External interru                           | pt input, the latch must be set to "1".                                            |  |  |  |

| R63 to R60              |               |                                                                                                 | ,                                                                                  |  |  |  |

| R73 (XTOUT)             | I/O (Output)  | 4-bit I/O port with latch.                                                                      | Resonator connecting pins.                                                         |  |  |  |

| R72 (XTIN)              | I/O (Input)   |                                                                                                 | For inputting external clock, XIN is used and XOUT is opened.                      |  |  |  |

| R71 (WTO)               | I/O (Output)  | When used as input port, watchdog                                                               | Watchdog timer output                                                              |  |  |  |

| R70 (ECIN)              | I/O           | timer output or External pulse input pin,<br>the latch must be set to "1".                      | External pulse input pin                                                           |  |  |  |

| R83 (T1)                | I/O           | 4-bit I/O port with latch.                                                                      | Timer/Counter 1 external input                                                     |  |  |  |

| R82 ( <del>INT1</del> ) |               | When used as input port, external                                                               | External interrupt 1 input                                                         |  |  |  |

| R81 (T2)                | I/O (Input)   | interrupt input pin, or Timer/Counter                                                           | Timer/Counter 2 external input                                                     |  |  |  |

| R80 ( <del>INT2</del> ) |               | external input pin, the latch must be set to "1".                                               | External interrupt 2 input                                                         |  |  |  |

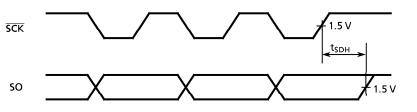

| R92 (SCK)               | I/O (I/O)     | 3-bit I/O port with latch.                                                                      | Serial clock I/O                                                                   |  |  |  |

| R91 (SO)                | I/O (Output)  | When used as input port, serial port the                                                        | Serial data output                                                                 |  |  |  |

| R90 (SI)                | I/O (Input)   | latch must be set to "1".                                                                       | Serial data input                                                                  |  |  |  |

| SEG23 to SEG0           |               | LCD Segment drive output                                                                        |                                                                                    |  |  |  |

| COM4 to COM1            | Output        | LCD Common drive output                                                                         |                                                                                    |  |  |  |

| XIN                     | Input         | Resonator connecting pins (high-frequence                                                       | cy) .                                                                              |  |  |  |

| XOUT                    | Output        | For inputting external clock, XIN is used a                                                     | nd XOUT is opened.                                                                 |  |  |  |

| RESET                   | Input         | Reset signal input                                                                              |                                                                                    |  |  |  |

| HOLD (KEO)              | Input (Input) | Hold request/ release signal input                                                              | Sense input                                                                        |  |  |  |

| TEST                    | Input         | Test pin for out-going test. Be opened or                                                       | fixed to low level.                                                                |  |  |  |

| VDD                     |               | +5V                                                                                             |                                                                                    |  |  |  |

| vss                     | Power supply  | oply 0 V (GND)                                                                                  |                                                                                    |  |  |  |

| VLC                     |               | LCD drive power supply                                                                          |                                                                                    |  |  |  |

## **Operational Description**

Concerning the TMP47C623/823 the configuration and functions of hardwars are described. As the description has been provided with priority on those parts deffering from the TMP47C1260/1660 (TLCS-470A), thehnical data sheets for the TMP47C1260/1660 shall also be referred to.

## 1. System Configuration

- (1) Internal CPU Function

- 2.1 Program Counter (PC)

- 2.2 Program Memory (ROM), and Data Table Bank Selector (DTB)

- 2.3 Data Memory (RAM)

The others are the same as those of the TMP47C1260/0660.

- (2) Peripheral Hardware Function

- ① I/O Port

- 2 Interval Timer

- 3 Timer/Counter

- Watchdog Timer

- **5** High Speed Event/Counter

- 6 Pulse output

- ① LCD Driver

- 8 Serial Interface

The description has been provide with priority on functions (①, ⑤, ⑥ and ⑦) added to and changed from the TMP47C1260/1660.

## 2. Internal CPU Function

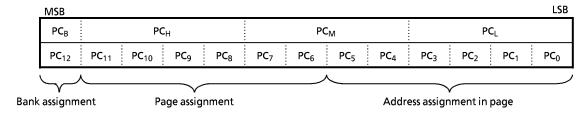

## 2.1 Program Counter (PC)

The program counter is a 13-bit binary counter which indicates the address of the program memory storing the next instruction to be executed.

Figure 2-1. Configuration of program counter

The PC can directly address an 8192-byte address space.

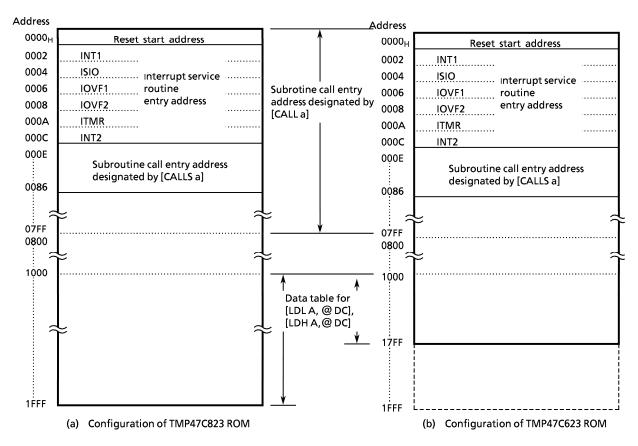

## 2.2 Program Memory (ROM), and Data Table Bank Selector (DTB)

The TMP47C823 contains a program memory (masked ROM) of 8192  $\times$  8 bit (addresses 0000 through 1FFF<sub>H</sub>). The TMP47C623 contains a program memory (masked ROM) of 6144  $\times$  8 bits (addresses 0000 through 17FF<sub>H</sub>). The TMP47C623/823 don't have a data table bank selector (DTB).

The fixed data is read from the table look-up instructions is located in the program memory (address 1000 through 17FF for the TMP47C623, 1000 through 1FFF for the TMP47C823) and the fixed data can specify the data counter of a 12-bit register.

3-23-5 2000-10-19

Figure 2-2. Program memory map

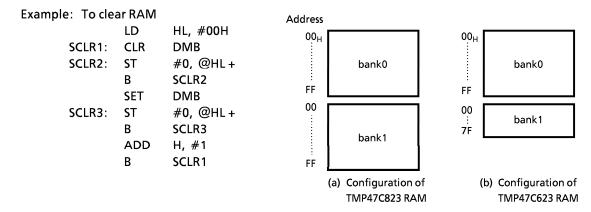

## 2.3 Data Memory Capacity

The TMP47C823 has two data memory banks (banks 0 and 1) of  $256 \times 4$  bit.

The TMP47C623 has a data memory banks 0 of  $256 \times 4bit$  and a data memory banks 1 of  $128 \times 4bit$ . A private stack (STK13) and stack pointer word (SPW13) for PC<sub>13</sub> have not been installed. When power-on is performed, the contents of the data memory become unpredictable, so that they must be initialized by the initialize routine.

When verifying the functions of the TMP47C623 with the TMP47P823V, addresses 80<sub>H</sub> and later in DMB1 should not be accessed.

Figure 2-3. Data memory (RAM)

## 3. Peripheral Hardware Function

## 3.1 I/O Port

The TMP47C623/823 have 9 I/O port (32 pins) each as follows.

- ① K0 ; 4-bit input

- ② R3 ; 4-bit input / output (shared with segment output)

- 3 R4; 4-bit input / output (R40 pin is shared with pulse output)

- R5 ; 4-bit input / output (R53 pin is shared with external interruput input)

- 5 R6; 4-bit input / output

- © R7; 4-bit input / output (shared with the Low-frequency reasonator connecting pin and the Watchdog timer output and high speed event counter input)

- R8; 4-bit input / output (shared with external interrupt and timer/counter input)

- 8 R9 ; 3-bit input / output (shared with serial port)

The description has been provided with priority on ports (②③④⑥ and ⑧) changed from TMP47C1660. Futher, TMP47C623/823 have not P1, P2 port, Therefore, the instruction [OUTB @ HL] and 5 bit to 8 bit data conversion table cannot be used.

Table 2-1 lists the port address assignments and the I/O instruction that can access the ports.

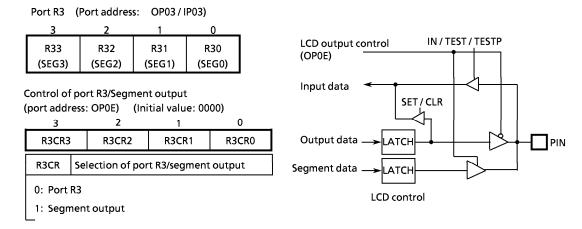

## (1) port R3 (R33 to R30)

Port R3 is a 4-bit I/O port with latch shared by the segment output pin of LCD Driver. The port R3 control register (OP0E) determine whether this port is used for I/O port or segment output. The port R3 control register is initialized to "0" during reset and the Port R3 is I/O port. When used as an input port, the latch showld be set to "1". The output latch of port R3 is initialized to "1" during reset.

Figure 3-1. Port R3

Table 3-1. Port address assignments and available I/O instruction

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | SET @L      | CLR @L<br>TEST @L          | ı             | ļ | I | 0                           | 0                             | 0                 | 0              | 0              | I              |                                                              | I                        | I                  | I                                             | ļ                 | -                                           | ł                           | ı               | l               | 1               | I               | I                      | I                    | 1           | I                    | 1                                | 1                    | ı                    | and a                   | ı                       | I                                          | 1                                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|----------------------------|---------------|---|---|-----------------------------|-------------------------------|-------------------|----------------|----------------|----------------|--------------------------------------------------------------|--------------------------|--------------------|-----------------------------------------------|-------------------|---------------------------------------------|-----------------------------|-----------------|-----------------|-----------------|-----------------|------------------------|----------------------|-------------|----------------------|----------------------------------|----------------------|----------------------|-------------------------|-------------------------|--------------------------------------------|--------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | TEST % P    | , d. %                     | 0             | I | 1 | 0                           | 0                             | 0                 | 0              | )(             | ) (            | )                                                            | 1                        | ı                  | ı                                             | 1                 | _                                           | I                           | ı               | I               | ı               | 1               | I                      | 1                    | ı           | ļ                    | ı                                | ŀ                    | ı                    |                         | ı                       | ı                                          | -                                          |

| i                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | SET % B b   | CLR %p, b                  | 1             | ì | ı | 0                           | 0                             | 0                 | 0 (            | )(             | )(             | )                                                            | ı                        | ı                  | ı                                             | ı                 |                                             | 1                           | ı               | 1               | 1               | ı               | 1                      | 1                    | l           | I                    | 1                                | 1                    | ı                    | ı                       | !                       | I                                          | I                                          |

| listi dettoli                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |             | оотв @нг                   |               | ı | ı | 1                           | I                             | ı                 | ı              | ı              |                |                                                              | ı                        | ı                  | 1                                             | ı                 | 1                                           |                             | ı               | I               | 1               | 1               | ı                      | I                    | ı           | ı                    | 1                                | 1                    | 1                    | ı                       | ı                       | 1                                          | 1                                          |

| indicate of the second |             | OUT #k, %p                 | I             | I | 1 | 0                           | 0                             | 0                 | 0(             | )(             |                |                                                              | 0                        | I                  | 0                                             | 0                 | 0                                           |                             | I               | I               | I               | 1               | ı                      | ı                    | 1           | ı                    | ı                                | 1                    | I                    | 1                       | ı                       | 1                                          | 1                                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | n V N N N N | OUT @HL,%p                 | I             | 1 | ŀ | 0                           | 0                             | 0                 | 0 (            | )(             | ) (            | ) (                                                          | 0                        | ı                  | 0                                             | 0                 | 0                                           | 0                           | ı               | 1               | ı               | 1               | 0                      | 0                    | 0           | 0                    | 0                                | 0                    | 0                    | 0                       | 0                       | 0                                          | 0                                          |

| Sill Sill Bisson                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Δ α% N      | %р, А<br>%р, @нц           | 0             | ı | 1 | 0                           | 0                             | 0                 | 0(             | )(             | ) (            | )                                                            | l                        | 0                  | 0                                             | 0                 | 0                                           | 0                           | 1               | 1               | ı               | 1               | 1                      | ı                    | 1           | ı                    | ı                                | 1                    | ı                    | 1                       | 1                       | ı                                          | 1                                          |

| 255                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |             |                            |               |   |   | _                           | Ē                             |                   |                |                |                |                                                              |                          | -                  |                                               |                   |                                             |                             |                 |                 |                 |                 |                        |                      |             |                      |                                  |                      |                      |                         |                         |                                            |                                            |

| 200                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ב  <br>ב    | Output (OP**)              |               |   |   | R3 output port (LCD OUTPUT) | R4 output port (PULSE OUTPUT) | R5 output port    | R6 output port | R7 output port | K8 output port | ng datpat port<br>HEC1 To Setting register                   | HEC2 Tb Setting resister |                    | Window gate pulse control                     | R3 output control | Serial tansmit buffer                       | Hold operating mode control |                 |                 |                 |                 | Watchdog timer control | System clock control | HEC Control | Pulse output control | Interval Timer interrupt control | LCD driver control 1 | LCD driver control 2 | Timer/Counter 1 control | Timer/Counter 2 control | Serial Interface control 1                 | Serial Interface control 2                 |

| ו מסוב טיין.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Port        | Input (IP**) Output (OP**) | K0 input port |   |   | R3 input port (LCD OUTPUT)  |                               | (Interrupt input) | (HEC input)    |                |                | NS Output point HEC Chatus (Note 2) HECT To Setting register | (1010 5)                 | HEC Low data input | HEC High data input Window gate pulse control |                   | Serial receive buffer Serial tansmit buffer |                             | HOLD pin status | HOLD pin status | HOLD pin status | HOLD pin status |                        |                      |             |                      |                                  |                      |                      |                         |                         | HOLD pin status Serial Interface control 1 | HOLD pin status Serial Interface control 2 |

Note 1: "——" means the reserved state. Unavailable for the user programs.

To detect the overflow and status input of the high speed event counter (HEC). The status input of serial interface, clock generator, and  $\overline{\text{HOLD}}$  (KEO) pin. Note 2: Note 3:

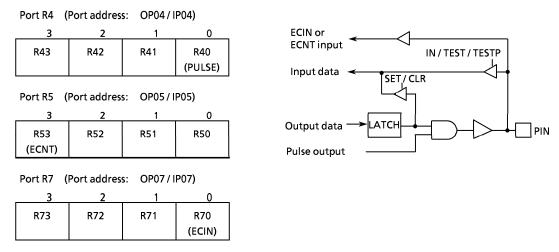

### (2) Port R4 (R43-R40), R5 (R53-R50), R7 (R73-R70)

The 4-bit I/O ports with a latch. When used as an input port, the latch showld be set to "1". The latch is initialized to "1" during reset. R40 pin is shared by pulse output pin. To use this pin for the functional pin, the latch must be set to "1".

R53 pin is shared by pulse input pin. To use this pin for the functional pin, the latch must be set to "1". R70 pin is shared by high speed event counter pin. To use this pin for the functional pin, the latch must be set to "1".

Figure 3-2. Port R4, R5, R7

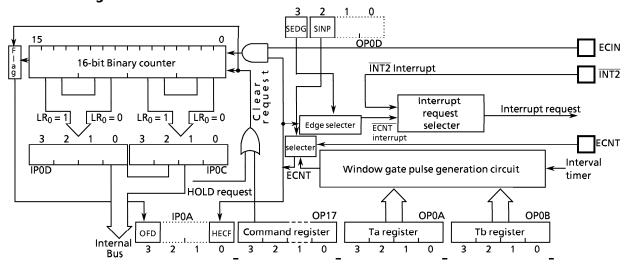

## 3.2 High Speed Event/Counter (HEC)

The TMP47C623/823 have a 16-bit high-speed event counter (HEC) which can be used for ECIN pin input frequency measurement. HEC counts the edge (falling edge, falling edge/rising edge) of input pulses while the window gate pulse is at "H" level and interrupt requests (ECNT) are generated when the window gate pulse edge (falling edge, falling edge/rising edge).

The window gate pulse cycle is set by command.

The ECIN pin is also used as the R70 pin. When used as the ECIN pin, the R70 output latch is set to "1".

## 3.2.1 Configuration of HEC circuit

Figure 3-3. Configuration of high-speed event/counter

### 3.2.2 Control of HEC

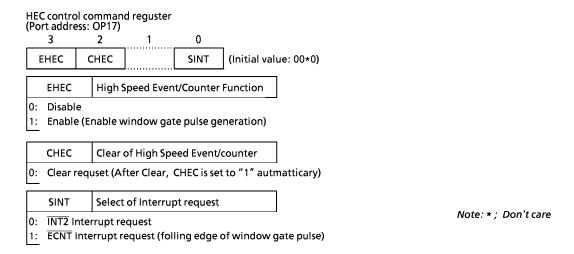

HEC is controlled by the command register (OP17). External interrupt 2 is used as the interrupt source. The INT2 interrupt request is selected during reset, so ECNT interrupt is requested by command. Interrupt priority is the same as for external interrupt 2.

Figure 3-4. HEC control command resister

## 3.2.3 HEC operation

HEC counts input frequency only during the intervals that the window gate pulse is at "H" level when EHEC (command register bit 3) is "1". The window gate pulse can be set to 256 different cyclse using port addresses OPOA and OPOB.

### (1) Select of window gate pulse input

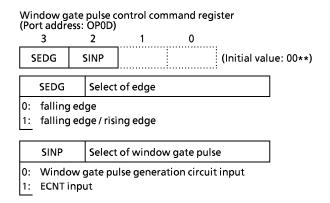

The window gate pulse (ECNT) input can be set to the window gate pulse generation circuit or ECNT input (R53) using SINP (bit 2) of command register (OP0D).

The window gate pulse is selected the window gate pulse generation circuit during initial.

Figure 3-5. Window gate pulse control command register

### (2) Window gate pulse setting

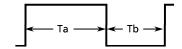

The window gate pulse (ECNT) consists of a count time (Ta) and non-count time (Tb), each of which can be set independently using OPOA and OPOB. Thus, one cycle is Ta + Tb. The Ta and Tb setting times are as follows.

$$(16-n) \times 2^{13}/fc$$

[s]  $(n = 0 \text{ to } 15)$

Table 3-2 shows the setting times when fc = 4.194304 MHz ECNT can be generated at the next rise edge of interval timer output ( $fc/2^{13}$  [Hz] by setting EHEC = 1.)

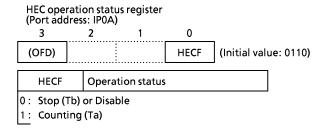

Figure 3-6. HEC operation status register

Example: Generating ECNT with a cycle of approximately 29 ms and a duty ratio of 3:2.

OUT #07H, %0P0A ; Set Ta to 17.58 ms OUT #0AH, %0P0B ; Set Tb to 11.72 msC

LD A, #0FH

OUT A, % OP17 ; Enables ECNT generation

Table 3-2. Setting of Ta, Tb

| Setting<br>value | Setting time | Setting<br>value | Setting time |

|------------------|--------------|------------------|--------------|

| 0                | 31.25 ms     | 8                | 15.63 ms     |

| 1                | 29.30 ms     | 9                | 13.67 ms     |

| 2                | 27.34 ms     | Α                | 11.72 ms     |

| 3                | 25.39 ms     | В                | 9.77 ms      |

| 4                | 23.44 ms     | С                | 7.81 ms      |

| 5                | 21.48 ms     | D                | 5.86 ms      |

| 6                | 19.53 ms     | Е                | 3.91 ms      |

| 7                | 17.58 ms     | F                | 1.95 ms      |

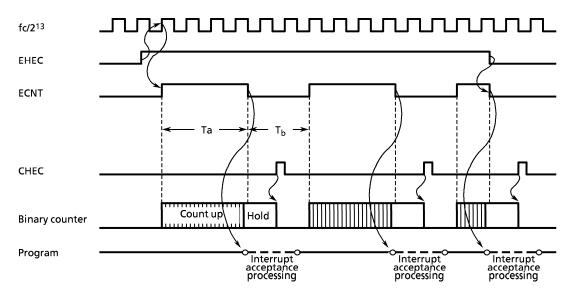

#### (3) Count operation

Counting is enabled by setting EHEC to "1". Counting is stopped by clearing EHEC to "0" but the binary count values are held.

An INT2 interrupt is issued at the fall edge of the window gate pulse when SINT(command register bit 0) is set to "1". Normally, binary counter date are read, the counter cleared and the next count operation started by the interrupt service routine.

Select of window gate pulse edge can be set to edge (falling edge, falling edge/rising edge) using SEDG of command register (OPOD).

The binary counter is cleared with CHEC (command register bit2). EHEC and the binary counter are cleared during hold operation.

The window gate pulse (ECNT) status can be monitored using the status register. "1" is read out at "H" level (during counting). Figure 3-7 shows the HEC operation timing.

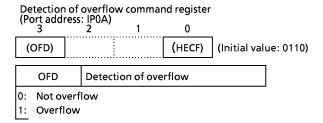

The detection of overflow (binary counter) can be monitored using the OFD (bit3) of command register (IPOA). The flag of OFD is held till the CHEC is cleaved to "0".

Figure 3-8. Detection of overflow command register

## (4) Reading of count data

Binary counter data are read out by port addresses IPOC and IPOD. At that time, a total of 16 bits of data is read out by reading 4 bits at a time in accordance with the LR0 (L register bit 0) value. Table 3-3 shows the relationship between port address LR0 and count data.

| Port address | LR <sub>0</sub> | Reading bit of HEC |

|--------------|-----------------|--------------------|

| IDOC         | 0               | HEC3 to HEC0       |

| IP0C         | 1               | HEC7 to HEC4       |

| IDOD         | 0               | HEC11 to HEC8      |

| IP0D         | 1               | HEC15 to HEC12     |

Table 3-3. The relation ship between port address LR0 or count data

Figure 3-7. HEC operation timing

## 3.3 Pulse output circuit

The TMP47C623/823 has a built-in one-channel pulse output to use in driving, for example, a buzzer. Eight different pulse output frequencies can be selected by command. Pulses are output from the PULSE pin. The PULSE pin is also used as the R40 pin. When used as the PULSE pin, the R40 output latch is set to "1".

## 3.3.1 Control of pulse output circuit

The pulse output circuit is controlled by the command register (OP18). Pulses are output by setting EPULS to "1". Pulse output is disabled (by clearing OP18 to "0") during hold operation.

Figure 3-9. Pulse output circuit

Figure 3-10. Pulse output command resister

### 3.4 LCD Driver

The TMP47C623/823 have the circuit that directly drives the liquid crystal display (LCD) and its control circuit.

The TMP47C623/823 have the following connecting pins with LCD.

- ① Segment output port 24 pins (SEG23 to SEG4)

- ② Segment output port (R3 I/O port) 4 pins (SEG3 to SEG0)

- ③ Common output port 4 pins (COM4 to COM1)

In addition, VLC pin is provided as the drive power pin.

The devices that can be directly driven is selectable from LCD of the following drive methods.

```

1/4 Duty (1/3 Bias) LCD ...... Max. 96 Segment (12 digits × 8 segments)

1/3 Duty (1/3 Bias) LCD ...... Max. 72 Segment (9 digits × 8 segments)

1/3 Duty (1/2 Bias) LCD ...... Max. 72 Segment (9 digits × 8 segments)

1/2 Duty (1/2 Bias) LCD ...... Max. 48 Segment (6 digits × 8 segments)

Static LCD ....... Max. 24 Segment (3 digits × 8 segments)

```

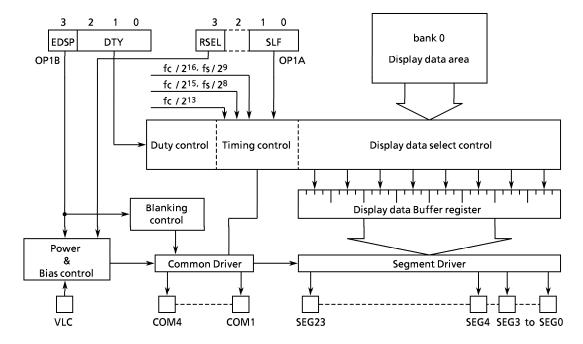

## 3.4.1 Configuration of LCD driver

Figure 2-8 shows the configuration of the LCD driver.

Figure 3-11. LCD driver

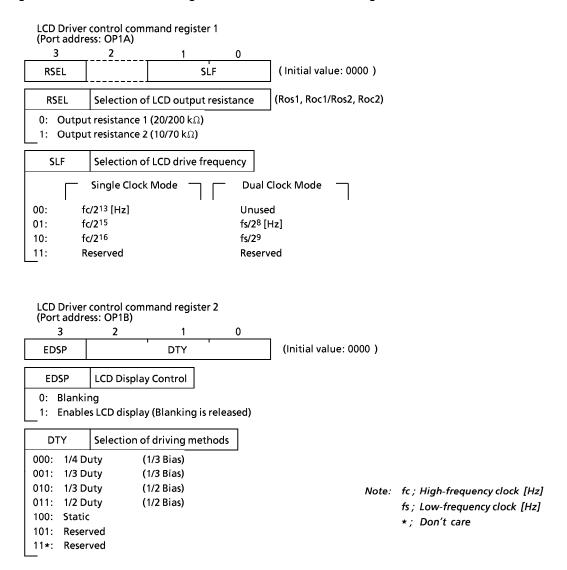

### 3.4.2 Control of LCD driver circuit

The LCD driver is controlled by the command register 1,2 (OP1A, OP1B). Further, when the command register 1 is accessed, the most significant bit of the command register 2 must be set to "0" (Blanking).

Figure 3-12. LCD driver control Command Register

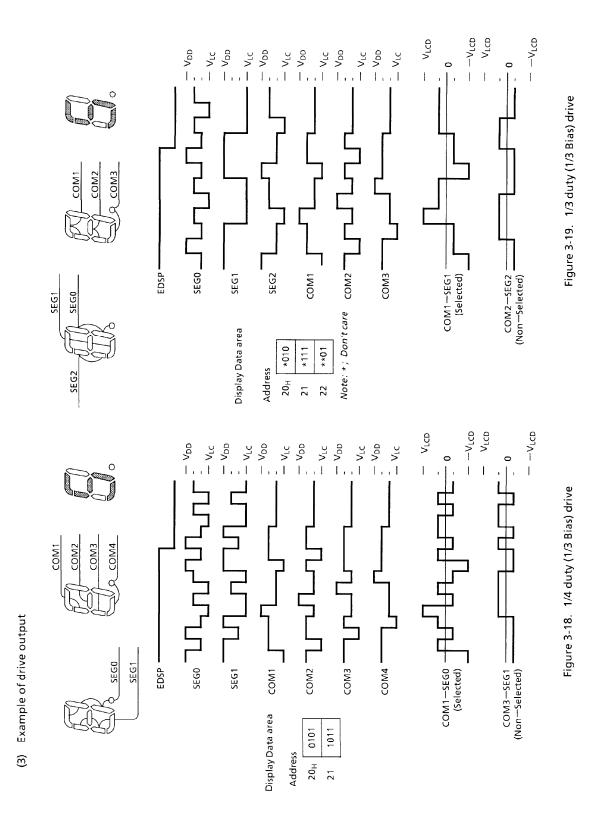

#### (1) Driving methods of LCD driver

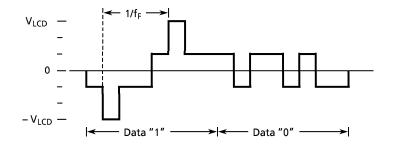

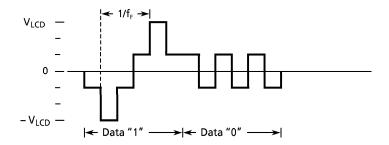

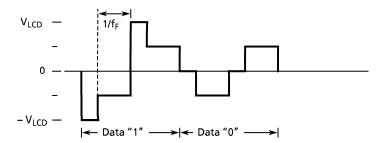

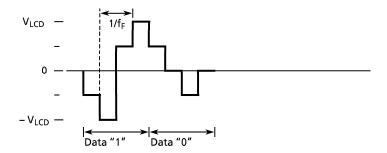

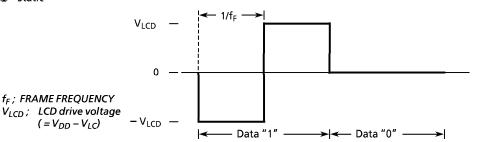

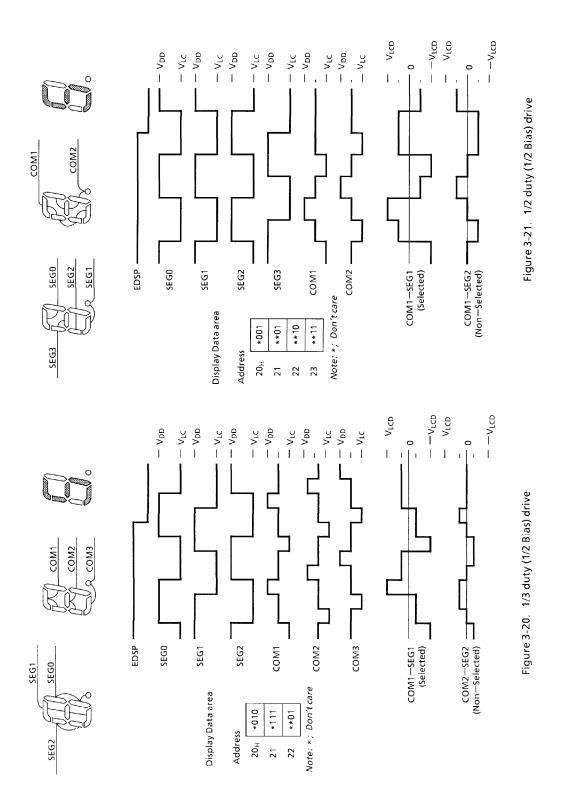

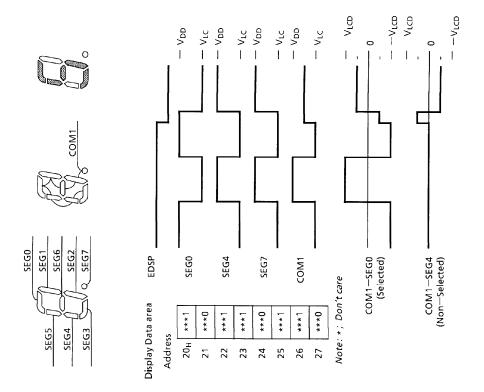

Driving methods of LCD is selected 5 kind of DTY (bit 2 to 0 of command register 2). The drive method is initialized according to LCD used in the initial program. Example of LCD and their drive waveform are shown in Figure 3-13.

① 1/4 Duty (1/3 Bias)

② 1/3 Duty (1/3 Bias)

3 1/3 Duty (1/2 Bias)

4 1/2 Duty (1/2 Bias)

⑤ Static

Note:  $f_F$ ; FRAME FREQUENCY

$(=V_{DD}-V_{LC})$

Figure 3-13. LCD drive waveform (COM-SEG pins)

#### (2) Frame frequency

Frame frequency (f<sub>F</sub>) is set according to the drive method and base frequency as shown in the following Table 3-4.

The base frequency is selected by SLF (the lower 2 bits of the command register) according to the reference clock frequency and fs.

Table 3-4. Setting of LCD frame frequency

### a. At the single clock mode

| CI E |                        | Frame Frequency [Hz]   |                                       |                                       |                        |  |  |  |  |  |

|------|------------------------|------------------------|---------------------------------------|---------------------------------------|------------------------|--|--|--|--|--|

| SLF  | Base Frequency [Hz]    | 1/4 Duty               | 1/3 Duty                              | 1/2 Duty                              | Static                 |  |  |  |  |  |

| 10   | fc 2 <sup>16</sup>     | fc                     | $\frac{4}{3} \cdot \frac{fc}{2^{16}}$ | $\frac{4}{2} \cdot \frac{fc}{2^{16}}$ | fc                     |  |  |  |  |  |

|      | fc = 4 MHz             | 61                     | 81                                    | 122                                   | 61                     |  |  |  |  |  |

|      | _fc_                   | _fc                    | _4fc_                                 | _4fc_                                 | fc                     |  |  |  |  |  |

| 01   | <b>2</b> <sup>15</sup> | <b>2</b> <sup>15</sup> | 3 2 <sup>15</sup>                     | 2 2 <sup>15</sup>                     | <b>2</b> <sup>15</sup> |  |  |  |  |  |

|      | fc = 4 MHz             | 122                    | 163                                   | 244                                   | 122                    |  |  |  |  |  |

| 00   | fc 2 <sup>13</sup>     | fc 2 <sup>13</sup>     | $\frac{4}{3} \cdot \frac{fc}{2^{13}}$ | $\frac{4}{2} \cdot \frac{fc}{2^{13}}$ | fc 2 <sup>13</sup>     |  |  |  |  |  |

|      | fc = 1 MHz             | 122                    | 163                                   | 244                                   | 122                    |  |  |  |  |  |

Note: fc; High-frequency clock [Hz]

#### b. At the dual clock mode

| 41.5 |                             | Frame Frequency [Hz] |             |           |                             |  |  |  |  |  |

|------|-----------------------------|----------------------|-------------|-----------|-----------------------------|--|--|--|--|--|

| SLF  | Base Frequency [Hz]         | 1/4 Duty             | 1/3 Duty    | 1/2 Duty  | Static                      |  |  |  |  |  |

| 10   | <u>fs</u><br>2 <sup>9</sup> | fs                   | 4/3 · fs/29 | 4 · fs 29 | <u>fs</u><br>2 <sup>9</sup> |  |  |  |  |  |

|      | fs = 32 kHz                 | 61                   | 83          | 125       | 61                          |  |  |  |  |  |

| 01   | <u>fs</u><br>28             | <u>fs</u><br>28      | 4 · fs 28   | 4 · fs 28 | <u>fs</u><br>28             |  |  |  |  |  |

|      | fs = 32 kHz                 | 125                  | 167         | 250       | 125                         |  |  |  |  |  |

Note: fs; Low-frequency clock [Hz]

### (3) LCD drive voltage

The LCD drive voltage ( $V_{LCD}$ ) is given by the difference in potential ( $V_{DD}$  to  $V_{LC}$ ) between pins VDD and VLC. Therefore, when the CPU operating voltage and LCD drive voltage are the same, the VLC pin is connected to the VSS pin.

The LCDs light only when the difference in potential between the segment output and common output is  $\pm V_{LCD}$ , and turn off at all other times.

During reset, the power switch of the LCD driver is turned off automatically, shutting off the VLC voltage.

Both the segment output and common output become  $V_{\mbox{\scriptsize DD}}$  level at this time and the LCDs turn off.

The power switch is turned on to supply VLC voltage to the LCD driver by setting EDSP (bit 3 of the command register 2) to "1". After that, the power switch will not turn off even during blanking (setting EDSP to "0") and the VLC voltage continues to flow.

The power switch is turned off during hold operation low power consumption by turning off the LCD. When hold operation is released the status in effect immediately before the hold operation is reinstated.

### (4) LDC output resistance

Selection of LCD output resistance can be selected by command register (OP1A).

The LDC output resistance is selected by RSEL (MSB of command register) according to LCD used.

The LDC output resistance is selected 20/200  $k\Omega$  (RSEL) during initial.

Table 3-5. Selection of LCD output resistance

| DCEL | Output low               | resistance              | Output high resistance   |                         |  |  |

|------|--------------------------|-------------------------|--------------------------|-------------------------|--|--|

| RSEL | Segment R <sub>OS1</sub> | Common R <sub>OC1</sub> | Segment R <sub>OS2</sub> | Common R <sub>OC2</sub> |  |  |

| 0    | 20                       | kΩ                      | 200                      | kΩ                      |  |  |

| 1    | 10                       | kΩ                      | 70                       | kΩ                      |  |  |

Note: The output resistance shows Typ. values (Topr =  $25^{\circ}$ C, VDD =  $5^{\circ}$ V)

## 3.4.3 LCD display operation

### (1) Display data setting

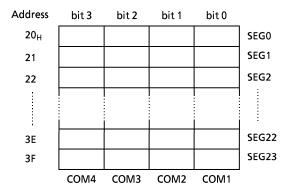

Display data are stored to the display data area (Max 32 words) in the data memory (bank0).

The display data stored to the display data area (address 20-3F<sub>H</sub>) are read automatically and sent to the LCD driver by the hardware.

The LCD driver generates the segment signals and common signals in accordance with the display data and drive method. Therefore, display patterns can be changed by only overwriting the contents of the display data area with a program. The table look up instruction is mainly used for this overwriting.

Figure 3-14 shows the correspondence between the display data area and the SEG/COM pins. The LCD light when the display data is "1" and turn off when "0".

The number of segment which can be driven differs depending on the LCD drive method therefore, the number of display data area bits used to store the data also differs. Consequently, data memory not used to store display data and data memory for which the addresses are not connected to LCD can be used to store ordinary user's processing data.

Figure 3-14. LCD display data area (Bank 0)

Table 3-6. Drivinig method and bit for display data

| Driving methods | bit 3 | bit 2 | bit 1 | bit 0 |

|-----------------|-------|-------|-------|-------|

| 1/4 Duty        | сом4  | сомз  | СОМ2  | COM1  |

| 1/3 Duty        | _     | сомз  | СОМ2  | COM1  |

| 1/2 Duty        | _     | -     | СОМ2  | COM1  |

| Static          | _     | -     | -     | COM1  |

Note: -; This bit is not used for display data.

#### (2) Blanking

Blanking is applied by setting EDSP to "0" and turns off the LCD by outputting the non light operation level to the COM pin.

The SEG pin continuously outputs the signal level in accordance with the display data and drive method.

With static drive, no voltage is applied between the COM and SEG pins when the LCD is turned off by data (display data cleared to "0"), but the COM pin output becomes constant at the  $V_{LCD}/2$  level when turning off the LCD by blanking, so the COM and SEG pins are then driven by  $V_{LCD}/2$ .

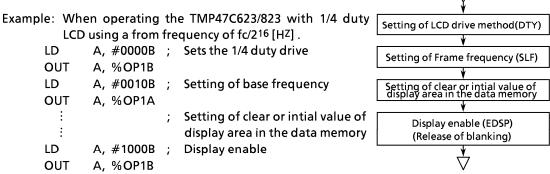

### 3.4.4 Control method of LCD driver

#### (1) Initial Setting

Flow chart of intial setting are as shown in Figure 3-15.

Figure 3-15. Intial setting of LCD driver

## (2) Store of display data

Normally, display data are kept permanently in the program memory and are then stored to the display data area by the table look-up instruction.

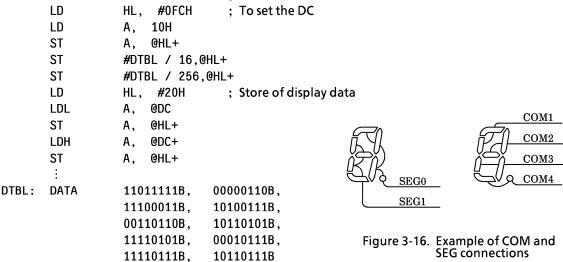

This can be explained using numerical display with 1/4 duty LCD as an example. The COM and SEG connections to the LCD are the same as those shown in Figure 3-16 and the display data are as shown in Table 3-7. Programming example for displaying numerals corresponding to BCD data stored at address 10<sub>H</sub> in the data memory is shown below.

3-23-19 2000-10-19

Table 3-7. Example of display data (1/4 Duty LCD)

| Normanal | Diaglass                                | Displa | y data | Normanal | Diaglass                                | Displa | y data |

|----------|-----------------------------------------|--------|--------|----------|-----------------------------------------|--------|--------|

| Numeral  | Display                                 | Upper  |        |          | Display                                 | Upper  | Lower  |

| 0        |                                         | 1101   | 1111   | 5        |                                         | 1011   | 0101   |

| 1        | *************************************** | 0000   | 0110   | 6        |                                         | 1111   | 0101   |

| 2        |                                         | 1110   | 0011   | 7        | *************************************** | 0001   | 0111   |

| 3        |                                         | 1010   | 0111   | 8        |                                         | 1111   | 0111   |

| 4        | <b>-</b>                                | 0011   | 0110   | 9        |                                         | 1011   | 0111   |

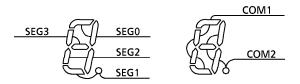

Table 3-8 shows the same numerical display used in Table 3-7, but using 1/2 duty LCD. The connections of the COM and SEG pins to the LCD are the same as those shown in Figure 3-17.

Figure 2-17 Example of COM and SEG connections

Table 3-8. Example of display data (1/2 Duty LCD)

| Numeral |      | Displa | y data |      | Numeral - | Display data |      |       |      |  |

|---------|------|--------|--------|------|-----------|--------------|------|-------|------|--|

| Numeral | Upp  | er     | Lo     | ower | Numeral   | Upp          | er   | Lower |      |  |

| 0       | **01 | **11   | **01   | **11 | 5         | **11         | **10 | **01  | **01 |  |

| 1       | **00 | **10   | **00   | **10 | 6         | **11         | **11 | **01  | **01 |  |

| 2       | **10 | **01   | **01   | **11 | 7         | **01         | **10 | **00  | **11 |  |

| 3       | **10 | **10   | **01   | **11 | 8         | **11         | **11 | **01  | **11 |  |

| 4       | **11 | **10   | **00   | **10 | 9         | **11         | **10 | **01  | **11 |  |

Note: \*; Don't care

3-23-22 2000-10-19

3-23-23 2000-10-19

Figure 2-11. Static drive

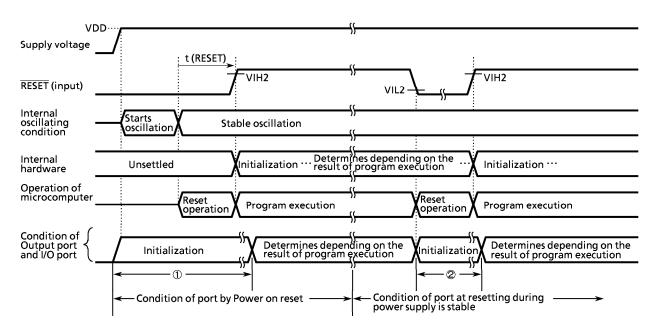

## **Port Condition by RESET Operation**

The transition of Port condition by RESET operation is shown as below.

Figure 2-12. Port condition by Reset operation

- Note 1: t(RESET) > 24/fc

- Note 2: VIL2: Stands for low level input voltage of RESET pin.

- VIH2: Stands for high level input voltage of RESET pin.

- Note 3: The term from power on reset to the time program is executed (above ①) and also the term starting from reset operation during power supply is stable to the program is executed (above ②), the port is on the initial condition. The initial condition of Port differs from I/O circuit by each port, refer to the section of "INPUT/OUTPUT CIRCUITRY". Thus, when using Port as an output pin, in the term of the above ① and ②, the voltage level on the signal that connects with the output pin of Port to the input pin of external application circuit should be determined by the external circuitry such as pull-up resistor and / or pull-down resistor.

3-23-25 2000-10-19

## **Input / Output Circuitry**

(1) Control pins

The input / output circuitries of the TMP47C623/823 control pins are similar to those of the TMP47C1260/1660.

(2) I/O Ports

The input / output circuitries of the TMP47C623/823 I/O ports are shown as belows, any one of the circuitries can be chosen by a code (GA to GF) as a mask option.

| Port     | I/O   | In                                                | out / Output Circu | itry and Code  | e                                                                       | Remarks                                                                                                                                                                  |

|----------|-------|---------------------------------------------------|--------------------|----------------|-------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| К0       | Input | GA, GD  R R R                                     | GB, GI             |                | GC, GF  R <sub>IN</sub> R <sub>IN</sub> R <sub>IN</sub> R <sub>IN</sub> | Pull-up/pull-down resister $R_{IN} = 70 \text{ k}\Omega \text{ (typ.)}$                                                                                                  |

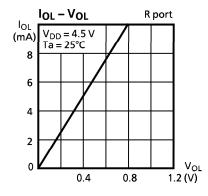

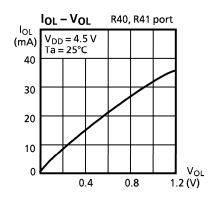

| R4       | I/O   |                                                   | NV R               |                | <i>m</i>                                                                | $R = 1  \text{k}\Omega  \text{(typ.)}$ Sink open drain output Initial "Hi-Z" High current $I_{OL} = 20  \text{mA}  \text{(typ.)}$ $R = 1  \text{k}\Omega  \text{(typ.)}$ |

| R5<br>R6 | I/O   | GA, GB, GC Initial "Hi-Z"                         | ₹R                 | Initial "High  | GD, GE, GF                                                              | Sink open darin output or push-pull output $R=1~k\Omega$ (typ.)                                                                                                          |

| R7       | I/O   |                                                   |                    | ≱R             |                                                                         | Sink open drain output Initial "Hi-Z" $R=1~k\Omega~(typ.)$                                                                                                               |

| R8<br>R9 | 1/0   |                                                   |                    | R <sup>R</sup> | 1                                                                       | Sink open drain output Initial "Hi-Z" Hysteresis input $R=1~k\Omega$ (typ.)                                                                                              |

| R3       | 1/0   | Segment output —————————————————————————————————— |                    | R <sup>R</sup> | ]                                                                       | Sink open drain output or Segment output $R=1~k\Omega$ (typ.)                                                                                                            |

## **Electrical Characteristics**

$(V_{SS} = 0 V)$ **Absolute Maximum Ratings**

| Parameter                       | Symbol             | Pins                                                 | Ratings                        | Unit |  |

|---------------------------------|--------------------|------------------------------------------------------|--------------------------------|------|--|

| Supply Voltage                  | $V_{DD}$           |                                                      | – 0.3 to 7                     | V    |  |

| Supply Voltage (LCD drive)      | $V_{LC}$           |                                                      | - 0.3 to V <sub>DD</sub> + 0.3 | ٧    |  |

| Input Voltage                   | V <sub>IN</sub>    |                                                      | – 0.3 to V <sub>DD</sub> + 0.3 | V    |  |

| Output Voltage                  | V <sub>OUT1</sub>  | Except sink open drain pin, but include ports R7, R3 | - 0.3 to V <sub>DD</sub> + 0.3 | V    |  |

|                                 | V <sub>OUT2</sub>  | Sink open drain pin, but include ports R7, R3        | - 0.3 to 10                    |      |  |

| Output Current (Per 1 pin)      | I <sub>OUT1</sub>  | Except port R4                                       | 3.2                            |      |  |

|                                 | I <sub>OUT2</sub>  | Port R4                                              | 30                             | mA   |  |

| Output Current (Total)          | Σ I <sub>OUT</sub> | Port R4                                              | 60                             | mA   |  |

| Power Dissipation [Topr = 50°C] | PD                 |                                                      | 600                            | mW   |  |

| Soldering Temperature (time)    | Tsld               |                                                      | 260 (10 s)                     | °C   |  |

| Storage Temperature             | Tstg               |                                                      | – 55 to 125                    | °C   |  |

| Operating Temperature           | Topr               |                                                      | – 40 to 70                     | °C   |  |

Note: The absolute maximum ratings are rated values which must not be exceeded during operation, even for an instant. Any one of the ratings must not be exceeded. If any absolute maximum rating is exceeded, a device may break down or its performance may be degraded, causing it to catch fire or explode resulting in injury to the user. Thus, when designing products which include this device, ensure that no absolute maximum rating value will ever be exceeded.

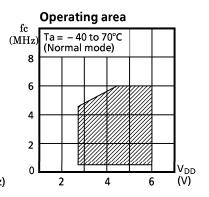

**Recommended Opeating Conditions**

$(V_{SS} = 0 \text{ V}, \text{ Topr} = -40 \text{ to } 70^{\circ}\text{C})$

| Parameter          | Symbol           | Pins                    | Conditions                                     | Min                  | Max                  | Unit             |

|--------------------|------------------|-------------------------|------------------------------------------------|----------------------|----------------------|------------------|

| Supply Voltage     |                  |                         | In the Normal mode                             | 2.7                  |                      |                  |

|                    |                  |                         | (fc = 4.2 MHz)                                 |                      |                      |                  |

|                    |                  |                         | In the Normal mode                             | 2.9                  |                      |                  |

|                    | .,               |                         | (fc = 5.0 MHz) Note3                           | 2.3                  |                      | l <sub>v</sub> l |

|                    | $V_{DD}$         |                         | In the Normal mode                             | 4.5                  | 6.0                  | V                |

|                    |                  |                         | (fc = 6.0 MHz)                                 | 4.5                  |                      |                  |

|                    |                  |                         | In the SLOW mode                               | 2.7                  |                      |                  |

|                    |                  |                         | In the HOLD mode                               | 2.0                  |                      |                  |

| Input High Voltage | $V_{IH1}$        | Except Hysteresis Input | V <sub>DD</sub> ≧ 4.5 V                        | $V_{DD} \times 0.7$  |                      | V                |

|                    | $V_{\text{IH2}}$ | Hysteresis Input        | V <sub>DD</sub> ≅ 4.3 V                        | $V_{DD} \times 0.75$ | $V_{DD}$             |                  |

|                    | V <sub>IH3</sub> |                         | V <sub>DD</sub> < 4.5 V                        | $V_{DD} \times 0.9$  |                      |                  |

| Input Low Voltage  | $V_{IL1}$        | Except Hysteresis Input | V <sub>DD</sub> ≧ 4.5 V                        |                      | $V_{DD} \times 0.3$  |                  |

|                    | $V_{IL2}$        | Hysteresis Input        | V <sub>DD</sub> ≦ 4.3 V                        | 0                    | $V_{DD} \times 0.25$ | V                |

|                    | V <sub>IL3</sub> |                         | V <sub>DD</sub> < 4.5 V                        |                      | $V_{DD} \times 0.1$  |                  |

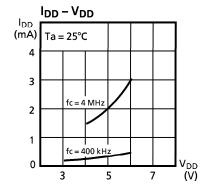

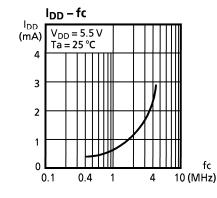

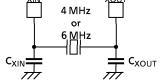

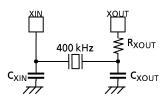

| Clock Frequency    | fc               | XIN, XOUT               | High freq. V <sub>DD</sub> ≧2.7 V              |                      | 4.2                  |                  |

|                    |                  |                         | High freq. $V_{DD} \ge 2.9  V^{\text{Note 3}}$ | 0.4                  | 5.0                  | MHz              |

|                    |                  |                         | High freq. $V_{DD} \ge 4.5 V$                  |                      | 6.0                  |                  |

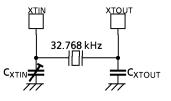

|                    | fs               | XTIN, XTOUT             | Low freq.                                      | 30.0                 | 34.0                 | kHz              |

Note 1: The recommended operating conditions for a device are operating conditions under which it can be guaranteed that the device will operate as specified. If the device is used under operating conditions other than the recommended operating conditions (supply voltage, operating temperature range, specified AC/DC values etc.), malfunction may occur. Thus, when designing products which include this device, ensure that the recommended operating conditions for the device are always adhered to.

Note 2: Input Voltage  $V_{IH3}$ ,  $V_{IL3}$ : in the SLOW and HOLD mode. Note 3: Operating Temperature -30 to  $50^{\circ}$ C

2000-10-19 3-23-27

**DC Characteristics**

$(V_{SS} = 0 \text{ V}, \text{ Topr} = -40 \text{ to } 70^{\circ}\text{C})$

| Parameter                                             | Symbol            | Pins                                          | Conditions                                                                                             | Min | Тур.  | Max        | Unit |

|-------------------------------------------------------|-------------------|-----------------------------------------------|--------------------------------------------------------------------------------------------------------|-----|-------|------------|------|

| Hysteresis Voltage                                    | V <sub>HS</sub>   | Hysteresis Input                              |                                                                                                        | _   | 0.7   | -          | V    |

| Input Current                                         | I <sub>IN1</sub>  | Port K0, TEST, RESET, HOLD  Open drain R port | V <sub>DD</sub> = 5.5 V,<br>V <sub>IN</sub> = 5.5 V / 0 V                                              | _   | _     | ± 2        | μΑ   |

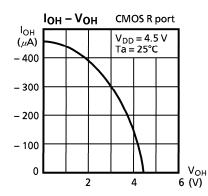

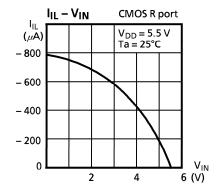

| Input Low Current                                     | I <sub>IL</sub>   | Push-pull R port                              | V <sub>DD</sub> = 5.5 V, V <sub>IN</sub> = 0.4 V                                                       | _   | _     | <b>– 2</b> | mA   |

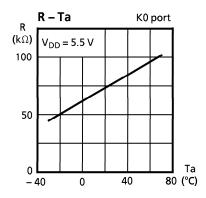

|                                                       | R <sub>IN1</sub>  | Port K0 with pull-up/pull-down                |                                                                                                        | 30  | 70    | 150        | - 0  |

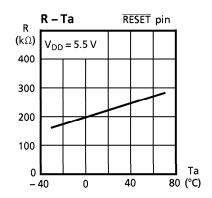

| Input Registance                                      | R <sub>IN2</sub>  | RESET                                         |                                                                                                        | 100 | 220   | 450        | kΩ   |

| Output Leakage<br>Current                             | I <sub>LO</sub>   | Open drain port R                             | V <sub>DD</sub> = 5.5 V, V <sub>OUT</sub> = 5.5 V                                                      | _   | _     | 2          | μΑ   |